t

Изобретение относится к измерительной и вычислительной технике и может быть использовано в системах обработки и передачи информации, а также в измерительной техг

нике в качестве формирователя равномерной сетки частот.

Целью изобретения является повышение точности преобразования за .счет исключения влияния методической погрепшости дискретности.

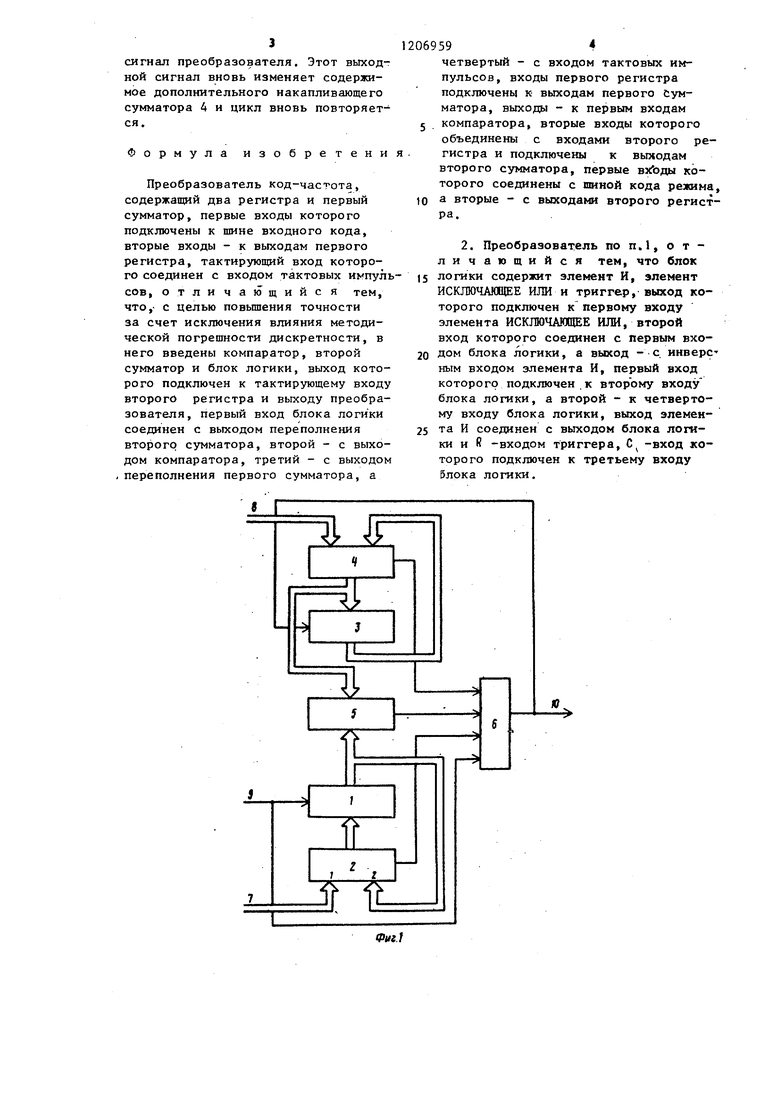

На фиг, 1 представлена функциональная схема преобразователя код-частота г .на фиг, 2 - схема блока логики.

Преобразователь содержит ре- тсту 1, сумматор 2, регистр 3s сумматор 4, компаратор 5, блок 6 логики, шину 7 входного кода, шину 8 режима, вход 9 тактирующих импульсов, шину 10 выхода преобразователя. Блок 6 логики содержит элемент И 11, элемент ИСКЛЮЧАКЩЕЕ ИЛИ 12 и триггер 13.

;Преобраэователь работает следую- mjiM образом.

На шину 7 подается входной

код N

ВЦ

а на шину 8 - код режима М.

На шине 9 действует импульсный сигнал с частотой FO 5 входной код N поступает на первый вход сумматора 2. Так тирующие импульсы поступают с ши- иы 9 с частотой о на тактирующий вход регистра 1. Входным сигналом для сумматора 4 является код регистра М. Выходной сигнал преобразователя поступает на тактирующий вход регистра 3. В обоих сумматорах 2 и 4 имеется выход, с которого снимается сигнал перепо.лнения, используемый для управления блока 6 . Сигнал переполнения появляется в том слу чае, когда содержимое сумматора будет удовлетворять условию

(1)

где : П - разрядность регистров 1 и и сумматоров 2 и 4.

При включении питания преобразователя содержимое регистров 1 и 3 обнуляется. Тогда при.включении на выходе сумматора 2 будет нулевой код, а на выходе сумматора 4 - код равный коду режима М. Увеличение содержимого сумматора 2 происходит по мере поступления тактирукжих км- пульсов с шины 9 на тактирующий

:2069592

вход регистра 1, При достижении такого состояния, когда выполняется условие

3, S2 ,

Х2)

где 5, - содержимое основного накапливающего сумматораJ Sg - содержимое дополнительного

накапливающего сумматора, на выходе , компаратора 5 появится сигнал, поступающий на второй вход блока 6 логики. Одновременное появление на входах блока 6 логики сигналов и отсутствие сигналов переполнения (естественное состояние для начала процесса) приводит к формированию на выходе блока 6 логики выходного импульса. Выходной импульс с блока 6 логики поступает на тактирующий вход регистра 3. Это приводит к увеличению содержимого сумматора 4: к текущему значению прибавляется величина, равная коду режима М. Дальнейшее развитие процесса зависит от соотношения величин Мин. Если 2 - 2 , то процесс будет повторяться описанным образом до тех 62 2 что приведет к формированию импульса переполнения, который поступает на первый вход блока 6 логики. Этот импульс блокирует формирование выходных «мпульсов преобразователя (выход блока 6 логики), до тех пор, пока не появится импульс переполнения с сумматора 2. Во время блокирующего действия импульса переполнения сумматора 4 содержимое сумматора 2 продолжает увеличиваться за счет поступающих на тактовый вход регистра 1 импульсов. Поступающие в это время на блок 6 логики сигналы с компаратора 5 блокируются импульсом переполнения сумматора 4, Формирование выходных ,импульсов не происходит. Как только на выходе переполнения сумматора 2 появляется сигнал, свидетельствующий о выполнении неравенства (1}, блокирую- ш;ее действие сигнала переполнения сумматора 2 заканчивается (хотя сам сигнал переполнения может присутствовать) ,

После снятия блокировки импульсом переполнения сумматора 2 импульсы, появляющиеся по условию (2) на выходе компаратора 5, поступают на блок 6 логики и формируют в,ыходной

3

сигнал преобразователя. Этот выходной сигнал вновь изменяет содержимое дополнительного накапливающего сумматора 4 и цикл вновь повторяется.

Формула изобретени

Преобразователь код-частота, содержащий два регистра и первый сумматор, первые входы которого подключены к шине входного кода, вторые входы - к выходам первого регистра, тактирующий вход которого соединен с входом тактовых импулсов, отличающийся тем, что,- с целью повьшения точности за счет исключения влияния методической погрешности дискретности, в него введены компаратор, второй сумматор и блок логики, выход которого подключен к тактирующему входу второго регистра и выходу преобразователя, первый вход блока логи ки соединен с выходом переполнения второго сумматора, второй - с выходом компаратора, третий - с выходом переполнения первого сумматора, а

069594

четвертый - с входом тактовых импульсов, входы первого регистра подключены к выходам первого Сумматора, выходы - к первым входам 5 . компаратора, вторые входы которого объединены с входами второго регистра и подключены к выходам второго сумматора, первые вхЪды которого соединены с шиной кода режима, to 3 вторые - с выходами второго регистра.

2. Преобразователь по п.1, о т - личающийся тем, что блок

15 логики содержит злемент И, элемеит ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер, выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с первым вхо20 дом блока логики, а выход --с, инверсным входом элемента И, первый вход которого подключен к второму входу блока логики, а второй - к четвертому входу блока логики, выход элемен25 та И соединен с выходом блока логики и В -входом триггера, С -вход которого подключен к третьему входу блока логики.

Г

Редактор Л.Гратилпо

Составитель О.Тюрина Техред А.Бабинец

Заказ 8734/59 Тираж 818Подписное

ВНИИПИ Государственного ко1иитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Филиал ШШ Патент, г.Ужгород, ул.Проектная,4

Фиг.2

Корректор Г.Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОД - ЧАСТОТА | 1995 |

|

RU2092973C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-ЧАСТОТА | 2000 |

|

RU2175813C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Преобразователь код-частота | 1984 |

|

SU1167736A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство для коррекции положения изображения объекта | 1989 |

|

SU1785015A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано в системах обработки и передачи информации. Изобретение позволяет повысить точность преобразования за счет исключения влияния методической погрешности дискретности. Преобразователь код-частота содержит первый :И- второй регистры, первый и второй сумматоры, компаратор, блок логи- ки, шины входного кода и кода режима, вход тактирукицих импульсов, шину выхода преобразователя. Блок лопики содержит элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер, 1 з.п. ф-лы, 2 ил. § (О с tsD О Од О сл со

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода в частоту | 1982 |

|

SU1039026A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-01-23—Публикация

1984-08-10—Подача