2

4

10

Н -з:

PiLS

05

Ai(t)

ff;

Г

ел

со ;о

(f,(e -mo.

Sz(t)

Sjfi)

m элементов тактовой задержки 11-17 К блоков задержки 18-20 по циклам, элементы задержки 21-26. Основной НС 1 тактируется импульсами (t) с опорной частотой fg, содержимое основного НС 1 увеличивается с каждым тактом на величину а. Импульсы Р.(t) переполнения основного НС 1 следуют с час- toтoй fg afo/b, где b - емкость основ- Чого НС 1 эти импульсы поступают на Эход фазового детектора 2 в петле фазовой автоподстройки. Импульсы переполнения дополнительных НС 5, 6 7 поступают через,блоки задержки 18-20

на входы комбинационного сумматора 8 который образует суммарную последовательность, которая с помощью преобразователя кода 9 преобразуется в позиционный код, управляющий мультиштексором 10, который совместно с элементами тактовой задержки П-17 выполня- ет роль фазового нанипулятора.З йл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1987 |

|

SU1431034A1 |

| Синтезатор частоты | 1985 |

|

SU1347145A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1231570A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частот | 1988 |

|

SU1518865A2 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Цифровой синтезатор частоты | 1989 |

|

SU1626316A1 |

Изобретение относится к радиотехнике. Цель изобретения - упрощение устройства. Синтезатор частот содержит основной накапливающий сумматор (НС) 1, фазовый детектор 2, фильтр 3 нижних частот, управляемый генератор 4, K дополнительных НС 5, 6, 7, комбинационный сумматор 8, преобразователь кода 9, мультиплексор 10, M элементов тактовой задержки 11...17, K блоков задержки 18-20 по циклам, элементы задержки 21...26. Основной НС 1 тактируется импульсами δо(T) с опорной частотой Fо, содержимое основного НС 1 увеличивается с каждым тактом на величину A. Импульсы Pо(T) переполнения основного НС 1 следует с частотой FеъAFо/B, где B-емкость основного НС 1, эти импульсы поступают на вход фазового детектора 2 в петле фазовой автоподстройки. Импульсы переполнения дополнительных НС 5, 6, 7 поступают через блоки задержки 18...20 на входы комбинационного сумматора 8, который образует суммарную последовательность, которая с помощью преобразователя кода 9 преобразуется в позиционный код, управляющий мультиплексором 10, который совместно с элементами тактовой задержки 11...17 выполняет роль фазового манипулятора. 3 ил.

Изобретение относится к радиотех™ нике и может быть использовано в пря мопередающей; . и измерительной аппаратуре. - -

Целью изобретения является упрощение устройства.

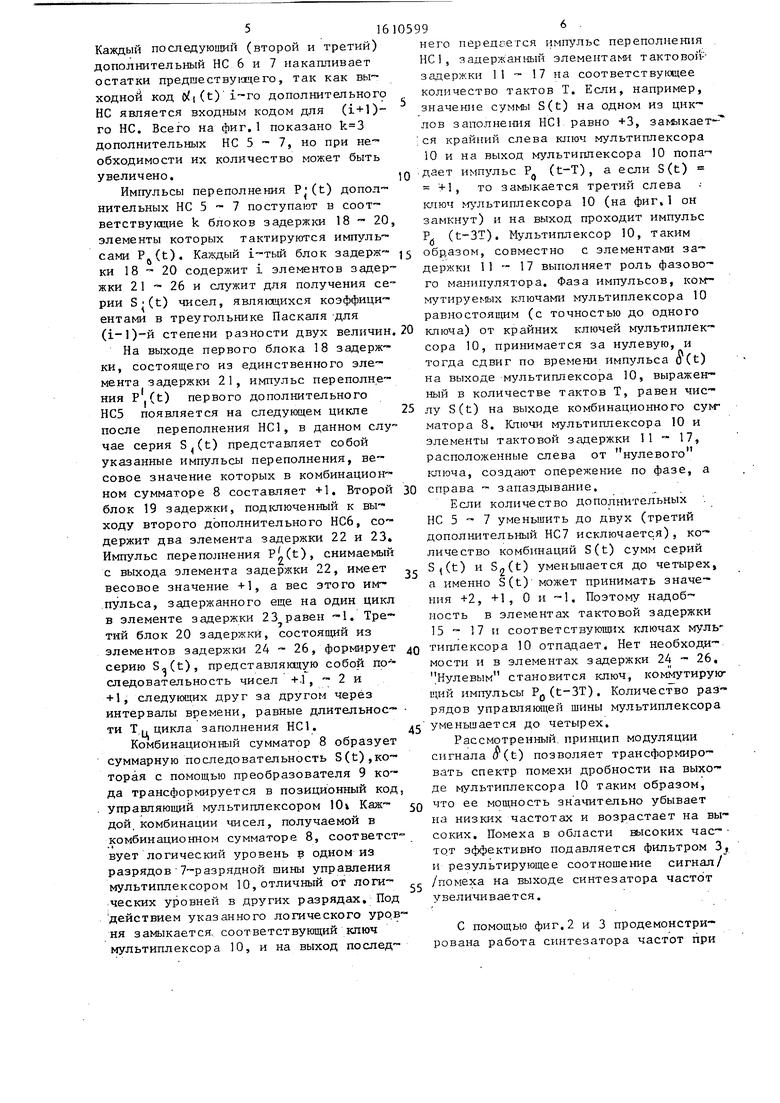

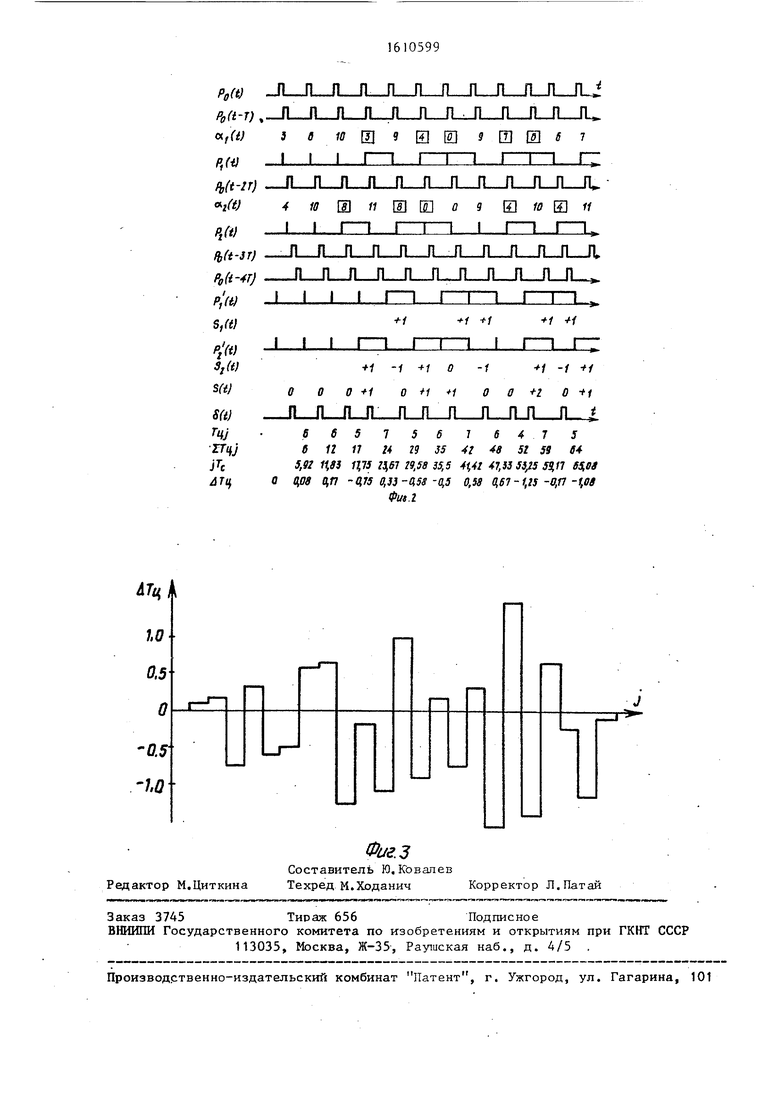

На фиг.1 изображена электрическая структурная схема синтезатора частот на фиг,2 - временные диаграммы работы устройства при двух дополнительных накапливагацих сумматорах; на фиг.3 - характер помехи при двух дополнительных накапливающих сумматорах,

Синтезатор частот содержит накап- лившоций сумматор (НС) 1, фазовый детектор 2, фильтр 3 нижних частот, управляемый генератор 4, первый, второй и третий дополнительные НС 5-7, комбинационный сумматор 8, преобразова- тель 9 кода, мультиплексор 10, m эле- ментов тактовой задержки 1 1 17 у блоков задержки 18 - 20 по ци1слам, i элементов задержки 21 - 26,

Синтезатор частот работает следующим образом.

Число а, задающее выходную часто- - ту fg, поступает на первый кодовый вход НС1, емкость которого равна чис- лу Ь, присутствующему на втором кодо- вом входе НС 1. НС1 тактируется им- пyльcaмIi (J(j(t) с опорной частотой f. и формирует на кодовом выходе ступенчатую пилообразную функцию а (t), возрастающую на каждом такте на величи г ну а. Импульсы ) переполнения НС1 следуют с частотой, в среднем равной декадных синтезаторах частот, в которых шаг сетки частот равен 10 где г - целое по- ложительное или отрицательное число, ча.стота fg и число b обычно выбираются постоянными и кратными десяти.

Через га элементов тактовой задерж ки II - 17 и мультиплексор 10, один из ключей которого обязательно замкнут, импульсы переполнения поступают на фазовый детектор 2 и являются опорными для системы фазовой автоподстройки частоты, содержащей, кроме того,фильтр 3 и управляемый генера- тор 4. Петля фазовой автоподстройки предназначена для фильтрации помех дробности, содержащихся в сигнале переполнения р (t) НС1.

Переменный код a(t), образующийся на выходе НС1, поступает на первый кодовый вход первого дополнительного НС 5, входящего в цепь последовательно включенных дополнительных накапливающих сумматоров 5-7, тактируемых импульсами P(t), задержанными с помощью первых k из m элементов тактовой задержки 11 - 13 на время i Т тактов, где i - порядковый номер первого второго или третьего дополнительных НС 5 - 7 или, что то же самое, порядковый номер элемента тактовой задержки 1 i . 13, Т 1/f - длительность такта.

При переполнении HCI импульсом ) в первом дополнительном НС5. записывается остаток в функции a(t), и затем с каждым циклом заполнения основного НС1 в первом дополнительном НС 5 накапливаются остатки в виде, функции Oi iCt). Емкости первого, второго и третьего дополнительных НС 5-7 одинаковы и равны числу а, которое поступает йа вторые входы этих сумматоров, благодаря чему емкость первого второго и третьего дополнительных НС 5 - 7 изменяется при перестройке частоты, т.е. при изменении числа а.

Каждый последующий (второй и третий) дополнительный НС 6 и 7 накапливает остатки предшествуюцего, так как выходной код (t) i -ro дополнительног9 НС является входным кодом для (i+1)- го НС. Всего на фиг.1 показано дополнительных НС 5 - 7, но при необходимости их количество может быть увеличено.

Импульсы переполнения (t) допел™ нительных НС 5 7 поступают в соответствующие k блоков задержки 18 20, элементы которых тактируются импуль10

него передается импульс переполнения НС1 , задержанный элементами тактовой-- задержки 11 - 17 на соответствующее количество тактов Т. Если, например, значение суммы S(t) на одном из циклов заполне1шя НС1, равно +3, заьыкает ;ся крайний слева ключ мультиплексора

10 и на выход мультиплексора 10 попа .дает импульс Р (t-T) , а если S(t) 4-1, то замыкается третий слева - К.ПЮЧ м льтиплексора 10 (на фиг. 1 он замкнут) и на выход проходит импульс Р. (t-ЗТ). Мультиплексор 10, таким

сами Р (t). Каждый i-тый блок задерж- 15 обр,азом, совместно с элементами заки 18 - 20 содержит i элементов задержки 21 - 26 и служит для получения серии S (t) чисел, являющихся коэффициентами в треугольнике Паскаля -для (1-1)-й степени разности двух величин. На выходе первого блока 18 задержки, состоящего из единственного элемента задержки 21, импульс переполнения Р (t) первого дополнительного НС5 появляется на следующем цикле после переполнения НС1, в данном случае серия S(t) представляет собой указанные импульсы переполнения, весовое значение которых в комбинационном сумматоре 8 составляет +1. Второй блок 19 задержки, подключенный к выходу второго дополнительного НС6, содержит два элемента задержки 22 и 23. Импульс переполнения P(t), снимаемый с выхода элемента задержки 22, имеет весовое значение +1, а вес этого импульса, задержанного еще на один цикл в элементе задержки 23.равен -1. Тре- тий блок 20 задержки, состоящий из элементов задержки 24 - 26, формирует серию S,(t), представляющую собой последовательность чисел +.1 , - 2 и +1, следующих друг за другом через интервалы времени, равные длительности Т.ц цикла заполнения НС1.

Комбинационный сумматор 8 образует

суммарную последовательность S(t),которая с помощью преобразователя 9 кода трансформируется в позиционный код, управляющий мультиплексором 10 Каж- 50 дои. комбинации чисел, получаемой в комбинационном сумматоре В, соответст- вует логический уровень в одном из разрядов 7 -разрядной шины управления мультиплексором 10,отличный от логических уровней в других разрядах. Под действием указанного логического уров ня замыкается, соответствующий ключ мультиплексора 10, и на выход последдержки 11 - 17 выполняет роль фазово го ма п1пулятора. Фаза импульсов, ком мутируемых ключами мультиплексора 10 равностояп1 1м (с точностью до одного 20 ключа) от крайних ключей мультиплек сора 10, принимается за нулевую, и тогда сдвиг по времени импульса О(t) на выходе мультиплексора 10, выражен ный в количестве тактов Т, равен чис 25 лу S(t) на выходе комбинационного су матора 8. Ключи мультиплексора 10 и элементы тактовой задержки 11 - 17, расположенные слева от нулевого ключа, создают опережение по фазе, а

30 справа - запаздывание.

Если количество дополнительных . НС 5 - 7 уменьшить до двух (третий дополнительный НС7 исключается), количество комбинаций S(t) сумм серий S,(t) и S2(t) уменьшается до четырех а именно S(t) может принимать значения +2, +1, О и -1. Поэтому надобность в элементах тактовой задержки 15 - 17 и соответствующих ключах мул 40 типлексора 10 отпдцает. Нет необходи мости и в элементах задержки 24 - 26 Нулевым становится ключ, щий импульсы P(t-3T). Количество ра рядов управляющей щины мультиплексор дс уменьшается до четырех.

Рассмотренный, принцип модуляции сигнала (t) позволяет трансформировать спектр помехи дробности на вых де мультиплексора 10 таким образом, что ее мощность значительно убывает на низких частотах и возрастает на соких. Помеха в области высоких ча тот эффективно подавляется фильтром и результирующее соотношение сигнал /помеха на выходе синтезатора частот увеличивается.

55

С помощью фиг.2 и 3 продемонстри рована работа синтезатора частот пр

10599

10

него передается импульс переполнения НС1 , задержанный элементами тактовой-- задержки 11 - 17 на соответствующее количество тактов Т. Если, например, значение суммы S(t) на одном из циклов заполне1шя НС1, равно +3, заьыкает- ;ся крайний слева ключ мультиплексора

10 и на выход мультиплексора 10 .дает импульс Р (t-T) , а если S(t) 4-1, то замыкается третий слева - К.ПЮЧ м льтиплексора 10 (на фиг. 1 он замкнут) и на выход проходит импульс Р. (t-ЗТ). Мультиплексор 10, таким

5 обр,азом, совместно с элементами за50

держки 11 - 17 выполняет роль фазового ма п1пулятора. Фаза импульсов, коммутируемых ключами мультиплексора 10 равностояп1 1м (с точностью до одного 0 ключа) от крайних ключей мультиплексора 10, принимается за нулевую, и тогда сдвиг по времени импульса О(t) на выходе мультиплексора 10, выраженный в количестве тактов Т, равен чис- 5 лу S(t) на выходе комбинационного сумматора 8. Ключи мультиплексора 10 и элементы тактовой задержки 11 - 17, расположенные слева от нулевого ключа, создают опережение по фазе, а

0 справа - запаздывание.

Если количество дополнительных . НС 5 - 7 уменьшить до двух (третий дополнительный НС7 исключается), количество комбинаций S(t) сумм серий S,(t) и S2(t) уменьшается до четырех, а именно S(t) может принимать значения +2, +1, О и -1. Поэтому надобность в элементах тактовой задержки 15 - 17 и соответствующих ключах муль 40 типлексора 10 отпдцает. Нет необходимости и в элементах задержки 24 - 26, Нулевым становится ключ, ко1 тирую щий импульсы P(t-3T). Количество разрядов управляющей щины мультиплексора дс уменьшается до четырех.

Рассмотренный, принцип модуляции сигнала (t) позволяет трансформировать спектр помехи дробности на выходе мультиплексора 10 таким образом, что ее мощность значительно убывает на низких частотах и возрастает на высоких. Помеха в области высоких час- тот эффективно подавляется фильтром 3, и результирующее соотношение сигнал/ /помеха на выходе синтезатора частот увеличивается.

55

С помощью фиг.2 и 3 продемонстрирована работа синтезатора частот при

16105998

тора, комбинационный сумматор, k бло ков задержки по циютам, вход первого, второго блоков задержки по циклам подключены соответственно к выходам переполнения первого, второго, k-ro дополнительных накапливанщих сумматоров, при этом первый, второй, блоки задержки по циклам содержат соответственно один, два, k последовательно соединенных элементов задержки, выходы которых подключены к соответствующим входам комбинационного сумматора, первый и второй кодовые входы

10

двух дополнительных НС 5,6, При этом №1брано ,, Ь 71.

Через обозначена длительность j-ro цикла заполнения НС1, выражаемая количеством тактов опорной последовательности импульсов (j (t) с частотой ТР Дполагается, что фазовый детектор 2 выполнен в виде импульсно- фазового детектора типа выборка - запоминание, Импульсы (t) являю ся ком- . мутирующими, а импульсы с частотой С Сигнала определяют начало

очередного цнюта коммутируемого пило-., ,.н-о,« к второй кодовые входы

образного напряжения. Тогда величина ,5 и тактовый вход накапливающего сумма помехи на выходе фазового детекторатора являются соответственно первым

,,,пропорционш1ьна разности ,.-и вторым кодовыми входами и тактовым

т JJiC и jTj - моменты пос-входом синтезатора частот, о т л и тутшения импульсов соответственночающийся тем, что, с целью

опорной и сигнально|1 последоватапьнос-го Упрощения синтезатора, между выходом тей на соответствующие входы фазового комбинационного сумматора и вторым детектора 2.. входом фазового детектора заведены по-,

Как видно из диаграммы, приведен-следовательно соединенные преобразо-

ной на фиг.З, с увеличением количест- ватель кода и мультиплексор а также ва дополнительных НС 5 - 7 процесс 25 введены последовательно соединенные й1ц становится более динамичным, ам- та элементов тактовой задержки такто- шштуда его растет. Расчеты на ЭВМвые входы которых объединены и подключены к тактовому входу накапливающего сумматора, тактовый вход каждо- 30 го из элементов задержки в первом,

втором, k-M блоках задержки по циклам подключен к выходу переполнения накаппоказывают, что спектральные составляющие процесса вида фиг.З в низкочастотной области вплоть до 10% от частоты fg сигнала на несколько порядков ниже соответствующих составлянщих процесса в случае отсутствия до- ливающего сумматора, который также полнитепьных НС 5 - 7. Посколысу вы- соединен с входом первого из ш эле- сокочастотные составляющие эффективно 35 ментов тактовой задержки, выход каж- подавляются фильтром 3, выигрыш по доТо из m элементов тактовой задержки соотношению сигнал/помеха оказывается подключен к соответствующему входу значительным. мультиплексора, при этом выходы перВ качестве m элементов тактовойвых k из m элементов тактовой задержзадержки П - 17 и элементов задержки 40 ки подключены к тактовому входу соот- 21-26 можно использовать Д-триггеры, ветствующего дополнительного накапли- а в качестве комбинационного суммато- вагацего сумматора, второй кодовый ра 8 - комбинационный сумматор, выцол- вход каждого из k дополнительных на- ненныи на простейших двоичных сумма- кагшивающих сумметоров соединен с пер45 вым кодовым входом накапливакщего сумматора, при этом количество суммируемых комбинаций комбинационного сумма- i тора равно k, кодовые комбинации на

- , ..J--.,.... itinc:pci- выходе первого, второго, k-го блоков тор, фазовый детектор и фильтр нижних 50 задержки по циклам образуют коэффици- частот, накапливающий сумматор,,k по- енты соответственно первой, второй следовательно соединенных дополнитель k-й строк треугольника Паскаля m ;ных накапливающих сумматоров, кодовый р авно сумме модулей коэффициентов вход первого из которых подключен квсех строк треугольника паскаля а

кодовому выходу накапливагадего сумма-55 ..

торах.

Формула изобретени я Синтезатор частот, содержащий соединенные в кольцо управляемый генера

JLJLJLJl Jl JLJl JLJL LJl nn П nn n П.П П ПП n

±

w L

r

ПППППППППППП,

4 да El « U Ш Д 9 Ш « Ш JL

ТПL

ПППППППП П л П ry ппппппппппп.

JI I L

I I I

+1 t ...J { IL

-/f

+1 -1 0 -i

0 -fi

0 1 1

-i -ti в l 0 -tl

П П П П П П П П П П П i

6 65 7 56 7 647 5

б 12 17 14 гд 354248 51 59 64

5,92 Has 1115 23,61 29,58 35,541,4247,,11 65,Bt

а OflS ЦП 0,33-ass-0,5 0,580,61 - 1,2S -0,Г1-1,08 Фиг.г

лтщ

0.5

О

0.5 1.0

r

Ш Д 9

ТПL

JI I L

+1 t ...J { IL

-/f

-1 0 -i

0 1 1

-i -ti в l 0 -tl

| Патент США № 4609881, кл.ЗЗЫА, 02.09.86 | |||

| Синтезатор частот | 1987 |

|

SU1431034A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-11-30—Публикация

1987-12-02—Подача