Изобретение относиться к измерительной технике и может быть использовано в системах автоматического управления и контроля, в которых информация представлена в частотной форме.

Известно устройство для измерения временных интервалов (а. с. 1.728.665, кл. G 04 F 10/04) в составе генератора импульсов, элемента И, формирователя импульсов, счетчика импульсов, двух регистров, блока сравнения, триггера, элемента ИЛИ-НЕ и блока элементов И. По своей сути устройство представляет собой преобразователь интервала времени в код и может быть использовано для преобразования периода в код.

Первым существенным недостатком этого устройства является то, что оно преобразует в код только часть периода следования сигналов, что придает процессу преобразования прерывистый характер. Вторым существенным недостатком рассматриваемого устройства является отсутствие синхронизации при считывании данных о величине временных интервалов. Каждый из вышеперечисленных недостатков приводит к снижению достоверности результатов преобразования периода следования сигналов в код.

Наиболее близким по технической сущности - прототипом - является устройство по а. с. 1.580.315, кл. G 04 F 10/04, которое по своей сути представляет собой преобразователь периода следования сигналов в код. Рассматриваемое устройство содержит формирователь импульсов, реле времени, элемент И, генератор импульсов, счетчик импульсов, пересчетное устройство, RS-триггер, коммутатор и регистр, причем выход элемента И соединен с тактовым входом счетчика импульсов и вторым входом пересчетного устройства, а вход формирователя импульсов является сигнальным входом устройства.

Первым существенным недостатком данного устройства является то, что оно работает в ограниченном диапазоне длительности преобразуемых периодов. Вторым существенным недостатком этого устройства является отсутствие синхронизации при считывании данных о величине преобразуемых периодов, что приводит к снижению достоверности результатов преобразования: во-первых, не исключена возможность получения ложного результата, если время считывания совпадает с временем передачи числа из счетчика в регистр, и, во-вторых, возможно неоднократное считывание из регистра одного и того же числа.

Задачей изобретения является повышение достоверности результатов преобразования периода следования сигналов в код с одновременным расширением диапазона длительности преобразуемых периодов.

Поставленная задача достигается тем, что в известное устройство в составе формирователя импульсов, генератора импульсов, триггера, первого элемента И, счетчика импульсов, регистра, причем выход первого элемента И соединен с тактовым входом счетчика импульсов, а вход формирователя импульсов является сигнальным входом преобразователя, дополнительно введены два блока управления, блок ключей, элемент памяти, блок запрета выдачи сигнала "Готовность", элемент НЕ, второй и третий элементы И, причем выход генератора импульсов соединен с тактовым входом первого блока управления и через элемент НЕ - с первым входом первого элемента И и тактовым входом второго блока управления; выход формирователя импульсов соединен с входом запуска первого блока управления, первый выход которого подключен к R-входу триггера и первому входу блока запрета выдачи сигнала "Готовность", второй выход - к тактовому входу регистра, третий выход - к входу разрешения установки счетчика импульсов, тактовому входу элемента памяти и второму входу блока запрета выдачи сигнала "Готовность", четвертый выход - к S-входу триггера, пятый выход - к третьему входу блока запрета выдачи сигнала "Готовность"; выходы данных D(0-n) счетчика импульсов через регистр и блок ключей соединены с выходами данных D(0-n) устройства; выход триггера соединен с входом разрешения счетчика импульсов, выход переполнения которого подключен ко второму входу первого элемента И, а входы данных - к шине начальной установки этого счетчика; выход элемента памяти соединен с первым входом второго элемента И, выход которого подключен к входу данных D(n+1) блока ключей и к выходу "Готовность", а второй вход - к выходу блока запрета выдачи сигнала "Готовность" и первому входу третьего элемента И; R-вход элемента памяти соединен с выходом третьего элемента И, второй вход которого подключен к первому выходу второго блока управления; вход данных элемента памяти соединен с шиной логической "1"; вход "Считывание" соединен с четвертым входом блока запрета выдачи сигнала "Готовность", входом запуска второго блока управления и входом разрешения блока ключей, выход данных D(n+1) которого подключен к выходу данных D(n+1) устройства.

Блок запрета выдачи сигнала "Готовность" предложено выполнить на двух триггерах и элементе И, причем первый вход этого блока соединен с S-входом одного из триггеров, второй вход блока - с R-входом этого триггера, выход которого подключен к первому входу элемента И, ко второму входу которого подсоединен четвертый вход блока запрета выдачи сигнала "Готовность"; выход элемента И соединен с тактовым входом другого триггера, S-вход которого подключен к третьему входу блока, вход данных - к шине логического "0", а выход этого триггера - к выходу блока запрета выдачи сигнала "Готовность".

Введение в известное устройство новых блоков, элементов и их связей позволило сформировать:

- на выходе "Готовность" устройства - сигнал "Готовность" (например, логическую "1"), свидетельствующий об окончании процесса преобразования периода в код (число), передаче полученного кода из счетчика импульсов в регистр и готовности устройства к процессу считывания;

- на выходе данных D(n+1) устройства сигнал "Норма" (например, логическую "1"), свидетельствующий о том, что информация, выданная на выходы данных D(0-n) устройства, является новой и достоверной.

При этом полностью исключается выдача сигналов "Готовность" и "Норма" в двух случаях: во-первых, когда процесс считывания информации с регистра происходит одновременно с записью в этот регистр числа, накопленного в счетчике импульсов. В этом случае на выходе данных D(n+1) устройства будет отсутствовать сигнал "Норма" и он появится там только при выполнении следующего процесса считывания; во-вторых, когда после первого считывания числа, сопровождаемого сигналами "Готовность" и "Норма" на соответствующих выходах устройства, производятся последующие считывания этого же числа.

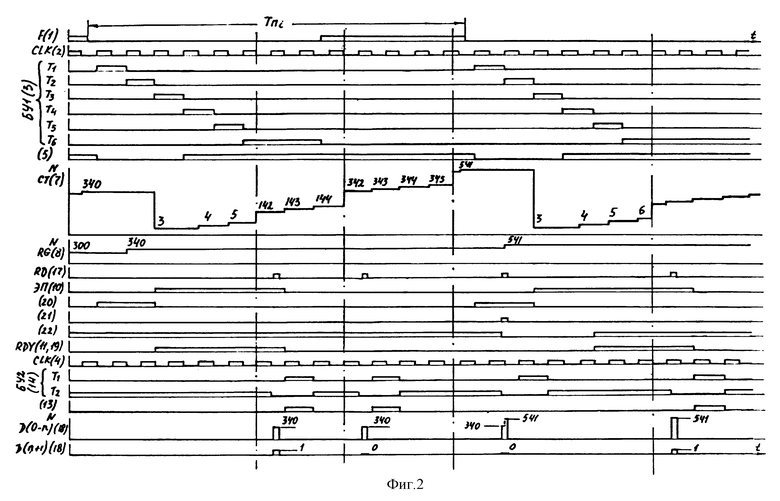

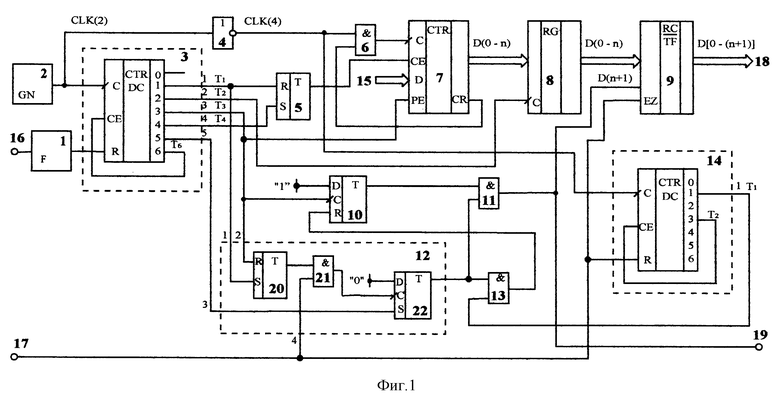

На фиг. 1 представлена блок-схема предлагаемого преобразователя периода в код, на фиг. 2 - временные диаграммы, поясняющие работу этого преобразователя.

В состав преобразователя периода в код входят формирователь импульсов 1, генератор импульсов 2, первый блок управления 3, элемент НЕ 4, триггер 5, первый элемент И 6, счетчик импульсов 7, регистр 8, блок ключей 9, элемент памяти 10, второй элемент И 11, блок запрета выдачи сигнала "Готовность" 12, третий элемент И 13, второй блок управления 14, шина начальной установки счетчика импульсов 15, сигнальный вход устройства 16, вход "Считывание" 17, выходы данных устройства 18 и выход "Готовность" 19, причем сигнальный вход устройства 16 соединен с входом формирователя импульсов 1, а выход первого элемента И 6 - с тактовым входом счетчика импульсов 7; выход генератора импульсов 2 соединен с тактовым входом первого блока управления 3 и через элемент НЕ 4 - с первым входом первого элемента И 6 и тактовым входом второго блока управления 14; выход формирователя импульсов 1 соединен с входом запуска первого блока управления 3, первый выход которого подключен к R-входу триггера 5 и первому входу блока запрета выдачи сигнала "Готовность" 12, второй выход - к тактовому входу регистра 8, третий выход - к входу разрешения установки счетчика импульсов 7, тактовому входу элемента памяти 10 и второму входу блока запрета выдачи сигнала "Готовность" 12, четвертый выход - к S-входу триггера 5, пятый выход - к третьему входу блока запрета выдачи сигнала "Готовность" 12; выходы данных D(0-n) счетчика импульсов 7 через регистр 8 и блок ключей 9 соединены с выходами данных D(0-n) 18 устройства; выход триггера 5 соединен с входом разрешения счетчика импульсов 7, выход переполнения которого подключен ко второму входу первого элемента И 6, а входы данных - к шине начальной установки 15 этого счетчика; выход элемента памяти 10 соединен с первым входом второго элемента И 11, выход которого подключен к входу данных D(n+l) блока ключей 9 и к выходу "Готовность" 19, а второй вход - к выходу блока запрета выдачи сигнала "Готовность" 12 и первому входу третьего элемента И 13; R-вход элемента памяти 10 соединен с выходом третьего элемента И 13, второй вход которого подключен к первому выходу второго блока управления 14; вход данных элемента памяти 10 соединен с шиной логической "1"; вход "Считывание" 17 соединен с четвертым входом блока запрета выдачи сигнала "Готовность" 12, входом запуска второго блока управления 14 и входом разрешения блока ключей 9, выход данных D(n+1) которого подключен к выходу данных D(n+1) 18 устройства.

Блок запрета выдачи сигнала "Готовность" 12 выполнен на триггерах 20 и 22 и элементе И 21, причем первый вход этого блока соединен с S-входом триггера 20, второй вход блока - с R-входом этого триггера, выход которого подключен к первому входу элемента И 21, ко второму входу которого подсоединен четвертый вход блока запрета выдачи сигнала "Готовность"; выход элемента И соединен с тактовым входом триггера 22, S-вход которого подключен к третьему входу блока, вход данных - к шине логического "0", а выход этого триггера - к выходу блока запрета выдачи сигнала "Готовность "12.

На фиг. 1 и 2 приняты следующие условные обозначения:

CLK(2) - последовательность тактовых импульсов, вырабатываемых генератором импульсов (2);

CLK(4) - последовательность тактовых импульсов, инверсных CLK(2);

D(0-n) - входы/выходы данных, имеющие номера от 0 до n;

D(n+1) - вход/выход данных, имеющий номер n+1;

F(1) - выходные сигналы формирователя импульсов 1;

Tпi - период следования сигналов F(1), подлежащий преобразованию в код и имеющий номер i;

БУ1(3), БУ2(14) - соответственно первый 3 и второй 14 блоки управления;

T1-6 - управляющие импульсы, вырабатываемые блоками управления 3 и 14;

N СТ(7) - число, накопленное в счетчике импульсов 7;

N RG (8) - число, зафиксированное в регистре 8;

RD(17) - импульсы считывания, поступающие на вход 17 устройства;

ЭП(10) - выходной сигнал элемента памяти 10;

RDY(11,19) - сигнал "Готовность", имеющий место на выходе схемы И 11 и на шине 19;

N D(0-n) (18) - число, переданное на выходные шины данных D(0-n) 18 устройства.

При этом на фиг. 2 в скобках указаны номера блоков и элементов, на выходах которых имеют место приведенные осциллограммы.

Предлагаемое устройство работает следующим образом. При включении питания начинает работать генератор импульсов 2. Далее в работе устройства можно выделить два цикла: цикл преобразования периода Тпi в код (число) Ni, записи полученного кода Ni в регистр 8 и цикл считывания записанного кода Ni, то есть цикл передачи числа Ni из регистра 8 на выходы данных 18.

Цикл считывания может начинаться либо по требованию внешнего устройства - потребителя информации, например процессора, вырабатывающего с этой целью последовательность импульсов считывания RD (асинхронный режим работы двух устройств), либо по требованию предлагаемого устройства, которое с этой целью вырабатывает сигнал готовности RDY, приводящий к прерыванию работы процессора и формированию последним одиночного импульса считывания RD (синхронный режим работы двух устройств).

Цикл преобразования периода Tпi начинается с приходом на вход устройства 16 сигнала, соответствующего окончанию периода Тпi-1 и началу преобразуемого периода Тпi. При этом формирователь 1 выработает из входного сигнала импульс F1 (например, отрицательной полярности), запускающий первый блок управления 3. По переднему фронту тактовых импульсов CLK(2) на выходах этого блока управления сформируются управляющие импульсы Ti.

Первый управляющий импульс T1 устанавливает триггер 5 в состояние логического "0" и сигнал с прямого выхода этого триггера запрещает счет импульсов CLK(4) в счетчике 7. Кроме того, первый управляющий импульс T1 устанавливает триггер 20 в состояние логической "1", что соответствует включению в блоке 12 режима ожидания.

По переднему фронту второго управляющего импульса Т2 происходит запись числа Ni-1, накопленного в счетчике 7, в регистр 8.

Третий управляющий импульс Т3 осуществляет запись в счетчик 7 начального установочного числа "3", которое равно числу импульсов, не поступивших в счетчик из-за запрета счета, имеющего место во время работы первого блока управления 3. Кроме того, третий управляющий импульс Т3 устанавливает элемент памяти 10 в состояние логической "1", что соответствует формированию им сигнала "Готовность", а триггер 20 - в состояние логического "0", что равнозначно выключению в блоке 12 режима ожидания.

Четвертый управляющий импульс Т3 устанавливает триггер 5 в состояние логической "1" и сигнал с его прямого выхода разрешает поступление тактовых импульсов CLK(4) в счетчик 7, в котором начинается счет импульсов. Процесс счета импульсов продолжается до окончания преобразуемого периода Tпi.

Пятый управляющий импульс T5 устанавливает триггер 22 в состояние логической "1" (если до этого он был в состоянии логического "0").

Шестой тактовый импульс Т6 поступает на вход СЕ блока управления 3 и прекращает формирование последующих управляющих импульсов.

Цикл преобразования периода Tпi в код Ni и записи полученного кода Ni в регистр 8 будет повторяться периодически, синхронно с поступлением на шину 16 входных сигналов.

Цикл считывания при асинхронной работе двух устройств происходит следующим образом. На вход 17 поступает от процессора импульс считывания RD. На время действия этого импульса блок ключей 9 переводится из третьего состояния в состояние замкнутых ключей и с выходов D(0-n) регистра 8 на выходы данных D(0-n) 18 подается код Ni. Одновременно с этим с выхода элемента памяти 10 на выход данных D(n+1) 18 поступает логическая 1, что равнозначно формированию на этом выходе устройства сигнала "Норма".

После окончания импульса считывания RD начинает работать второй блок управления 14. При этом по переднему фронту тактовых импульсов CLK(4) на выходах этого блока формируются управляющие импульсы. Первый управляющий импульс T1 блока управления 14 поступает через третий элемент И 13 на R-вход элемента памяти 10 и устанавливает его в состояние логического "0".

При повторном поступлении импульса считывания RD на вход 17 процесс считывания повторится. Однако в этот раз с выхода элемента памяти 10 на выход данных D(n+1) 18 будет передан логический "0", что свидетельствует о повторном считывании числа Ni.

В цикле считывания, при котором импульс считывания RD поступает на вход 17 в то время, когда в блоке 12 включен режим ожидания, триггер 20 будет находиться в состоянии логической "1", с его прямого выхода на первый вход элемента И 21 будет подан открывающий сигнал и импульс считывания RD, пройдя через элемент И 21, установит триггер 22 в состояние логического "0".

При этом на прямом выходе триггера 22 будет сигнал, соответствующий логическому "0". Этот сигнал поступит через схему И 11 на вход данных D(n+1) блока 9 и при замыкании ключей этого блока на выход данных D(n+1) 18. В этом случае наличие логического "0" на выходе данных D(n+1) 18 будет свидетельствовать о недостоверности информации, поданной на выходы данных D(0-n) 18.

Одновременно с этим сигнал логического "0" с выхода триггера 22 будет подан в качестве запрещающего на второй вход схемы И 13. При этом управляющий импульс T1 с выхода блока 14 не пройдет через схему И 13 на R-вход элемента памяти 10 и последний останется в состоянии логической "1". После окончания импульса T1 блока 14 пятый управляющий импульс Т5 блока 3 установит триггер 22 в состояние логической "1".

В следующем цикле считывания на выходе данных D(n+1) 18 будет зафиксирован сигнал "Норма", так как в этом случае с выходов элемента памяти 10 и триггера 22 на входы элемента И 11 будут поданы открывающие сигналы и выходной сигнал элемента И 11, соответствующий логической "1", пройдя через блок ключей 9, будет подан на выход данных D(n+1) устройства.

Цикл чтения при синхронной работе двух устройств начинается в процессе работы первого блока управления 3. При этом третий управляющий импульс Т3 блока 3 устанавливает элемент памяти 10 в состояние логической "1". Сигнал с выхода элемента памяти 10 поступает через элемент И 11 на выход готовности 19 предлагаемого устройства и далее на соответствующий вход процессора. Последний прерывает свою работу и выдает на вход 17 предлагаемого устройства сигнал считывания RD. Далее происходит процесс считывания, описание которого приведено выше.

Предлагаемое устройство может работать в широком диапазоне длительности преобразуемых периодов. Причем минимальное значение длительности преобразуемых периодов ограничивается погрешностью преобразования, а максимальное значение - емкостью счетчика импульсов 7. Введение связи выхода переноса счетчика 7 со вторым входом первого элемента И 6 позволило исключить ложные результаты преобразования, обусловленные переполнением счетчика 7 при подаче на вход устройства сигналов с низкими частотами. В этом случае сигнал с выхода переноса подается на второй вход первого элемента И 6 и запрещает поступление импульсов на счетный вход счетчика 7, во всех разрядах которого будет записана логическая "1".

В предлагаемом устройстве исключается выдача сигналов "Готовность" и "Норма" при втором и последующих считываниях одного и того же числа, что повышает достоверность результатов преобразования периода в код. Это позволяет, во-первых, реализовать алгоритмы, связанные с вычислением разности длительности двух смежных периодов, например алгоритм вычисления скорости изменения частоты, приведенный в описании а. с. 1.288.620, кл. G 01 R 23/00.

Во-вторых, существенно сократить количество операций, выполняемых процессором. Последнее объясняется тем, что для получения информации о длительности каждого периода необходимо, чтобы выполнялось условие TRD<Тnmin, где TRD - длительность такта считывания, Тnmin - минимальная длительность преобразуемого периода. Из этого следует, что при преобразовании в широком диапазоне длительности периода возможно многократное считывание одного и того же числа. В предлагаемом устройстве процессор будет получать информацию о повторном считывании числа Ni и поэтому может исключить обработку полученных вторично данных.

Предлагаемый преобразователь не требует начальной установки и вырабатывает достоверную информацию о длительности периода начиная с первого периода исследуемой последовательности сигналов. Однако для того, чтобы при считываниях, предшествующих началу работы источника исследуемых сигналов, на выходах данных 18 фиксировалось число "0", необходимо производить предварительное обнуление триггера 5, счетчика 7, регистра 8, элемента памяти 10. Схема обнуления этих элементов на фиг. 1 не приведена.

В предлагаемом устройстве в качестве элементов блок-схемы фиг. 1 могут быть использованы серийно выпускаемые интегральные микросхемы. Так, например, функцию блоков управления 2 и 14 могут выполнять счетчик - дешифратор 564 ИЕ9 или счетчик 1554 ИЕ2 и дешифратор 1554ИД7, функцию счетчика импульсов 7 - счетчики 1554 ИЕ10, регистра 8 - регистры 1554 ИР35, блока ключей 9 - формирователи сигналов 1554 АП5. Реализация остальных элементов блок-схемы фиг. 1 ничем не отличается от реализации аналогичных элементов блок-схемы прототипа и не вызывает затруднений.

Как видно из вышеизложенного, предлагаемое устройство обеспечивает высокую достоверность результатов преобразования периода следования сигналов в код, при этом преобразование может осуществляться в широком диапазоне длительности этих периодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2001 |

|

RU2208797C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332784C2 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ РЕГУЛЯРНОЙ ПРЕЦЕССИИ (ВАРИАНТЫ) | 1999 |

|

RU2153446C1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 2000 |

|

RU2174284C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОМАНДЫ НА ИСКЛЮЧЕНИЕ АВАРИЙНОЙ СИТУАЦИИ ПРИ УПРАВЛЕНИИ ИСПОЛНИТЕЛЬНЫМИ МЕХАНИЗМАМИ СТЫКОВОЧНОГО АГРЕГАТА | 2000 |

|

RU2167797C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧАСТОТЫ ВРАЩЕНИЯ | 2003 |

|

RU2240565C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ПО ДЛИТЕЛЬНОСТИ | 2006 |

|

RU2332783C2 |

| СЧЕТЧИК | 2014 |

|

RU2565528C1 |

| МНОГОКАНАЛЬНЫЙ КОМАНДНЫЙ АППАРАТ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 2005 |

|

RU2340925C2 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

Изобретение относится к измерительной технике и может быть использовано в системах автоматического управления и контроля, в которых информация представлена в частотной форме. Преобразователь содержит формирователь импульсов, генератор импульсов, два блока управления, элемент НЕ, триггер, три элемента И, счетчик импульсов, регистр, блок ключей, элемент памяти, блок запрета выдачи сигнала "Готовность". Устройство работает в широком диапазоне длительности преобразуемых сигналов, при этом минимальное значение длительности ограничивается погрешностью преобразования, а максимальное значение - емкостью счетчика импульсов. Изобретение обеспечивает повышение достоверности результатов преобразования периода следования сигналов в код с одновременным расширением диапазона длительности преобразуемых периодов. 1 з. п. ф-лы, 2 ил.

| Измеритель периода | 1987 |

|

SU1580315A1 |

| Устройство для измерения временных интервалов | 1990 |

|

SU1728665A1 |

| ЦИФРОВОЙ ПЕРИОДОМЕР | 1991 |

|

RU2011997C1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2043648C1 |

| RU 2071104 C1, 27.12.1996. | |||

Авторы

Даты

2002-01-27—Публикация

2000-05-06—Подача