Изобретение относится к вычислительной и импульсной технике, и может быть использовано при построении высоконадежных резервированных систем для счета и обработки цифровой информации.

Известны устройства мажоритарного резервирования, см., например, описанное в [1]. Они содержат мажоритарный элемент, который позволяет при сбое в одном из каналов формировать верный обобщенный сигнал.

Однако эти устройства не могут самостоятельно восстанавливать истинное логическое состояние в канале, потерпевшем сбой (несанкционированное изменение состояния элементов памяти, например триггеров) и в дальнейшем, при втором сбое, могут сформировать ложную информацию.

Известен резервированный счетчик импульсов - прототип, описание которого приведено в [2] . Устройство содержит m каналов, а в каждом канале n-разрядный счетчик, каждый разряд которого включает триггер, два элемента И и мажоритарный элемент, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, выходы которых подключены соответственно к S-входу и R-входу триггера, прямой выход мажоритарного элемента каждого разряда, кроме n-го, соединен с C-входом триггера последующего разряда, прямой выход мажоритарного элемента каждого разряда каждого канала является выходом канала, соединенным с соответствующим выходом резервированного счетчика импульсов, выходы триггеров одноименных разрядов всех каналов соединены с соответствующими входами мажоритарных элементов тех же разрядов, кроме того, каждый канал содержит генератор импульсов и последовательно соединенные (n+1)-й мажоритарный элемент и элемент задержки, выход которого соединен с C-входом триггера первого разряда, входы (n+1)-го мажоритарного элемента каждого канала подключены к входам каналов и являются входами резервированного счетчика импульсов, выход (n+1)-го мажоритарного элемента в каждом канале соединен с управляющим входом генератора импульсов, выход которого соединен с вторыми входами первого и второго элементов И всех разрядов.

Этот резервированный счетчик импульсов может самостоятельно восстанавливать информацию, потерянную при наличии сбоев, количество которых меньше, чем мажоритарное число M[M=(m+1):2] в каждом разряде счетчика. Однако для нормальной работы резервированного счетчика импульсов требуется, чтобы входные импульсы приходили синхронно или с незначительным разбегом по переднему и заднему фронтам, что ограничивает область применения устройства.

Задача изобретения - расширение области применения за счет обеспечения работы с несинхронными (следующими в разное время) входными импульсами.

Эта задача достигается тем, что в резервированный счетчик, содержащий m каналов, а в каждом канале n-разрядный счетчик, каждый разряд которого включает триггер, два элемента И и мажоритарный элемент, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, выходы которых подключены соответственно к S-входу и R-входу триггера, прямой выход мажоритарного элемента каждого разряда, кроме n-го, соединен с C-входом триггера последующего разряда, прямой выход мажоритарного элемента каждого разряда каждого канала является выходом канала, соединенным с соответствующим выходом резервированного счетчика, выходы триггеров одноименных разрядов всех каналов соединены с соответствующими входами мажоритарных элементов тех же разрядов, кроме этого, каждый канал содержит (n+1)-й мажоритарный элемент, элемент задержки и генератор импульсов, выход которого соединен с вторыми входами первого и второго элементов И всех разрядов, а управляющий вход - через элемент задержки соединен с C-входом триггера первого разряда, входы (n+1)-го мажоритарного элемента каждого канала подключены к соответствующим входам (n+1)-х мажоритарных элементов других каналов, дополнительно введены в каждый канал формирователь импульсов, реверсивный счетчик, (2n+1)-й, (2n+2)-й элементы И, первый и второй элементы И-НЕ, при этом в каждом канале выходы первого и второго элементов И-НЕ соединены с первыми входами соответственно (2n+1)-го и (2n+2)-го элементов И, выходы которых подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, второй вход (2n+2)-го элемента И является входом данного канала резервированного счетчика, выход (n+1)-го мажоритарного элемента соединен через формирователь импульсов с элементом задержки и вторым входом (2n+1)-го элемента И, прямой и инверсный выходы первого разряда реверсивного счетчика соединены, соответственно, с первыми входами первого и второго элементов И-НЕ, а инверсный и прямой выходы второго разряда реверсивного счетчика соединены соответственно с вторыми входами первого и второго элементов И-НЕ, кроме этого, прямой выход второго разряда реверсивного счетчика соединены с первым входом (n+1)-го мажоритарного элемента.

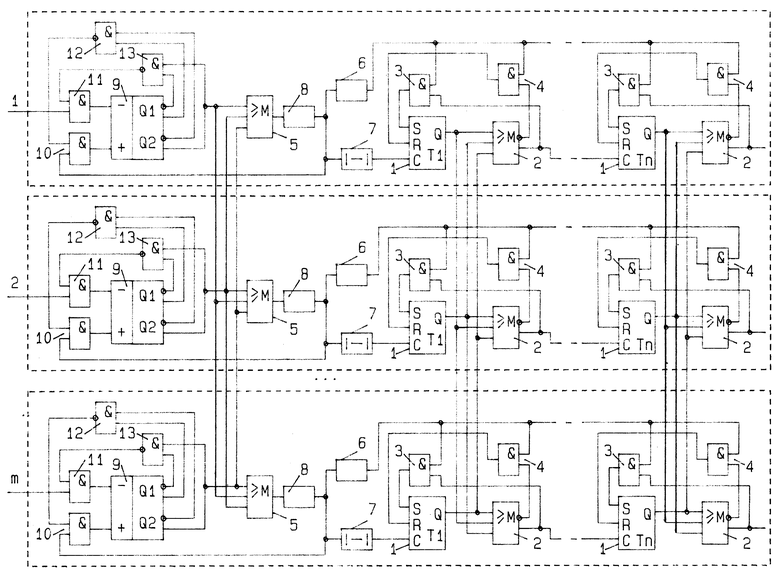

На фиг. 1 приведена блок-схема резервированного счетчика, где 1 - триггер, 2 - мажоритарный элемент, 3 - первый элемент И, 4 - второй элемент И, 5 - (n+1)-й мажоритарный элемент, 6 - генератор импульсов, 7 - элемент задержки, 8 - формирователь импульсов, 9 - реверсивный счетчик, 10 - (2n+1)-й элемент И, 11 - (2n+2)-й элемент И, 12 - первый элемент И-НЕ, 13 - второй элемент И-НЕ.

Резервированный счетчик содержит m каналов, каждый из которых включает n-разрядный счетчик. Каждый разряд содержит триггер 1, первый 3 и второй 4 элементы И, мажоритарный элемент 2, прямой и инверсный выходы которого соединены с первыми входами соответственно первого 3 и второго 4 элементов И, выходы которых подключены соответственно к S-входу и R-входу триггера 1. Прямой выход мажоритарного элемента 2 каждого разряда, кроме n-го, соединен с C-входом триггера 1 последующего разряда. Прямой выход мажоритарного элемента 2 каждого разряда каждого канала является выходом канала, соединенным с соответствующим выходом резервированного счетчика. Выходы триггеров 1 одноименных разрядов всех каналов соединены с соответствующими входами мажоритарных элементов 2 тех же разрядов. Кроме этого, каждый канал содержит (n+1)-й мажоритарный элемент 5, элемент задержки 7 и генератор импульсов 6, выход которого соединен с вторыми входами первого 3 и второго 4 элементов И всех разрядов, а управляющий вход - через элемент задержки 7 соединен с C-входом триггера первого разряда 1. Входы (n+1)-го мажоритарного элемента 5 каждого канала подключены к соответствующим входам (n+1)-х мажоритарных элементов 5 других каналов. Каждый канал резервированного счетчика содержит формирователь импульсов 8, реверсивный счетчик 9, (2n+1)-й 10, (2n+2)-й 11 элементы И, первый 12 и второй 13 элементы И-НЕ. При этом в каждом канале выходы первого 12 и второго 13 элементов И-НЕ соединены с первыми входами соответственно (2n+1)-го 10 и (2n+2)-го 11 элементов И, выходы которых подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика 9. Второй вход (2n+2)-го элемента И 11 является входом данного канала резервированного счетчика, выход (n+1)-го мажоритарного элемента 5 соединен через формирователь импульсов 8 с элементом задержки 7 и вторым входом (2n+1)-го элемента И 11. Прямой и инверсный выходы первого разряда реверсивного счетчика 9 соединены соответственно с первыми входами первого 12 и второго 13 элементов И-НЕ, а инверсный и прямой выходы второго разряда реверсивного счетчика 9 соединены соответственно с вторыми входами первого 12 и второго 13 элементов И-НЕ, кроме этого, прямой выход второго разряда реверсивного счетчика 9 соединены с первым входом (n+1)-го мажоритарного элемента 5.

Резервированный счетчик работает следующим образом (для наглядности примем m=3 и что все реверсивные счетчики 9 находятся в нулевом состоянии, а логической единице соответствует высокий уровень сигнала). Генератор импульсов 6 в каждом канале, при наличии низкого разрешающего уровня на его управляющем входе, периодически формирует импульсы, которые поступают на вторые входы всех элементов И 3, 4 этого канала, и разрешают им пропустить информацию с прямого и инверсного выходов мажоритарных элементов 2 каждого разряда на S и R входы триггеров 1 этих разрядов. Так, если в триггерах 1 k-х разрядов (где k может принимать значение от 1 до n) каждого канала записана единица, то на прямом выходе мажоритарного элемента 2 этого разряда будет высокий уровень, который, пройдя через первый элемент И 3 на S-вход триггера 1, подтвердит его единичное состояние, а если в триггерах 1 k-х разрядов каждого канала был ноль, то высокий уровень с инверсного выхода мажоритарного элемента 2 пройдет через второй элемент И 4 на R-вход триггера 1 и подтвердит его нулевое состояние. Учитывая, что реверсивные счетчики 9 всех каналов находятся в нулевом состоянии, в результате чего нулевые уровни с прямых выходов их 1-го и 2-го разрядов поступают на первый вход первого 12 и второй вход второго 13 элементов И-НЕ, поэтому на их выходах будут высокие уровни которые и поступят на первые входы (2n+1)-го 10 и (2n+2)-го 11 элементов И. Информационный импульс, поступив на один из входов (например, первый) резервированного счетчика, пройдет через второй вход (2n+2)-го элемента И 11 (на его первом входе высокий разрешающий уровень) на вычитающий вход реверсивного счетчика 9 и переведет его в состояние, при котором во всех разрядах будут единицы. В результате высокий уровень с его прямого выхода 2-го разряда поступит на первый вход (n+1)-го мажоритарного элемента 5 первого канала и соответствующие входы мажоритарных элементов 5 остальных каналов. А нулевые уровни с инверсных выходов 1-го и 2-го разрядов реверсивного счетчика 9 поступят на первый вход второго 13 и второй вход первого 12 элементов И-НЕ, в результате чего на их выходах останется высокий уровень. После того как на любой другой вход устройства, например второй, поступит импульс, он также будет воспринят реверсивным счетчиком 9 своего канала. В результате высокий уровень с прямого выхода его 2-го разряда попадет на первый вход (n+1)-го мажоритарного элемента 5 второго канала и соответствующие входы мажоритарных элементов 5 остальных каналов. При наличии двух единиц на входах трехразрядных мажоритарных элементов 5 на их выходах появится высокий уровень, который поступит на входы формирователя импульсов 8 и последними будут сформированы импульсы. Эти импульсы поступят на вторые входы (2n+1)-х элементов И 10 каждого канала, пройдя через которые попадут на суммирующие входы всех реверсивных счетчиков 9. В результате чего их состояние увеличится на единицу - реверсивный счетчик 9 1-го канала и реверсивный счетчик 9 2-го канала будут обнулены, а реверсивный счетчик 9 3-го канала перейдет в состояние "+1" (единица в младшем разряде). Ближайшим импульсом (опаздывающим), пришедшим на третий вход резервированного счетчика, состояние реверсивного счетчика 9 третьего канала будет уменьшено на единицу, т.е. реверсивный счетчик 9 перейдет в исходное нулевое состояние. Кроме этого, в каждом канале, импульс с выхода формирователя импульсов 8 попадет на управляющий вход генератора импульсов 8 и вход элемента задержки 7. В результате в каждом канале генератор импульсов 6 будет заблокирован - во время присутствия импульсов на управляющем входе генератора импульсов 6 на его выходе будет низкий уровень. Импульс с выхода формирователя импульсов 8 пройдет через элемент задержки 7 и попадет на C-вход триггера 1 младшего разряда канала, и своим передним фронтом изменит его состояние. Элемент задержки 7 необходим для того чтобы передний фронт информационного импульса с выхода формирователя импульсов 8 попал на C-вход триггера 1 в момент, когда на его S и R входах отсутствует высокий установочный уровень.

В случае сбоя в каком-либо разряде счетчика, например в k-м любого канала, например 1, ложная информация с k-го триггера 1 поступит на первый вход k-го мажоритарного элемента 2, на остальных входах которого находится истинная информация с k-х триггеров 1 остальных каналов. В результате этой комбинации на выходе k-го мажоритарного элемента 2 будет истинная информация, которая поступит на первые входы первого и второго элементов И 3, 4 k-го разряда. Ближайший очередной импульс с выхода генератора импульсов 6 этого канала, поступит на вторые входы первого и второго элементов И 3, 4 k-го разряда резервированного счетчика импульсов, и разрешит им пропустить истинную информацию с их первых входов на S и R входы k-го триггера. В результате этого в нем будет восстановлено истинное логическое состояние. Аналогичным образом будет компенсирован сбой в любом разряде любого канала.

Рассмотрим работу резервированного счетчика при различном количестве информационных импульсов, поступающих на его входы, - такая ситуация может возникнуть в случае отказа одного из каналов источника информации. Рассмотрим вариант, когда на один из входов не поступают информационные импульсы, например на первый. Пусть реверсивный счетчик 1-го канала 9 находится в нулевом состоянии (в его 1-м и 2-м разряде ноль). В этом случае после прихода первых информационных импульсов на входы резервированного счетчика и восприятия им последних в реверсивном счетчике 1-го канала 9 в 1-м разряде появится единица - высокий уровень на прямом выходе 1-го разряда, последний поступит на первый вход первого элемента И-НЕ 12. В результате на выходе первого элемента И-НЕ 12 появится низкий уровень, который поступит на первый вход (2n+1)-го элемента И 10 и запретит ему пропускать очередной импульс с выхода (n+1)-го мажоритарного элемента 5 на суммирующий вход реверсивного счетчика 9. Т.е. реверсивный счетчик 9 не может быть заполнен больше чем до уровня единица в 1-м разряде при положительном переполнении. Это необходимо для того, чтобы не допустить потери информации при положительном переполнении реверсивного счетчика 9. Рассмотрим вариант, когда на один из входов поступает больше информационных импульсов, чем в остальных каналах, например на первый. Первый, пришедший на вход канала, импульс переведет реверсивный счетчик 9 в состоянии, при котором во всех его разрядах находятся единицы. Следующий информационный импульс изменит состояние младшего разряда реверсивного счетчика 9 - в его 1-м разряде появится ноль - низкий уровень на прямом выходе и высокий на инверсном выходе, последний поступит на первый вход второго элемента И-НЕ 13. В результате на выходе второго элемента И-НЕ 13 появится низкий уровень, который поступит на первый вход (2n+2)-го элемента И 11 и запретит ему пропускать очередной информационный импульс с первого входа резервированного счетчика. Таким образом, реверсивный счетчик 9 не может быть заполнен больше чем до уровня ноль в 1-м разряде при отрицательном переполнении. Это не позволит ему переполниться и потери информации в резервированном счетчике не произойдет.

Как видно из описания работы резервированного счетчика, положительный эффект заключается в том, что он обеспечивает работу с несинхронными входными импульсами, более того импульс может приходить на любой вход резервированного счетчика после того, как на других входах информационные импульсы уже прошли.

Предлагаемая совокупность признаков, в рассмотренных авторами решениях, не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства можно использовать логические элементы цифровых микросхем любых серий, например 564 и т.д. В качестве элементов задержки 7 можно использовать реле времени, например РДВ-11. Время задержки Т должно определяться как:

t1 + t2 < T < t3,

где t1 - время переключения генератора импульсов 6 под действием управляющего сигнала, t2 - задержка сигнала при прохождении через элемент И, t3 - длительность импульса генерируемого формирователем импульсов 8.

Литература

1. Справочник. Микропроцессорные структуры. Инженерные решения. Б.В. Шевкопляс. М.: Радио и связь, 1993, с. 47.

2. Патент Российской Федерации N 2122282, кл. МПК6 H 03 K 21/40, G 06 F 11/18, от 13.05.1997. Резервированный счетчик импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 2003 |

|

RU2264690C2 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2008 |

|

RU2396591C1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2240568C1 |

| СЧЕТЧИК | 2014 |

|

RU2565528C1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ДЛЯ ФОРМИРОВАНИЯ МЕТОК ВРЕМЕНИ | 2008 |

|

RU2379829C1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2122282C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДА В КОД | 2000 |

|

RU2178908C1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2422870C2 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408045C2 |

Изобретение относится к вычислительной и импульсной технике и может быть использовано в системах счета и обработки цифровой информации. Техническим результатом является расширение области применения за счет работы с несинхронными входными импульсами. Счетчик содержит m каналов, а в каждом канале n-разрядный счетчик, каждый разряд которого включает триггер, элементы И, мажоритарный элемент, формирователь импульсов, реверсивный счетчик и элементы И-НЕ. 1 ил.

Резервированный счетчик, содержащий m каналов, а в каждом канале n-разрядный счетчик, каждый разряд которого включает триггер, два элемента И и мажоритарный элемент, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, выходы которых подключены соответственно к S-входу и R-входу триггера, прямой выход мажоритарного элемента каждого разряда, кроме n-го, соединен с С-входом триггера последующего разряда, прямой выход мажоритарного элемента каждого разряда каждого канала является соответственно выходом канала, соединенным с соответствующим выходом резервированного счетчика, выходы триггеров одноименных разрядов всех каналов соединены с соответствующими входами мажоритарных элементов тех же разрядов всех каналов, кроме того, каждый канал содержит (n+1)-й мажоритарный элемент, элемент задержки и генератор импульсов, выход которого соединен с вторыми входами первого и второго элементов И всех разрядов, отличающийся тем, что в каждый канал введены формирователь импульсов, реверсивный счетчик, (2n+1)-й, (2n+2)-й элементы И, первый и второй элементы И-НЕ, при этом в каждом канале выходы первого и второго элементов И-НЕ соединены с первыми входами соответственно (2n+1)-го и (2n+2)-го элементов И, выходы которых подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, второй вход (2n+2)-го элемента И является входом данного канала резервированного счетчика, выход (n+1)-го мажоритарного элемента соединен через формирователь импульсов со вторым входом (2n+1)-го элемента И и с элементом задержки, через который управляющий вход генератора импульсов соединен с С-входом триггера первого разряда, прямой и инверсный выходы первого разряда реверсивного счетчика соединены соответственно с первыми входами первого и второго элементов И-НЕ, а инверсный и прямой выходы второго разряда реверсивного счетчика соединены соответственно с вторыми входами первого и второго элементов И-НЕ, кроме того, прямой выход второго разряда реверсивного счетчика каждого канала соединен с первым входом (n+1)-го мажоритарного элемента этого канала, входы которого подключены к соответствующим входам (n+1)-х мажоритарных элементов других каналов.

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2122282C1 |

| ШЕВКОПЛЯС Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения | |||

| Справочник | |||

| - М.: Радио и связь | |||

| Способ изготовления фанеры-переклейки | 1921 |

|

SU1993A1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1990 |

|

RU2040855C1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК | 1996 |

|

RU2103815C1 |

| US 4686483 A, 11.08.1987 | |||

| Способ стерилизации емкостей | 1973 |

|

SU494161A1 |

Авторы

Даты

2001-09-27—Публикация

2000-04-07—Подача