Предлагаемое изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении высоконадежных резервированных устройств и систем, содержащих блоки с число-импульсным выходом (датчики угловой скорости, акселерометры и т.д), где требуется мажоритарный выбор «среднего» число-импульсного сигнала.

Известно устройство для мажоритарного выбора сигналов [1], содержащее резервируемые блоки, мажоритарный элемент, в каждом канале реверсивный счетчик, элементы ИЛИ, элементы И, элементы И-НЕ, инверторы, элемент сравнения, элемент задержки.

Недостаток этого устройства состоит в сложности реализации и низкой надежности.

Наиболее близким решением к предлагаемому является устройство для мажоритарного выбора сигналов [2], содержащее мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, вычитающий вход которого соединен с входом канала, выход m-го разряда реверсивного счетчика соединен с соответствующим входом мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала.

Недостаток известного решения [2] состоит в том, что при возможном отказе блока с число-импульсным выходом система не имеет информации об отказавшем блоке и о моменте, когда информация с выхода устройства для мажоритарного выбора сигнала становится недостоверной. Этот момент наступает в случае отказа (n+1)/2 блоков с число-импульсным выходом. В резервированных троированных системах, что обычно имеет место, при отказе второго канала информация в систему поступает недостоверной, система теряет управление, что недопустимо.

Задача изобретения - расширение функциональных возможностей устройства за счет формирования сигналов неисправности каждого канала (блока с число-импульсным выходом) и сигнала неисправности устройства и как следствие, увеличение надежности резервированных устройств и систем.

В первом варианте эта задача достигается тем, что в устройство для мажоритарного выбора сигналов, содержащее мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, вычитающий вход которого соединен с входом канала, выход m-го разряда реверсивного счетчика соединен с соответствующим входом мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала, дополнительно введены делитель частоты, счетчик импульсов, коммутатор, элемент задержки и генератор импульсов, в каждый канал устройства дополнительно введены элемент выделения модуля числа, ключ, цифровой коммутатор, триггер и элемент ИЛИ, выход которого соединен с R-входом реверсивного счетчика, шина кодового состояния которого подключена к элементу выделения модуля числа, соединенного своим выходом с входом ключа, выход которого соединен с шиной В цифрового компаратора, его выход В>А соединен с S-входом триггера, выход которого соединен с выходом неисправности канала и первым входом элемента ИЛИ, при этом выход генератора импульсов соединен с входами управления ключей каждого канала, входом управления коммутатора и входом элемента задержки, выход которого соединен с вторыми входами элемента ИЛИ каждого канала и R-входом счетчика импульсов, С-вход которого соединен с выходом делителя частоты, подключенного своим входом к выходу мажоритарного элемента, выход кодового состояния счетчика импульсов соединен с входом коммутатора, выход которого соединен с шиной А цифрового компаратора всех каналов.

Во втором варианте эта задача достигается тем, что в устройство для мажоритарного выбора сигналов, содержащее первый мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, вычитающий вход которого соединен с входом канала, выход m-го разряда реверсивного счетчика соединен с соответствующим входом первого мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала, дополнительно введены второй мажоритарный элемент, задатчик цифрового кода и генератор импульсов, в каждый канал устройства дополнительно введены элемент выделения модуля числа, цифровой коммутатор, триггер и элемент ИЛИ, выход которого соединен с R-входом реверсивного счетчика, шина кодового состояния которого подключена к элементу выделения модуля числа, выход которого соединен с шиной В цифрового компаратора, его выход В>А0 соединен с S-входом триггера, выход которого соединен с соответствующим входом второго мажоритарного элемента, выходом неисправности канала и первым входом элемента ИЛИ, при этом выход генератора импульсов соединен с вторыми входами элемента ИЛИ каждого канала, выход задатчика цифрового кода соединен с шиной А цифрового компаратора всех каналов, а выход второго мажоритарного элемента соединен с выходом неисправности устройства.

В третьем варианте эта задача достигается тем, что в устройство для мажоритарного выбора сигналов, содержащее мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, выход m-го разряда которого соединен с соответствующим входом мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала, дополнительно введены счетчик импульсов, задатчик цифрового кода, элемент ИЛИ и генератор импульсов, в каждый канал устройства дополнительно введены мультиплексор, элемент выделения модуля числа, цифровой компаратор, элемент задержки, коммутатор и регистр, выходная шина которого соединена с шиной управления мультиплексора, выход которого соединен с вычитающим входом реверсивного счетчика, соединенного своей выходной шиной кодового состояния с входной шиной элемента выделения модуля числа, выход которого подключен к шине В цифрового компаратора, выход которого В>А0 соединен с входом элемента задержки, выходом неисправности канала и соответствующим входом элемента ИЛИ, выход элемента задержки соединен с управляющим входом коммутатора, выход которого соединен с входом регистра, подключенного своим выходом к входу управления мультиплексора, основной вход которого соединен с основным входом канала, а резервные r входов мультиплексора соединены с резервными входами канала, при этом выход элемента ИЛИ соединен с входом С счетчика импульсов, шина кодового состояния которого соединена с шиной неисправности устройства и входной шиной коммутатора каждого канала, выход генератора импульсов соединен с R-входом реверсивного счетчика каждого канала, а выходная шина задатчика цифрового кода соединена с шиной А цифрового компаратора всех каналов.

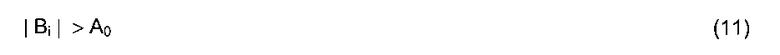

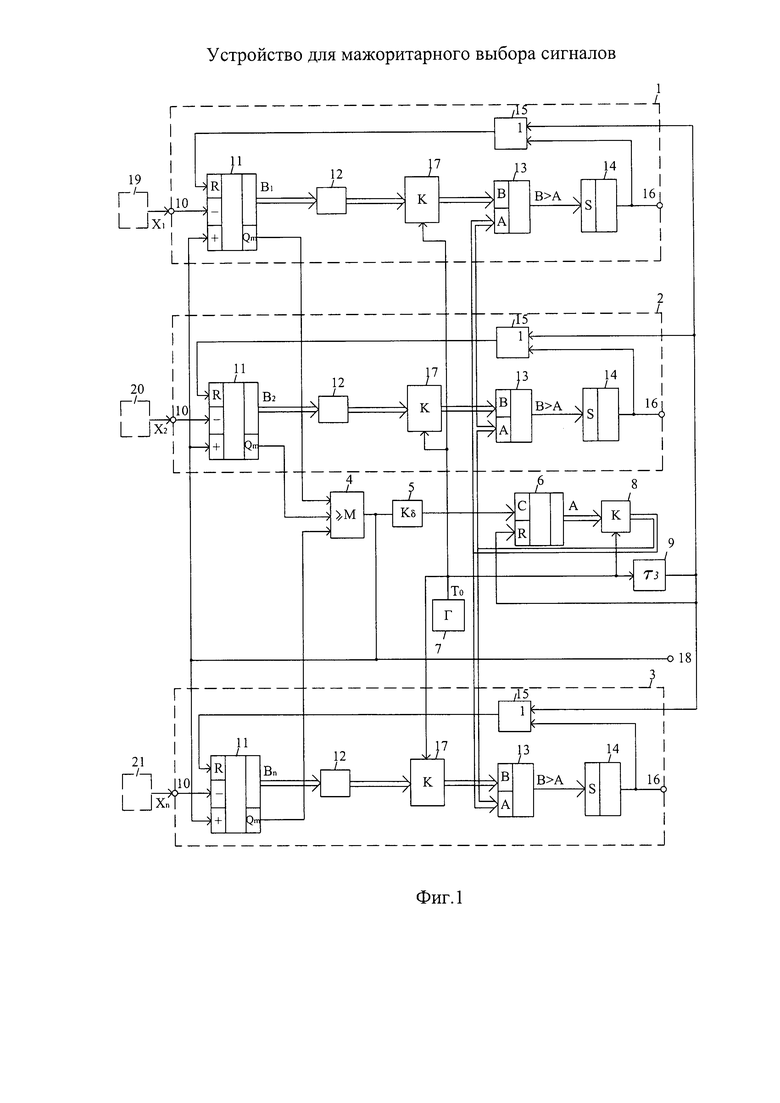

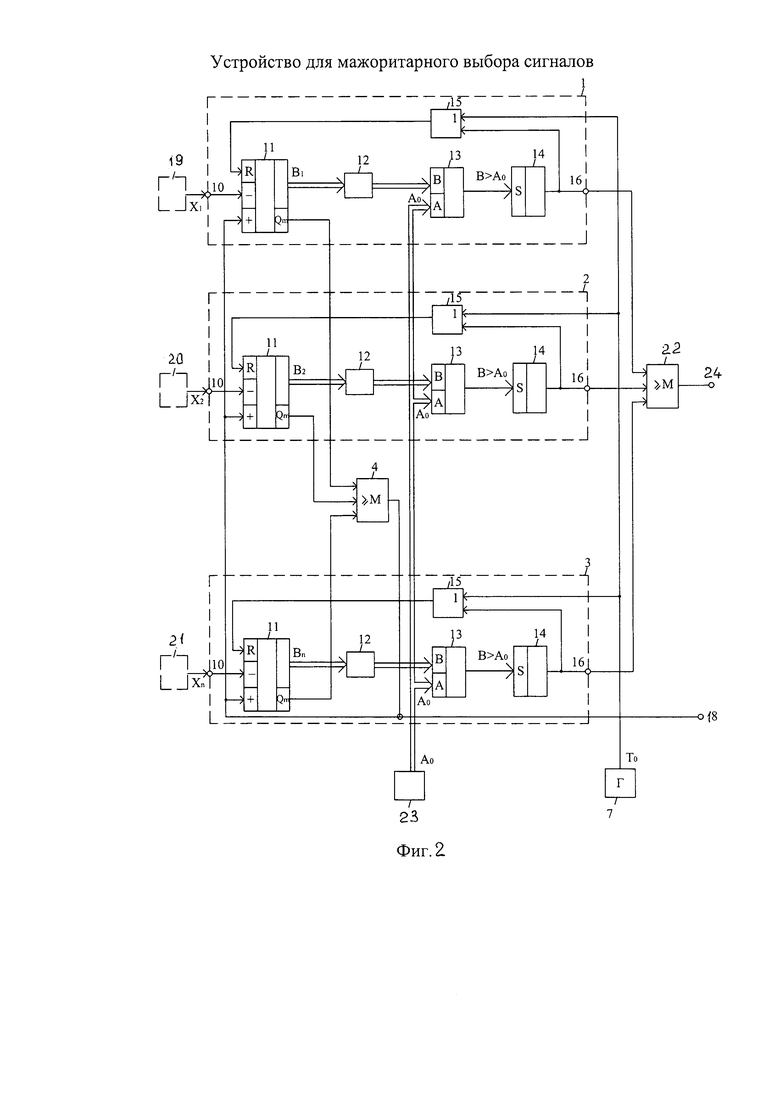

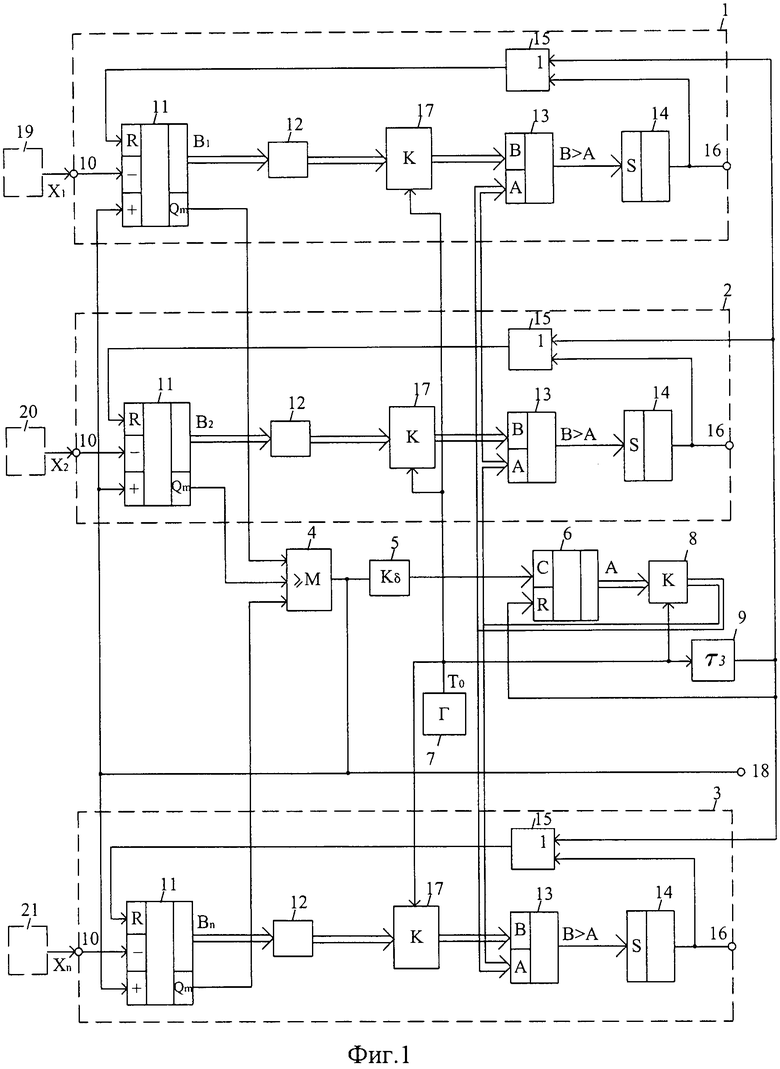

На фиг. 1 приведена блок-схема устройства для мажоритарного выбора сигналов первого варианта, на фиг. 2 приведена блок-схема устройства для мажоритарного выбора сигналов второго варианта, на фиг 3 приведена блок-схема устройства для мажоритарного выбора сигналов третьего варианта.

На схеме фиг. 1: 1, 2 и 3 - первый, второй и n-й каналы, 4 - мажоритарный элемент, 5 - делитель частоты, 6 - счетчик импульсов, 7 - генератор импульсов, 8 - коммутатор, 9 - элемент задержки. В каждом канале: 10 - вход канала, 11 - реверсивный счетчик, 12 - элемент выделения модуля числа, 13 - цифровой компаратор, 14 - триггер, 15 - элемент ИЛИ, 16 - выход неисправности канала, 17 - ключ, 18 - сигнальный выход. Показаны условно: 19, 20 и 21 - блоки с число-импульсным выходом.

В каждом канале вход 10 соединен с вычитающим входом реверсивного счетчика 11, шина кодового состояния которого подключена к элементу выделения модуля числа 12, выход которого соединен с входом ключа 17, соединенного своим выходом с шиной В цифрового компаратора 13. Выход В>А цифрового компаратора 13 соединен с S-входом триггера 14, выход которого соединен с выходом неисправности канала 16 и первым входом элемента ИЛИ 15. Выход элемента ИЛИ 15 соединен с R-входом реверсивного счетчика 11. Выход генератора импульсов 7 соединен с входами управления ключей 17 каждого канала, с входом управления коммутатора 8 и входом элемента задержки 9, выход которого соединен с вторыми входами элемента ИЛИ 15 каждого канала и R-входом счетчика импульсов 6. Выход кодового состояния счетчика импульсов 6 соединен с входом коммутатора 8, выход которого соединен с шиной А цифрового компаратора 13 всех каналов. Выход m-го разряда реверсивного счетчика 11 соединен с соответствующим входом мажоритарного элемента 4, выход которого соединен с сигнальным выходом устройства 18, с суммирующим входом реверсивного счетчика 11 каждого канала и с входом делителя частоты 5, выход которого соединен с С-входом счетчика импульсов 6.

На фиг. 2: 1, 2 и 3 - первый, второй и n-й каналы, 4 - первый мажоритарный элемент, 7 - генератор импульсов, 18 - сигнальный выход, 22 - второй мажоритарный элемент, 23 - задатчик цифрового кода, 24 - выход неисправности устройства. В каждом канале: 10 - вход канала, 11 - реверсивный счетчик, 12 - элемент выделения модуля числа, 13 - цифровой компаратор, 14 - триггер, 15 - элемент ИЛИ, 16 - выход неисправности канала. Показаны условно: 19, 20 и 21 - блоки с число-импульсным выходом.

В каждом канале вход 10 соединен с вычитающим входом реверсивного счетчика 11, шина кодового состояния которого подключена к элементу выделения модуля числа 12, выход которого соединен с шиной В цифрового компаратора 13. Выход В>А0 цифрового компаратора 13 соединен с S-входом триггера 14, выход которого соединен с соответствующим входом второго мажоритарного элемента 5, выходом неисправности канала 16 и первым входом элемента ИЛИ 15. Выход элемента ИЛИ 15 соединен с R-входом реверсивного счетчика 11. Выход генератора импульсов 7 соединен с вторым входом элемента ИЛИ 15 соответственно всех каналов, выход задатчика цифрового кода 23 соединен с шиной А цифрового компаратора 13 всех каналов, выход второго мажоритарного элемента 22 является выходом неисправности заявляемого устройства 24. Выход m-го разряда реверсивного счетчика 11 соединен с соответствующим входом первого мажоритарного элемента 4, выход которого соединен с сигнальным выходом устройства 18 и с суммирующим входом реверсивного счетчика 11 каждого канала.

На фиг. 3: 1, 2 и 3 - первый, второй и n-й каналы, 4 - мажоритарный элемент, 6 - счетчик импульсов, 7 - генератор импульсов, 15 - элемент ИЛИ, 18 - сигнальный выход, 23 - задатчик цифрового кода, 24 - шина неисправности устройства. В каждом канале: 8 - коммутатор, 10 - основной вход канала, 11 - реверсивный счетчик, 12 - элемент выделения модуля числа, 13 - цифровой компаратор, 16 - выход неисправности канала, 25 - мультиплексор, 26 - элемент задержки, 27 - регистр, 28, 29 - резервные входы канала. Показаны условно: 19, 20 и 21 - основные блоки с число-импульсным выходом, 30, 31 - резервные блоки с число-импульсным выходом.

В каждом канале основной вход мультиплексора 25 соединен с основным входом канала 10, резервные входы 28, 29 канала соединены с резервными входами мультиплексора 25, выход которого соединен с вычитающим входом реверсивного счетчика 11, выходная шина кодового состояния которого соединена с входной шиной элемента выделения модуля числа 12, подключенного своим выходом к шине В цифрового компаратора 13. Выход В>А0 цифрового компаратора 13 соединен с входом элемента задержки 26, выходом неисправности канала 16 и с соответствующим входом элемента ИЛИ 15. Выход элемента задержки 26 соединен с входом управления коммутатора 8, выход которого соединен с входом регистра 27, подключенного своим выходом к входу управления мультиплексора 25. Выход m-го разряда реверсивного счетчика 11 соединен с соответствующим входом мажоритарного элемента 4, выход которого соединен с сигнальным выходом устройства 18 и с суммирующим входом реверсивного счетчика 11 каждого канала. Выход генератора импульсов 7 соединен с R-входом реверсивного счетчика 11 всех каналов, выход задатчика цифрового кода 23 соединен с шиной А цифрового компаратора 13 каждого канала, выход элемента ИЛИ 15 соединен с входом С счетчика импульсов 6, выход которого соединен с шиной неисправности 24 и входной шиной коммутатора 8 каждого канала.

Устройство для мажоритарного выбора сигналов первого варианта фиг. 1 работает следующим образом. Входные сигналы Χ1, Х2, Xn поступают на входы 10 соответствующих каналов устройства. Для наглядности примем n=3. Считаем, что в начальный момент времени все реверсивные счетчики 11 и счетчик импульсов 6 находятся в нулевом состоянии, а логической единице соответствует высокий уровень сигнала. Входной импульс, например Χ1, поступая на вычитающий вход реверсивного счетчика 11 первого канала 1, переводит все его разряды в состояние "минус единица". В результате высокий уровень с его прямого выхода старшего разряда m поступит на соответствующий вход мажоритарного элемента 4.

После того как на любой другой вход устройства, например на вход 10 второго канала 2, поступит импульс Х2, он также будет воспринят реверсивным счетчиком 11 второго канала 2. Высокий уровень с прямого выхода его старшего разряда попадает на второй вход мажоритарного элемента 4. При наличии двух высоких уровней на входах мажоритарного элемента 4 на его выходе также появится высокий уровень, который поступает на суммирующий вход реверсивного счетчика 11 всех каналов и на сигнальный выход устройства 18.

В результате состояние всех реверсивных счетчиков увеличится на единицу: реверсивный счетчик 11 первого канала 1 и реверсивный счетчик 11 второго канала 2 будут обнулены, а реверсивный счетчик 11 третьего канала 3 перейдет в состояние "+1" (единица в младшем разряде). Если далее на вход 10 третьего канала 3 поступит импульс Х3, то в соответствии с приведенным описанием этот импульс проходит на вычитающий вход реверсивного счетчика 11 своего канала и переводит реверсивный счетчик 11 третьего канала 3 в нулевое состояние. В результате все реверсивные счетчики 11 приходят в исходное состояние.

Таким образом, устройство выбирает среднюю по частоте импульсов последовательность. Если, например, частота следования импульсов сигнала Χ1 равна f1, частота следования импульсов сигнала Х2 равна f2, частота следования импульсов сигнала Х3 равна f3, причем

то на сигнальном выходе 18 мажоритарного элемента 4 будут появляться импульсы со средней частотой f2.

Пусть на входы каналов поступают импульсы Χ1, Х2, Х3 с частотой следования в соответствии с (1). При длительном функционировании реверсивный счетчик 11 первого канала 1 будет «накапливать» отрицательное число, реверсивный счетчик 11 второго канала 2 будет находиться в нулевом состоянии, реверсивный счетчик 11 третьего канала 3 будет «накапливать» положительное число. За время Т0 модуль числа реверсивного счетчика 11 первого канала 1 будет равен

Модуль числа В3 реверсивного счетчика 11 третьего канала 3 за время Т0 будет равен

В системе управления блоки 19, 20 и 21 характеризуют один и тот же параметр, поэтому их выходные сигналы близки друг к другу и могут иметь допустимое расхождение. Если допустимое относительное расхождение сигналов Χ1, Х2, Х3 по частоте не должно превышать δ, то допустимое расхождение этих сигналов по числу импульсов А за время Т0 можно определить в виде

где fCP - средняя частота следования импульсов, в рассматриваемом случае это f2.

Если в процессе работы за время Т0 число |В1|, соответствующее кодовому состоянию реверсивного счетчика 11 первого канала 1, превысит число А, то это означает, что блок 19, выходной сигнал которого поступает на вход первого канала 1, имеет неисправность.

Генератор импульсов 7 каждый раз в моменты Т0 открывает ключи 17 всех каналов, подавая на шину В цифрового компаратора 13 модуль кодового состояния реверсивного счетчика 11 Bi, i=1, 2, …n. Этим же сигналом с генератора импульсов 7 открывается коммутатор 8, подавая на шину А цифрового компаратора 13 кодовое состояние А счетчика импульсов 6. В этот момент времени кодовое состояние А счетчика импульсов 6 будет определяться выражением (4), если делителю частоты 5 установить коэффициент деления Кδ согласно (5)

Если, например, допустимое относительное расхождение сигналов Χ1, Х2, Х3 по частоте не должно превышать значение δ=0,05 (5%), то согласно (5) коэффициент деления Кδ делителя частоты устанавливается равным 20. Цифровой компаратор 13 в каждом канале производит сравнение числа |Bi|, с числом А и, если

то выходной сигнал компаратора 13 i-го канала В>А поступает на вход 3 триггера 14 и устанавливает его в единичное состояние. Выходной сигнал триггера 14 этого канала поступает на первый вход элемента ИЛИ 15, выходной сигнал которого подается на R-вход реверсивного счетчика 11 и устанавливает его в нулевое состояние, отключая тем самым неисправно работающий блок от системы управления. По истечении времени задержки τ3 элемента задержки 9 производится обнуление реверсивных счетчиков 11 всех каналов и счетчика импульсов 6 выходным сигналом элемента задержки 9.

В рассматриваемом случае при выполнении условия (6) для первого канала (i=1) на выходе неисправности 16 первого канала 1 появляется сигнал, который блокирует неисправно работающий блок 19, проходя через элемент ИЛИ 15 на R-вход реверсивного счетчика 11. В результате реверсивный счетчик 15 устанавливается в нулевое состояние, поддерживается в этом состоянии и не реагирует на входные импульсы Χ1.

При дальнейшей работе при появлении неисправности, например, в третьем блоке 21 цифровой компаратор 13 третьего канала 3 фиксирует эту неисправность. В результате срабатывает триггер 14 третьего канала 3 и его выходной сигнал поступает на выход неисправности 16 этого канала и первый вход элемента ИЛИ 15, выходной сигнал которого блокирует поступление сигналов неисправно работающего блока 21 в систему управления установкой реверсивного счетчика 11 в нулевое состояние. При блокировке выходных сигналов двух блоков 19 и 21 из трех прекращается поступление сигналов в систему управления. По сигналу неисправности в двух каналах система может перейти на резервное управление.

Рассмотренное устройство расширяет функциональные возможности, так как фиксирует каждую неисправность, отключает от управления неисправный блок и при возникновении недопустимой (критической) неисправности отключает все блоки от управления и вырабатывает своевременные сигналы, по которым можно перейти на резервное управление. В рассматриваемом случае появление второго сигнала неисправности на выходе 16 является моментом отказа устройства. Этот сигнал позволяет подключить к управлению другое устройство. Так, при использовании троированного устройства при двух отказах система сохраняет свою работоспособность за счет формирования сигнала неисправности, который позволяет перейти на резервное управление и тем самым выполнить заданный режим. Надежность троированной системы, использующей предлагаемое устройство и сохраняющей свою работоспособность при двух отказах значительно выше надежности троированной системы, использующей известное устройство и рассчитанной на один отказ.

Устройство для мажоритарного выбора сигналов второго варианта фиг. 2 работает следующим образом. Входные сигналы Χ1, Х2, Xn поступают на входы 10 соответствующих каналов устройства. Для наглядности примем n=3. Считаем, что в начальный момент времени все реверсивные счетчики 11 находятся в нулевом состоянии, а логической единице соответствует высокий уровень сигнала. Входной импульс, например Χ1, поступая на вычитающий вход реверсивного счетчика 11 первого канала 1, переводит все его разряды в состояние "минус единица". В результате высокий уровень с его прямого выхода старшего разряда m поступит на соответствующий вход первого мажоритарного элемента 4.

После того как на любой другой вход устройства, например на вход 10 второго канала 2, поступит импульс Х2, он также будет воспринят реверсивным счетчиком 11 второго канала 2. Высокий уровень с прямого выхода его старшего разряда попадает на второй вход первого мажоритарного элемента 4. При наличии двух высоких уровней на входах первого мажоритарного элемента 4 на его выходе также появится высокий уровень, который поступает на суммирующий вход реверсивного счетчика 11 всех каналов и сигнальный выход устройства 18.

В результате состояние всех реверсивных счетчиков увеличится на единицу: реверсивный счетчик 11 первого канала 1 и реверсивный счетчик 11 второго канала 2 будут обнулены, а реверсивный счетчик 11 третьего канала 3 перейдет в состояние "+1" (единица в младшем разряде). Если далее на вход 10 третьего канала 3 поступит импульс Х3, то в соответствии с приведенным описанием этот импульс проходит на вычитающий вход реверсивного счетчика 11 своего канала и переводит реверсивный счетчик 11 третьего канала 3 в нулевое состояние. В результате все реверсивные счетчики 11 приходят в исходное состояние.

Таким образом, устройство выбирает среднюю по частоте импульсов последовательность. Если, например, частота следования импульсов сигнала Χ1 равна f1, частота следования импульсов сигнала Х2 равна f2, частота следования импульсов сигнала Х3 равна f3, причем

то на выходе 18 первого мажоритарного элемента 4 будут появляться импульсы с частотой f2.

Пусть на входы каналов поступают импульсы Χ1, Х2, Х3 с частотой следования в соответствии с (7). При длительном функционировании реверсивный счетчик 11 первого канала 1 будет «накапливать» отрицательное число, реверсивный счетчик 11 второго канала 2 будет находиться в нулевом состоянии, реверсивный счетчик 11 третьего канала 3 будет «накапливать» положительное число. За время Т0 модуль числа В1 реверсивного счетчика 11 первого канала 1 будет равен

Модуль числа В3 реверсивного счетчика 11 третьего канала 3 за время Т0 будет равен

В системе управления блоки 19, 20 и 21 характеризуют один и тот же параметр, поэтому их выходные сигналы близки друг к другу и могут иметь допустимое расхождение. Если допустимое относительное расхождение сигналов Χ1, Х2, Х3 по частоте не должно превышать δ, то допустимое расхождение этих сигналов по числу импульсов А0 за время Т0 можно определить в виде

где fмакс - возможная максимальная частота следования импульсов.

Если в процессе работы за время Т0 число |В1|, соответствующее кодовому состоянию реверсивного счетчика 11 первого канала 1, превысит число А0, то это означает, что блок 19, выходной сигнал которого поступает на вход первого канала 1, имеет неисправность.

Генератор импульсов 7 каждый раз в моменты Т0 обнуляет все реверсивные счетчики 11. На шину А цифрового компаратора 13 каждого канала поступает выходной сигнал с задатчика цифрового кода 23, соответствующий числу А0. Выходной сигнал (кодовое состояние) Bi i=1, 2, …n реверсивного счетчика 11 каждого канала поступает на вход элемента выделения модуля 12, выходной сигнал которого |Bi| подается на шину В цифрового компаратора 13. Цифровой компаратор 13 в каждом канале производит сравнение числа |Bi| с числом А0, и если

то выходной сигнал компаратора 13 i-го канала В>А0 поступает на вход S триггера 14 и устанавливает его в единичное состояние. Выходной сигнал триггера 14 этого канала поступает на соответствующий вход второго мажоритарного элемента 22 и первый вход элемента ИЛИ 15, выходной сигнал которого подается на R-вход реверсивного счетчика 11 и устанавливает его в нулевое состояние, отключая тем самым неисправно работающий блок от системы управления.

В рассматриваемом случае при выполнении условия (11) для первого канала (i=1) на выходе неисправности 16 первого канала 1 появляется сигнал, который блокирует неисправно работающий блок 19, проходя через элемент ИЛИ 15 на R-вход реверсивного счетчика 11.

При дальнейшей работе при появлении неисправности, например, в третьем блоке 21 цифровой компаратор 13 третьего канала 3 фиксирует эту неисправность. В результате срабатывает триггер 14 третьего канала 3 и его выходной сигнал поступает на выход неисправности 16 этого канала, соответствующий вход второго мажоритарного элемента 22 и первый вход элемента ИЛИ 15, выходной сигнал которого блокирует поступление сигналов неисправно работающего блока 21 в систему управления. На выходе 24 второго мажоритарного элемента 22 появляется сигнал неисправности устройства. При блокировке выходных сигналов двух блоков 19 и 21 из трех прекращается поступление сигналов в систему управления. По сигналу неисправности 24 система может перейти на резервное управление.

Рассмотренное устройство расширяет функциональные возможности, так как фиксирует каждую неисправность, отключает от управления неисправный блок и при возникновении недопустимой (критической) неисправности отключает все блоки от управления и вырабатывает своевременный сигнал, по которому можно перейти на резервное управление. Так, при использовании троированного устройства при двух отказах система сохраняет свою работоспособность за счет формирования сигнала неисправности, который позволяет перейти на резервное управление и тем самым выполнить заданный режим. Надежность троированной системы, использующей предлагаемое устройство и сохраняющей свою работоспособность при двух отказах значительно выше надежности троированной системы, использующей известное устройство и рассчитанной на один отказ.

Устройство для мажоритарного выбора сигналов третьего варианта работает следующим образом. Входные сигналы Χ1, Х2, Xn с выходов основных блоков с число-импульсным выходом 19, 20, 21 соответственно поступают на основные входы 10 соответствующих каналов устройства. Для наглядности примем n=3. Считаем, что в начальный момент времени все реверсивные счетчики 11, регистры 27 и счетчик импульсов 6 находятся в нулевом состоянии, а логической единице соответствует высокий уровень сигнала. Считаем, что при нулевом состоянии регистра 27 выход мультиплексора 25 подключен к его основному входу 10. Считаем также, что резервные блоки с число-импульсным выходом 30, 31 находятся в «горячем» состоянии.

Входной импульс, например Χ1, поступая на вход 10 мультиплексора 25, с его выхода подается на вычитающий вход реверсивного счетчика 11 первого канала 1 и переводит все его разряды в состояние "минус единица". В результате высокий уровень с его прямого выхода старшего разряда m поступит на соответствующий вход мажоритарного элемента 4. После того как на любой другой вход устройства, например на вход 10 второго канала 2, поступит импульс Х2, он также с выхода мультиплексора 25 будет воспринят реверсивным счетчиком 11 второго канала 2. Высокий уровень с прямого выхода его старшего разряда попадает на второй вход мажоритарного элемента 4. При наличии двух высоких уровней на входах мажоритарного элемента 4 на его выходе также появится высокий уровень, который поступает на суммирующий вход реверсивного счетчика 11 всех каналов и на сигнальный выход устройства 18.

В результате состояние всех реверсивных счетчиков увеличится на единицу: реверсивный счетчик 11 первого канала 1 и реверсивный счетчик 11 второго канала 2 будут обнулены, а реверсивный счетчик 11 третьего канала 3 перейдет в состояние "+1" (единица в младшем разряде). Если далее на вход 10 третьего канала 3 поступит импульс Х3, то в соответствии с приведенным описанием этот импульс проходит на вычитающий вход реверсивного счетчика 11 своего канала и переводит реверсивный счетчик 11 третьего канала 3 в нулевое состояние. В результате все реверсивные счетчики 11 приходят в исходное состояние.

Таким образом, устройство выбирает среднюю по частоте импульсов последовательность. Если, например, частота следования импульсов сигнала Χ1 равна f1, частота следования импульсов сигнала Х2 равна f2, частота следования импульсов сигнала Х3 равна f3, причем

то на сигнальном выходе 18 мажоритарного элемента 4 будут появляться импульсы с частотой f2.

Пусть на входы каналов поступают импульсы Χ1, Х2, Х3 с частотой следования в соответствии с (12). При длительном функционировании реверсивный счетчик 11 первого канала 1 будет «накапливать» отрицательное число, реверсивный счетчик 11 второго канала 2 будет находиться в нулевом состоянии, реверсивный счетчик 11 третьего канала 3 будет «накапливать» положительное число. За время Т0 модуль числа В1 реверсивного счетчика 11 первого канала 1 будет равен

Модуль числа В3 реверсивного счетчика 11 третьего канала 3 за время Т0 будет равен

В системе управления блоки 19, 20 и 21 (также и блоки 30, 31) характеризуют один и тот же параметр, поэтому их выходные сигналы близки друг к другу и могут иметь допустимое расхождение. Если допустимое относительное расхождение сигналов Χ1, Х2, Х3 (а также и сигналов XP1, XPm резервных блоков с число-импульсным выходом 30, 31) по частоте не должно превышать δ, то допустимое расхождение этих сигналов по числу импульсов А0 за время Т0 можно определить в виде

где fмакс - возможная максимальная частота следования импульсов.

Если в процессе работы за время Т0 число |В1|, соответствующее кодовому состоянию реверсивного счетчика 11 первого канала 1, превысит число А0, то это означает, что блок 19, выходной сигнал которого поступает на вход первого канала 1, имеет неисправность.

Генератор импульсов 7 каждый раз в моменты Т0 обнуляет все реверсивные счетчики 11. На шину А цифрового компаратора 13 каждого канала поступает выходной сигнал с задатчика цифрового кода 23, соответствующий числу А0. Выходной сигнал (кодовое состояние) Bi i=1, 2, …n реверсивного счетчика 11 каждого канала поступает на вход элемента выделения модуля 12, выходной сигнал которого |Bi| подается на шину В цифрового компаратора 13. Цифровой компаратор 13 в каждом канале производит сравнение числа |Bi| с числом А0, и если

то выходной сигнал компаратора 13 i-го канала В>А0 поступает на вход элемента задержки 26 и соответствующий вход элемента ИЛИ 15 и с его выхода на вход С счетчика импульсов 6, который изменяет свое состояние на плюс «единицу». В i-м канале выходной сигнал компаратора 13 В>А0, проходя через элемент задержки 26, открывает коммутатор 8, который устанавливает регистр 27 в состояние счетчика импульсов 6 (плюс «единица»), в результате чего в этом канале мультиплексор 25 подключает свой выход к резервному входу 28. Эта процедура означает отключение неисправного основного блока с число-импульсным выходом в канале i и подключение вместо него резервного исправного блока 30 с число-импульсным выходом ΧP1. Информация о неисправности формируется на выходе 16 канала и шине неисправности 24.

Пусть число резервных блоков с число-импульсным выходом равно r (r=2). Если при дальнейшей работе выходит из строя, например, блок 20 с число-импульсным выходом, то по описанной выше процедуре на выходе цифрового компаратора 13 второго канала формируется сигнал |В2|>А0, который поступает на вход элемента задержки 26 и соответствующий вход элемента ИЛИ 15 и с его выхода на вход С счетчика импульсов 6, который изменяет свое состояние еще на плюс «единицу», устанавливаясь в состояние «плюс два». Выходной сигнал компаратора 13 В>А0, проходя через элемент задержки 26, открывает коммутатор 8, который устанавливает регистр 27 в состояние счетчика импульсов 6 («плюс два»), в результате чего в этом канале мультиплексор 25 подключает свой выход к резервному входу 29. В результате отключается неисправный основной блок с число-импульсным выходом в канале 2 и подключается вместо него резервный блок 31 с число-импульсным выходом ХР2. Информация о неисправности формируется на выходе 16 второго канала и шине неисправности 24.

При дальнейшей работе при появлении неисправности, например, в третьем блоке с число-импульсным выходом 21 цифровой компаратор 13 третьего канала 3 фиксирует эту неисправность. В результате состояние счетчика импульсов 6 изменяется еще на «плюс единицу», а регистр 8 третьего канала устанавливается в состояние «плюс три», отключая тем самым неисправный блок с число-импульсным выходом 21. Информация о неисправности формируется на выходе 16 третьего канала и шине неисправности 24.

После фиксации трех отказов в трех блоках с число-импульсным выходом система продолжает работу с двумя исправными блоками с число-импульсным выходом, получая правильную информацию на сигнальном выходе 18. Если при дальнейшей работе происходит выход из строя одного из двух оставшихся исправных блоков с число-импульсным выходом, то устройство фиксирует и эту неисправность описанным выше способом. В результате счетчик импульсов 6 переходит в состояние «плюс четыре», отключается еще один из блоков с число-импульсным выходом, информация на сигнальном выходе 18 отсутствует, а информация на шине неисправности 24 свидетельствует о необходимости перехода на резервное управление.

Рассмотренное устройство повышает надежность системы и расширяет функциональные возможности, так как фиксирует каждую неисправность, отключает от управления неисправный блок и при возникновении недопустимой (критической) неисправности отключает все блоки от управления и вырабатывает своевременный сигнал, по которому можно перейти на резервное управление.

Оценим надежность предлагаемого решения. Пусть надежность блока с число-импульсным выходом равна р (р=0,9), вероятность отказа этого блока равна λ=1-р=0,1. Система, состоящая из трех основных и двух резервных блоков с число-импульсным выходом и использующая предлагаемое устройство для мажоритарного выбора, сохраняет свою работоспособность при отказах трех из пяти блоков с число-импульсным выходом. Надежность Р рассматриваемой системы в этом случае будет равна

В соответствии с (6) надежность Р=0,99954, вероятность отказа системы равна λ=1-Р=0,00046. Оценим надежность известной системы Р1, предполагая, что известное решение использует также пять блоков с число-импульсным выходом и мажоритарное устройство «три из пяти». Известное решение сохраняет работоспособность при отказе двух из пяти блоков с число-импульсным выходом. В этом случае надежность известной системы Р1 определяется в виде

В соответствии с (7) надежность Р1=0,99144, вероятность отказа известной системы равна λ1=1-Р1=0,00856. Вероятность отказа λ1 системы с известным устройством для мажоритарного выбора сигналов в 18,6 раза выше вероятности отказа λ системы с предлагаемым устройством для мажоритарного выбора сигналов (λ1/λ=0,00856/0,00046=18,6).

Предлагаемая совокупность признаков, в рассмотренных авторами решениях, не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения всех вариантов критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства можно использовать стандартные элементы: реверсивные счетчики, цифровые компараторы, логические микросхемы, мажоритарные элементы, элементы выделения модуля числа, триггеры, генераторы, элементы задержки, коммутаторы, счетчики импульсов.

Литература

1. Авторское свидетельство СССР №1215113, кл. G06F 11/18. Устройство для мажоритарного выбора асинхронных сигналов.

2. Патент Российской Федерации №2110835, кл. G06F 11/18, H05K 10/00, Устройство для мажоритарного выбора сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛОВ УПРАВЛЕНИЯ (2 ВАРИАНТА) | 2014 |

|

RU2580476C1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2401449C1 |

| Коммутатор для переключения резервных генераторов | 1988 |

|

SU1541763A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для контроля мажоритарных схем | 1977 |

|

SU705451A1 |

| Устройство для контроля мажоритарных блоков | 1981 |

|

SU1015389A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2012 |

|

RU2476923C1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408045C2 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408046C2 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

Изобретение относится к области построения высоконадежных резервированных устройств и систем. Технический результат заключается в повышении надежности за счет формирования сигналов неисправности каждого канала (блока с число-импульсным выходом) и интегрировании сигнала неисправности каждого канала, что позволяет отключать от управления неисправно работающие блоки и в критической ситуации (при многочисленных отказах) своевременно формировать сигнал на переход на резервное управление. 3 н.п. ф-лы, 3 ил.

1. Устройство для мажоритарного выбора сигналов, содержащее мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, вычитающий вход которого соединен с входом канала, выход m-го разряда реверсивного счетчика соединен с соответствующим входом мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала, отличающееся тем, что в устройство дополнительно введены делитель частоты, счетчик импульсов, коммутатор, элемент задержки и генератор импульсов, в каждый канал устройства дополнительно введены элемент выделения модуля числа, ключ, цифровой коммутатор, триггер и элемент ИЛИ, выход которого соединен с R-входом реверсивного счетчика, шина кодового состояния которого подключена к элементу выделения модуля числа, соединенного своим выходом с входом ключа, выход которого соединен с шиной В цифрового компаратора, его выход B>A соединен с S-входом триггера, выход которого соединен с выходом неисправности канала и первым входом элемента ИЛИ, при этом выход генератора импульсов соединен с входами управления ключей каждого канала, входом управления коммутатора и входом элемента задержки, выход которого соединен с вторыми входами элемента ИЛИ каждого канала и R-входом счетчика импульсов, C-вход которого соединен с выходом делителя частоты, подключенного своим входом к выходу мажоритарного элемента, выход кодового состояния счетчика импульсов соединен с входом коммутатора, выход которого соединен с шиной A цифрового компаратора всех каналов.

2. Устройство для мажоритарного выбора сигналов, содержащее первый мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, вычитающий вход которого соединен с входом канала, выход m-го разряда реверсивного счетчика соединен с соответствующим входом первого мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала, отличающееся тем, что в устройство дополнительно введены второй мажоритарный элемент, задатчик цифрового кода и генератор импульсов, а в каждый канал устройства дополнительно введены элемент выделения модуля числа, цифровой коммутатор, триггер и элемент ИЛИ, выход которого соединен с R-входом реверсивного счетчика, шина кодового состояния которого подключена к элементу выделения модуля числа, выход которого соединен с шиной B цифрового компаратора, его выход B>A0 соединен с S-входом триггера, выход которого соединен с соответствующим входом второго мажоритарного элемента, выходом неисправности канала и первым входом элемента ИЛИ, при этом выход генератора импульсов соединен с вторыми входами элемента ИЛИ каждого канала, выход задатчика цифрового кода соединен с шиной A цифрового компаратора всех каналов, а выход второго мажоритарного элемента соединен с выходом неисправности устройства.

3. Устройство для мажоритарного выбора сигналов, содержащее мажоритарный элемент и n каналов, каждый из которых включает m-разрядный реверсивный счетчик, выход m-го разряда которого соединен с соответствующим входом мажоритарного элемента, выход которого соединен с сигнальным выходом устройства и с суммирующим входом реверсивного счетчика каждого канала, отличающееся тем, что в устройство дополнительно введены счетчик импульсов, задатчик цифрового кода, элемент ИЛИ и генератор импульсов, а в каждый канал устройства дополнительно введены мультиплексор, элемент выделения модуля числа, цифровой компаратор, элемент задержки, коммутатор и регистр, выходная шина которого соединена с шиной управления мультиплексора, выход которого соединен с вычитающим входом реверсивного счетчика, соединенного своей выходной шиной кодового состояния с входной шиной элемента выделения модуля числа, выход которого подключен к шине B цифрового компаратора, выход которого B>A0 соединен с входом элемента задержки, выходом неисправности канала и соответствующим входом элемента ИЛИ, выход элемента задержки соединен с управляющим входом коммутатора, выход которого соединен с входом регистра, подключенного своим выходом к входу управления мультиплексора, основной вход которого соединен с основным входом канала, а резервные r входов мультиплексора соединены с резервными входами канала, при этом выход элемента ИЛИ соединен с входом C счетчика импульсов, шина кодового состояния которого соединена с шиной неисправности устройства и входной шиной коммутатора каждого канала, выход генератора импульсов соединен с R-входом реверсивного счетчика каждого канала, а выходная шина задатчика цифрового кода соединена с шиной A цифрового компаратора всех каналов.

| ТЕПЛОНОСИТЕЛЬ | 1991 |

|

RU2010835C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| US 4562575, 31.12.1985. | |||

Авторы

Даты

2016-04-10—Публикация

2014-06-27—Подача