Изобретение относится к многопараметровому неразрушающему электромагнитному контролю физико-механических свойств материалов и может быть использовано для измерения амплитудно-частотных и фазочастотных характеристик четырехполюсников.

Известно устройство, содержащее блок питания, выполненный в виде последовательно соединенных генератора прямоугольных импульсов фиксированной частоты, управляемого делителя частоты, счетчика, преобразователя на основе функций Уолша и фильтра низких частот; последовательно соединенные управляемый усилитель мощности, датчики, буферный усилитель; последовательно соединенные преобразователь фаза-напряжение и аналоговый ключ, а также последовательно соединенные преобразователь переменного напряжения в постоянное и второй аналоговый ключ, микропроцессор и цифровой индикатор (а.с. СССР N 1000896, кл. G 01 N 27/90, опубл. 28.02.83, бюл. N 8).

Недостатком устройства является низкое быстродействие, обусловленное инерционностью сглаживающих фильтров, входящих в состав преобразователя переменного напряжения в постоянное и преобразователя фаза-напряжение.

Наиболее близким к предлагаемому устройству является устройство, содержащее последовательно соединенные генератор прямоугольных импульсов фиксированной частоты, управляемый делитель частоты, счетчик, формирователь синусоидального напряжения, усилитель мощности, коммутатор, вихретоковый преобразователь, буферный усилитель, последовательно соединенные микропроцессор и устройство отображения, а также цифровой фазорасщепитель, синхронный детектор и интегрирующий преобразователь напряжения во временной интервал (а.с. СССР N 1100558, кл. G 01 N 27/90, опубл. 30.06.84, бюл. N 24).

Недостатком прототипа является невысокая точность измерений. Прототип содержит последовательно соединенные синхронный детектор и интегрирующий преобразователь напряжения во временной интервал. Основным узлом интегрирующих преобразователей напряжения во временной интервал является интегратор, который строится, как правило, на базе операционных усилителей (одного или нескольких). Недостатком операционных усилителей является ограниченная полоса пропускания и ограниченная скорость изменения выходного напряжения. В то же время сигнал на выходе синхронного детектора в общем случае будет иметь крутые фронты с высокой скоростью изменения напряжения, поскольку моменты переключения синхронного детектора в общем случае не совпадают с моментами перехода синусоидального входного напряжения синхронного детектора через ноль. Максимальная скорость изменения напряжения на выходе синхронного детектора определяется параметрами синхронного детектора и амплитудой синусоидального входного напряжения синхронного детектора. Если скорость изменения выходного напряжения синхронного детектора превышает максимальную скорость изменения выходного напряжения операционного усилителя интегратора интегрирующего преобразователя напряжения во временной интервал, то операционный усилитель перегружается и погрешность преобразования напряжения во временной интервал растет; соответственно растет погрешность измерения.

Технической задачей изобретения является повышение точности измерений при сохранении высокой производительности, которая определяется малым временем измерений.

Техническая задача решается тем, что электромагнитный многочастотный структуроскоп (далее в тексте - структуроскоп), содержащий последовательно соединенные генератор прямоугольных импульсов фиксированной частоты, управляемый делитель частоты, счетчик, формирователь синусоидального напряжения, усилитель мощности, вихретоковый преобразователь, коммутатор, синхронный детектор, а также интегрирующий преобразователь напряжения во временной интервал, цифровой фазорасщепитель, последовательно соединенные микропроцессор и устройство отображения, снабжен фильтром низкой частоты с малой постоянной времени и схемой синхронизации, причем выход синхронного детектора соединен со входом фильтра низкой частоты с малой постоянной времени, а выход фильтра низкой частоты с малой постоянной времени соединен со входом интегрирующего преобразователя напряжения во временной интервал, входы схемы синхронизации соединены соответственно с выходами цифрового фазорасщепителя и микропроцессора, а выход схемы синхронизации соединен со входом управления интегрирующего преобразователя напряжения во временной интервал, один из выходов микропроцессора подключен ко вторым входам управляемого делителя частоты, два входа коммутатора подключены соответственно к выходам усилителя мощности и вихретокового преобразователя, третий вход коммутатора подключен к микропроцессору, а выход коммутатора подключен к первому (сигнальному) входу синхронного детектора, первый вход цифрового фазорасщепителя соединен с дополнительным выходом счетчика, второй вход цифрового фазорасщепителя соединен с выходом микропроцессора, выход цифрового фазорасщепителя соединен со вторым (опорным) входом синхронного детектора, выход интегрирующего преобразователя напряжения во временной интервал соединен с микропроцессором.

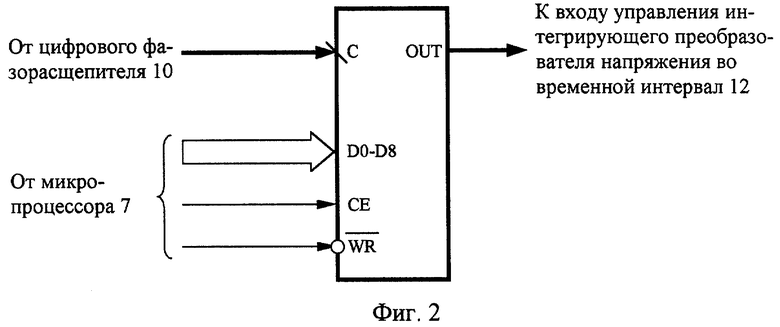

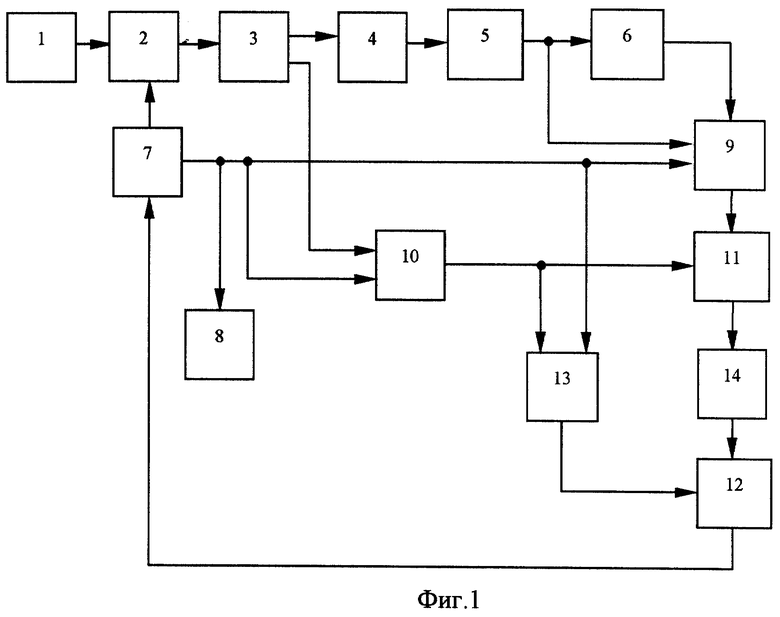

Сущность изобретения поясняется чертежами, где на фиг.1 представлена блок-схема структуроскопа, а на фиг.2 представлена структурно-функциональная схема схемы синхронизации на базе интегральной микросхемы программируемого таймера КР580ВИ53.

Структуроскоп содержит последовательно соединенные генератор прямоугольных импульсов фиксированной частоты 1, управляемый делитель частоты 2, счетчик 3, формирователь синусоидального напряжения 4, усилитель мощности 5, вихретоковый преобразователь 6, коммутатор 9; а также цифровой фазорасщепитель 10, схему синхронизации 13, синхронный детектор 11, фильтр низкой частоты с малой постоянной времени 14, интегрирующий преобразователь напряжения во временной интервал 12, последовательно соединенные микропроцессор 7 и устройство отображения 8.

Структуроскоп работает следующим образом. Последовательность прямоугольных импульсов фиксированной частоты с выхода генератора прямоугольных импульсов фиксированной частоты 1 поступает на вход управляемого делителя частоты 2. Коэффициент деления частоты управляемого делителя частоты 2 устанавливается микропроцессором 7. Частота импульсов на выходе управляемого делителя частоты 2, таким образом, определяется частотой прямоугольных импульсов, генерируемых генератором прямоугольных импульсов фиксированной частоты 1 и коэффициентом деления частоты управляемого делителя частоты 2, устанавливаемым микропроцессором 7. С выхода управляемого делителя частоты 2 последовательность импульсов поступает на вход счетчика 3, преобразующего последовательность импульсов в параллельный код. С выходов счетчика 3 кодовые комбинации поступают на входы формирователя синусоидального напряжения 4, преобразующего последовательность выходных кодовых комбинаций счетчика 3 в аналоговый синусоидальный сигнал (синусоидальное напряжение). С дополнительного выхода счетчика 3 импульсы, частота которых в 4 раза превышает частоту формируемого синусоидального сигнала (синусоидального напряжения), поступают на вход цифрового фазорасщепителя 10. Цифровой фазорасщепитель 10 формирует последовательность прямоугольных импульсов, частота которых равна частоте синусоидального сигнала, формируемого формирователем синусоидального напряжения 4. Фаза этой последовательности (0 или 90o) устанавливается микропроцессором 7. Выходное напряжение формирователя синусоидального напряжения 4 усиливается усилителем мощности 5 и поступает на вход (т.е. на обмотку возбуждения) вихретокового преобразователя 6, а также на вход коммутатора 9. На второй вход коммутатора 9 поступает сигнал с выхода вихретокового преобразователя 6. Коммутатор 9 пропускает на первый (сигнальный) вход синхронного детектора 11 напряжение либо с выхода, либо со входа вихретокового преобразователя 6, что определяется микропроцессором 7, управляющим коммутатором 9. На второй (опорный) вход синхронного детектора 11 поступает последовательность прямоугольных импульсов с выхода цифрового фазорасщепителя 10; фаза этой последовательности (0 или 90o) устанавливается микропроцессором 7. Синхронный детектор 11 осуществляет синхронное детектирование выходного сигнала коммутатора 9. Фильтр низкой частоты с малой постоянной времени 14 подавляет высокочастотные составляющие спектра выходного сигнала синхронного детектора 11 и уменьшает максимальную скорость изменения входного сигнала интегрирующего преобразователя напряжения во временной интервал 12. Тем самым предотвращается перегрузка и выход из рабочего режима интегрирующего преобразователя напряжения во временной интервал 12, а следовательно, уменьшается обусловленная перегрузкой интегрирующего преобразователя напряжения во временной интервал 12 погрешность. Время установления выходного напряжения фильтра низкой частоты с малой постоянной времени 14 мало и не увеличивает время измерения (т.е. не снижает быстродействия структуроскопа). Схема синхронизации 13 синхронизирует работу синхронного детектора 11 и интегрирующего преобразователя напряжения во временной интервал 12 таким образом, что начало и окончание процесса интегрирования совпадают с фронтом очередного импульса управления синхронным детектором 11, генерируемого цифровым фазорасщепителем 10. При этом время измерения устанавливается схемой синхронизации 13 равным целому числу периодов входного сигнала интегрирующего преобразователя напряжения во временной интервал 12 (и целому числу периодов последовательности прямоугольных импульсов, генерируемых цифровым фазорасщепителем 10). Тем самым обеспечивается измерение среднего за период значения входного напряжения интегрирующего преобразователя напряжения во временной интервал 12. В противном случае, если длительность процесса интегрирования входного напряжения интегрирующего преобразователя напряжения во временной интервал 12 не равна целому числу периодов входного напряжения интегрирующего преобразователя напряжения во временной интервал 12, возникает погрешность измерения среднего за период значения входного напряжения интегрирующего преобразователя напряжения во временной интервал 12. На вход интегрирующего преобразователя напряжения во временной интервал 12 поступают импульсы с частотой синусоидального сигнала возбуждения вихретокового преобразователя 6, генерируемого формирователем синусоидального напряжения 4 и поступающего на вход вихретокового преобразователя 6 через усилитель мощности 5. В случае, если длительность процесса интегрирования не равна целому числу периодов входного сигнала интегрирующего преобразователя напряжения во временной интервал 12, происходит интегрирование некоторого числа целых импульсов, поступающих на вход интегрирующего преобразователя напряжения во временной интервал 12, и части импульса (т.е. неполного импульса). Именно вследствие интегрирования части импульса возникает погрешность измерения среднего за период значения входного напряжения интегрирующего преобразователя напряжения во временной интервал 12: результат измерения отличается от среднего за период значения входного напряжения интегрирующего преобразователя напряжения во временной интервал 12 на величину, которая зависит от длительности и формы проинтегрированной части импульса (т.е. неполного импульса), числа проинтегрированных целых входных импульсов интегрирующего преобразователя напряжения во временной интервал 12 и т.д. Схема синхронизации 13 устраняет данную погрешность, поскольку устанавливает длительность процесса интегрирования равной целому числу периодов входного сигнала интегрирующего преобразователя напряжения во временной интервал 12. Тем самым устраняется необходимость снижения указанной погрешности путем увеличения длительности процесса интегрирования, когда число проинтегрированных входных импульсов интегрирующего преобразователя напряжения во временной интервал 12 велико, и погрешность, вносимая интегрированием части импульса (т.е. неполного импульса), относительно мала. Схема синхронизации 13 позволяет тем самым уменьшить число интегрируемых входных импульсов интегрирующего преобразователя напряжения во временной интервал 12, сократив тем самым время измерения и повысив быстродействие структуроскопа (т.е. схема синхронизации 13 позволяет сократить число периодов входного сигнала интегрирующего преобразователя напряжения во временной интервал 12, в течение которых производится интегрирование). Формируя интервал интегрирования входного сигнала интегрирующего преобразователя напряжения во временной интервал 12, схема синхронизации 13 обеспечивает путем варьирования длительности интервала интегрирования входного сигнала интегрирующего преобразователя напряжения во временной интервал 12 изменение коэффициента передачи измерительного тракта структуроскопа, включающего коммутатор 9, синхронный детектор 11, фильтр низкой частоты с малой постоянной времени 14, интегрирующий преобразователь напряжения во временной интервал 12 и схему синхронизации 13. Управление коэффициентом передачи измерительного тракта структуроскопа осуществляется микропроцессором 7, устанавливающим соответствующий код на входах схемы синхронизации 13, соединенных с микропроцессором 7.

Схема синхронизации 13 может быть реализована на базе интегральной микросхемы программируемого таймера (например, КР580ВИ53 или аналогичного). При этом на счетный вход программируемого таймера КР580ВИ53 подаются импульсы, генерируемые цифровым фазорасщепителем 10, выход программируемого таймера соединяется со входом управления интегрирующего преобразователя напряжения во временной интервал 12; время измерения задается микропроцессором 7 путем программирования программируемого таймера на соответствующую длительность выходного импульса, которая задается микропроцессором 7 в количестве импульсов, генерируемых цифровым фазорасщепителем 10. Естественно, программируемый таймер вносит определенную задержку в распространение сигнала: фронт выходного импульса программируемого таймера сдвинут относительно фронта очередного импульса, поступившего на счетный вход канала программируемого таймера с выхода цифрового фазорасщепителя 10, на некоторый временной интервал, длительность которого определяется параметрами микросхемы программируемого таймера. Вследствие этого моменты начала и окончания процесса интегрирования не будут точно совпадать с фронтами сигнала управления синхронным детектором 11, который генерируется цифровым фазорасщепителем 10 и поступает также на вход схемы синхронизации 13, т.е. в данном случае - на счетный вход канала программируемого таймера. Однако временной сдвиг начала и окончания процесса интегрирования не играет роли (не влияет на точность измерения) и может варьироваться в весьма широких пределах при условии, что задержка начала процесса измерения по отношению к фронту очередного импульса, поступившего с выхода цифрового фазорасщепителя 10, равна задержке окончания процесса измерения по отношению к фронту очередного импульса, поступившего с выхода цифрового фазорасщепителя 10. Важно соблюдение равенства длительности процесса интегрирования целому числу периодов входного сигнала интегрирующего преобразователя напряжения во временной интервал 12, а это условие выполняется с достаточной точностью. В случае построения схемы синхронизации на базе одного канала программируемого таймера КР580ВИ53 последний следует запрограммировать для работы в режиме ждущего мультивибратора. В этом режиме канал программируемого таймера КР580ВИ53 обеспечивает формирование импульсов низкого уровня, длительность которых составляет t = n • Тc, где Тc - период импульсов, генерируемых цифровым фазорасщепителем 10, которые подаются на счетный вход канала программируемого таймера и на второй (опорный) вход синхронного детектора 11. Минимальное значение n для режима ждущего мультивибратора равно 1, а максимальное (в режиме двухбайтового счета для одного канала программируемого таймера) - 65535. При необходимости получения большего интервала интегрирования возможно последовательное включение двух или трех каналов программируемого таймера. Максимальная длительность интервала интегрирования в этом случае составляет около 2,7•1014 выходных импульсов цифрового фазорасщепителя 10 (для последовательного соединения трех каналов программируемого таймера в режиме двухбайтового счета), что позволяет варьировать длительность процесса интегрирования (а значит, и коэффициент передачи измерительного тракта структуроскопа) в весьма широких пределах.

Отсчет времени интегрирования схемой синхронизации 13 начинается по фронту импульса разрешения счета, поступающего на вход разрешения счета программируемого таймера с выхода микропроцессора 7. При этом минимальная длительность импульса разрешения счета ограничена техническими параметрами микросхемы программируемого таймера.

Система "микропроцессор - программируемый интегральный таймер КР580ВИ53" работает следующим образом: в ходе процедуры инициализации структуроскопа микропроцессор 7 программирует таймер КР580ВИ53, устанавливая режим работы канала (или каналов, если последовательно включены два или три канала) программируемого таймера. Предположим для определенности, что для построения схемы синхронизации 13 используется только один канал программируемого таймера. Для формирования нужного интервала интегрирования в счетчик канала программируемого таймера микропроцессором 7 загружаются коды, определяющие длительность процесса интегрирования в количестве импульсов, генерируемых цифровым фазорасщепителем 10 и поступающих на счетный вход канала программируемого таймера и на второй (опорный) вход синхронного детектора 11. Начало процесса интегрирования инициируется микропроцессором 7 путем подачи на вход разрешения счета канала программируемого таймера импульса высокого уровня. Согласно техническим данным интегральной микросхемы программируемого таймера КР580ВИ53, начало выходного импульса канала программируемого таймера (начало отсчета и, соответственно, начало процесса интегрирования) соответствует спаду очередного импульса, поступившего на счетный вход канала программируемого таймера, т. е. в данном случае - очередного импульса, поступившего с выхода цифрового фазорасщепителя 10. Фронт выходного импульса канала программируемого таймера (окончание отсчета каналом программируемого таймера интервала интегрирования и окончание процесса интегрирования) также соответствует спаду очередного импульса, поступившего на счетный вход канала программируемого таймера с выхода цифрового фазорасщепителя 10. Таким образом, обеспечивается синхронизация работы синхронного детектора 11 и интегрирующего преобразователя напряжения во временной интервал 12. Пример построения схемы синхронизации 13 на базе микросхемы интегрального программируемого таймера КР580ВИ53 приведен на фиг. 2, где для построения схемы синхронизации 13 используется один канал программируемого таймера (при необходимости получения больших интервалов интегрирования последовательно могут быть включены два или три канала программируемого таймера).

Помимо микросхемы программируемого таймера КР580ВИ53 для построения схемы синхронизации могут также использоваться ее полные или приближенные аналоги отечественного или зарубежного производства (например, КР1810ВИ54 отечественного производства, i8253, i8254 фирмы Intel и аналоги перечисленных микросхем). При этом схема включения при необходимости должна быть скорректирована в соответствии с параметрами конкретной интегральной микросхемы.

Временной интервал, полученный с помощью интегрирующего преобразователя напряжения во временной интервал 12, преобразуется в код микропроцессором 7. На устройство отображения 8 микропроцессором 7 выдаются результаты измерения квадратурных составляющих синусоидального сигнала, снимаемого с выхода вихретокового преобразователя 6, или значения контролируемых параметров, рассчитанных микропроцессором 7 по заданной математической модели неразрушающего контроля, которая представляет собой функцию от значений квадратурных составляющих выходного сигнала вихретокового преобразователя 6 на различных частотах сигнала возбуждения вихретокового преобразователя 6, поступающего на вихретоковый преобразователь 6 с формирователя синусоидального напряжения 4 через усилитель мощности 5.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электромагнитный многочастотный структуроскоп | 1983 |

|

SU1100558A1 |

| УСТРОЙСТВО ДЛЯ АКУСТИЧЕСКОГО КОНТРОЛЯ ЗА СОСТОЯНИЕМ ПЧЕЛИНОЙ СЕМЬИ | 1996 |

|

RU2099942C1 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА К ЭЛЕКТРОМАГНИТНОМУ МНОГОЧАСТОТНОМУ СТРУКТУРОСКОПУ | 1999 |

|

RU2178945C2 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА | 1999 |

|

RU2156027C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ДЕВИАЦИИ ЧАСТОТЫ | 1997 |

|

RU2126587C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ФИЗИЧЕСКОЙ ВЕЛИЧИНЫ | 1999 |

|

RU2162592C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДЛЯ НАБЛЮДЕНИЯ И СОДЕРЖАНИЯ ПЧЕЛИНЫХ СЕМЕЙ | 1995 |

|

RU2096952C1 |

| КОГЕРЕНТНО-ОПТИЧЕСКИЙ СПЕКТРОАНАЛИЗАТОР ИЗОБРАЖЕНИЙ | 1996 |

|

RU2098857C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ МНОГОЭЛЕМЕНТНЫХ ДВУХПОЛЮСНЫХ ЦЕПЕЙ | 2001 |

|

RU2212677C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1998 |

|

RU2138828C1 |

Изобретение относится к многопараметровому неразрушающему электромагнитному контролю физико-механических свойств материалов и может быть использовано для измерения амплитудно-частотных и фазочастотных характеристик четырехполюсников. Техническое решение заключается во введении схемы синхронизации и фильтра низкой частоты с малой постоянной времени. Фильтр низкой частоты с малой постоянной времени подавляет высокочастотные составляющие спектра выходного сигнала синхронного детектора и уменьшает максимальную скорость изменения входного сигнала интегрирующего преобразователя напряжения во временной интервал. Тем самым устраняется погрешность измерения из-за перегрузки интегрирующего преобразователя. Длительность процесса интегрирования задается микропроцессором и устанавливается схемой синхронизации, равной целому числу периодов входного сигнала интегрирующего преобразователя напряжения во временной интервал. Тем самым устраняется необходимость снижения погрешности преобразования путем увеличения времени интегрирования. 2 ил.

Электромагнитный многочастотный структуроскоп, содержащий последовательно соединенные генератор прямоугольных импульсов фиксированной частоты, управляемый делитель частоты, счетчик, формирователь синусоидального напряжения, усилитель мощности, вихретоковый преобразователь, коммутатор, синхронный детектор, а также интегрирующий преобразователь напряжения во временной интервал, цифровой фазорасщепитель, последовательно соединенные микропроцессор и устройство отображения, отличающийся тем, что он снабжен фильтром низкой частоты с малой постоянной времени и схемой синхронизации, причем выход синхронного детектора соединен со входом фильтра низкой частоты с малой постоянной времени, а выход фильтра низкой частоты с малой постоянной времени соединен со входом интегрирующего преобразователя напряжения во временной интервал, входы схемы синхронизации соединены соответственно с выходами цифрового фазорасщепителя и микропроцессора, а выход схемы синхронизации соединен со входом управления интегрирующего преобразователя напряжения во временной интервал, один из выходов микропроцессора подключен ко вторым входам управляемого делителя частоты, два входа коммутатора подключены соответственно к выходам усилителя мощности и вихретокового преобразователя, третий вход коммутатора подключен к микропроцессору, а выход коммутатора подключен к первому (сигнальному) входу синхронного детектора, первый вход цифрового фазорасщепителя соединен с дополнительным выходом счетчика, второй вход цифрового фазорасщепителя соединен с выходом микропроцессора, выход цифрового фазорасщепителя соединен со вторым (опорным) входом синхронного детектора, выход интегрирующего преобразователя напряжения во временной интервал соединен с микропроцессором.

| Электромагнитный многочастотный структуроскоп | 1983 |

|

SU1100558A1 |

| Электромагнитное многочастотное устройство для неразрушающего контроля | 1981 |

|

SU1000896A1 |

Авторы

Даты

2002-02-10—Публикация

1999-01-15—Подача