Изобретение относится к измерительной технике и может быть использовано совместно с электромагнитными структуроскопами для дефектоскопии и структуроскопии изделий, в частности, методом вихревых токов.

Известен генератор синусоидального сигнала к электромагнитному структуроскопу, содержащий соединенные последовательно генератор прямоугольных импульсов фиксированной частоты, регулируемый делитель частоты и счетчик, соединенные последовательно блок постоянной памяти, цифроаналоговый преобразователь, фильтр и блок управления, подключенный к регулируемому делителю частоты (а. с. СССР 1000896, кл. G 01 N 27/90, опубл. 28.02.83, бюл. 8).

Недостатком генератора является ограниченный частотный диапазон генерируемого синусоидального сигнала. В случае большого числа точек дискретизации на период синусоидального сигнала верхняя частота генерируемого синусоидального сигнала оказывается весьма низкой. Очевидно, что минимальный период дискретизации ТДmin не может быть меньше величины

ТДmin= tС+tA+tЦАП, (1)

где tС - время переключения счетчика (с момента подачи на счетный вход счетчика сигнала с выхода управляемого делителя частоты до установления нового выходного кода счетчика); tА - время выборки адреса постоянного запоминающего устройства (ПЗУ), используемого в качестве блока постоянной памяти; tцап - время установления выходного сигнала цифроаналогового преобразователя. Анализ временных характеристик современной элементной базы показывает, что для распространенных микросхем постоянных запоминающих устройств время выборки адреса составляет от 45 (К 1500 РТ 416) до 60 нс (КР 556 РТ 18), а для относительно недорогих быстродействующих цифроаналоговых преобразователей время преобразования кода в ток составляет от 5 (К 1118 ПА 6 А) до 20 нс (К 1118 ПА 1 А). Таким образом, минимальный период дискретизации (даже без учета времени, необходимого для переключения счетчика) составляет от 50 до 80 нс, что соответствует частоте дискретизации fД не выше 12,5. . . 20 МГц. В то же время частота генерируемого синусоидального сигнала fС равна частоте дискретизации fД, деленной на число точек дискретизации на период синусоидального сигнала nД

fС= fД/nД, (2)

где fС - частота генерируемого синусоидального сигнала; fГ - частота прямоугольных колебаний, генерируемых генератором прямоугольных колебаний фиксированной частоты; fД - частота дискретизации; nД - число точек дискретизации на период синусоидального сигнала.

Следовательно, при числе точек дискретизации nД = 512 и частоте дискретизации fД≈12,5. . . 20 МГц максимальная частота генерируемого синусоидального сигнала fСmax= fД/nД≈24. . . 39 кГц.

Следовательно, верхняя граница частотного диапазона генерируемого синусоидального сигнала оказывается для данного устройства ограниченной частотой fСmaх порядка десятков кГц; в то же время для многочастотных электромагнитных структуроскопов зачастую требуется тестовый синусоидальный сигнал с частотой до единиц МГц. Таким образом, упомянутое устройство (аналог) характеризуется недостаточно широким частотным диапазоном генерируемого синусоидального сигнала. Расширение частотного диапазона генерируемого синусоидального сигнала невозможно, поскольку на высоких частотах невозможно использовать большое число точек дискретизации на период синусоидального сигнала nД ввиду ограниченного быстродействия элементной базы, а на низких частотах при малом числе точек дискретизации на период синусоидального сигнала снижается точность генерируемого синусоидального сигнала (т. е. увеличивается коэффициент гармоник генерируемого синусоидального сигнала).

Наиболее близким к предлагаемому устройству является генератор синусоидальных сигналов к электромагнитному многочастотному структуроскопу, содержащий последовательно соединенные генератор прямоугольных импульсов фиксированной частоты, управляемый делитель частоты и счетчик, соединенные последовательно блок постоянной памяти, цифроаналоговый преобразователь и фильтр, и блок управления, подключенный к управляемому делителю частоты, а также блок ключей, включенных между выходами младших разрядов счетчика и входами младших разрядов блока постоянной памяти (а. с. СССР 1118908, кл. G 01 N 27/90, опубл. 15.10.84, бюл. 38).

Недостатком прототипа также является ограниченный частотный диапазон генерируемых синусоидальных сигналов. Некоторое расширение частотного диапазона генерируемого синусоидального сигнала достигнуто за счет уменьшения числа точек дискретизации на период синусоидального сигнала на высоких частотах, для чего предназначен блок ключей. Блок ключей служит для коммутации входов блока постоянной памяти: путем отключения входов блока постоянной памяти от младших разрядов счетчика уменьшается число точек дискретизации на период синусоидального сигнала, поскольку при отключении одного младшего разряда счетчика от входа блока постоянной памяти происходит считывание из блока постоянной памяти кода каждой второй точки дискретизации, а число точек дискретизации на период синусоидального сигнала уменьшается вдвое; при отключении двух младших разрядов счетчика от входов блока постоянной памяти происходит считывание из блока постоянной памяти кода каждой четвертой точки дискретизации, а число точек дискретизации на период уменьшается вчетверо; при отключении трех младших разрядов счетчика от входов блока постоянной памяти происходит считывание из блока постоянной памяти кода каждой восьмой точки дискретизации, а число точек дискретизации на период уменьшается в 8 раз и т. д. , т. е. при отключении от входов блока постоянной памяти m младших разрядов счетчика (где m - положительное число, максимальное значение которого определяется отношением максимального числа точек дискретизации на период синусоидального сигнала к минимальному числу точек дискретизации на период синусоидального сигнала) число точек дискретизации на период уменьшается в 2m раз. Уменьшением числа точек дискретизации на период удается добиться повышения максимальной частоты генерируемого сигнала; при этом на низких частотах используется максимальное (для данного устройства) число точек дискретизации на период, а с повышением частоты генерируемого сигнала число точек дискретизации при необходимости уменьшается. Уменьшение числа точек дискретизации на период синусоидального сигнала приводит к ухудшению качества генерируемого синусоидального сигнала. Частоты побочных составляющих спектра генерируемого сигнала определяются по формуле

fm= fС•(i•nД±1)= fД•i±fС, (3)

где fС - частота генерируемого синусоидального сигнала (частота основной гармоники генерируемого сигнала); nД - число точек дискретизации на период синусоидального сигнала; i - номер гармоники (неотрицательное число): минимальное значение i равно 0 и соответствует основной гармонике генерируемого сигнала; прочие (положительные) значения i соответствуют побочным составляющим спектра генерируемого сигнала. Как видно из (3), уменьшение числа точек дискретизации на период синусоидального сигнала приводит к тому, что частоты побочных составляющих стягиваются к частоте основной гармоники, что затрудняет их подавление неперестраиваемым фильтром низкой частоты. Однако для высоких частот генерируемого синусоидального сигнала ухудшение его качества при снижении числа точек дискретизации на период синусоидального сигнала менее значительно, чем для низких частот. Действительно, из (3) следует, что с повышением частоты генерируемого синусоидального сигнала fС абсолютная разница между частотами основной и побочных гармоник возрастает, следовательно, задача подавления побочных составляющих спектра генерируемого сигнала с помощью фильтра низкой частоты упрощается.

Для случая, когда все входы блока постоянной памяти соединены с соответствующими выходами счетчика

fС= fГ/nД•kД, (4)

где fС - частота генерируемого синусоидального сигнала; fГ - частота прямоугольных колебаний, генерируемых генератором прямоугольных колебаний фиксированной частоты; nД - число точек дискретизации на период синусоидального сигнала; kД - коэффициент деления частоты управляемого делителя частоты.

Поскольку для случая, когда все входы блока постоянной памяти соединены с соответствующими выходами счетчика, справедливо соотношение

fД= fГ/kД, (5)

где fД - частота дискретизации; fГ - частота прямоугольных колебаний, генерируемых генератором прямоугольных колебаний фиксированной частоты; kД - коэффициент деления частоты управляемого делителя частоты;

выражение (4) может быть преобразовано к виду

fС= fГ/nД, (6)

где fС - частота прямоугольных колебаний, генерируемых генератором прямоугольных колебаний фиксированной частоты; fД - частота дискретизации; nД - число точек дискретизации на период синусоидального сигнала.

Выражение (6) справедливо также и для случаев, когда один или несколько младших разрядов счетчика отключены от выходов блока постоянной памяти. Из (4) и (6) видно, что уменьшение числа точек дискретизации на период синусоидального сигнала nД должно привести к увеличению частоты генерируемого синусоидального сигнала. Однако следует учитывать, что для прототипа при изменении числа точек дискретизации на период синусоидального сигнала путем отключения младших разрядов счетчика от блока постоянной памяти частота счета счетчика остается неизменной. Отсюда нетрудно определить, что отключение m младших разрядов счетчика от младших адресных входов блока постоянной памяти приводит к уменьшению частоты дискретизации в 2m раз. Действительно, частота дискретизации определяется частотой переключения самого младшего разряда счетчика, соединенного со входом блока постоянной памяти. Для самого младшего разряда счетчика частота переключения равна частоте выходного сигнала управляемого делителя частоты, т. е. определяется соотношением fГ/kД, где fГ - частота прямоугольных импульсов, генерируемых генератором прямоугольных импульсов фиксированной частоты; kД - коэффициент деления частоты управляемого делителя частоты. Для следующего разряда счетчика частота переключения в 2 раза ниже частоты переключения самого младшего разряда и т. д. : частота переключения каждого следующего (более старшего) разряда в 2 раза меньше, чем частота переключения предыдущего (более младшего) разряда. Отсюда следует, что при отключении m младших разрядов счетчика от входов блока постоянной памяти частота дискретизации fД уменьшается в 2m раз.

Следовательно, согласно (6) при изменении числа точек дискретизации на период синусоидального сигнала nД отключением младших разрядов счетчика от входов блока постоянной памяти частота генерируемого синусоидального сигнала fС не изменяется, поскольку и число точек дискретизации на период синусоидального сигнала, и частота дискретизации уменьшаются в равное число (2m) раз, а значит, соотношение fД/kД остается постоянным.

Таким образом, уменьшение числа точек дискретизации на период синусоидального сигнала nД отключением младших разрядов счетчика от входов блока постоянной памяти не приводит к увеличению частоты генерируемого синусоидального сигнала. Для увеличения частоты генерируемого синусоидального сигнала необходимо с отключением m младших разрядов счетчика уменьшить соответственно в 2m раз коэффициент деления частоты управляемого делителя частоты kД, увеличив тем самым частоту выходного сигнала управляемого делителя частоты в 2m раз. Таким образом, частота дискретизации остается постоянной, но частота fСЧ, на которой работает счетчик, увеличивается в 2m раз. Следовательно, для прототипа при сохранении частоты дискретизации постоянной частота, на которой работает счетчик, растет. Очевидно, что по сравнению с аналогом для прототипа число точек дискретизации на период может быть изменено от nДmax до nДmin, где nДmax и nДmin - соответственно максимальное и минимальное число точек дискретизации на период синусоидального сигнала, что при сохранении постоянной частоты дискретизации снижает требования к быстродействию цифроаналогового преобразователя и блока постоянной памяти, следовательно, максимальная частота генерируемого синусоидального сигнала fСmax может быть увеличена.

Однако, поскольку частота, на которой работает счетчик, не снижается, к элементном базе счетчика, генератора прямоугольных импульсов фиксированной частоты и управляемого делителя частоты по-прежнему предъявляются чрезмерно жесткие требования. При этом рабочая частота генератора прямоугольных импульсов фиксированной частоты и управляемого делителя частоты (fГ) может быть и более высокой, чем рабочая частота счетчика fСЧ, что зависит от диапазона изменения коэффициента деления частоты kД управляемого делителя частоты: при минимальном коэффициенте деления частоты управляемого делителя частоты, равном kДmin, рабочая частота fГ генератора прямоугольных импульсов фиксированной частоты и управляемого делителя частоты в kДmin раз превышает частоту fСЧ, на которой работает счетчик, и в kДmin•2m раз превышает частоту дискретизации (в частном случае, если kДmin= 1, рабочая частота генератора прямоугольных импульсов fГ фиксированной частоты и управляемого делителя частоты равна рабочей частоте счетчика fСЧ).

Таким образом, к элементной базе прототипа, а именно элементной базе счетчика, управляемого делителя частоты и генератора прямоугольных импульсов фиксированной частоты предъявляются чрезмерно жесткие требования. Так, если максимальное число точек дискретизации на период синусоидального сигнала nДmax= 512, а минимальное nДmin= 8 (при nДmin<8 качество генерируемого синусоидального сигнала оказывается неудовлетворительным ввиду значительного роста амплитуд побочных составляющих спектра выходного сигнала прототипа, частоты которых приближаются к частоте генерируемого сигнала, вследствие чего затрудняется подавление побочных составляющих спектра выходного сигнала прототипа и растет коэффициент гармоник генерируемого синусоидального сигнала). В этом случае при максимальной частоте генерируемого сигнала частота fСЧ, на которой работает счетчик, превышает частоту дискретизации в nДmax/nДmin= 512/8= 64 раза (наименьшее число точек дискретизации на период синусоидального сигнала nДmin соответствует максимальной частоте генерируемого сигнала fСmax, а значит, максимальному числу отключенных от младших разрядов счетчика входов блока постоянной памяти). Таким образом, при частоте генерируемого синусоидального сигнала fС= 1 МГц и числе точек дискретизации на период синусоидального сигнала nД= 8 частота дискретизации составляет

fД= fС•nД= 8•1= 8 МГц,

а рабочая частота счетчика fСЧ, превышающая частоту дискретизации fД в nДmах/nДmin= 64 раза

fСЧ= fД•(nДmax/nДmin)= 8•64= 512 МГц.

Соответственно частота fГ, на которой работают делитель частоты и генератор прямоугольных импульсов фиксированной частоты, также должна быть не менее 512 МГц. В то же время даже частота переключения триггеров быстродействующей серии логических микросхем 1500 составляет не более 300 МГц (для других распространенных серий логических микросхем, таких как 555, 1533, и даже 500 и 1554 частота переключения триггеров не превышает указанной величины, а для некоторых из указанных серий является еще меньшей). Очевидно, что максимальная частота переключения триггеров определяет максимальную рабочую частоту счетчиков микросхем указанных серий, которая будет даже меньшей, чем максимальная частота переключения триггеров. Таким образом, диапазон частот генерируемого синусоидального сигнала оказывается существенно ограниченным временными характеристиками (быстродействием) элементной базы, причем если для аналога препятствием к увеличению максимальной частоты генерируемого синусоидального сигнала fСmax является ограниченное быстродействие блока постоянной памяти и цифроаналогового преобразователя, то для прототипа препятствием в большей степени являются параметры элементной базы генератора прямоугольных импульсов фиксированной частоты, управляемого делителя частоты и счетчика. Прототип позволяет снизить требования только к временным параметрам (быстродействию) блока постоянной памяти и цифроаналогового преобразователя, чего оказывается недостаточно для построения широкополосного генератора синусоидального сигнала.

Технической задачей изобретения является расширение частотного диапазона генерируемого синусоидального сигнала при сохранении качества генерируемого синусоидального сигнала.

Техническая задача решается тем, что генератор синусоидального сигнала к электромагнитному многочастотному структуроскопу (далее в тексте - устройство), содержащий соединенные последовательно генератор прямоугольных колебаний фиксированной частоты, управляемый делитель частоты, счетчик, а также блок постоянной памяти и соединенные последовательно цифроаналоговый преобразователь и фильтр низкой частоты, подключенный к управляемому делителю частоты блок управления, отличающийся тем, что он снабжен блоком коммутаторов, блоком коммутаторов кодов дискретизации, блоком инверторов, а также коммутатором, причем одни входы блока коммутаторов соединены с выходами счетчика (за исключением выхода самого старшего разряда счетчика), а вторые входы блока коммутаторов - с выходами блока управления, входы управления блока коммутаторов соединены с выходами блока управления, выходы блока коммутаторов соединены со входами блока постоянной памяти (за исключением самого старшего входа блока постоянной памяти); одни входы блока коммутаторов кодов дискретизации соединены с выходами блока постоянной памяти, а другие входы блока коммутаторов кодов дискретизации - с выходами блока инверторов, выходы блока коммутаторов кодов дискретизации соединены со входами цифроаналогового преобразователя, входы блока инверторов соединены с выходами блока постоянной памяти, вход управления блока коммутаторов кодов дискретизации соединен с выходом коммутатора, входы коммутатора соединены с выходами счетчика, а входы управления коммутатора соединены с выходами блока управления, старший вход блока постоянной памяти соединен с блоком управления.

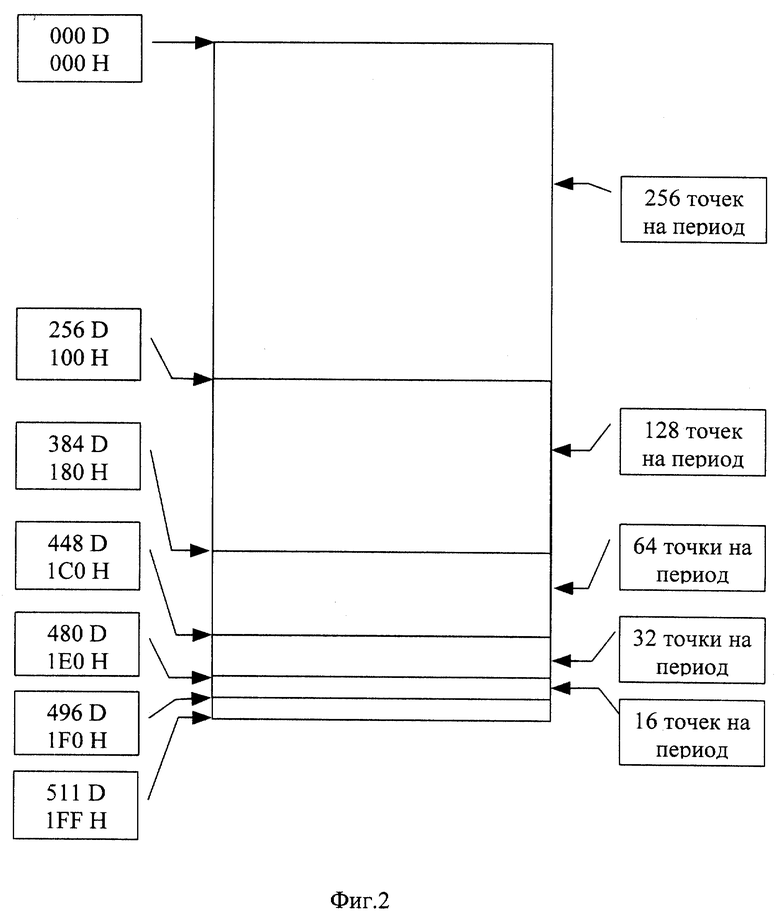

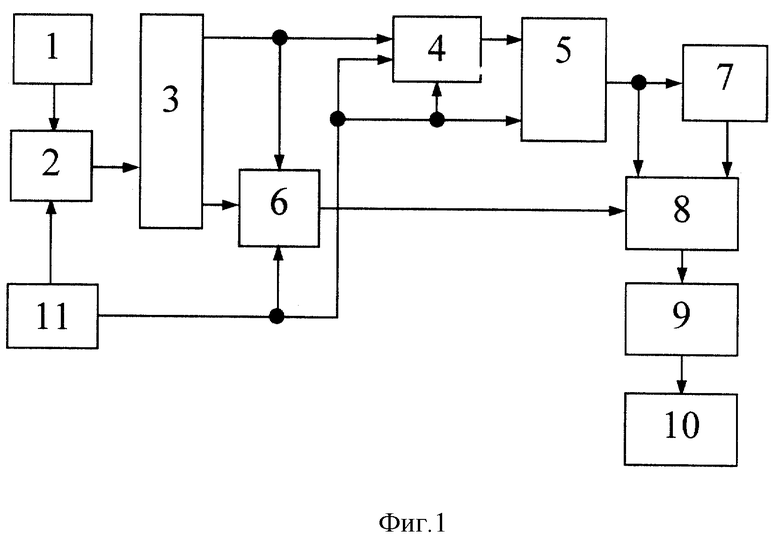

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена блок-схема устройства, а на фиг. 2 - пример схемы распределения адресного пространства блока постоянной памяти для числа точек дискретизации от nДmin= 16 до nДmax= 256 на период синусоидального сигнала (отметим, что при меньшем минимальном числе точек дискретизации на период синусоидального сигнала, например, при nДmin= 2, которое является минимально возможным числом точек дискретизации на период синусоидального сигнала, общий объем блока постоянной памяти останется тем же самым).

Устройство содержит последовательно соединенные генератор прямоугольных импульсов фиксированной частоты 1, управляемый делитель частоты 2, счетчик 3, блок коммутаторов 4, блок постоянной памяти 5, коммутатор 6, блок инверторов 7, блок коммутаторов кодов дискретизации 8, цифроаналоговый преобразователь 9, фильтр низкой частоты 10, блок управления 11.

Устройство работает следующим образом. Прямоугольные импульсы фиксированной частоты fГ с выхода генератора прямоугольных импульсов фиксированной частоты 1 поступают на управляемый делитель частоты 2, коэффициент деления частоты kД которого устанавливается блоком управления 11. Импульсы с выхода управляемого делителя частоты 2 поступают на счетный вход счетчика 3. Частота счета fСЧ счетчика 3, таким образом, определяется частотой генерации fГ генератора прямоугольных импульсов фиксированной частоты 1 и коэффициентом деления частоты kД управляемого делителя частоты 2, который устанавливается блоком управления 11, и равна частоте дискретизации fД

fСЧ= fГ/kД= fД, (7)

где fСЧ - частота, на которой работает счетчик 3; fГ - частота генерации генератора прямоугольных импульсов фиксированной частоты 1; kД - коэффициент деления частоты управляемого делителя частоты 2; fД - частота дискретизации.

Поскольку при числе точек дискретизации на период синусоидального сигнала nд= 2N (где N= log2(nД) - целое положительное число, равное числу входов блока постоянной памяти 5, соединенных с выходами счетчика 3 коммутатором 4) значения функции |sin(x)| (т. е. модуль функции sin(x)) повторяются на протяжении периода синусоидального сигнала, по крайней мере, дважды, для экономии адресного пространства блока постоянной памяти 5 в блоке постоянной памяти 5 сохраняются коды дискретизации синусоидального сигнала только для 1/2 периода синусоидального сигнала, вычисленные по формуле

где 2N= nД - число точек дискретизации на период синусоидального сигнала (N - число входов блока постоянной памяти, соединенных коммутатором 4 с выходами счетчика 3); i - порядковый номер точки дискретизации, i = 0 . . . nД-1; А - амплитуда синусоидального сигнала, определяемая по формуле

где М - разрядность выходного кода блока постоянной памяти 5.

Согласно (8) и (9) нулевое значение синусоидального сигнала кодируется кодом round(A), соответственно минимальному значению синусоидального сигнала соответствует код 0, а максимальному значению синусоидального сигнала - код (2М-1), т. е. минимальному и максимальному значениям выходного цифрового кода блока постоянной памяти 5 соответствуют минимальное (т. е. -1 соответствует код дискретизации 0) и максимальное (т. е. 1 соответствует код дискретизации 2М-1) значения синусоидального сигнала.

В этом случае коды дискретизации второй половины периода синусоидального сигнала могут быть определены без применения сложных (и относительно медленных по сравнению с более простыми логическими элементами тех же серий) арифметико-логических устройств путем простого инвертирования кода соответствующих мгновенных значений синусоидального сигнала первой половины периода синусоидального сигнала. Используется известное соотношение sin(x) = -sin(x+π); если же минимальному значению синусоидального сигнала соответствует код дискретизации 0, а максимальному значению синусоидального сигнала соответствует код дискретизации (2М-1), где М - разрядность выходного кода блока постоянной памяти 5, то справедливым для кодов дискретизации синусоидального сигнала, вычисленных по приведенной выше формуле (8), становится выражение

где i - номер точки дискретизации - целое положительное число в диапазоне 1. . . ((nД/2)-1); nД - число точек дискретизации на период синусоидального сигнала. Точке дискретизации с номером 0 соответствует код дискретизации, соответствующий нулевому значению sin(x). При этом полученные для второй половины полупериода синусоиды значения совпадают с полученными по формуле (8) во всех случаях, кроме i= 0 (который соответствует нулевому значению функции sin (x)), т. е. при i= 1. . . ((nД/2)-1).

Особенностью такого способа кодирования и последующего восстановления синусоидального сигнала по его цифровым значениям, как нетрудно видеть, является представление нулевого значения синусоидального сигнала двумя значениями кода (1000. . . 0000 и 0111. . . 1111 в двоичной системе счисления). А= 2M-1 - нечетное число, следовательно, А/2= (2М-1-1/2)= (2М-1-0,5) - нецелое число, дробная часть которого равна 0,5. При преобразовании результата А/2 в двоичный код с последующим округлением будет получено число вида 1000. . . 0000 в двоичном представлении, т. е. 2М-1, которое при инвертировании дает значение 0111. . . 1111, т. е. (2М-1-1), где М - разрядность выходного кода блока постоянной памяти 5.

Таким образом, вычисленное по формуле (8) значение кода дискретизации, соответствующего нулевому значению синусоидального сигнала, составляет 1000. . . 000, а вычисленное по формуле (10) - 0111. . . 1111. Нетрудно видеть, что и в том, и в другом случае погрешность представления нулевого значения не превышает погрешности округления, равной 1/2М+1, или 2-(М+1), где М - разрядность выходного кода блока постоянной памяти 5, и не оказывает (при достаточно большом значении М) существенного влияния на качество генерируемого синусоидального сигнала. Кроме того, увеличением разрядности М кода дискретизации синусоидального сигнала (т. е. разрядности выходного кода блока постоянной памяти 5, а соответственно, и входного кода цифроаналогового преобразователя 9) указанная погрешность может быть уменьшена.

Блок постоянной памяти 5 разделен на секторы, в каждом из которых сохранены коды дискретизации синусоидального сигнала для 1/2 периода синусоидального сигнала, причем каждому сектору соответствует свое число точек дискретизации на период синусоидального сигнала nДj (соответственно j-сектор имеет объем nДj). Для двух соседних частот дискретизации число точек дискретизации на период синусоидального сигнала nД отличается вдвое (соответственно объемы соответствующих секторов блока постоянной памяти 5 также отличаются вдвое).

Переключением секторов блока постоянной памяти 5, из которых считываются коды дискретизации синусоидального сигнала, изменяется число точек дискретизации на период генерируемого синусоидального сигнала nД. Секторы блока постоянной памяти 5 имеют объем, равный 2n, где n - целое положительное число, и расположены в адресном пространстве блока постоянной памяти 5 таким образом, что начальный адрес каждого сектора кратен его размеру (т. е. начальный адрес сектора размером 2m адресного пространства блока постоянной памяти 5 кратен 2m).

Минимальное значение числа точек дискретизации на период синусоидального сигнала nДmin зависит от требуемого качества генерируемого синусоидального сигнала. Очевидно, что минимальное значение числа точек дискретизации на период синусоидального сигнала nДmin не может быть меньше 2. В случае nДmin= 2 выходной сигнал цифроаналогового преобразователя 4 имеет форму меандра. С помощью фильтра низкой частоты 10 из меандра также может быть получен синусоидальный сигнал, однако в этом случае к параметрам фильтра низкой частоты 10 предъявляются весьма жесткие требования, поскольку амплитуда побочных составляющих генерируемого сигнала (т. е. высокочастотных гармоник) в данном случае велика.

Сектор блока постоянной памяти 5, из которого производится чтение кодов дискретизации синусоидального сигнала (а значит, и частота дискретизации fД), устанавливается с помощью блока коммутаторов 4. При этом объем считываемого сектора блока постоянной памяти 5 (и число точек дискретизации на период синусоидального сигнала nД) определяется числом разрядов счетчика 3, соединенных с входами блока постоянной памяти 5, а координаты начала сектора в адресном пространстве блока постоянной памяти 5 - состоянием выходов блока управления 11, соединенных блоком коммутаторов 4 с входами блока постоянной памяти 5. При этом состояние старших входов блока постоянной памяти 5 (соединенных с выходами блока управления 11) остается неизменным, а состояние младших адресных входов блока постоянной памяти 5 (соединенных с выходами счетчика 3) изменяется в соответствии с изменением состояния соответствующих разрядов счетчика 3. Для коммутации входов блока постоянной памяти 5 служит блок коммутаторов 4. Управление блоком коммутаторов 4 осуществляется блоком управления 11, устанавливающим код на входах управления блоком коммутаторов 4. Изменением кода на входах управления блоком коммутаторов 4 входы блока постоянной памяти 5 соединяются либо с выходами соответствующих разрядов счетчика 3, либо с выходами блока управления 11. В первом случае состояние входов блока постоянной памяти 5, соединенных с выходами блока коммутаторов 4, изменяется в соответствии с изменением состояния соответствующих разрядов счетчика 3, а во втором - остается статическим и задается блоком управления 11, определяя область и объем адресного пространства блока постоянной памяти 5 (сектор блока постоянной памяти 5), из которой производится считывание кодов мгновенных значений синусоидального сигнала. Выбор сектора блока постоянной памяти 5 и установка числа точек дискретизации синусоидального сигнала на период синусоидального сигнала nД, таким образом, производится блоком управления 11 с помощью блока коммутаторов 4.

Таким образом, для предлагаемого устройства установка кодов на входах управления блока коммутаторов 4 определяет число точек дискретизации на период синусоидального сигнала и частоту генерируемого синусоидального сигнала fС: при уменьшении либо увеличении числа точек дискретизации на период синусоидального сигнала nД частота дискретизации fД (т. е. в данном случае частота следования выборок кодов дискретизации мгновенных значений синусоидального сигнала из блока постоянной памяти 5) остается неизменной, однако поскольку число точек дискретизации на период синусоидального сигнала nД уменьшается, частота генерируемого сигнала fС соответственно увеличивается (при уменьшении числа точек дискретизации на период синусоидального сигнала nД) или уменьшается (при увеличении числа точек дискретизации на период синусоидального сигнала nД). Таким образом, частота генерируемого синусоидального сигнала fС регулируется двумя способами: во-первых, изменением коэффициента деления частоты kД управляемого делителя частоты 2, а во-вторых, изменением числа точек дискретизации на период синусоидального сигнала nД с помощью блока коммутаторов 4 и блока управления 11. Первый способ изменения частоты генерируемого синусоидального сигнала fС (изменение коэффициента деления частоты kД управляемого делителя частоты 2) применяется в области относительно низких частот генерируемого синусоидального сигнала, пока параметры элементной базы блока постоянной памяти 5, цифроаналогового преобразователя 9, блока инверторов 7 и блока коммутаторов кодов дискретизации 8 позволяют увеличивать частоту дискретизации fД. После достижения предельно возможной частоты дискретизации fДmax частота генерируемого синусоидального сигнала fС повышается уменьшением числа точек дискретизации на период синусоидального сигнала nД с помощью блока коммутаторов 4 и блока управления 11 (вплоть до значения nДmin, соответствующего максимальной частоте генерируемого синусоидального сигнала fCmax).

Объем наименьшего и наибольшего секторов блока постоянной памяти 5 определяется соответственно минимальным nДmin и максимальным nДmax числом точек дискретизации на период синусоидального сигнала. В общем случае распределение кодов дискретизации синусоидального сигнала в адресном пространстве блока постоянной памяти 5 осуществляется следующим образом. Адресное пространство блока постоянной памяти 5 делится на две равные части (т. е. пополам). В одной половине адресного пространства блока постоянной памяти 5 сохраняются коды 1/2 периода синусоидального сигнала с наибольшим числом точек дискретизации на период синусоидального сигнала (nДmax, длина этого наибольшего сектора составляет nДmax/2). Оставшаяся (вторая) половина адресного пространства блока постоянной памяти 5 также делится пополам; длина каждой половины оказывается равной 1/4 общего адресного пространства блока постоянной памяти 5. В первой половине (равной 1/4 общего адресного пространства блока постоянной памяти 5) сохраняются коды дискретизации для синусоидального сигнала с числом точек дискретизации на период синусоидального сигнала nД, в 2 раза меньшим nДmax (т. е. nДmax/2). Вторая половина (1/4 всего адресного пространства блока постоянной памяти 5) вновь делится пополам: в первой половине (равной 1/8 адресного пространства блока постоянной памяти 5) сохраняются коды дискретизации для синусоидального сигнала с числом точек дискретизации на период синусоидального сигнала nДmax/4. Вторая половина (равная 1/8 адресного пространства блока постоянной памяти 5) вновь делится пополам: в одной половине (равной 1/16 адресного пространства блока постоянной памяти 5) сохраняются коды дискретизации 1/2 периода синусоидального сигнала с числом точек дискретизации на период синусоидального сигнала nДmax/8, а вторая половина (равная 1/16 адресного пространства) вновь делится пополам и т. д. В результате емкость блока постоянной памяти 5 не увеличивается по сравнению с емкостью блока постоянной памяти прототипа. При этом, если максимальное число точек дискретизации на период синусоидального сигнала равно 2k, то емкость блока постоянной памяти 5 также будет равна 2k. Пример расположения секторов в адресном пространстве блока постоянной памяти 5 для числа точек дискретизации от 16 до 256 приведен на фиг. 2.

Нетрудно видеть, что при описанном способе хранения кодов дискретизации синусоидального сигнала состояние старшего адресного входа блока постоянной памяти 5 остается статическим независимо от частоты генерируемого синусоидального сигнала fС. Состояние старшего адресного входа блока постоянной памяти 5 определяет, из какой именно части (половины) адресного пространства блока постоянной памяти 5 считываются коды дискретизации синусоидального сигнала. При этом в процессе генерирования синусоидального сигнала состояние старшего адресного входа блока постоянной памяти 5 остается статическим. Отметим также, что при минимальном числе точек дискретизации на период синусоидального сигнала nДmin= 2 состояние всех адресных входов блока постоянной памяти 5 должно оставаться статическим, в результате чего на выходе блока постоянной памяти 5 постоянно присутствует код, соответствующий минимальному (т. е. 000. . . 000), или, наоборот, максимальному (т. е. 111. . . 111) значению кода дискретизации. Меандр на выходе цифроаналогового преобразователя 9 формируется за счет того, что в течение одной половины периода генерируемого сигнала выходной код блока постоянной памяти 5 инвертируется, а в течение второй половины периода - не инвертируется.

При таком способе хранения кодов дискретизации синусоидального сигнала и восстановления синусоидального сигнала по его мгновенным значениям при сохранении качества генерируемого синусоидального сигнала диапазон частот генерируемого синусоидального сигнала значительно расширяется, а емкость блока постоянной памяти 5 по сравнению с прототипом остается неизменной. Таким образом, предлагаемое устройство менее требовательно к временным параметрам элементной базы и не требует применения блоков постоянной памяти большей (по сравнению с прототипом) емкости, что важно для генератора синусоидальных сигналов с широким диапазоном генерируемых частот: поскольку емкость интегральных микросхем ПЗУ с малым временем выборки адреса (т. е. быстродействующих интегральных микросхем ПЗУ) относительно невелика при значительном энергопотреблении (до 1 Вт на корпус и более для отечественных микросхем ПЗУ), а повышение качества синусоидального сигнала достигается увеличением числа точек дискретизации nД на период синусоидального сигнала, имеет смысл возможно более рационально использовать адресное пространство блока постоянной памяти 5. В противном случае требуется применение микросхем ПЗУ большего объема (либо нескольких микросхем ПЗУ), а следовательно, неизбежен рост мощности, потребляемой блоком постоянной памяти 5, а также ухудшение массогабаритных показателей устройства в целом. Более рациональное использование адресного пространства блока постоянной памяти 5 заключается в хранении кодов дискретизации только для 1/2 периода синусоидального сигнала, что позволяет разместить в адресном пространстве блока постоянной памяти 5 коды дискретизации для различных чисел точек дискретизации на период синусоидального сигнала, что, в свою очередь, позволяет сделать частоту переключения счетчика 3, равной частоте дискретизации fД, снизив, таким образом, максимальную частоту, на которой работают элементы схемы устройства, в nДmax/nДmin раз по сравнению с прототипом, а значит, и повысить максимальную частоту генерируемого синусоидального сигнала fСmax в соответствующее число раз при использовании той же элементной базы.

Коммутатор 6 служит для формирования сигнала управления блоком коммутаторов кодов дискретизации 8. На входы коммутатора 6 поступают коды с выхода счетчика 3, а на управляющие входы коммутатора 6 - управляющий код с выхода блока управления 11. Код на входах управления коммутатора 6 устанавливается блоком управления 11 таким, что с входом управления блоком коммутаторов кодов дискретизации 8 соединяется разряд счетчика 3 с номером (N+1), где N - количество разрядов счетчика 3, соединенных с входами блока постоянной памяти 5 (при этом минимальный номер соответствует самому младшему разряду счетчика 3). Т. е. с входом управления блоком коммутаторов 8 соединен следующий за самым старшим разрядом счетчика 3, соединенным в данный момент через коммутатор 4 с адресным входом блока постоянной памяти 5. Очевидно, что частота импульсов на выходе счетчика 3 с номером (N+1) в 2 раза ниже частоты импульсов на выходе с номером N. Тем самым обеспечивается смена состояния сигнала управления блоком коммутаторов кодов дискретизации 8 один раз в течение периода генерируемого синусоидального сигнала. Число n в данном случае может быть определено как N= log2(nДj/2)= log2(nДj)-1, где nДj - число точек дискретизации на период синусоидального сигнала для j-го сектора.

Цифровой код (код дискретизации синусоидального сигнала) с выхода блока коммутаторов кодов дискретизации 8 поступает на входы цифроаналогового преобразователя 9. Цифроаналоговый преобразователь 9 преобразует цифровой код, поступающий с выходов блока коммутаторов кодов дискретизации 8 на входы цифроаналогового преобразователя 9, в аналоговый сигнал. Поскольку состояние входа управления блока коммутаторов кодов дискретизации 8 изменяется один раз в течение периода генерируемого синусоидального сигнала, в течение одной половины периода генерируемого синусоидального сигнала на вход цифроаналогового преобразователя 9 поступает прямой, а в течение второй половины периода генерируемого синусоидального сигнала - инвертированный код с выхода блока постоянной памяти 5. И в течение первой, и в течение второй половины периода генерируемого синусоидальнего сигнала из блока постоянной памяти 5 считываются одни и те же коды дискретизации синусоидального сигнала, формирование синусоиды осуществляется за счет инвертирования кодов дискретизации.

Переключение между выходами блока постоянной памяти 5 и блока инверторов 7 осуществляется блоком коммутаторов кодов дискретизации 8. На выходе цифроаналогового преобразователя 9, таким образом, формируется ступенчатая синусоида, форма которой зависит от числа точек дискретизации на период синусоидального сигнала nД (при числе точек дискретизации на период синусоидального сигнала nД>2) или меандр (при nД= 2). Фильтр низкой частоты 10 подавляет побочные составляющие спектра генерируемого сигнала (т. е. высокочастотные гармоники, присутствующие в спектре выходного сигнала цифроаналогового преобразователя). Таким образом, на выходе фильтра низкой частоты 10 формируется синусоидальный сигнал, частота которого fС определяется частотой fГ генератора прямоугольных импульсов фиксированной частоты 1, коэффициентом деления частоты kД управляемого делителя частоты 2, управление которым осуществляет блок управления 11, а также числом точек дискретизации на период синусоидального сигнала nД, которое устанавливается блоком управления 11 с помощью блока коммутаторов 4, коммутирующего младшие адресные входы блока постоянной памяти 5

fС= fГ/kД•nД, (11)

где fС - частота генерируемого синусоидального сигнала; fГ - частота прямоугольных импульсов, генерируемых генератором прямоугольных импульсов фиксированной частоты 1; kД - коэффициент деления частоты управляемого делителя частоты 2; nД - число точек дискретизации на период синусоидального сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА | 1999 |

|

RU2156027C1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| ЭЛЕКТРОМАГНИТНЫЙ МНОГОЧАСТОТНЫЙ СТРУКТУРОСКОП | 1999 |

|

RU2179312C2 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204197C2 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

Устройство относится к измерительной технике и может быть использовано совместно с электромагнитными структуроскопами для неразрушающего контроля изделий, в частности, методом вихревых токов. Устройство содержит генератор импульсов, управляемый делитель частоты, счетчик, блок постоянной памяти, цифроаналоговый преобразователь и фильтр низкой частоты. В состав устройства введены два блока коммутаторов, блок инверторов и коммутатор. Первый блок коммутаторов служит для коммутации адресных входов блока постоянной памяти. В каждом из секторов блока постоянной памяти сохранены коды мгновенных значений синусоидального сигнала для половины периода синусоиды. Каждому сектору соответствует свое число точек дискретизации на период синусоидального сигнала. Второй блок коммутаторов, блок инверторов и коммутатор служат для восстановления синусоидального сигнала по половине его полного периода. Указанный способ хранения кодов дискретизации позволяет сделать частоту, на которой работает счетчик, равной частоте дискретизации. Изобретение расширяет частотный диапазон генерируемого сигнала в сторону увеличения максимальной частоты. 2 ил.

Генератор синусоидального сигнала к электромагнитному многочастотному структуроскопу, содержащий соединенные последовательно генератор прямоугольных колебаний фиксированной частоты, управляемый делитель частоты, счетчик, а также блок постоянной памяти и соединенные последовательно цифро-аналоговый преобразователь и фильтр низкой частоты, подключенный к управляемому делителю частоты блок управления, отличающийся тем, что он снабжен блоком коммутаторов, блоком коммутаторов кодов дискретизации, блоком инверторов, а также коммутатором, причем одни входы блока коммутаторов соединены с выходами счетчика (за исключением выхода самого старшего разряда счетчика), а вторые входы блока коммутаторов - с выходами блока управления, входы управления блока коммутаторов соединены с выходами блока управления, выходы блока коммутаторов соединены с входами блока постоянной памяти (за исключением самого старшего входа блока постоянной памяти); одни входы блока коммутаторов кодов дискретизации соединены с выходами блока постоянной памяти, а другие входы блока коммутаторов кодов дискретизации - с выходами блока инверторов, выходы блока коммутаторов кодов дискретизации соединены с входами цифро-аналогового преобразователя, входы блока инверторов соединены с выходами блока постоянной памяти, вход управления блока коммутаторов кодов дискретизации соединен с выходом коммутатора, входы коммутатора соединены с выходами счетчика, а входы управления коммутатора соединены с выходами блока управления, старший вход блока постоянной памяти соединен с блоком управления.

| Генератор синусоидальных сигналов к электромагнитному многочастотному структуроскопу | 1982 |

|

SU1118908A1 |

| Электромагнитное многочастотное устройство для неразрушающего контроля | 1981 |

|

SU1000896A1 |

| Цифроаналоговый функциональный генератор | 1983 |

|

SU1124347A2 |

| US 4484296 A, 20.11.1984 | |||

| DE 4037137A1,25.05.1992. | |||

Авторы

Даты

2002-01-27—Публикация

1999-05-05—Подача