Настоящее изобретение относится к средствам и способам коммутации в телекоммуникационных системах, в частности к переключателю и способу выполнения операции переключения с однобитовым разрешением в цифровой телекоммуникационной системе.

Уровень техники

В цифровых системах передачи данные передаются в последовательном потоке бит или символов во временных интервалах, в которых передается заданное число бит, обычно восемь бит. В известных системах с импульсно-кодовой модуляцией (РСМ) эти биты в одном временном интервале полностью резервируются для одного канала. В Европейской основной мультиплексной системе, имеющей скорость передачи данных 2048 кбит/сек (в которой длина фрейма составляет 32 временных промежутка, то есть 256 бит), можно передавать таким способом всего 30 речевых каналов, каждый из которых имеет скорость передачи 64 кбит/сек. (Соответствующая система, действующая в США, имеет 24 канала при скорости передачи 1544 кбит/сек).

Однако в настоящее время для повышения пропускной способности передачи данных используются сложные способы кодирования речевых сообщений. Например, пропускную способность основной системы со скоростью передачи выше 2048 кбит/сек можно увеличить до 60 или 120 речевых каналов. В этом случае информацию, содержащуюся в речевых каналах, необходимо кодировать в кодеке.

Следовательно, из-за таких способов кодирования в одном речевом канале задействована только часть бит временного интервала, например, четыре или два бита из восьми. Например, кодеки, в которых используется полоса пропускания 7 кГц, позволяют передавать 6, 7 или 8 бит за временной интервал, то есть повысить пропускную способность основной мультиплексной системы до 48, 56 или 64 кбит/сек. Такие подходы позволяют уплотнять субканалы, такие как каналы данных, в течение одного временного интервала, поскольку фактический канал должен передавать менее 8 бит за временной интервал.

В результате развития вышеописанной системы возникла потребность в переключении информации, которую необходимо передавать с разрешением 1 бит вместо побайтового переключения (то есть одно слово за период времени). В таких переключателях, работающих с разрешением 1 байт, обычно используют переключение схем памяти, которые имеют разрядность 1 бит. Однако для такого подхода существует проблема, связанная с тем, что число схем памяти увеличивается квадратично по отношению к числу каналов. Поэтому схемы памяти на практике приводят к ограничению пропускной способности переключателя, поскольку при увеличении числа каналов быстро возрастают физические размеры, а также потребление мощности переключателя, становясь при этом чрезмерно высокими.

Этот недостаток имеет также переключатель, описанный в заявке РСТ WO 93/16568. В этой публикации описан переключатель, который переключает на уровне бит и служит в качестве средства переключения работы на уровне байта. В этом переключателе переключение осуществляется в два этапа, сначала производится выбор требуемых байтов и после этого проводится выбор требуемых бит из этих байтов. Входные байты (слова) во вспомогательном переключателе сначала записываются в память речевых сигналов, которая имеет разрядность в один байт, причем их число равно числу бит в байте. Под управлением первого блока управления памятью из каждой памяти речевых сигналов выбирается один байт и этот байт хранится в соответствующей памяти байта. Следовательно, число ячеек памяти байтов равно числу ячеек памяти речевых сигналов. Поэтому под управлением второго блока управления памятью для хранения в памяти бит из каждой памяти байтов выбирается один бит. Таким образом, новое слово РСМ образуется в качестве выхода переключателя.

Однако недостаток, свойственный вышеупомянутым решениям, заключается в том, что необходимо иметь относительно большое число схем памяти, поскольку число копий каждого входного байта должно быть равно числу бит в байте. В результате физические размеры и потребление мощности переключателя также сохраняются относительно высокими. Кроме того, это решение используется в качестве маленького вспомогательного переключателя, находящегося рядом с переключателем, который выполняет переключение, ориентированное на байт, и не используется в качестве независимого (с высокой пропускной способностью) переключателя.

Задачей настоящего изобретения является выполнение усовершенствования в независимом переключателе с однобитовым разрешением для того, чтобы получить значительно более высокую эффективность использования схемы памяти.

Эта задача решается с помощью способа выполнения операции переключения в переключателе в цифровой телекоммуникационной системе, заключающегося в том, что вводят N входных сигналов в переключатель, причем каждый входной сигнал представляет последовательные однобитовые временные интервалы, образующие последовательные фреймы, причем каждый фрейм содержит К однобитовых временных интервалов, запоминают содержимое временных интервалов входных сигналов в памяти в ее соответствующих ячейках, которые определяют при помощи адреса записи, и считывают содержимое из ячеек памяти для вывода сигналов из переключателя, причем N выходных сигналов перед записью распределяют по Х мультиплексорам, в каждом из которых поступающие на него сигналы преобразуют в выходной сигнал, представляющий единую последовательность N•K/X однобитовых временных интервалов входных сигналов, и записывают в соответствующую ячейку упомянутой памяти, которая выполнена разрядностью не менее Х бит, выходные сигналы Х мультиплексоров, соответствующие одноименным разрядам сформированных на выходах мультиплексоров выходных сигналов. При этом сам переключатель для цифровой телекоммуникационной системы, предназначенный для выполнения операции переключения с однобитовым разрешением, имеет входы для N входных сигналов, каждый входной сигнал представляет последовательные однобитовые временные интервалы, образующие последовательные фреймы, а каждый фрейм содержит К однобитовых временных интервалов, и содержит память для хранения содержимого временных интервалов входных сигналов в соответствующих ячейках памяти, которые определяют при помощи адреса записи, средство для считывания содержимого ячеек памяти и средство для выбора заданного бита из считываемых слов, Х мультиплексоров, по которым N входных сигналов распределяются перед записью, причем каждый из мультиплексоров преобразует поступающие на него сигналы в выходной сигнал, представляющий единую последовательность N•K/X однобитовых временных интервалов входных сигналов, а указанная память состоит из ячеек памяти разрядностью по меньшей мере Х бит, и предназначена для хранения содержимого соответствующих выходных сигналов Х мультиплексоров, соответствующих одноименным разрядам сформированных на выходах мультиплексоров выходных сигналов.

Идея изобретения состоит в том, чтобы выполнить переключатель по вышеприведенному способу, более подробно описанному ниже.

Входные линии связи переключателя группируются в мультиплексоры, которые преобразуют входные сигналы переключателя в меньшее число высокоскоростных последовательных сигналов. Эти сигналы сохраняются при помощи записи бит последовательных сигналов в одной и той же ячейке памяти, имеющей разрядность в несколько бит. Это выполняется предпочтительно таким образом, по которому биты, соответствующие друг другу (т.е. биты, приходящие в тот же самый интервал времени записи), хранятся в одной ячейке памяти. В предпочтительном варианте осуществления разрядность ячейки памяти соответствует числу мультиплексоров. Считывание из памяти выполняется в два этапа: сначала выбирают правильный байт из памяти, а затем - требуемый бит из этого байта.

Благодаря такому решению согласно изобретению можно очень эффективно выполнить уплотнение данных в памяти переключателя.

Другими словами, коммутационную память можно реализовать, используя минимум схем памяти, обеспечивая таким образом низкое потребление мощности и небольшие физические размеры переключателя.

Краткое описание чертежей

Сущность изобретения иллюстрируется ссылкой на сопроводительные чертежи, на которых

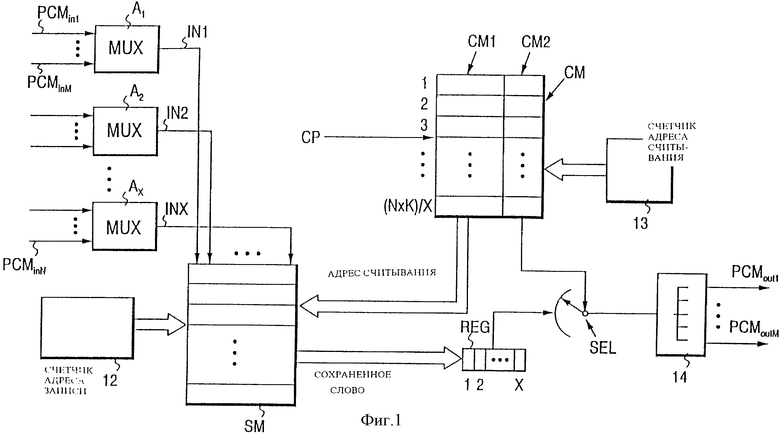

фиг.1 изображает переключатель согласно настоящему изобретению;

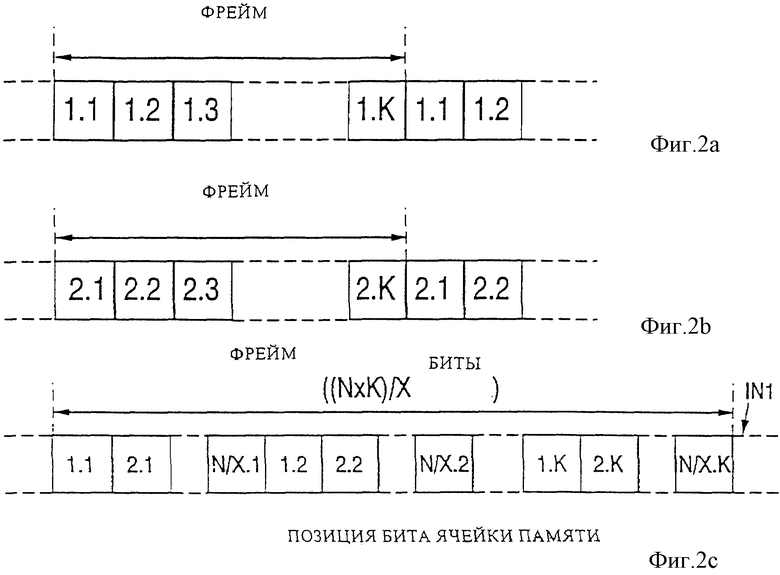

фиг.2а и 2b изображают два входных сигнала в переключателе (фиг.1);

фиг.2с изображает сигнал, который хранится в переключателе (фиг.1);

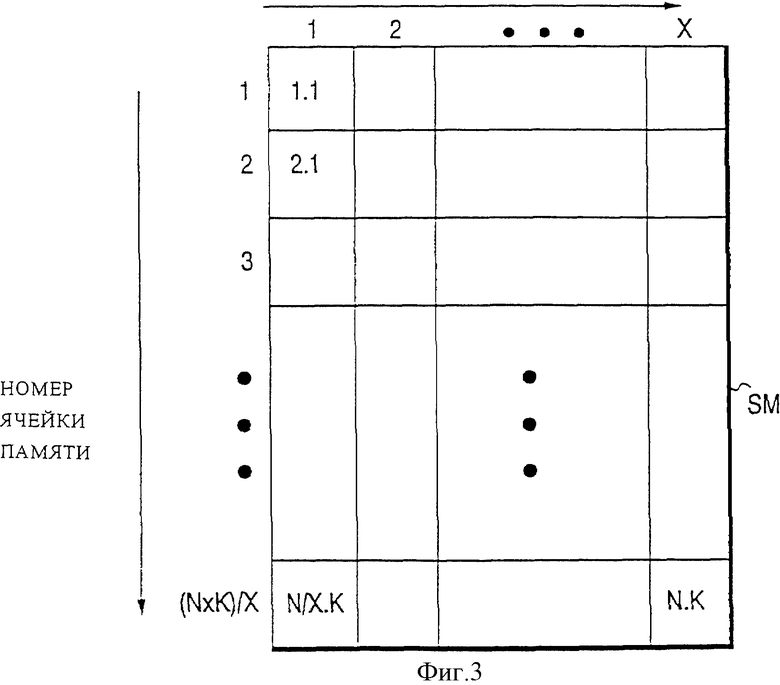

фиг.3 изображает хранение в коммутационной памяти (фиг.1);

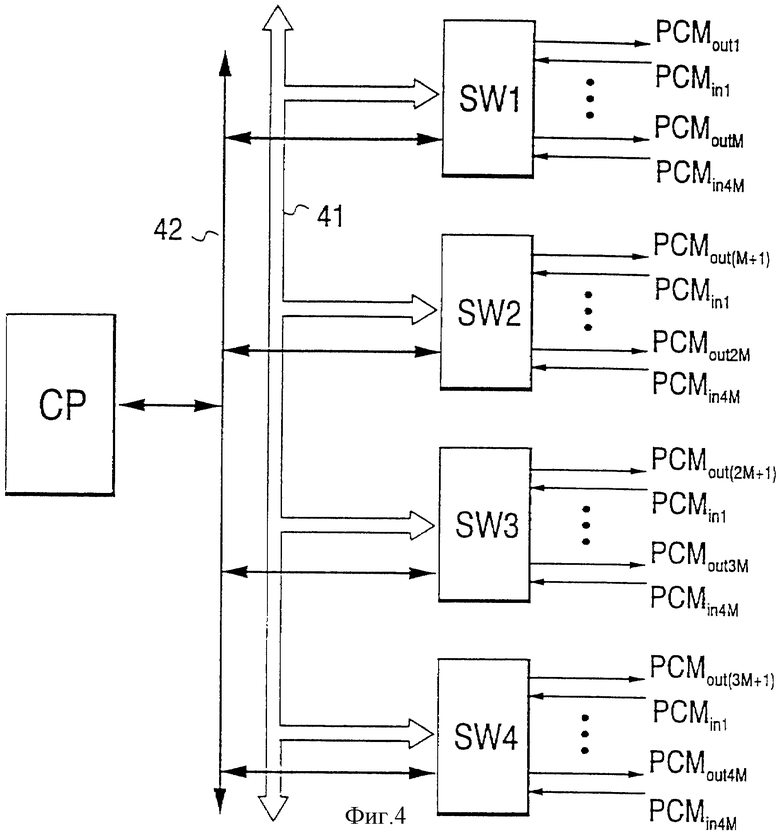

фиг. 4 изображает более экстенсивный переключатель, состоящий из четырех отдельных переключателей.

Подробное описание предпочтительного варианта осуществления

На фиг. 1 изображен переключатель согласно настоящему изобретению с однобитовым разрешением. В этом случае, например, n входных последовательных уплотненных во времени подсоединений или линий связи, которые обозначаются как PCMin1. . . PCMinN, подсоединяются к переключателю. В каждом из этих входных сигналов длина фрейма составляет К бит и, следовательно, отдельный сигнал имеет максимальное число К каналов в соответствии с вышеприведенным описанием.

Отдельный входной сигнал может, например, иметь скорость 2048 кбит/сек в соответствии с рекомендациями G.703 и G704 ITU-T (бывший CCITT) или иметь скорость передачи, кратную этой основной скорости. Если сигнал имеет скорость 2048 кбит/сек, то фрейм может содержать, например, только один канал, имеющий разрядность 256 бит или 256 каналов, имеющих разрядность 1 бит, или комбинацию этих двух экстремальных случаев, В общих чертах фрейм, состоящий из К бит для отдельного выходного сигнала, может содержать 1...К каналов, каждый из которых имеет разрядность, равную n бит, где n - целое число, меньшее или равное К. Далее, в качестве примера выбрана скорость, равная удвоенной основной скорости, при этом каждая входная линия образует последовательные подсоединения при скорости передачи 4096 кбит/сек (К=512), причем предусмотрено 32 из таких сигналов (N=32) и, следовательно, всего существует К•N= 512•32= 16384 входных "однобитовых каналов" в переключателе, каждый из которых имеет пропускную способность 8 кбит/сек. Таким образом, все каналы выполнены из таких однобитовых каналов или их комбинаций. Однако, поскольку переключатель изобретения выполняет переключение из всех каналов для одного однобитового "субканала" за период времени, то этот однобитовый канал называется основным каналом в этом контексте (хотя он формирует только часть высокоскоростного канала).

Входные линии разделяются в мультиплексорах A1...Ax, при этом имеется Х мультиплексоров. Следовательно, существует М=N/X подобных сигналов в каждом мультиплексоре. Таким образом, отношение входных сигналов и мультиплексоров равно (предпочтительно) такому значению, при котором сигналы можно разделить поровну между мультиплексорами. Каждый мультиплексор преобразовывает входные сигналы в последовательный по виду сигнал и, следовательно, скорость передачи бит на выходе каждого мультиплексора равна значению N/X скорости передачи бит входных сигналов. Число Х может быть равно, например, 4, 8 или 16, и следующем примере выбрано Х=4.

На фиг. 2а и 2b изображены первый и второй входные сигналы для первого мультиплексора (A1), то есть на фиг.2а показан входной сигнал, поступающий из линии связи PCMin1 и на фиг.2b показан входной сигнал из линии связи РСМin2. Каждый бит обозначается символами х.y, где число х перед полным окончанием показывает последующее число входного сигнала или линии связи в мультиплексоре, и число y после полного окончания показывает последовательное число бит внутри структуры фрейма сигнала (1≤y≤К).

Сигнал IN1 типа, который показан на фиг.2с, вырабатывается на выходе первого мультиплексора (A1), включает в себя первоначально первый бит от каждого входного сигнала, после этого второй бит от каждого входного сигнала и т.д. и, наконец, К-ый бит от каждого входного сигнала (имеется N/X входных сигналов). Соответственно, каждый мультиплексор преобразовывает входные сигналы в единственный последовательный выходной, представляющий единую последовательность N•К/Х, сигнал. Следовательно, существует в итоге Х таких выходных сигналов, которые обозначены на фиг.1 как IN1...INX.

Выходные сигналы мультиплексоров хранятся в коммутационной памяти SM, которая имеет в общем (N•К)/X ячеек памяти, каждая из которых имеет разрядность Х бит. На фиг.3 изображена коммутационная память в режиме хранения. В каждом временном интервале для входных сигналов (то есть выходных сигналов мультиплексоров), запись выполняется в той же самой ячейке памяти, которая имеет разрядность Х бит таким способом, что в первом временном интервале фрейма данные записываются в ячейку 1 памяти, во втором временном интервале фрейма - записываются в ячейку 2 памяти, и т.д., и в последнем временном интервале фрейма - в ячейку (N•К)/X памяти. (Следует отметить, что в этом случае временной интервал соответствует одному основному каналу.) Следовательно, содержимое выходного фрейма сигнала первого мультиплексора (A1) сохраняется в позициях 1 бита, содержимое выходного фрейма сигнала второго мультиплексора (А2) сохраняется в позициях 2 бита, и т.д., и содержимое фрейма для последнего мультиплексора (Аx) сохраняется в последней позиции (X) бит в ячейках коммутационной памяти.

Адреса записи вырабатываются в счетчике 12 записи адреса, который осуществляет приращение (синхронно с тактовым сигналом на стороне записи) непрерывно от 1 до (N•К)/X (в этом конкретном случае 4096). Операция записи выполняется циклически с адресами, которые вырабатывает счетчик 12.

Существует одна выходная мультиплексированная линия 8•4М (то есть 16 стандартных сигналов РСМ 2М), выходящая из переключателя, показанного фиг.1. Одна ячейка памяти выполнена в памяти SM управления переключателя для каждого бита, который выводится в линию, то есть существует общее число ячеек памяти N•К/Х. Память управления считывают поэтапно с помощью счетчика 13 записи адреса. Счетчик непрерывно выполняет приращение от одного до N•К/Х. Каждая ячейка памяти в памяти СМ управления состоит из двух частей таким образом, что первая часть СМ1 хранит адрес считывания коммутационной памяти SM и биты второй части СМ2 управляют селектором SEL. Данные, которые хранятся в первой части каждой ячейки памяти показывают, сохранен ли адрес коммутационной памяти Х-битового слова, содержимое бит которого (то есть основная скорость передачи канала 8 кбит/сек) необходимо переключать в соответствующем выходном канале.

Следовательно, соединения между двумя каналами устанавливаются в случае, когда память СМ управления считывают циклически по адресам, которые вырабатываются счетчиком 13, и адреса считывания для коммутационной памяти SM получаются из данных памяти управления. В переключающей памяти запись в памяти постоянно изменяют за счет считывания из нее. К тому же, вышеупомянутая система известна из переключателей, ориентированных на байт.

Посредством адреса считывания, который получается из первой части памяти управления, содержимое соответствующей ячейки памяти (в коммутационной памяти) считывается в регистре REG, который имеет разрядность Х бит. Посредством слова управления, которое получается из второй части памяти управления, с другой стороны, корректный бит этого слова, который ввели в регистр, выбирают с помощью селектора SEL. Следовательно, одно слово считывается в регистре за каждый выходной бит, и из них выбирается правильный бит.

Переключение информации, которая хранится в памяти управления, выполняется из модуля СР процессора (не показано), которое управляет оборудованием и может принимать информацию, например, через сигнальную сеть, к которой подсоединено оборудование. Поскольку поддержка содержимого памяти управления осуществляется известным в технике способом, который не относится фактически к идее изобретения, то ее подробное описание в этом контексте опущено.

Окончательно последовательные подсоединения для выходного направления формируются из последовательных данных, которые получаются из селектора SEL известным в технике способом в модуле 14 демультиплексора. Поскольку формирование выходящих подсоединении не входит фактически в идею изобретения, то связанное с этим дальнейшее подробное описание будет опущено.

Ряд выходных подсоединений М основного блока вышеописанного переключателя равно N/X, другими словами равно числу подсоединении мультиплексированных при помощи одного мультиплексора. Число выходных подсоединений можно продублировать при помощи дублирующих частей SM, CM, REG и SEL, показанных на фиг.1. В этом случае, например, если согласно вышеупомянутому предпочтительному варианту осуществления требуется матрица переключения 64 РСМ • 64 РСМ (РСМ обозначается стандартный сигнал РСМ 2М), то необходимо иметь четыре параллельно соединенные комбинации "коммутационная память - память управления - регистр - селектор", причем каждый переключает одну выходную мультиплексированную линию 8•4М. В течение этапа записи четырехбитовый выходной сигнал 8•4М из мультиплексора A1-А4 записывается непрерывно в каждой из четырех переключающихся памятей под управлением общего счетчика записи адреса. Во время этапа считывания слово, соответствующее требуемому переключению, которое хранится в коммутационной памяти, соответствующей каждой мультиплексированной линии 8•4М, хранится в регистре, который относится к соответствующей линии. Селектор, соответствующий линии, выбирают под управлением памяти управления бит в соответствии с требуемым подсоединением из этого регистра. Это позволяет подключить требуемое подсоединение, состоящее из четырех входных мультиплексированных линий 8•4М, к четырем выходным линиям 8•4М. Если скорость считывания коммутационной памяти SM можно увеличить до четырехкратной свертки относительно скорости записи, то коммутационную память не обязательно дублировать, но все четыре комбинации "память управления - регистр - селектор" могут использовать в общем переключающую память.

В соответствии с изобретением входные подсоединения РСМ можно легко добавить к комбинации, описанной выше, без добавления к фактическому оборудованию переключения. Вышеупомянутый переключатель 64 РСМ • 64 РСМ, например, можно легко расширить до переключателя 256 PSC • 64 РСМ только за счет использования четырехкратного числа свертки входных мультиплексоров и имея при этом память с разрядностью шестнадцать бит в коммутационной памяти (памятях).

Например, матрица размером 256 РСМ • 256 РСМ соответственно приводится к виду, показанному на фиг.4, за счет использования параллельно соединенных четырех переключателей SW1...SW4 РСМ 256 PSM • 64 РСМ, как описано выше. Все переключатели управляются при помощи процессора СР управления через шину 42 управления. Процессор управления также распределяет необходимые тактовые сигналы для всех переключателей. Каждый переключатель (SW) преобразовывает входные последовательные сигналы PSMin1...PSMin4M до общей шины 42 данных, которая в этом случае имеет разрядность 4Х бит, и некоторый (в этом случае четвертый) из сигналов выводится из каждого переключателя. В каждом переключателе содержимое шины данных записывается в коммутационную память, которая, предпочтительно, в этом случае имеет разрядность, равную числу сигналов (4Х), проходящих по шине 42 данных. В каждом основном переключателе слово, соответствующее требуемому каналу, считывается из коммутационной памяти, и выбранный бит выбирается из этого слова при помощи селектора. Вышеописанный высокоэффективный переключатель можно, естественно, выполнить также в виде одного физического модуля.

В каждом случае число последовательных сигналов (РСМ), которые будут переключаться, и скорость памяти управления/переключения, которая используется для определения, сколько копий необходимо извлечь из коммутационной памяти.

Хотя изобретение описание со ссылками на примеры в целях иллюстрации, очевидно, что изобретение не ограничивается этими примерами и может изменяться в пределах объема изобретения, которое раскрыто в сопроводительной формуле изобретения.

Изобретение относится к средствам и способам коммутации в телекоммуникационных системах, в частности к переключателю и способу выполнения операции переключения с однобитовым разрешением в цифровой телекоммуникационной системе. Техническим результатом является расширение функциональных возможностей. Переключатель содержит память для хранения содержимого временных интервалов входных сигналов, средство для считывания содержимого ячеек памяти, средство для выбора заданного бита из считываемых слов, Х мультиплексоров. Способ описывает работу данного переключателя. 2 с. и 5 з.п. ф-лы, 6 ил.

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

| ЦИФРОВОЕ КОММУТАЦИОННОЕ ПОЛЕ | 1991 |

|

RU2012153C1 |

| ЕР 0285777 А2, 12.10.1988 | |||

| US 4718058 А, 05.01.1988 | |||

| СПОСОБ ПОЛУЧЕНИЯ ХЛОРГИДРАТОВ2 | 1972 |

|

SU418475A1 |

| Грунтонос для отбора проб мягких горных пород | 1970 |

|

SU483516A1 |

Авторы

Даты

2002-03-27—Публикация

1996-09-04—Подача