Изобретение относится к технике электрической связи и может использоваться в системах автоматической коммутации.

Цель изобретения - уменьшение временных задержек сигнала, передаваемого во временном канале через звеньевое цифровое коммутационное поле, и упрощение устройства путем уменьшения количества ячеек информационного запоминающего устройства.

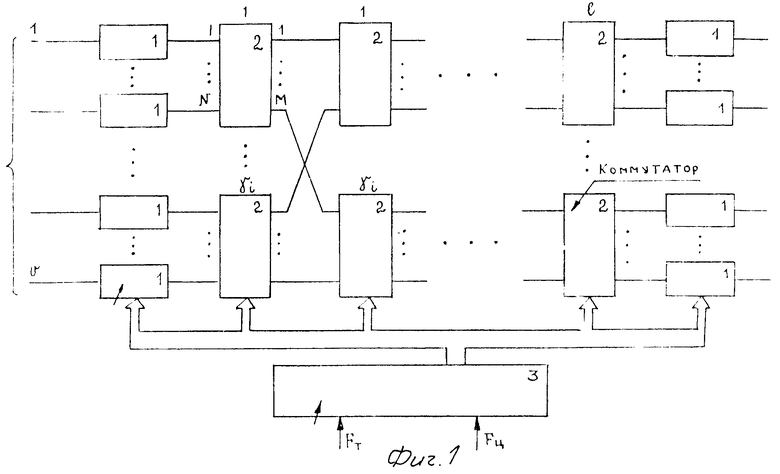

На фиг. 1 изображена структурная схема предлагаемого цифрового коммутационного поля.

Цифровое коммутационное поле содержит (V + V') блоков преобразования формата 1, l звеньев коммутаторов 2 по γi коммутаторов 2 в каждом звене цифрового коммутационного поля (  ji коммутаторов 2), блок синхронизации 3, при этом во входе V блоков преобразования формата 1 включены V линий, имеющих n временных каналов с многоразрядной организацией, выходы V блоков преобразования формата 1 соединены с соответствующими входами γi коммутаторов 2 первого звена цифрового коммутационного поля, выходы γi коммутаторов 2 последнего (l) звена цифрового коммутационного поля соединены линиями с временным уплотнением с входами других V' блоков преобразования формата 1, в выходы которых включены V' линий, имеющих m временных каналов с многоразрядной организацией, входы управления (V+V') блоков преобразования формата 1 всех коммутаторов 2 цифрового коммутационного поля соединены многоразрядной шиной с выходом блока синхронизации 3, на первый и второй входы которого поступают соответственно сигналы цикловой Fц 1/Тцсинхронизации и тактовой синхронизации FТ= b/tb от генератора тактовых импульсов.

ji коммутаторов 2), блок синхронизации 3, при этом во входе V блоков преобразования формата 1 включены V линий, имеющих n временных каналов с многоразрядной организацией, выходы V блоков преобразования формата 1 соединены с соответствующими входами γi коммутаторов 2 первого звена цифрового коммутационного поля, выходы γi коммутаторов 2 последнего (l) звена цифрового коммутационного поля соединены линиями с временным уплотнением с входами других V' блоков преобразования формата 1, в выходы которых включены V' линий, имеющих m временных каналов с многоразрядной организацией, входы управления (V+V') блоков преобразования формата 1 всех коммутаторов 2 цифрового коммутационного поля соединены многоразрядной шиной с выходом блока синхронизации 3, на первый и второй входы которого поступают соответственно сигналы цикловой Fц 1/Тцсинхронизации и тактовой синхронизации FТ= b/tb от генератора тактовых импульсов.

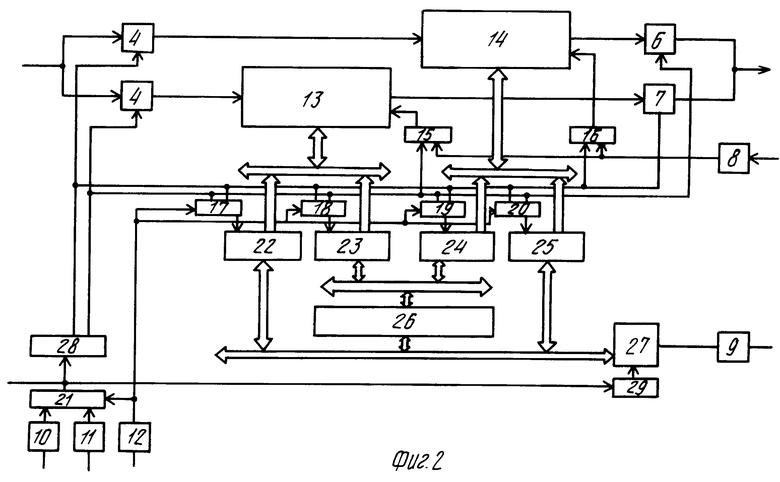

На фиг. 2 изображена функциональная схема блока преобразования формата 1.

Блок преобразования формата 1 содержит девять буферных блоков 4-12, два запоминающих блока 13 и 14, два элемента ИЛИ 15 и 16, пять мультиплексоров 17-21, четыре коммутатора 22-25, блок памяти 26, счетчик 27, триггер 28, элемент НЕ 29, причем во входы буферных блоков 4 и 5 и в выходы буферных блоков 6 и 7 включены линии, содержащие временные каналы с многоразрядной организацией, выход буферного блока 4 соединен с информационным входом запоминающего устройства 14, информационный выход которого соединен с входом буферного блока 6, выход буферного блока 5 соединен с информационным входом запоминающего блока 13, информационный выход которого соединен с входом буферного блока 7.

Выход триггера 28 соединен с управляющим входом буферного блока 4, управляющим входом буферного блока 7, вторыми входами мультиплексоров 17-20, первым входом элемента ИЛИ 16, инверсный выход триггера 28 соединен с управляющим входом буферного блока 5, управляющим входом буферного блока 6, первым входом элемента ИЛИ 15 и первыми входами мультиплексоров 17-20, выход схемы ИЛИ 15 соединен с управляющим входом запоминающего блока 13, выход элемента ИЛИ 16 соединен с управляющим входом запоминающего блока 14, выходы коммутаторов 22 и 23 соединены с адресным входом запоминающего блока 13 многоразрядной шиной. Выходы коммутаторов 24 и 25 соединены с адресным входом запоминающего блока 14 многоразрядной шиной, управляющие входы мультиплексоров 17-21 соединены с выходом буферного блока 13, вторые входы элемента ИЛИ 15 и 16 соединены с выходом буферного блока 8, входы коммутаторов 23 и 24 соединены с выходом блока памяти 26 многоразрядной шиной, входы коммутаторов 22, 25 и адресный вход блока памяти 26 соединены с выходом счетчика 27, вход сброса которого соединен с выходом элемента НЕ 29, счетный вход счетчика 27 соединен с выходом буферного блока 9, выход мультиплексора 21 соединен с входами триггера 28 и элемента НЕ 29, первый и второй входы мультиплексора 21 соединены соответственно с выходами буферных блоков 10 и 11.

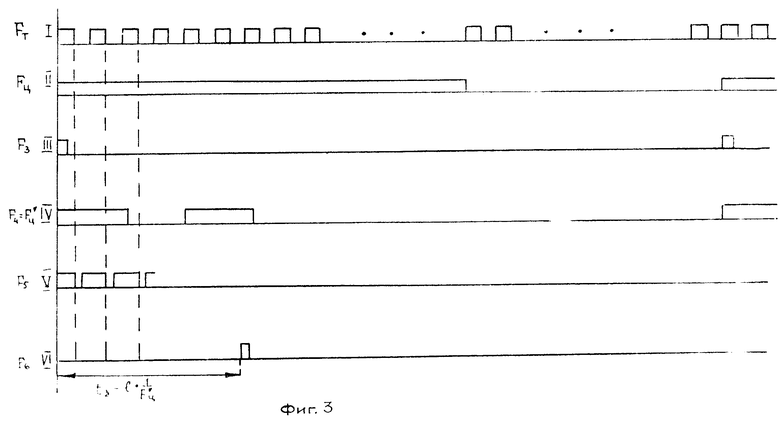

На фиг. 3 представлены временные диаграммы тактового и циклового сигналов синхронизации, поступающих от генератора тактовых импульсов, а также временные диаграммы сигналов управления, формируемых блоком синхронизации 3.

Сигнал 1 - это тактовый сигнал, поступающий от генератора тактовых импульсов, FT= b/tb. Сигнал II - сигнал цикловой синхронизации, Fц = 1/Тц. Сигнал III - сигнал управления для блоков преобразования формата 1 на входе цифрового коммутационного поля. Сигнал III имеет период, равны 1/Fц, при этом длительность импульса τ=  . Сигнал IV - это цикловой сигнал для коммутаторов 2 цифрового коммутационного поля, его частота равна Fц= b Fц = FT/n. Поскольку блок преобразования формата 1 снижает разрядность временного канала линии, то соответственно увеличивается частота циклового сигнала до Fц. Сигнал V - сигнал управления записью в запоминающие блоки 13 и 14 блока преобразования формата 1, поступающий на вторые входы элемента ИЛИ 15 и 16. Период сигнала V равен Т5= 1/Fц, по длительности нулевой посылки уменьшен для избежания искажений при совпадении фронтов разных управляющих сигналов. Сигнал VI - сигнал управления для блоков преобразования формата 1 на выходе цифрового коммутационного поля. Сигнал VI поступает на вход триггера 28 через буферный блок 1 и мультиплексор 21. Сигнал VI отличается от сигнала III тем, что имеет задержку τз= l/F4, так как в каждом звене цифрового коммутационного поля сигнал задерживается на величину 1/F4 из-за этого начало цикла в каждой линии, включенной в выходы последнего звена цифрового коммутационного поля, будет сдвинуто на величину этой задержки τз= l/F4.

. Сигнал IV - это цикловой сигнал для коммутаторов 2 цифрового коммутационного поля, его частота равна Fц= b Fц = FT/n. Поскольку блок преобразования формата 1 снижает разрядность временного канала линии, то соответственно увеличивается частота циклового сигнала до Fц. Сигнал V - сигнал управления записью в запоминающие блоки 13 и 14 блока преобразования формата 1, поступающий на вторые входы элемента ИЛИ 15 и 16. Период сигнала V равен Т5= 1/Fц, по длительности нулевой посылки уменьшен для избежания искажений при совпадении фронтов разных управляющих сигналов. Сигнал VI - сигнал управления для блоков преобразования формата 1 на выходе цифрового коммутационного поля. Сигнал VI поступает на вход триггера 28 через буферный блок 1 и мультиплексор 21. Сигнал VI отличается от сигнала III тем, что имеет задержку τз= l/F4, так как в каждом звене цифрового коммутационного поля сигнал задерживается на величину 1/F4 из-за этого начало цикла в каждой линии, включенной в выходы последнего звена цифрового коммутационного поля, будет сдвинуто на величину этой задержки τз= l/F4.

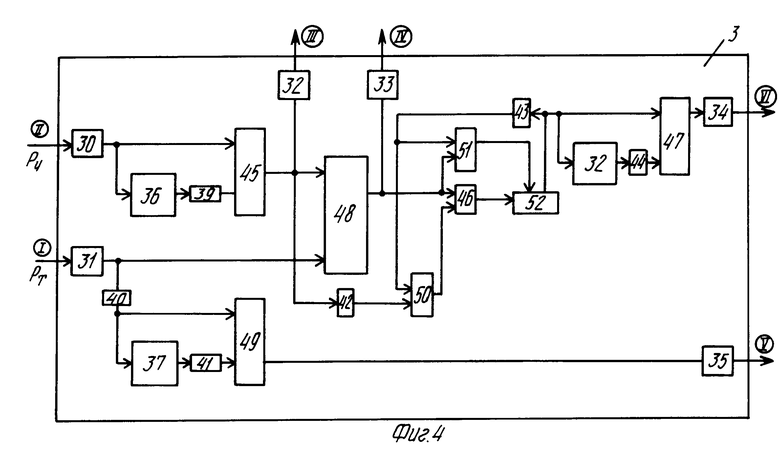

На фиг. 4 изображена функциональная схема блока синхронизации 3.

Блок синхронизации 3 содержит шесть буферных блоков 30-35, три блока задержки 36-38, шесть элементов НЕ 39-44, три элемента И 45-47, программируемый счетчик 48, элемент И-НЕ 49, триггер 50, элемент ИЛИ 51, регистр сдвига 52. Сигнал II цикловой синхронизации поступает через буферный блок 30 на вход блока задержки 36 и первый вход элемента И 45, выход блока задержки 36 через элемент НЕ 39 соединен с вторым входом элемента И 45, выход которой соединен с входами буферного блока 32, элемента НЕ 42 и с первым входом программируемого счетчика 48. Сигнал I тактовой синхронизации поступает на второй вход программируемого счетчика 48 и через элемент НЕ 40 - на вход блока задержки 37 и первый вход элемента И-НЕ 49, выход блока задержки 37 соединен с вторым входом элемента И-НЕ 49 через элемент НЕ 41, выход элемента 49 соединен с входом буферного блока 35, с выхода которого в цифровое коммутационное поле поступает сигнал V. Сигналы III, IV, VI поступают в цифровое коммутационное поле соответственно с выходов буферных блоков 32, 33, 34, выход элемента НЕ 42 соединен с входом установки триггера 50, выход которого соединен с вторым вводом элемента И 46, выход программируемого счетчика 48 соединен с входом буферного блока 33, первым входом элемента И 46 и вторым входом элемента ИЛИ 51, первый вход которой соединен с входом сброса триггера 50 и с выходом элемента НЕ 43, выход элемента И 46 соединен с тактовым входом регистра сдвига 52, выход элемента ИЛИ 51 соединен с входом сброса регистра сдвига 52, выход которого соединен с входами элемента НЕ 43, блока задержки 38 и с первым входом элемента И 47, выход блока задержки 38 через элемент НЕ 44 соединен с вторым входом элемента И 47, выход которой соединен с входом буферного блока 34.

Работает цифровое коммутационное поле следующим образом.

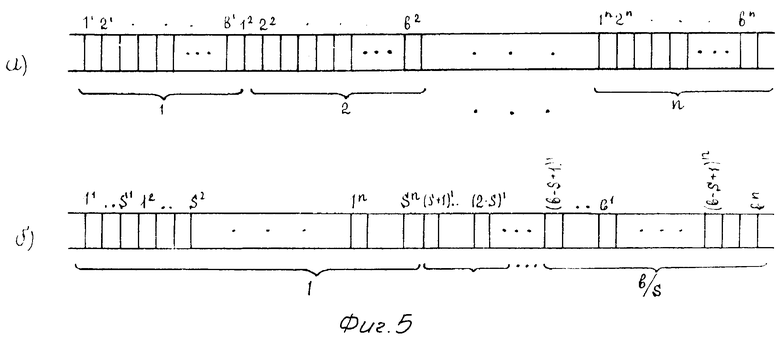

Блок преобразования формата 1 осуществляет преобразование формата цифрового сигнала (см. фиг. 5). При этом цикл уменьшается до τ= Тц/b, где b - число временных позиций в одном канале. Этот цифровой поток поступает на входы коммутаторов 2, которые при коммутации данных цифровых потоков вносят задержку tз=  , а суммарная задержка во всем цифровом коммутационном поле Ткп'= l·Tц/b = l·tg'. На выходе цифрового коммутационного поля блок преобразования формата 1 осуществляет обратное преобразование цифрового потока в исходный формат. Так как блок преобразования формата 1 вносит постоянную временную задержку, равную Тц, то общая временная задержка в предложенном цифровом коммутационном поле будет составлять

, а суммарная задержка во всем цифровом коммутационном поле Ткп'= l·Tц/b = l·tg'. На выходе цифрового коммутационного поля блок преобразования формата 1 осуществляет обратное преобразование цифрового потока в исходный формат. Так как блок преобразования формата 1 вносит постоянную временную задержку, равную Тц, то общая временная задержка в предложенном цифровом коммутационном поле будет составлять

TкпΣ= T +2Tц.

+2Tц.

Блок синхронизации 3 формирует из тактовых сигналов 2 МГц и 8 кГц (см. фиг. 3, сигналы I и II), тактовые сигналы для работы всех блоков цифрового коммутационного поля (см. фиг. 3, сигналы III-VI).

Блок преобразования формата 1 работает следующим образом.

Блок преобразования формата 1 содержит два запоминающих блока 13 и 14, работа которых описывается двумя фазами: фаза считывания, фаза записи. При этом установка запоминающих блока 13 и 14 в нужную фазу производится триггером 28, который осуществляет переключение своих состояний на выходах по положительному фронту импульсов, поступающих на его вход, с выхода мультиплексора 21. Таким образом, каждый цикл одного запоминающего блока работает на запись, а другого - на считывание, а в следующем цикле наоборот.

Как видно из фиг. 1, блок преобразования формата 1 может быть расположен или на входе или на выходе цифрового коммутационного поля. Если блок преобразования формата 1 установлен на входе цифрового коммутационного поля, то на вход буферного блока 12 необходимо подать логический ноль, который с его выхода поступает на управляющие входы мультиплексоров 17-21. Мультиплексоры 17-21 подключают свои выходы к первому входу. При этом на вход триггера 28 поступает сигнал III. Если блок преобразования формата 1 установлен на входе цифрового коммутационного поля, то преобразование формата цифрового потока, поступающего по линии с временным уплотнением, включенной в его входы, производится посредством последовательной записи и считывания в нужном порядке. Если блок преобразования формата 1 установлен на выход цифрового коммутационного блока, то на вход буферного блока 13 необходимо подать логическую единицу, которая с его входа поступает на управляющие входы мультиплексоров 17-21. Мультиплексоры 17-21 подключают свои выходы к второму входу. При этом на вход триггера 28 поступает сигнал VI. Если блок преобразования формата 1 установлен на выходе цифрового коммутационного поля, то преобразование формата цифрового потока производится посредством записи в определенном порядке и последовательного считывания. Формирование адресов для записи и считывания из запоминающего блока 13 и 14 производится блоком памяти 26, счетчиком 27 и коммутаторами 22-25.

Если блок преобразования формата 1 установлен на входе цифрового коммутационного поля, во вход блока преобразования формата 1 включается линия с n временными каналами по b разрядов в каждом, а выход блока преобразования формата 1 соединен с входом коммутатора 2 первого звена цифрового коммутационного поля линией с временным уплотнением. При этом на управляющие входы мультиплексоров 17-21 поступает логический ноль. Первые входы мультиплексоров 17-21 соединены с их выходами. Пусть на выходе триггера 28 - логическая единица, а на инверсном выходе - логический ноль. Логическая единица с выхода триггера 28 поступает на управляющие входы буферных блоков 4 и 7 и переводит их в третье состояние, а также поступает на первый вход элемента ИЛИ 16, запрещая прохождение сигнала записи на управляющий вход запоминающего блока 14. Логический ноль с инверсного выхода триггера 28 поступает на управляющие входы буферных блоков 5 и 6, которые подключают свои диоды к выходам, а также поступает на первые вход элемента ИЛИ 15, разрешая прохождение сигнала записи на управляющий вход запоминающего устройства 13.

Таким образом, запоминающий блок 13 работает в фазе записи, а запоминающий блок 14 - в фазе считывания. На выходах счетчика 27 в соответствии с тактовыми импульсами сигнала 1, поступающими на его счетный вход через буферный блок 9, появляются последовательные адреса, которые поступают на входы коммутаторов 22 и 25 и на адресный вход блока памяти 26, на информационном выходе которого появляются адреса в определенной последовательности, которые поступают на входы коммутаторов 23 и 24. Так как данный блок преобразования формата 1 расположен на входе цифрового коммутационного поля и к выходам мультиплексоров 17-21 подключен первый вход мультиплексоров 17-21, то на управляющие входы коммутаторов 22 и 24 поступает логический ноль с инверсного выхода триггера 26, подключая входы коммутаторов 22 и 24 к выходам, а на управляющие входы коммутаторов 23 и 25 поступает логическая единица с выхода триггера 28, отключая входы коммутаторов 23 и 25 от их выходов. Сигналы с выходов коммутаторов 22 и 24 поступают соответственно на адресные входы запоминающих блоков 13 и 14. При этом на информационном выходе запоминающего блока 14, а также на выходе буферного блока 6 появляется содержимое ячеек в соответствии с поступающими адресами, а в запоминающем блоке 13 записываются в ячейки, имеющие соответствующие адреса, данные, поступающие по временным каналам линии, включенной во вход блока преобразования формата 1, в момент времени, определяемый низким уровнем управляющего сигнала, поступающего через элемент ИЛИ 15 на управляющий вход запоминающего блока 13 от блока синхронизации 3.

При поступлении очередного импульса циклового сигнала Fц (сигнал II) переключается триггер 28 и обновляется счетчик 27, при этом на выходе триггера 28 появляется логический ноль, на инверсном выходе - логическая единица, что переводит запоминающий блок 14 в режим записи, а запоминающий блок 13 - в режим считывания. При этом информация с выходов коммутаторов 23 и 25 поступает соответственно на адресные входы запоминающих блоков 13 и 14. Так как входы шинных формирователей 23 и 24 включены в информационные выходы блока памяти 26, то, как следует из описания работы блока преобразования формата 1, запись в запоминающие блоки 13 и 14 производится последовательно, а считывание - в определенном порядке, определяемом содержимым блока памяти 26, что приводит к появлению на выходе блока преобразования формата 1 в этом случае цифрового потока (см. фиг. 5, б).

Если блок преобразования формата 1 находится на выходе цифрового коммутационного поля, то на управляющие входы мультиплексоров 17-21 поступает логическая единица, которая проключает вторые входы мультиплексоров 17-21 и их выходом. Это приводит к тому, что в фазе записи в запоминающие блоки 13 и 14 адресная информация поступает соответственно через коммутаторы 23 и 24, а в режиме считывания из запоминающих блоков 13 и 14 - через коммутаторы 22 и 25. Это приводит к установлению на выходе блока преобразования формата 1 исходного цифрового потока (см. фиг. 5, а).

Блок синхронизации 3 работает следующим образом.

Сигнал II поступает через буферный блок 30 на первый вход элемента И 45 и вход блока задержки 36, на выходе элемента И 45 формируется сигнал III, длительность единичной посылки которого определяется величиной задержки блока задержки 36. Сигнал III поступает на вход сброса программируемого счетчика 48, синхронизируя начало его работы. На счетный вход программируемого счетчика 48 поступает сигнал 1 через буферный блок 31 от генератора тактовых импульсов. Программируемый счетчик 48 производит деление частоты сигнала 1 на значение n (число временных каналов во входящей в блок преобразования формата 1 линии). На выходе программируемого счетчика появляется сигнал IV. Сигнал I с выхода буферного элемента 31 поступает также через элемент НЕ 40 на первый вход схемы И-НЕ 49 и вход блока задержки 37. На выходе элемента И-НЕ 49 формируется сигнал V. Инверсия поступающего сигнала в элементах НЕ 40 и И-НЕ 49 позволяет сократить длительность нулевой посылки исходного сигнала до величины, определяемой блоком задержки 37. Сигнал III с выхода элемента И 45 поступает через элемент НЕ 42 на вход установки S RS-триггера 50. Нулевая посылка этого сигнала приводит к появлению на выходе RS-триггера 50 логической единицы, которая поступает на второй вход элемента И 46, разрешая прохождение сигнала IV на тактовый вход регистра сдвига 52. На выходе регистра сдвига 52 через время tз= l·  появляется логическая единица, которая поступает на вход элемента НЕ 43, логический ноль с выхода которой поступает на первый вход элемента ИЛИ 51, а также на вход сброса R RS-триггера 50, на выходе которого появляется логический ноль. Логическая единица с выхода регистра сдвига 52 поступает также на первый вход элемента И 47 и вход блока задержки 38. При этом появлении на втором входе элемента ИЛИ 51 логический ноль с выхода элемента ИЛИ 51 поступает на вход сброса регистра сдвига 52. На выходе элемента И 47 формируется сигнал IV, длительность единичной посылки которого определяется величиной задержки блока задержки 38.

появляется логическая единица, которая поступает на вход элемента НЕ 43, логический ноль с выхода которой поступает на первый вход элемента ИЛИ 51, а также на вход сброса R RS-триггера 50, на выходе которого появляется логический ноль. Логическая единица с выхода регистра сдвига 52 поступает также на первый вход элемента И 47 и вход блока задержки 38. При этом появлении на втором входе элемента ИЛИ 51 логический ноль с выхода элемента ИЛИ 51 поступает на вход сброса регистра сдвига 52. На выходе элемента И 47 формируется сигнал IV, длительность единичной посылки которого определяется величиной задержки блока задержки 38.

Предлагаемое устройство позволяет уменьшить временные задержки сигнала, передаваемого во временном канале через звеньевое цифровое коммутационное поле, и сократить объем оборудования путем уменьшения количества ячеек информационного запоминающего устройства.

Использование: в технике электрической связи, в системах автоматической коммутации. Сущность изобретения: устройство содержит v+v′ блоков преобразования формата, где v количество входящих, v′ количество исходящих линий, l звеньев коммутаторов по γi коммутаторов в каждом звене, один блок синхронизации. Блок преобразования формата содержит девять буферных блоков, два запоминающих блока, два элемента ИЛИ, пять мультиплексоров, четыре коммутатора, один блок памяти, один счетчик, один триггер, один элемент НЕ. Цель изобретения - уменьшение временных задержек сигнала, передаваемого во временном канале через звеньевое цифровое коммутационное поле, и упрощение устройства путем уменьшения количества ячеек информационного запоминающего устройства. 5 ил.

ЦИФРОВОЕ КОММУТАЦИОННОЕ ПОЛЕ, содержащее l звеньев коммутаторов по γi коммутаторов в каждом звене, при этом V входящих линий с временным уплотнением, содержащих n многоразрядных каналов, подключены к соответствующим входам γi коммутаторов первого звена цифрового коммутационного поля, а V1 исходящих линий с временным уплотнением, содержащих по m каналов в каждой из V1 исходящих линий, подключены к соответствующим выходам γi коммутаторов последнего звена цифрового коммутационного поля, причем входы каждого коммутатора последующего звена соединены с соответствующими выходами коммутатора предыдущего звена линией с временным уплотнением, отличающееся тем, что, с целью уменьшения временных задержек сигнала, передаваемого во временном канале через звеньевое цифровое коммутационное поле, и упрощения устройства путем уменьшения количества ячеек информационного запоминающего устройства, введены V + V1 блоков преобразования формата и блок синхронизации, причем к входам V блоков преобразования формата включены V соответствующих входящих линий, а выходы V блоков преобразования формата соединены с соответствующими входами γi коммутаторов первого звена, а выходы V1 блоков преобразования формата подключены к соответствующим выходам γi коммутаторов последнего звена, при этом к выходам V1 блоков преобразования формата подключены соответствующие V1 исходящие линии, причем блок преобразования формата содержит девять буферных блоков, два запоминающих блока, два элемента ИЛИ, пять мультиплексоров, четыре коммутатора, блок памяти, счетчик, триггер, элемент НЕ, причем объединенные входы первого и второго буферных блоков и объединенные выходы третьего и четвертого буферных блоков являются соответственно входом и выходом блока преобразования формата, а выход первого буферного блока соединен с информационным входом второго запоминающего блока, информационный выход которого соединен с входом третьего буферного блока, а выход второго буферного блока соединен с информационным входом первого запоминающего блока, информационный выход которого соединен с входом четвертого буферного блока, а прямой выход триггера соединен с управляющими входами первого и четвертого буферных блоков, вторыми входами первого - четвертого мультиплексоров, первым входом второго элемента ИЛИ, а инверсный выход триггера соединен с управляющими входами второго и третьего буферных блоков, первым входом первого элемента ИЛИ и первыми входами первого - четвертого мультиплексоров, при этом выход первого элемента ИЛИ соединен с управляющим входом первого запоминающего блока, выход второго элемента ИЛИ - с управляющим входом второго запоминающего блока, причем выходы первого и второго коммутаторов соединены с адресным входом первого запоминающего блока многоразрядной шиной, а выходы третьего и четвертого коммутаторов - с адресным входом второго запоминающего блока многоразрядной шиной, при этом управляющие входы всех мультиплексоров соединены с выходом девятого буферного элементы, а вторые входы первого и второго элементов ИЛИ - с выходом пятого буферного блока, причем входы второго и третьего коммутаторов соединены с выходом блока памяти многоразрядной шиной, а входы первого и второго коммутаторов и адресный вход блока памяти соединены с выходом счетчика, вход сброса которого соединен с выходом элемента НЕ, а счетный вход - с выходом шестого буферного блока, при этом выход пятого мультиплексора соединен с входами триггера и элемента НЕ, причем первый - третий входы пятого мультиплексора соединены соответственно с выходами седьмого - девятого буферных блоков, при этом входы управления блоков преобразования формата, являющиеся входами пятого - девятого буферных блоков, а также входы управления всех коммутаторов цифрового коммутационного поля соединены многоразрядной шиной с выходом блока синхронизации, первый и второй входы которого являются соответственно входами сигналов тактовой и цикловой синхронизации.

Авторы

Даты

1994-04-30—Публикация

1991-06-11—Подача