Изобретение относится к техническим средствам автоматики и вычислительной техники и может быть использовано для сбора данных, управления и преобразования потоков данных между управляющими вычислительными машинами и объектом управления. В частности, предназначено для сопряжения информационных потоков двух магистралей, с возможностью контролирования работы объекта управления и корректировки информации, поступающей на объект управления. Может быть использовано в системах, связанных с передачей и управлением потоками информации в радиолокационных станциях летательных аппаратов.

Из уровня техники известны различные коммутационные устройства для построения сетей обмена данными. Известен адаптер [1] с блоком перегруппировки данных, содержащий регистр для обмена данными с памятью посредством управляемого смещения, который не осуществляет функцию сопряжения магистралей. Известна параллельная компьютерная система [2], в которой осуществляется управление пакетами заявок по двум параллельным магистралям, но передача данных происходит по одной магистрали. В известном устройстве сортировки информации [3] выполняется функция селекции слов из потока данных, но входная информация поступает по одной магистрали. Известно устройство коммутации для многопроцессорной системы [4], которое выбрано прототипом, содержащее два обрабатывающих процессора, обслуживающий процессор, блок памяти, блок n-канальных адаптеров. Недостатком данной системы является невозможность коммутации параллельных цифровых двунаправленных магистралей.

Задачей, решаемой в изобретении, является создание устройства, обеспечивающего преобразование мультиплексированных магистралей (МПИ) в демультиплексированную магистраль третьего уровня (М3), захвата управления с подменой информации по инициативе приоритетной управляющей вычислительной машины на основе анализа внешних воздействий и работы ведомой вычислительной машины.

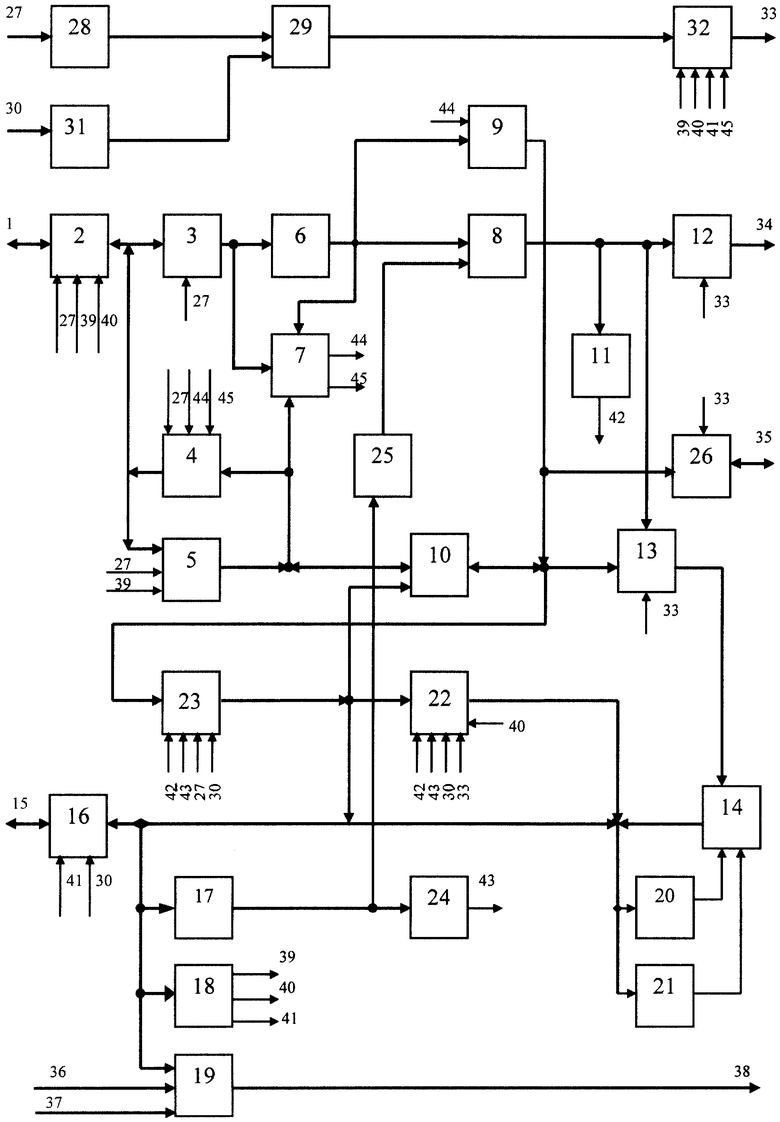

Технический результат достигается за счет того, что в адаптере-коммутаторе магистралей с самоконтролем содержатся следующие элементы и связи, показанные на чертеже. Мультиплексированная магистраль МПИ1 1 соединена с буферным приемопередатчиком МПИ1 2, выход которого соединен с первым входом регистра адреса МПИ1 3, с выходом буфера 4, с первым входом регистра данных 5, выход регистра адреса МПИ1 3 соединен с входом преобразователя адреса МПИ1 6 и со вторым входом формирователя сигналов контроля 7, выход преобразователя адреса МПИ1 6 соединен с первыми входами формирователя сигналов контроля 7, коммутатора адреса М3 8 и буфера контроля адреса 9, выход буфера контроля адреса 9 соединен с выходом двунаправленного коммутатора данных 10. Выход коммутатора адреса М3 8 соединен с входами дешифратора М3 11, буфера адреса М3 12 и первым входом формирователя данных 13, выход которого соединен с информационным входом оперативного запоминающего устройства (ОЗУ) контроля 14. Выход регистра данных 5 соединен с первым входом двунаправленного коммутатора данных 10, с третьим входом формирователя сигналов контроля 7 и с первым входом буфера 4. Мультиплексированная магистраль МПИ2 15 соединена с буферным приемопередатчиком МПИ2 16, выход которого соединен с первыми входами регистра адреса МПИ2 17, регистра режимов 18, коммутатора 19, со вторым входом двунаправленного коммутатора данных, с первыми входами преобразователя адреса 20, формирователя адреса 21, сверхоперативного запоминающего устройства 22, с выходами ОЗУ контроля 14, сверхоперативного запоминающего устройства и регистра состояния 23. Выход преобразователя адреса 20 соединен с первым адресным входом ОЗУ контроля 14. Выход формирователя адреса 21 соединен со вторым адресным входом ОЗУ контроля. Выход регистра адреса МПИ2 соединен с дешифратором МПИ2 24 и через преобразователь адреса МПИ2 25 со вторым входом коммутатора адреса М3 8. Выход двунаправленного коммутатора данных 10 соединен с входом буфера данных М3 26, со вторым входом формирователя данных 13, с входом регистра состояния 23. Шина управляющих сигналов МПИ1 27 через преобразователь управляющих сигналов МПИ1 28 соединена с первым входом коммутатора управляющих сигналов 29. Шина управляющих сигналов МПИ2 30 через преобразователь управляющих сигналов МПИ2 31 соединена со вторым входом коммутатора управляющих сигналов 29, выход которого соединен с первым входом буфера управляющих сигналов 32. Выход буфера управляющих сигналов соединен с шиной управляющих сигналов М3 33. Выход буфера адреса М3 12 соединен с шиной адреса М3 34. Выход буфера данных М3 26 соединен с шиной данных М3 35. Командные шины МПИ1 36 и МПИ2 37 соединены со вторыми и третьими входами коммутатора 19, выход которого соединен с командной шиной М3 38. Первый выход 39 регистра режимов соединен с первым управляющим входом буферного приемопередатчика МПИ1 2, вторыми входами буфера управляющих сигналов 32 и регистра данных 5. Второй выход 40 регистра режимов соединен с третьим управляющим входом буферного приемопередатчика МПИ1, третьим входом буфера управляющих сигналов 32, вторым входом сверхоперативного запоминающего устройства. Третий выход 41 регистра режимов 18 соединен с первым управляющим входом буферного приемопередатчика МПИ2, четвертым входом буфера управляющих сигналов 32. Выход 42 дешифратора М3 11 соединен с первыми управляющими входами регистра состояния и сверхоперативного запоминающего устройства. Выход 43 дешифратора МПИ2 24 соединен со вторыми управляющими входами регистра состояния и сверхоперативного запоминающего устройства 23, вторым входом регистра режимов 18, четвертым входом коммутатора 19, вторыми входами преобразователя адреса 20 и формирователя адреса 21. Первый выход 44 формирователя сигналов контроля 7 соединен со вторыми входами буфера контроля адреса 9 и буфера 4. Второй выход 45 формирователя сигналов контроля соединен с третьим входом буфера 4 и пятым входом буфера управляющих сигналов 32. Шина управляющих сигналов МПИ1 27 соединена со вторым управляющим входом буферного приемопередатчика МПИ1 2, вторым входом регистра адреса МПИ1 3, третьим управляющим входом регистра состояния 23, четвертым управляющим входом буфера 4, третьим входом регистра данных 5. Шина управляющих сигналов МПИ2 30 соединена со вторым управляющим входом приемопередатчика МПИ2 16 и вторым входом регистра адреса МПИ2 17, третьим входом регистра режимов 18, пятым входом коммутатора 19, третьими входами преобразователя адреса 20, формирователя адреса 21, с третьим управляющим входом сверхоперативного запоминающего устройства 22 и четвертым управляющим входом регистра состояния 23. Шина управляющих сигналов М3 33 соединена с управляющими входами буфера адреса М3, буфера данных М3 26, третьим входом формирователя данных 13, четвертым управляющим входом сверхоперативного запоминающего устройства 22.

Предлагаемое устройство обеспечивает передачу и прием информации и может быть использовано для управления блоками бортовых радаров (РЛС) со штатной управляющей вычислительной машиной по мультиплексированным магистралям МПИ1 либо МПИ2 (в зависимости от управляющей машины). А также, для обеспечения корректировки информации, передаваемой штатной вычислительной машиной по демультиплексированной магистрали третьего уровня М3; записи передаваемой информации в ОЗУ, с последующим считыванием в управляющую вычислительную машину высшего приоритета; обеспечения передачи и приема информации для управления блоками РЛС со стороны управляющей вычислительной машины высшего приоритета; обеспечения коммутации последовательных линий, разовых команд, синхросигналов на передачу от одного из двух источников информации к объекту управления. В устройстве предусмотрен режим контроля адресной и числовой магистралей при работе РЛС в режиме встроенного контроля.

Сравнение с техническими характеристиками, известными из опубликованных источников информации, показывают, что заявляемое решение обладает новизной и имеет изобретательский уровень.

Заявляемое решение носит технический характер, осуществимо, воспроизводимо и, следовательно, является промышленно применимым. Практическая реализация АКМ возможно на ПЛИС семейства MAX7000S и МАХ90000 фирмы "ALTERA", FLEX10K50, ОЗУ фирмы "Temic".

Адаптер-коммутатор магистралей с самоконтролем работает следующим образом.

При подаче напряжения питания АКМ устанавливается в режим 1 работы, запускается режим встроенного контроля блоков РЛС, после прохождения которого все блоки, включая АКМ, переходят в штатный режим работы. Для АКМ это означает трансляцию информации по мультиплексированной магистрали МПИ1 к управляемому объекту, например, к блокам радиолокационной станции. По командам бортовой цифровой вычислительной машины (БЦВМ), которая является управляющей машиной высшего приоритета, путем записи управляющего слова по мультиплексированной магистрали МПИ2 в регистр режимов 18, возможна установка еще двух режимов работы:

- в режиме 2 информация транслируется по мультиплексированной магистрали МПИ1 в демультиплексированную магистраль третьего уровня М3 с возможной подменой данных под управлением БЦВМ из сверхоперативного запоминающего устройства 22;

- в режиме 3 информация транслируется от БЦВМ по мультиплексированной магистрали МПИ2 в демультиплексированную магистраль третьего уровня М3 и дальше к блокам РЛС. Рассмотрим работу в каждом режиме подробнее.

Режим 1

Мультипликативный поток информации по мультиплексированной магистрали МПИ1 поступает на вход АКМ. Через буферный приемопередатчик МПИ1 1 поток разделяется на адресную и числовую части с помощью регистра адреса МПИ1 3, преобразователя адреса МПИ1 6 и регистра данных 5. Адресная часть через коммутатор адреса М3 8 поступает на буфер адреса М3 12, выход которого соединен с блоками РЛС. Данные проходят через двунаправленный коммутатор данных 10 на вход буфера данных М3 26, выход которого соединен с блоками РЛС. АКМ переходит в режим встроенного контроля при наличии определенной информации в адресной и числовой магистралях. С помощью формирователя сигналов контроля вырабатываются сигналы контроль Адреса и контроль Данных. При наличии сигнала контроль Адреса на первом выходе 44 формирователя сигналов контроля информация адресной магистрали через буфер контроля адреса 9, двунаправленный коммутатор данных 10, буфер 4, буферный приемопередатчик МПИ1 2 считывается по мультиплексированной магистрали МПИ1 и сравнивается с посланной. При наличии сигнала контроль Данных на втором выходе 45 формирователя сигналов контроля информация с числовой магистрали через буфер 4 и буферный приемопередатчик МПИ1 2 считывается по мультиплексированной магистрали МПИ1 и сравнивается с посланными данными. При этом контрольные данные не записываются в блоки РЛС из-за блокировки управляющих сигналов М3. После прохождения режима контроля АКМ переходит в штатный режим работы. Дешифратор М3 11 предназначен для распознавания адресов обращения к регистру состояния 23. При поступлении адреса, данные, передаваемые по мультиплексированной магистрали МПИ1 в демультиплексированную магистраль третьего уровня М3, записываются в регистр состояния с возможностью их последующего считывания по мультиплексированной магистрали МПИ2. Передаваемая при этом по демультиплексированной магистрали третьего уровня М3 информация поступает на блоки РЛС. Коммутаторы 19, 8, 10, 29 установлены в состояние передачи информации по мультиплексированной магистрали МПИ1 в демультиплексированную магистраль третьего уровня М3, синхроимпульсов, разовых команд и последовательных линий к блокам РЛС. Синхроимпульсы, разовые команды и последовательные линии поступают по шине команд МПИ1. В ОЗУ контроля записываются адреса и данные, передающиеся по этим адресам в М3. Адреса ОЗУ контроля 14 вырабатываются в формирователе адреса 21. Глубина ОЗУ контроля 14 определяется информацией БЦВМ, передаваемой по шине МПИ2 на вход формирователя адреса 21. Со стороны БЦВМ мультиплексированный поток информации МПИ2 через буферный приемопередатчик МПИ1 разделяется на адресную часть, записывающуюся под управлением сигналов в регистр адреса и данные. Данные поступают на вход двунаправленного коммутатора данных 10, либо в сверхоперативное запоминающее устройство 22, либо считываются из ОЗУ контроля 14 или регистра состояния 23. Дешифратор МПИ2 24 предназначен для распознавания адресов обращения БЦВМ к регистру режимов 18, преобразователю адреса 20 и регистру состояния 23. Преобразователь адреса МПИ2 25 переносит адресную область мультиплексированной магистрали МПИ2 в адресную область демультиплексированной магистрали третьего уровня М3. Функционирование БЦВМ в данном режиме заключается в том, что БЦВМ "наблюдает" за процессами в РЛС, происходящими под управлением информации, поступающей по демультиплексированной магистрали третьего уровня М3. Наблюдение происходит посредством считывания информации из регистра состояния 23 и ОЗУ контроля 14. Кроме этого, БЦВМ имеет возможность загрузки сверхоперативного запоминающего устройства 22. Считывание информации происходит так же с органов управления РЛС. По результатам анализа данной информации БЦВМ передает адаптеру команду - переходить в режим 2 или режим 3.

Режим 2

Отличается от режима 1 тем, что в зависимости от БЦВМ информационный поток транслируется по мультиплексированной магистрали МПИ1 в демультиплексированную магистраль третьего уровня М3 к блокам РЛС, либо по определенным адресам демультиплексированной магистрали третьего уровня М3 происходит подмена данных, извлекаемых из сверхоперативного запоминающего устройства 22. Загрузка данных в сверхоперативное запоминающее устройство 22 происходит от БЦВМ в любом из трех режимов.

Режим 3

Отличается тем, что управление блоками РЛС происходит со стороны БЦВМ. Демультипликативная адресная часть информации через регистр адреса МПИ2 17, преобразователь адреса МПИ2 25, коммутатор адреса М3 8 поступает на буфер адреса М3 12. Данные через буферный приемопередатчик МПИ2 16, двунаправленный коммутатор данных 10 поступают и принимаются с буфера данных М3 26. Сигналы управления с шины управляющих сигналов МПИ2 30 через преобразователь управляющих сигналов МПИ2 31, коммутатор управляющих сигналов 29 поступают на буфер управляющих сигналов М3 32. Коммутаторы 19, 8,10, 29 установлены в состояние передачи данных от БЦВМ к блокам РЛС.

Таким образом, адаптер-коммутатор магистралей с самоконтролем позволяет расширить функциональные возможности РЛС за счет обеспечения системы встроенного контроля, перекоммутации данных, накопления данных в ОЗУ. Обеспечивает, на основе анализа накопленных данных, изменение алгоритма взаимодействия блоков РЛС, подключенных к демультиплексированной магистрали третьего уровня М3, с подключенной к этой магистрали БЦВМ, посредством полного захвата и управления БЦВМ, либо подменой информации, передаваемой по демультиплексированной магистрали третьего уровня М3.

Использованные источники информации

1. Патент US 5721841, МКИ: G 06 F 15/02, опубликован ИСМ 4/99.

2. Патент JP 2781742, МКИ: G 06 F 15/16, опубликован ИСМ 16/99.

3. Патент RU 2128855, МКИ: G 06 F 7/08, опубликован 01.04.99.

4. Патент RU 2027220, МКИ: G 06 F 15/16, опубликован 20.01.95.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТЕР-КОММУТАТОР МАГИСТРАЛЕЙ | 2000 |

|

RU2188449C2 |

| СПОСОБ ОБРАБОТКИ РАДИОЛОКАЦИОННОГО СИГНАЛА | 2000 |

|

RU2192021C2 |

| ИМПУЛЬСНЫЙ МНОГОРЕЖИМНЫЙ МОДУЛЯТОР | 1999 |

|

RU2153763C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ХАОТИЧЕСКИХ ИМПУЛЬСНЫХ ПОМЕХ | 2001 |

|

RU2199763C1 |

| УСИЛИТЕЛЬ ИМПУЛЬСНОЙ СВЧ МОЩНОСТИ | 1999 |

|

RU2152125C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЗАПРОСНЫХ СИГНАЛОВ | 2001 |

|

RU2206103C2 |

| САМОЛЕТНЫЙ ОТВЕТЧИК | 2002 |

|

RU2215302C2 |

| УСТРОЙСТВО ДВУСТОРОННЕЙ ОПТИЧЕСКОЙ СВЯЗИ | 1999 |

|

RU2155450C1 |

| ИМПУЛЬСНЫЙ УСИЛИТЕЛЬ СВЕРХВЫСОКОЙ ЧАСТОТЫ | 2001 |

|

RU2207714C2 |

| ПЕРЕДАТЧИК СВЧ | 2001 |

|

RU2187880C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для сбора данных, управления и преобразования потоков данных между управляющими вычислительными машинами и объектом управления. Техническим результатом является обеспечение преобразования мультиплексированных магистралей в демультиплексированную магистраль третьего уровня, захвата управления с подменой информации по инициативе приоритетной управляющей вычислительной машины на основе анализа внешних воздействий и работы ведомой вычислительной машины. Для этого адаптер-коммутатор содержит мультиплексированные магистрали, коммутаторы, буферные приемопередатчики, буфер, регистры, формирователь сигналов контроля, преобразователь адреса, дешифраторы, оперативное запоминающее устройство контроля, сверхоперативное запоминающее устройство, шины управляющих сигналов. 1 ил.

Адаптер-коммутатор мультиплексированных магистралей с самоконтролем, содержащий мультиплексированную магистраль МПИ1, мультиплексированную магистраль МПИ2, коммутатор адреса М3, коммутатор, отличающийся тем, что мультиплексированная магистраль МПИ1 соединена с буферным приемопередатчиком МПИ1, выход которого соединен с входом регистра адреса МПИ1, с выходом буфера, с входом регистра данных, выход регистра адреса МПИ1 соединен с входом преобразователя адреса МПИ1 и со вторым входом формирователя сигналов контроля, выход преобразователя адреса МПИ1 соединен с первыми входами формирователя сигналов контроля, коммутатора адреса МЗ и входом буфера контроля адреса, выход буфера контроля адреса - с выходом двунаправленного коммутатора данных, выход коммутатора адреса МЗ - с входами дешифратора МЗ, буфера адреса МЗ и первым входом формирователя данных, выход которого соединен с информационным входом оперативного запоминающего устройства (ОЗУ) контроля, выход регистра данных соединен с первым входом двунаправленного коммутатора данных, с третьим входом формирователя сигналов контроля и с входом буфера, мультиплексированная магистраль МПИ2 соединена с буферным приемопередатчиком МПИ2, выход которого соединен с первыми входами регистра адреса МПИ2, регистра режимов, коммутатора, со вторым входом двунаправленного коммутатора данных, с входами преобразователя адреса, формирователя адреса, с входом сверхоперативного запоминающего устройства, с выходами ОЗУ контроля, сверхоперативного запоминающего устройства и регистра состояния, выход преобразователя адреса - с первым адресным входом ОЗУ контроля, выход формирователя адреса - со вторым адресным входом ОЗУ контроля, выход регистра адреса МПИ2 - с дешифратором МПИ2 и через преобразователь адреса МПИ2 со вторым входом коммутатора адреса М3, выход двунаправленного коммутатора данных - с входом буфера данных МЗ, со вторым входом формирователя данных, с входом регистра состояния, шина управляющих сигналов МПИ1 через преобразователь управляющих сигналов МПИ1 соединена с первым входом коммутатора управляющих сигналов, шина управляющих сигналов МПИ2 через преобразователь управляющих сигналов МПИ2 - со вторым входом коммутатора управляющих сигналов, выход которого соединен с первым входом буфера управляющих сигналов, выход буфера управляющих сигналов соединен с шиной управляющих сигналов М3, выход буфера адреса МЗ - с шиной адреса МЗ, выход буфера данных МЗ - с шиной данных МЗ, командные шины МПИ1 и МПИ2 соединены с соответствующими входами коммутатора, выход которого соединен с командной шиной М3, первый выход регистра режимов соединен с управляющими входами буферного приемопередатчика МПИ1, буфера управляющих сигналов, регистра данных, второй выход регистра режимов - с управляющими входами буферного приемопередатчика МПИ1, буфера управляющих сигналов, сверхоперативного запоминающего устройства, третий выход регистра режимов - с управляющими входами буферного приемопередатчика МПИ2, буфера управляющих сигналов, выход дешифратора МЗ - с управляющими входами регистра состояния и сверхоперативного запоминающего устройства, выход дешифратора МПИ2 - с управляющими входами регистра состояния, регистра режимов, коммутатора, сверхоперативного запоминающего устройства, преобразователя адреса, формирователя адреса, первый выход формирователя сигналов контроля соединен с управляющими входами буфера контроля адреса и буфера, второй выход формирователя сигналов контроля - с управляющими входами буфера и буфера управляющих сигналов, шина управляющих сигналов МПИ1 - с управляющими входами буферного приемопередатчика МПИ1, регистра адреса МПИ1, регистра состояния, буфера, регистра данных, шина управляющих сигналов МПИ2 - с управляющими входами буферного приемопередатчика МПИ2, регистра адреса МПИ2, регистра режимов, коммутатора, преобразователя адреса, формирователя адреса, сверхоперативного запоминающего устройства, регистра состояния, шина управляющих сигналов МЗ соединена с управляющими входами буфера адреса МЗ, буфера данных МЗ, формирователя данных, сверхоперативного запоминающего устройства.

| УСТРОЙСТВО КОММУТАЦИИ ДЛЯ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ | 1989 |

|

RU2027220C1 |

| RU 94026874 A1, 27.04.1996 | |||

| УСТРОЙСТВО ДЛЯ МУЛЬТИПЛЕКСНОГО ОБМЕНА ИНФОРМАЦИЕЙ | 1991 |

|

RU2012045C1 |

| RU 2015622 C1, 30.06.1994 | |||

| US 5050065 А, 17.09.1991 | |||

| Станок для гибки арматурных элементов | 1972 |

|

SU505781A1 |

Авторы

Даты

2002-06-20—Публикация

2001-01-03—Подача