Изобретение относится к технике информационно-вычислительных сетей и может быть использовано при построении сетей обмена данными крупномасштабных автоматизированных систем управления.

Известен автоматический коммутационный центр, содержащий центральный процессор, оперативное запоминающее устройство, постоянное запоминающее устройство, мультиплексор каналов, соединенные между собой общей системной магистралью, канальные адаптеры, соединенные с мультиплексором каналов [1].

Наиболее близким по технической сущности к предлагаемому решению является система SYSTEM/80, содержащая оперативную память, коммутатор, обслуживающий процессор, процессор ввода-вывода, языковый процессор, обрабатывающий процессор, файловый процессор [2].

Недостатками данной системы является невозможность работы с дискретными каналами связи, а также отсутствие приоритетной работы процессоров в зависимости от возложенных на них функций.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности перекоммутации данных, накопления информации поблочно и передачи данных пакетами.

Цель достигается тем, что в предлагаемое устройство, содержащее блок оперативной памяти, первый и второй обрабатывающие пpоцессоры, обслуживающий процессор, введены блок памяти, блок коммутации, блок n-канальных адаптеров (n - количество блоков данных, которые одновременно коммутируют устройство). Блок оперативной памяти, процессоры входами и выходами соединены с блоком коммутации, блок памяти входами и выходами соединен с блоком оперативной памяти и с блоком канальных адаптеров.

Предлагаемое устройство коммутации для многопроцессорной системы имеет следующие признаки, отличающие его от прототипа: введенные блок памяти, блок коммутации, блок n-канальных адаптеров, которые обеспечивают возможность перекоммутации данных, накопление информации поблочно и передачу данных пакетами.

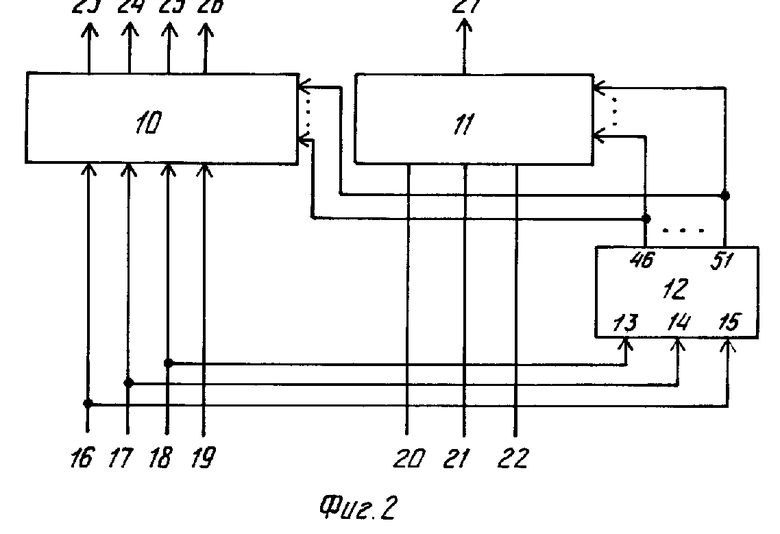

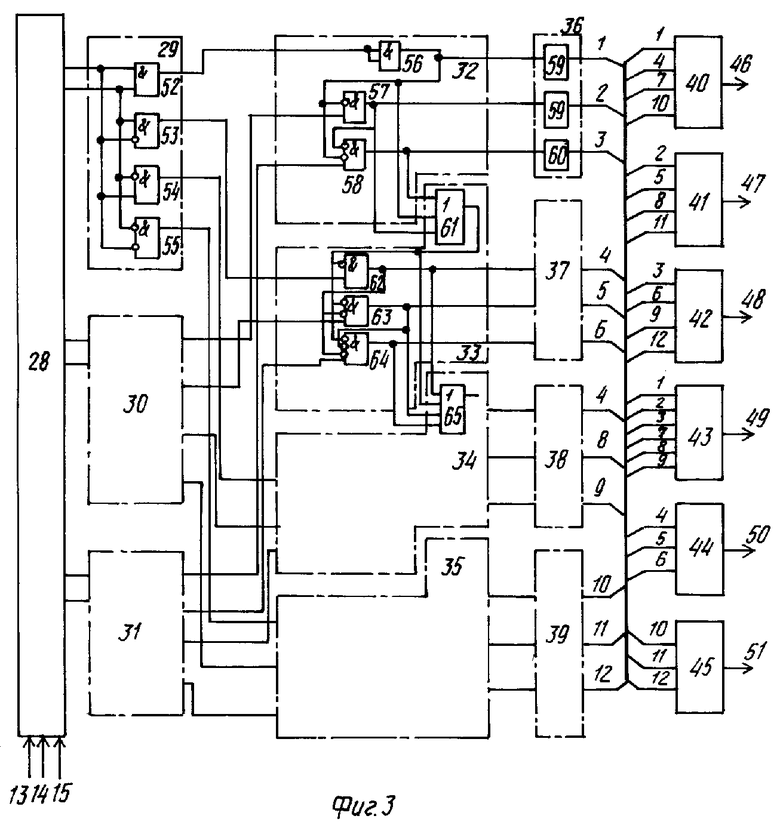

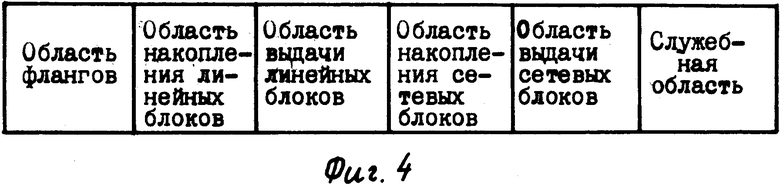

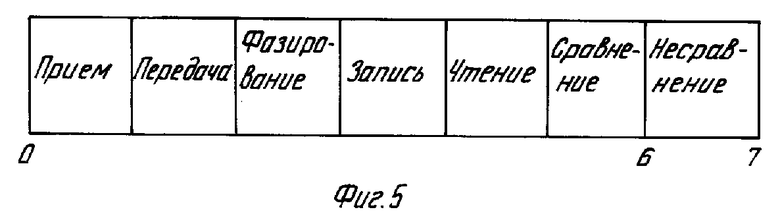

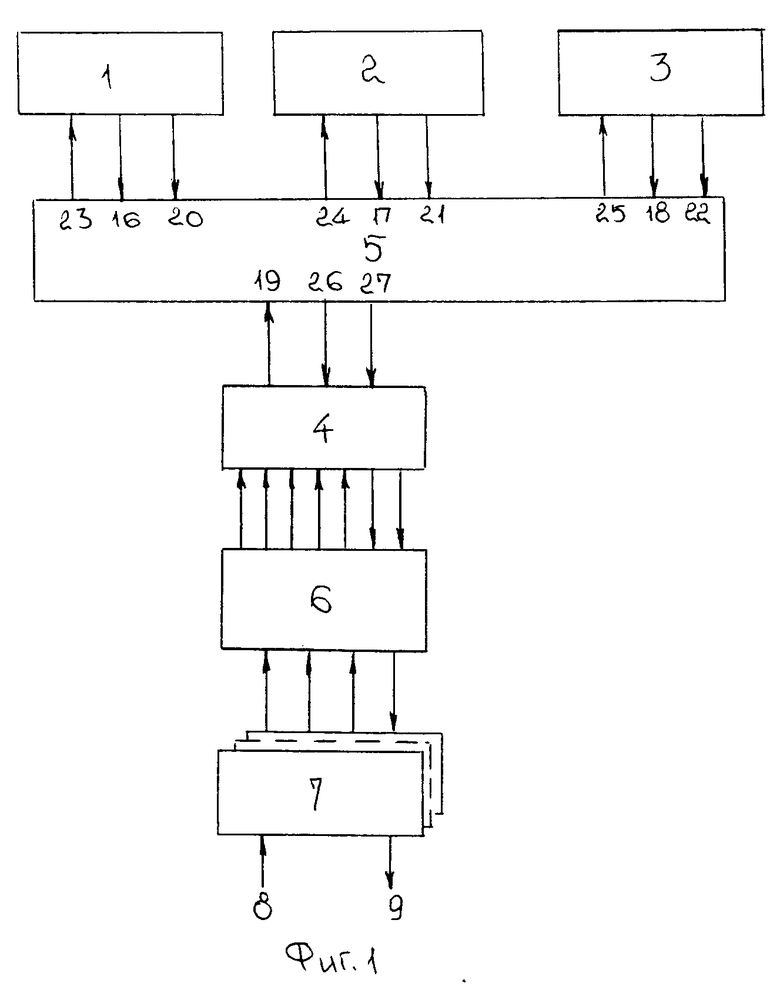

На фиг.1 представлена блок-схема устройства коммутации для многопроцессорной системы; на фиг.2 - блок-схема блока коммутации; на фиг.3 - функциональная схема узла управления; на фиг.4 -схема распределения оперативной памяти; на фиг.5 показаны значения разрядов регистра команды.

Устройство коммутации для многопроцессорной системы (фиг.1) содержит первый 1 и второй 2 обрабатывающие процессоры, обслуживающий процессор 3, блок 4 оперативной памяти, блок 5 коммутации, блок 6 памяти, блок 7n-канальных адаптеров, информационные входы и выходы первой группы которого являются входами 8 и выходами 9 устройства.

Блок коммутации (фиг. 2) содержит коммутатор 10 данных, коммутатор 11 адреса и узел 12 управления, информационные входы 13-15 которого соединены с информационными входами коммутатора данных и являются информационными входами 16-18 блока коммутации. Кроме того, информационный вход коммутатора данных является входом 19 блока, входы коммутатора адреса являются входами 20-22 блока, выходы коммутатора данных являются выходами 23-26 блока коммутации, а выход коммутатора адреса является выходом 27 блока.

Узел управления (фиг. 3) содержит регистр 28, первую 29, вторую 30 и третью 31 группы элементов И, первый 32, второй 33, третий 34 и четвертый 35 узлы приоритета, первую 36, вторую 37, третью 38 и четвертую 39 группы триггеров, с первого 40 по шестой 45 элементы ИЛИ, выходы которых являются управляющими выходами 46-51 узла управления.

Устройство работает следующим образом.

Поток пакетов данных, циркулирующий в системе обмена данными, поступает в устройство коммутации для многопроцессорной системы, где реализуются протоколы сетевого, канального и физического уровней. Последний реализуется в блоке 7 n-канальных адаптеров, передающих принятую информацию в блоке 6 памяти. Блок памяти реализует накопление байтов информации, адресацию блока 4 оперативной памяти и побайтную запись информации в область накопления линейных блоков. По накоплении одного линейного блока первым обрабатывающим процессором 1 реализуются функции протокола канала передачи данных. Обработанный линейный блок помещается в область накопления сетевых блоков. По накоплении сетевого блока он обрабатывается процессором 2, реализующим функции протокола сетевого уровня. После этого обработанный сетевой блок помещается в область выдачи сетевых блоков, где он разбивается на линейные блоки, обрабатываемые первым обрабатывающим процессором и помещаемые в области выдачи линейных блоков. Далее линейные блоки побайтно выдаются в блок 6 памяти для побитной передачи в блок 7 n-канальных адаптеров. Обслуживающий процессор 3 выполняет функции перераспределения оперативной памяти и обработки прерываний. Синхронизация работы процессоров осуществляется с помощью флагов, выставляемых процессорами в области флагов оперативной памяти. Для получения доступа к блоку 6 оперативной памяти процессоры 1-3 выставляют заявки в блок 5 коммутации, который предоставляет ресурс наиболее приоритетному запросу. По завершении обмена запрос снимается и начинает обслуживаться очередное требование на доступ к ресурсу.

Процессор, который производит обращение к какому-либо из блоков, выставляет заявку в двух младших битах по входам 13, 14, 15 блока обмена. Эта заявка фиксируется в регистре 28 блока выбора режима.

В блоке коммутации реализованы четыре режима: режим обращения процессора к блоку 4 оперативной памяти в зону приемного направления (код 11), режим обращения процессора к блоку 4 оперативной памяти за командой (код 10), режим обращения процессора к ОЗУ в зону передающего направления (код 01), режим 4 обращения процессора в область флагов блока 4 (код 00). Приоритетность режимов - в порядке номеров режимов.

Приоритетное обслуживание осуществляется при одновременном поступлении заявок от нескольких процессоров. При поступлении заявок на одноименный режим от нескольких процессоров их обслуживание, если нет заявок на более приоритетный режим, осуществляется, начиная с меньшего номера процессора. Группы 29, 30, 31 элементов И дешифрируют заявку и определяют режим, необходимый процессорам 1, 2, 3 соответственно. Элемент И 52 определяет заявку на первый режим, элемент И 53 - на второй режим, элемент И 54 - на третий режим, элемент И 55 - на четвертый режим 4.

Узлы 32-35 приоритета реализуют обслуживание заявок процессоров в случае одновременного поступления заявок на четыре режима соответственно, а также обслуживание по приоритетам. Сигналы элементов И 52 групп 29-31 поступают на входы элементов И 56-58. Если поступил запрос на первый режим от процессора 1, то элемент И 56 выдает сигнал на триггер 59 и устанавливает его в "1". Кроме того, этот сигнал поступает на инверсные входы элементов И 57, 58, тем самым запрещая появление на их выходе "1". Если поступила заявка на первый режим от процессора 2, то сигнал "1" формируется на выходе элемента И 57 (если отсутствует "1" на выходе элемента И 56), устанавливается в "1" триггер 59 и блокируется элемент ИЛИ 44. Аналогичные действия происходят при поступлении заявки на первый режим от процессора 3 при отсутствии заявок на данный режим от двух других процессоров. При этом работают элемент И 58 и триггер 60.

При установлении сигнала "1" на одном из выходов элементов И 56-58 он поступает на элемент ИЛИ 61, с которого поступает на инверсные входы элементов И 62-64, тем самым блокируя их работу, и на элемент ИЛИ 65, откуда он поступает на аналогичные элементы И узла 34 элемент ИЛИ узла 35. Этим блокируется работа узлов 34, 35. Элементы И 62-64 работают аналогично элементам И 56-58, но анализируют заявки на второй режим. Узлы 34, 35 анализируют соответственно заявки на третий и четвертый режимы и работают аналогично узлу 33. Таким образом сигнал "1" может появиться только на одном выходе групп 36-39 триггеров. Сигналы с триггеров групп 36-39 поступают на элементы ИЛИ 40-45, где формируются управляющие сигналы для коммутаторов адреса и данных. Сигнал "1" присутствует только на одном из выходов элементов ИЛИ 40-42, на одном из выходов элементов ИЛИ 43-45. Сигнал "1" на выходе элемента ИЛИ 40 свидетельствует об удовлетворении заявки на обслуживание процессора 1, на выход элемента ИЛИ 42 - процессора 3. "1" на выходе элемента ИЛИ 43 свидетельствует об обращении к блоку 4 оперативной памяти данных, на выходе элемента ИЛИ 44 - к блоку 4 оперативной памяти команд, на выходе элемента ИЛИ 45 - в область флагов блока 4 оперативной памяти. По окончании обмена процессор, производивший его, снимает свою заявку, и тем самым обеспечивается переход к обслуживанию заявок других процессоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ | 1990 |

|

RU2027219C1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для обмена информацией | 1982 |

|

SU1059561A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ | 1990 |

|

RU2041487C1 |

| Устройство для сопряжения двух процессоров | 1991 |

|

SU1784983A1 |

| Устройство для обмена информацией между магистралью параллельного интерфейса и последовательным каналом | 1986 |

|

SU1444788A1 |

| СПОСОБ МНОГОКАНАЛЬНОЙ ПЕРЕДАЧИ ПАКЕТОВ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043658C1 |

Изобретение относится к технике информационно-вычислительных сетей и может быть использовано при построении сетей обмена данными крупномасштабных автоматизированных систем управления. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности перекоммутации данных, накопления информации поблочно и передачи даных пакетами. Устройство содержит первый 1 и второй 2 обрабатывающие процессоры, обслуживающий процессор 3, блок 4 оперативной памяти, блок 5 коммутации, блок 6 памяти, блок 7 n-канальных адаптеров. 5 ил.

УСТРОЙСТВО КОММУТАЦИИ ДЛЯ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ, содержащее первый и второй обрабатывающие процессоры, обслуживающий процессор, блок оперативной памяти, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения возможности перекоммутации данных, накопления информации поблочно и передачи данных пачками, в устройство введены блок памяти, блок коммутации, блок n канальных адаптеров (где n - количество блоков данных, которые одновременно коммутируются устройством), информационные входы и выходы первой группы которого являются информационными входами и выходами первой группы устройства, первый, второй и третий информационные входы и выходы блока коммутации соединены с информационными выходами и входами первого, второго обрабатывающих и обслуживающего процессоров соответственно, первый, второй и третий адресные входы блока коммутации соединены с адресными выходами первого и второго обрабатывающих и обслуживающего процессоров соответственно, четвертый, пятый информационные входы и четвертый, пятый и шестой информационные выходы блока коммутации соединены с первым и вторым информационными выходами, первым и вторым адресными и первым информационным входами блока оперативной памяти, седьмой информационный выход и шестой информационный вход блока коммутации являются информационным входом и выходом второй группы устройства соответственно, первый и второй информационные входы, первый, второй, третий и четвертый информационные выходы блока памяти соединены с третьим и четвертым информационными выходами, входом адреса передачи данных, входом адреса приема данных, входом управления чтением и входом управления записью блока оперативной памяти соответственно, первый и второй информационные выходы блока памяти соединены с вторыми информационными входами группы блока канальных адаптеров и пятым информационным выходом блока оперативной памяти соответственно, третий информационный вход блока памяти соединен с информационным выходом второй группы блока канальных адаптеров, входы чтения данных и записи данных блока памяти соединены соответственно с первым и вторым управляющими выходами блока канальных адаптеров, причем блок коммутации содержит коммутатор адреса, коммутатор данных и узел управления, первый, второй, третий, четвертый, пятый и шестой управляющие выходы которого соединены с соответствующими управляющими входами коммутаторов адреса и данных, первый, второй и третий информационные входы узла управления соединены с первым, вторым и третьим информационными входами коммутатора данных и являются первым, вторым и третьим информационными входами блока коммутации, первый, второй и третий информационные входы коммутатора адреса соединены соответственно с первым, вторым и третьим адресными входами блока коммутации, первый и второй выходы коммутатора адреса являются четвертым и пятым информационными выходами блока коммутации, четвертый, пятый и шестой информационные входы коммутатора данных соединены с четвертым, пятым и шестым информационными входами блока коммутации, первый, второй, третий, четвертый и пятый информационные выходы коммутатора данных являются соответственно первым, вторым, третьим, шестым и седьмым информационными выходами блока коммутации, причем узел управления содержит регистр, первую, вторую, третью группы элементов И, первый, второй, третий и четвертый узлы приоритета, первую, вторую, третью и четвертую группы триггеров, с первого по девятый элементы ИЛИ, причем первый и второй информационные и управляющий входы регистра соединены соответственно с первым, вторым и третьим информационными входами блока коммутации, первый, второй и третий выходы регистра соединены с первыми входами первой, второй и третьей групп элементов И, соответственно четвертый, пятый и шестой выходы регистра соединены с вторыми входами первой, второй и третьей групп элементов И, причем узел приоритета содержит три элемента И и элемент ИЛИ первой группы элементов И, и с первыми входами первых элементов И узлов приоритета, выходы второй и третьей групп элементов И соединены с первыми входами вторых и третьих элементов И всех узлов приоритета, второй вход первого элемента И первого узла приоритета объединен с первым, выход первого элемента каждого узла приоритета соединен с вторыми входами второго и третьего элементов И узла приоритета, выход второго элемента И каждого узла приоритета соединен с третьим входом третьего элемента И узла приоритета, первый, второй и третий выходы первого, второго, третьего и четвертого узлов приоритета соединены с соответствующими входами первой, второй, третьей и четвертой групп триггеров, выходы которых соединены соответственно с входами четвертого, пятого, шестого, седьмого, восьмого и девятого элементов ИЛИ, выходы первого, второго и третьего элементов И первого, второго и третьего узлов приоритета соединены с первым, вторым и третьим входами первого, второго и третьего элементов И, выходы которых соединены с вторыми входами первых элементов И второго, третьего и четвертого узлов приоритета, выходы с четвертого по девятый элементов ИЛИ являются управляющими выходами узла управления.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ларионов А.М., Майоров С.А., Новиков Г.И | |||

| Вычислительные комплексы, системы и сети | |||

| Л.: Энергоиздат, 1987, с.104. | |||

Авторы

Даты

1995-01-20—Публикация

1989-11-03—Подача