1. Область применения изобретения

Изобретение относится, в общем, к устройству и способу канального кодирования в системе связи и, в частности, к устройству и способу вставки заранее известных битов на входном каскаде канального кодирующего устройства.

2. Описание предшествующего уровня техники

В системах связи для обработки речевых, символьных, видеосигналов и сигналов изображения передача данных обычно осуществляется на покадровой основе. Кадр определяется как основной интервал синхронизации в системе. Кроме того, в системе для передачи таких кадровых данных канальный кодер для коррекции ошибок должен также кодировать данные на покадровой основе. В этом случае канальный кодер осуществляет вставку нулевых хвостовых битов, указывая окончание каждого кадра с тем, чтобы декодер мог эффективно декодировать кадры с помощью этой информации. Хвостовые биты кодера представляют собой заданную последовательность битов, добавляемую в конец кадра данных, с целью сброса сверточного кодера в известное состояние. В системе IS-95 обычно используется нерекурсивный систематический сверточный кодер, который, реализуя указание окончания кадра, добавляет в конец каждого кадра последовательность нулевых (0) битов, длина которой равна количеству схем задержки. Однако в отличие от нерекурсивного систематического сверточного кодера, рекурсивный систематический кодер не может добавлять нулевые биты в конец кадра, чтобы реализовать указание окончания кадра, поскольку входные биты поступают обратно на схемы задержки.

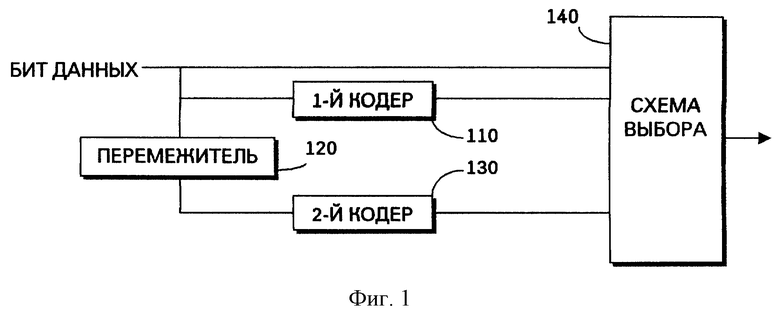

На фиг.1 изображена блок-схема общепринятого параллельного турбокодера, который представлен в патенте США 5446747, выданном Berrou. Кодер, изображенный на фиг.1, относится к типу общепринятого рекурсивного систематического кодера. Турбокодер кодирует N-битовый входной кадр в символы четности с использованием двух простых составных кодеров; и его можно конфигурировать на предмет образования параллельной или последовательной структуры. Кроме того, турбокодер, изображенный на фиг.1, использует в качестве составных кодов рекурсивные систематические сверточные коды.

Турбокодер, изображенный на фиг. 1, включает в себя перемежитель 120, подключенный между первым составным кодером 110 и вторым составным кодером 130. Перемежитель 120 имеет тот же размер, что и кадровая длина, N, входных битов данных и переупорядочивает биты данных, поступающие на второй составной кодер 130, с целью снижения корреляции между выходными сигналами первого и второго кодеров.

Первый составной кодер 110 кодирует входные биты данных, а перемежитель 120 перемежает (или рандомизирует) биты входного потока данных по особому правилу с тем, чтобы пакеты ошибок, внесенные каналом, можно было преобразовать в случайные ошибки. Второй составной кодер 130 кодирует выходной сигнал перемежителя 120.

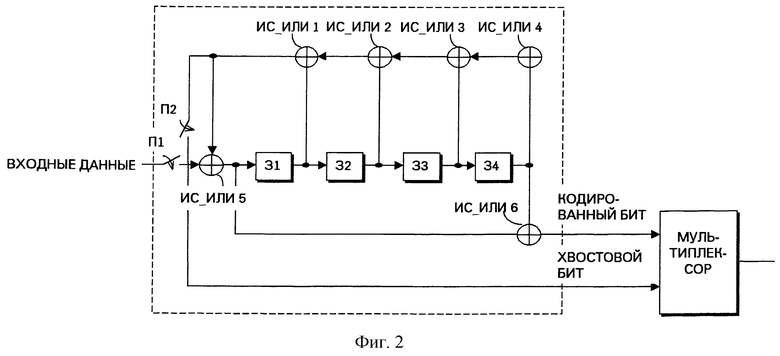

На фиг. 2 изображена схема, иллюстрирующая, как рекурсивный систематический сверточный кодер, изображенный на фиг.1, осуществляет указание окончания. Более подробную информацию см. D. Divsalar and F. Pollara, On the Design of Turbo Dodes, TDA Progress Report 42-123, Nov. 15, 1995. В данном случае предполагается, что кадровые данные, поступающие на первый и второй составные кодеры 110 и 130, представляют собой 20-битовые данные. На фиг.2 позиции 31-34 обозначают схемы задержки, а ИС_ИЛИ1-ИС_ИЛИ6 обозначают логические элементы "исключающее ИЛИ".

Согласно фиг. 2 кодирование производится следующими этапами. Переключатель П1 поддерживается в состоянии ВКЛ, и переключатель П2 поддерживается в состоянии ВЫКЛ. Данные 20-битового входного кадра последовательно поступают на схемы задержки 31-34 и подвергаются операции "исключающее ИЛИ" на логических элементах ИС ИЛИ1-ИС ИЛИ6, в результате чего на выходе логического элемента "исключающее ИЛИ" ИС_ИЛИ6 выводятся кодированные биты. После того как все 20 битов данных закодированы подобным образом, переключатель П1 переводится в состояние ВЫКЛ, а переключатель П2 переводится в состояние ВКЛ для указания окончания кадра. Затем логические элементы "исключающее ИЛИ" ИС_ ИЛИ1-ИС_ ИЛИ4 производят операцию "исключающее ИЛИ", соответственно, над выходными битами данных схем задержки и соответствующими возвращенными битами данных, выдавая, таким образом, нулевые биты. Полученные нулевые биты вновь поступают на схемы задержки 31-34 и сохраняются там. Эти нулевые биты, поступившие на схемы задержки 31-34, становятся хвостовыми битами, которые поступают на мультиплексор.

Мультиплексор мультиплексирует кодированные биты данных с хвостовыми битами, выдаваемыми составным кодером. Количество генерированных хвостовых битов зависит от количества схем задержки, входящих в состав базовых кодеров 110 и 130. Согласно фиг.2, при указании окончания генерируется 4 хвостовых бита на кадр, плюс к тому для каждого из соответствующих хвостовых битов генерируются дополнительные кодированные биты, в результате чего происходит нежелательное увеличение общего окончательного количества кодированных битов, что ведет к снижению скорости передачи битов. Итак, когда скорость передачи битов определяется по формуле скорость_передачи_битов = (количество входных битов данных)/(количество выходных битов данных), составной кодер, структура которого изображена на фиг.2, развивает скорость передачи битов, выражаемую следующим образом: скорость_передачи_битов = (количество входных битов данных)/{(количество кодированных битов данных)+(количество хвостовых битов)+(количество кодированных битов для хвостовых битов)}.

Итак, согласно фиг. 2, поскольку кадровые данные состоят из 20 битов и количество схем задержки равно 4, скорость передачи битов будет 20/28.

Ясно, что эффективность рекурсивного систематического сверточного кодера зависит от способа образования "хвостов", поскольку трудно совершенным образом создать "хвостовые" турбокоды.

Сущность изобретения

Итак, целью настоящего изобретения являются устройство и способ вставки битов в каждом канальном кадре в позиции, характеризующиеся более высокой вероятностью возникновения ошибки, каковые биты в последней битовой позиции кадровых данных имеют особое значение, притом, что в процессе декодирования в турбокодирующем устройстве последняя позиция характеризуется более высокой вероятностью возникновения ошибки.

Другой целью настоящего изобретения являются устройство и способ вставки особых битов в хвостовые позиции битовых потоков данных, поступающих соответственно на первый составной кодер и второй составной кодер турбокодирующего устройства.

Еще одной целью настоящего изобретения являются устройство и способ вставки особых битов в позиции битовых потоков данных, поступающих соответственно на первый составной кодер и второй составной кодер турбокодирующего устройства, причем позиция особого бита, вставляемого на втором составном кодере, сдвинута вперед, когда позиции особых битов, вставляемых на первом и на втором составных кодерах, взаимно перекрываются.

Для достижения вышеозначенных целей турбокодирующее устройство, отвечающее настоящему изобретению, включает в себя блок вставки битов, предназначенный для вставки одного или нескольких особых битов в хвостовые позиции битового потока данных, поступающего на первый составной кодер, и для вставки, по меньшей мере, одного особого бита в последнюю позицию перемеженного битового потока данных, поступающего на второй составной кодер; первый составной кодер, предназначенный для кодирования битов данных со вставленными особыми битами для генерирования первых символов четности; перемежитель, предназначенный для перемежения битов данных со вставленными особыми битами; второй составной кодер, предназначенный для кодирования перемеженных битов данных для генерирования вторых символов четности; и мультиплексор, предназначенный для мультиплексирования выходных сигналов блока вставки битов, первого составного кодера и второго составного кодера.

Краткое описание чертежей

Вышеозначенные и иные цели, признаки и достоинства настоящего изобретения явствуют из нижеследующего подробного описания, приведенного в сочетании с прилагаемыми чертежами, подобные детали которых обозначены подобными номерами. На чертежах:

ФИГ.1 представляет собой блок-схему, иллюстрирующую канальный кодер, отвечающий уровню техники, используемый в системе беспроводной связи;

ФИГ. 2 представляет собой подробную блок-схему, иллюстрирующую составной кодер, отвечающий уровню техники, изображенный на фиг.1;

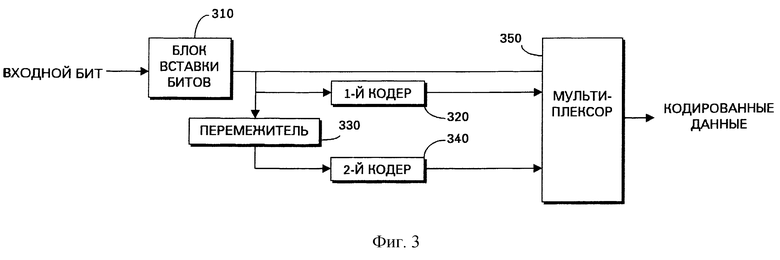

ФИГ. 3 представляет собой схему, иллюстрирующую канальный кодер, отвечающий первому варианту реализации изобретения;

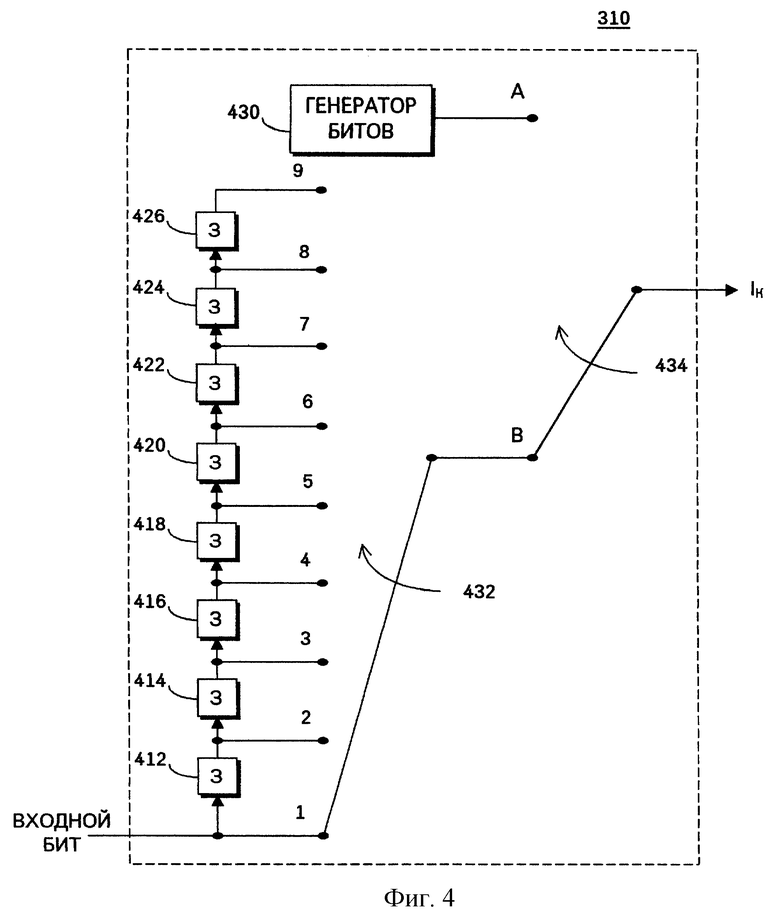

ФИГ. 4 представляет собой подробную схему, иллюстрирующую блок вставки битов, изображенный на фиг.3;

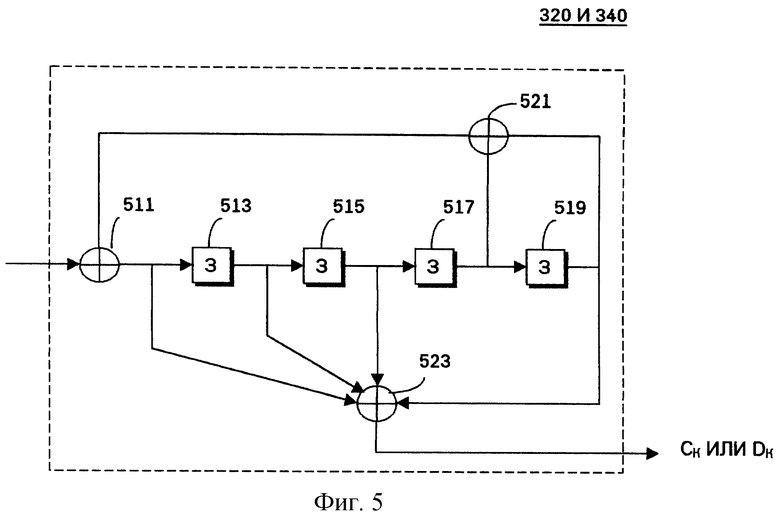

ФИГ. 5 представляет собой подробную схему, иллюстрирующую составной кодер, изображенный на фиг.3;

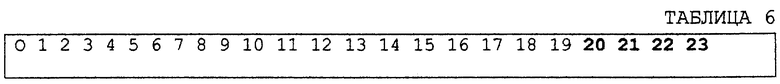

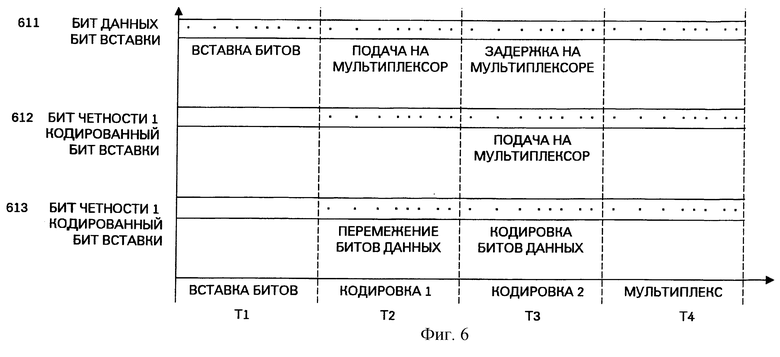

ФИГ. 6 представляет собой схему, иллюстрирующую процедуру обработки битов, отвечающую первому варианту реализации изобретения;

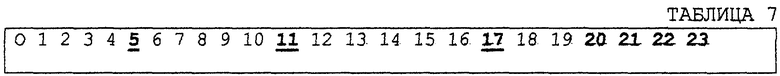

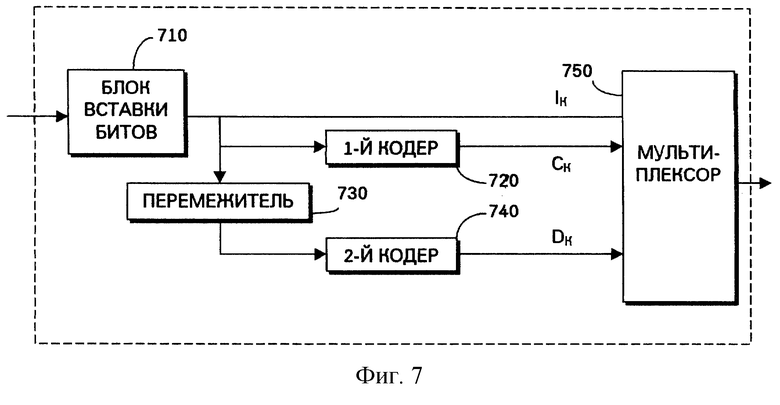

ФИГ. 7 представляет собой схему, иллюстрирующую канальный кодер, отвечающий второму варианту реализации изобретения;

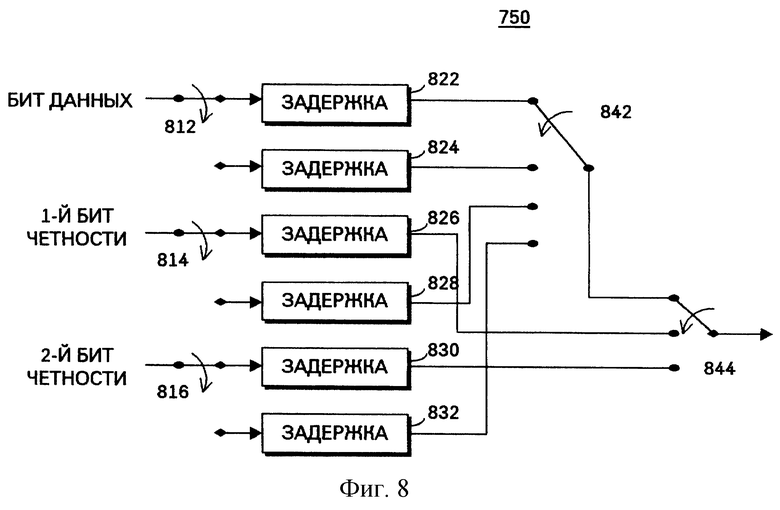

ФИГ. 8 представляет собой подробную схему, иллюстрирующую мультиплексор, изображенный на фиг.7;

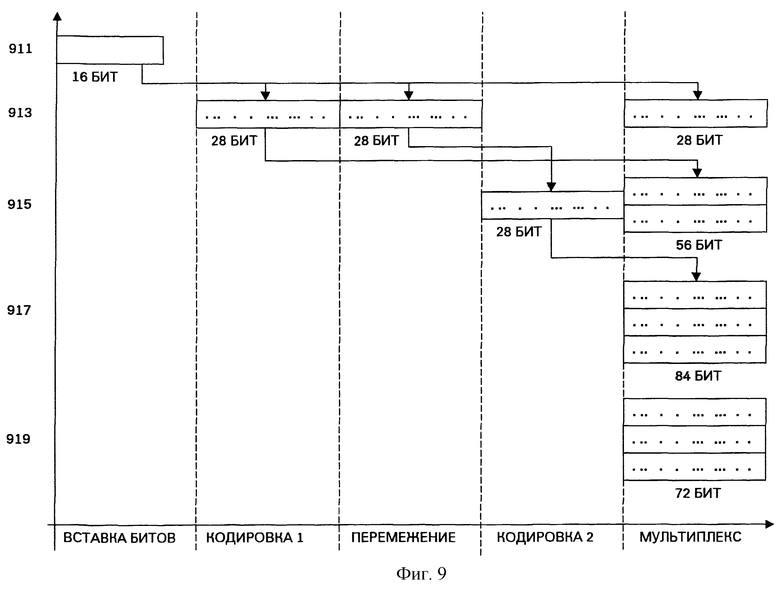

ФИГ. 9 представляет собой схему, иллюстрирующую процедуру обработки битов, отвечающую второму варианту реализации изобретения;

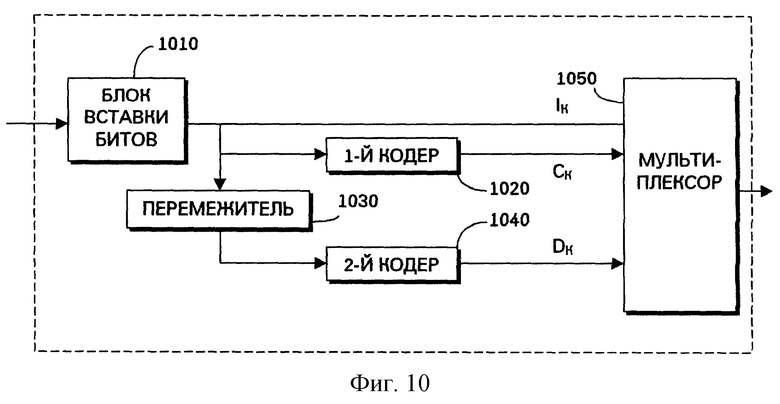

ФИГ. 10 представляет собой схему, иллюстрирующую канальный кодер, отвечающий третьему варианту реализации изобретения;

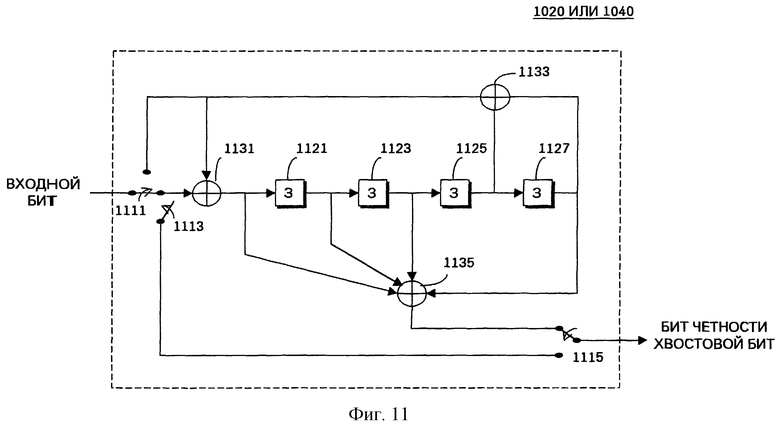

ФИГ.11 представляет собой подробную схему, иллюстрирующую базовый кодер, изображенный на фиг.10;

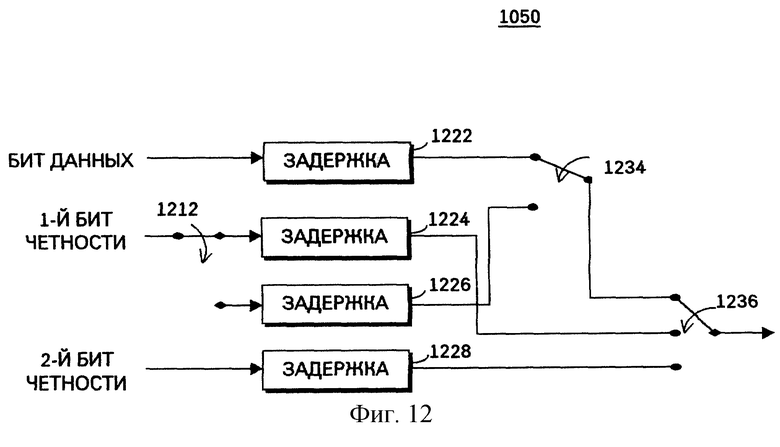

ФИГ.12 представляет собой подробную схему, иллюстрирующую мультиплексор, изображенный на фиг.10;

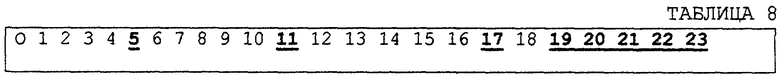

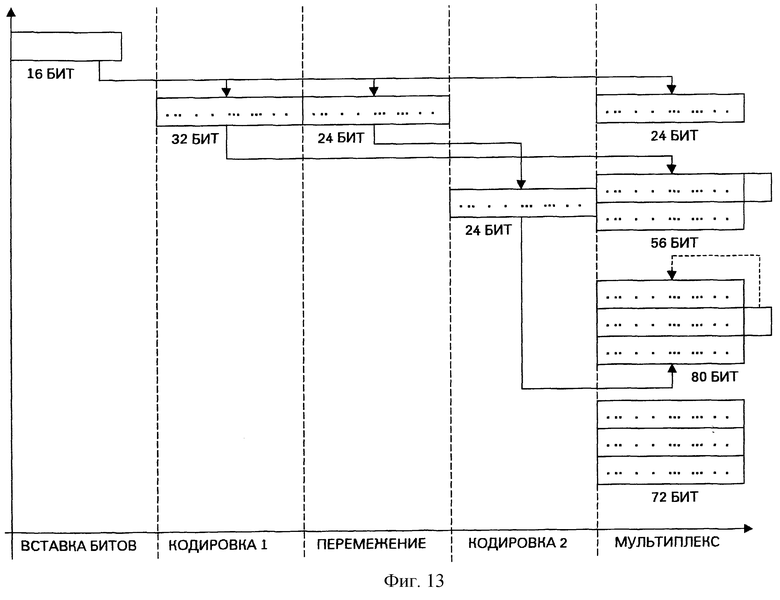

ФИГ. 13 представляет собой схему, иллюстрирующую процедуру обработки битов, отвечающую третьему варианту реализации изобретения;

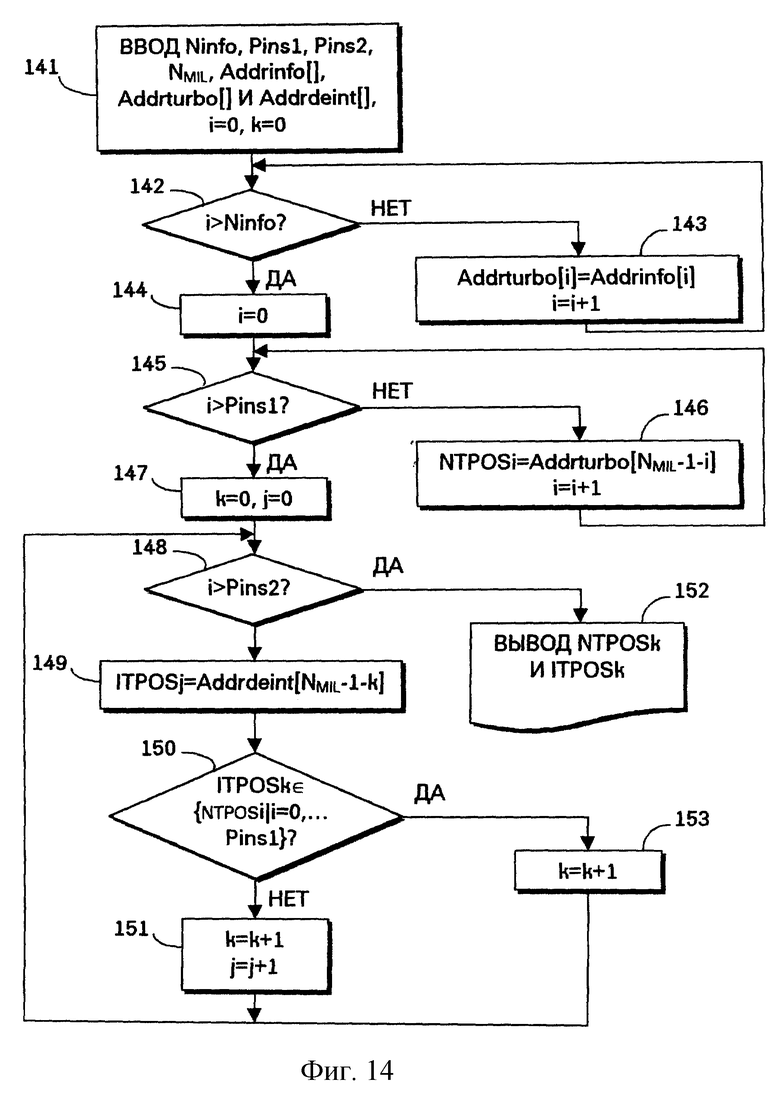

ФИГ. 14 представляет собой схему, иллюстрирующую процедуру вставки заранее известных битов на входном каскаде канального кодера, отвечающую варианту реализации настоящего изобретения.

Подробное описание преимущественных вариантов реализации

Ниже описаны преимущественные варианты реализации настоящего изобретения со ссылкой на прилагаемые чертежи. В нижеследующем описании общеизвестные функции или конструкции не описываются подробно, чтобы не затемнять сущность изобретения несущественными деталями. Употребляемый здесь термин "бит данных" относится к данным, не прошедшим кодирование, а термин "бит четности" относится к данным, прошедшим кодирование на составном кодере.

Обычно передатчик системы связи кодирует передаваемые данные с помощью канального кодера, а затем передает кодированные данные; приемник демодулирует данные, полученные от передатчика, с целью преобразования полученных данных в исходные данные. Канальный кодер кодирует передаваемые данные на покадровой основе и генерирует хвостовые биты, которые добавляются к каждому кадру с целью указания окончания кадра. Настоящее изобретение представляет кадровую структуру, имеющую эффект окончания в канальном кодере.

Ниже описано несколько вариантов реализации кадровой структуры, имеющей эффект окончания.

Первый вариант реализации. Некоторое количество особых битов вставляется в каждом канальном кадре в позиции, характеризующиеся более высокой вероятностью возникновения ошибки, причем количество вставляемых битов определяется количеством хвостовых битов. Поскольку рекурсивные систематические базовые кодеры не конфигурированы на генерирование хвостовых битов, вероятность возникновения ошибки определяется экспериментальным путем, и позиции вставки должны быть известны как канальному кодеру, так и канальному декодеру. Предпочтительно, чтобы особые биты, подлежащие вставке, были незначащими битами, которые оказывают небольшое влияние или вовсе не оказывают влияния на эффективность канала связи, вне зависимости от того, передаются они или нет. Кроме того, они могут быть кодированными битами или битами данных, заранее определенными приемником. В данном случае предполагается, что это нулевые биты.

Второй вариант реализации. Некоторое количество особых битов вставляется в каждом канальном кадре в позиции, характеризующиеся более высокой вероятностью возникновения ошибки, причем количество вставляемых битов определяется количеством хвостовых битов. Вставка особых битов приводит к превышению заранее заданной кадровой длины. Биты данных со вставленными битами кодируются с помощью базовых кодеров. Затем, при выводе канально-кодированных данных, биты, выходящие за пределы кадровой длины канально-кодированных данных, пробиваются в позициях вставки битов входных данных. В данном случае рекурсивный систематический кодер не генерирует хвостовые биты, и канальный декодер должен заранее знать позиции вставки битов.

Третий вариант реализации. Некоторое количество особых битов вставляется в каждом канальном кадре в позиции, характеризующиеся более высокой вероятностью возникновения ошибки, причем количество вставляемых битов определяется количеством хвостовых битов. Базовый кодер генерирует хвостовые биты для указания окончания и соответствующие кодированные данные для хвостовых битов, после чего пробивает биты данных в особых положениях вставки в каждом канальном кадре с целью вставки хвостовых битов и кодированных данных для хвостовых битов в позиции пробивки, выбранные для вставки битов.

Первый вариант реализации

Согласно первому варианту реализации настоящего изобретения кодер не генерирует хвостовые биты, но, вместо этого, вставляет особые биты в заранее определенные позиции с целью осуществления функции окончания. Согласно данному варианту реализации один 24-битовый кадр включает в себя 16 битов данных и 8 особых битов, причем каждый из 8 особых битов является нулевым битом, вставленным в кадр в битовые позиции, характеризующиеся более высокой вероятностью ошибки. В данном случае позиции вставки бита определяются путем экспериментального обнаружения позиций, где в процессе декодирования кодированных данных возникает наибольшее количество ошибок. Кроме того, каждый базовый кодер использует скорость кодирования 1/3.

Согласно данному варианту реализации позиции, характеризующиеся более высокой вероятностью ошибки при декодировании, определяются экспериментально, когда данные 24-битового кадра (т.е. 16 битов кадровых данных плюс 8 особых битов) кодируются с помощью турбокодера, имеющего скорость кодирования 1/3. Выявляется восемь битовых позиций, характеризующихся относительно высокой вероятностью ошибки, и в выявленные позиции вставляются особые биты. В данном случае декодер знает позиции вставки битов, когда декодирует кодированные кадровые данные, в которые вставлены особые коды.

На практике все "0" биты передаются как "-1". Когда вставленные особые биты являются нулевыми битами, нулевые биты в позициях вставки, в целях повышения надежности, заменяются перед кодированием большим отрицательным значением (например, -5). Это делается для увеличения эффективности декодирования, поскольку при передаче в среде радиосвязи могут происходить изменения. Однако, поскольку декодер заранее знает позицию особого бита, подлежащего приему, в фактическом процессе декодирования декодер вставляет для особого бита более высокое значение, отличное от -1. В этом случае декодер может повысить эффективность декодирования за счет вставки особого значения. Эта операция декодирования будет подробно описана со ссылкой на фиг.14. Таким образом, декодер, декодирующий биты, знает, по меньшей мере, 8 битов из 24 в силу того, что они передаются в виде большого отрицательного значения, благодаря чему эффективность декодирования повышается. Согласно данному варианту реализации эффективность декодирования тем выше, чем короче кадр.

Фиг. 3 представляет собой схему, иллюстрирующую турбокодер, отвечающий первому варианту реализации настоящего изобретения, в состав которого входит блок вставки битов, предназначенный для вставки особых битов. Блок вставки битов 310 включает в себя генератор битов, предназначенный для генерирования особых битов путем обработки входных битов данных, и генерирует биты данных на покадровой основе путем вставки особых битов, генерируемых генератором битов, в поступающий битовый поток данных в заранее заданные позиции вставки бита. Согласно данному варианту реализации предполагается, что позиция, куда блок вставки битов 310 вставляет особый бит, является последним участком битового потока данных. Вставка особых битов определяется контроллером, который не изображен на фигуре. Первый составной кодер 320 кодирует биты данных, выдаваемые блоком вставки битов 310. Перемежитель 330 перемежает на покадровой основе биты данных, выдаваемые блоком вставки битов 310, в соответствии с заранее определенным правилом, чтобы переупорядочить последовательность битов данных. Согласно иллюстративному варианту реализации в качестве перемежителя 330 используется диагональный перемежитель.

Второй составной кодер 340 кодирует на покадровой основе перемеженные биты данных, выдаваемые перемежителем 330. В качестве первого и второго составных кодеров 320 и 340 можно использовать рекурсивные систематические сверточные кодеры. Мультиплексор 350 мультиплексирует под управлением контроллера, который не изображен на фигуре, выходные сигналы блока вставки битов 310, первого составного кодера 320 и второго составного кодера 340. В данном случае блок вставки битов 310 выдает биты данных 1k. Первый составной кодер 320 выдает первые биты четности P1k, а второй составной кодер 340 выдает вторые биты четности P2k.

Фиг. 4 представляет собой подробную блок-схему, иллюстрирующую блок вставки битов 310, входящего в состав турбокодера, изображенного на фиг.3. Согласно фиг.4 генератор битов 430 генерирует особые биты, подлежащие вставке среди битов данных. В данном случае предполагается, что особые биты - это нулевые биты. Схемы задержки 412-426, реализовать которые можно в виде элементов памяти, например триггеров, могут иметь регистровую структуру с последовательным сдвигом для сдвига входных битов данных в соответствии с битовым синхросигналом.

Переключатель 432, управляемый контроллером, который не изображен на фигуре, переключается с целью выбора выходных сигналов схем задержки 412-426. Кроме того, переключатель 432 переключается под управлением контроллера, который не изображен на фигуре, на выход следующей схемы задержки в позициях, где особый бит, выдаваемый генератором битов 430, вставляется в биты данных. Таким образом, переключатель 432 выбирает бит данных, задержанный на один бит, когда в биты данных вставляется выбранный особый бит. Переключатель 432 может быть реализован в виде мультиплексора. Переключатель 434 переключается под управлением контроллера, который не изображен на фигуре, между выходами генератора битов 430 и переключателя 432, чтобы генерировать биты данных 1k. Переключатель 434 выбирает под управлением контроллера либо особые биты, либо биты данных для вставки в заранее заданные позиции.

Со ссылкой на фиг.4 описывается операция вставки битов. Входные биты данных задерживаются схемами задержки 412-426 в соответствии с битовым синхросигналом. Первоначально переключатель 432 выбирает входные биты данных (т. е. полюс 1) и переключатель 434 первоначально подключается к переключателю 432 (т.е. полюс В). Таким образом, входные биты данных выводятся через переключатели 432 и 434. Между тем, когда определена позиция вставки бита, переключатель 432 под управлением контроллера подключается к выходу схемы задержки 412 (т.е. полюс 2), а переключатель 434 также под управлением контроллера подключается к выходу генератора битов 430 (т.е. полюс А). В результате тракт битов данных перекрывается и в соответствующую битовую позицию вставляется нулевой бит, выдаваемый генератором битов 430. Для продолжения вывода битов данных после вставки нулевого бита переключатель 434 вновь подключается к переключателю 432 под управлением контроллера. Таким образом, поскольку после вставки нулевого бита выбирается бит данных, задержанный на один бит, нулевой бит можно вставлять в заранее заданную позицию без потери бита данных.

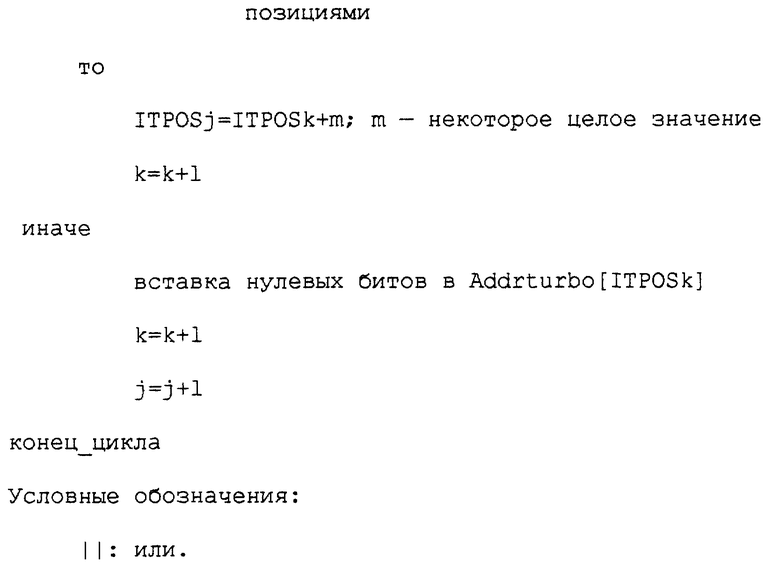

Вставка нулевых битов в биты данных на протяжении одного кадра осуществляется путем повторения этого процесса. Если после вставки нулевых битов начинают поступать биты данных следующего кадра, переключатель 432 вновь подключается к узлу входных битов (полюс 1) и вышеописанный процесс повторяется снова. При кодировании битов данных для передачи вероятность ошибки, по статистике, является относительно более высокой на заднем участке битового потока данных, поступающего на соответствующие базовые кодеры. Соответственно позиции, где осуществляется вставка нулевых битов, выдаваемых генератором битов 430, можно, по большей части, локализовать на заднем участке битового потока данных, что в качестве примера показано в таблице 1.

Представленные в таблице 1 биты данных, выдаваемые блоком вставки битов 310, параллельно поступают на первый составной кодер 320 и на перемежитель 330. Перемеженные на покадровой основе биты данных, выдаваемые перемежителем 330, кодируются вторым составным кодером 340. На фиг.5 представлена структура первого и второго составных кодеров 320 и 340, изображенных на фиг.3, в соответствии с первым вариантом реализации. Согласно фигуре, первый и второй составные кодеры 320 и 340 являются рекурсивными систематическими сверточными кодерами. Кроме того, согласно фиг.5, базовые кодеры 320 и 340 сконфигурированы так, что не генерируют хвостовые биты.

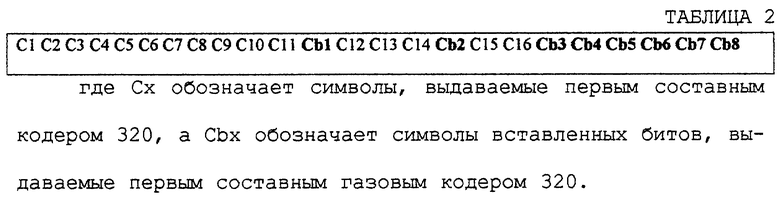

Первый базовый кодер 320 кодирует приведенные в таблице 1 биты данных, выдаваемые блоком вставки битов 310. Кодированные биты данных, выдаваемые первым составным кодером 320, представлены в таблице 2.

В данном случае, поскольку первый составной кодер 320 имеет скорость кодирования 1/3, каждый символ С представляет собой три символа. Отмечается однако, что в таблице 1 не показаны избыточные символы.

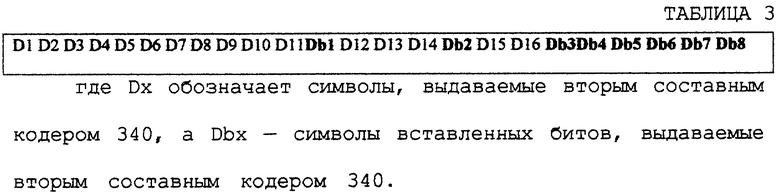

Тем временем перемежитель 330 перемежает биты данных, выдаваемые блоком вставки битов 310, и второй базовый кодер 340 кодирует перемеженные биты данных, выдаваемые перемежителем 330. Кодированные биты данных, выдаваемые вторым базовым кодером 340, представлены в таблице 3.

В данном случае, поскольку второй составной кодер 340 имеет скорость кодирования 1/3, каждый символ D представляет собой три символа. Хотя, на самом деле, последовательность битов данных была переупорядочена при перемежении для простоты объяснения в таблице 3 последовательность оставлена без изменения.

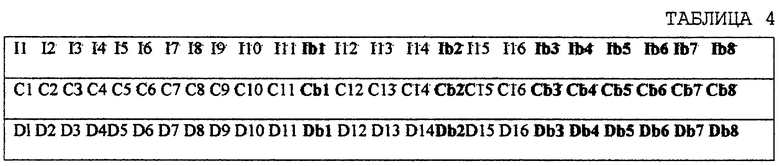

Затем мультиплексор 350 мультиплексирует выходные сигналы блока вставки битов 310, первого составного кодера 320 и второго составного кодера 340 под управлением контроллера, не изображенного на фигуре. На фиг.4 представлены биты данных со вставленными особыми битами и выходные сигналы первого и второго составных кодеров 320 и 340. Мультиплексор 350 может мультиплексировать входные символы в последовательность символа данных, первого символа четности и второго символа четности либо на покадровой основе, как показано в таблице 4, либо на посимвольной основе.

Фиг. 6 представляет собой схему синхронизации турбокодера, изображенного на фиг.3, согласно первому варианту реализации настоящего изобретения. Согласно фиг. 6 в интервале Т1 блок вставки битов 310 вставляет нулевые биты в кадре в заранее заданные позиции, генерируя битовый поток данных со вставленными битами Ik, где вставленные биты представляют собой нулевые биты, показанные в таблице 1 (см. 611). В интервале Т2 биты данных со вставленными нулевыми битами Ik одновременно поступают на мультиплексор 350, первый составной кодер 320 и перемежитель 330. Затем в интервале Т2 первый составной кодер 320 кодирует биты данных со вставленными нулевыми битами Ik, генерируя первые кодированные биты данных Сk, которые представляют собой первые биты четности (см. 612), и в том же интервале Т2 перемежитель 330 перемежает биты данных со вставленными нулевыми битами Ik согласно заранее заданному правилу (см. 613).

Затем, в интервале Т3, мультиплексор 350 задерживает биты данных Ik, выдаваемые блоком вставки битов 310, на один кадровый период, первый составной кодер 320 вводит первые кодированные биты данных Ck в мультиплексор 350, и второй составной кодер 340 кодирует перемеженные биты данных Ik, выдаваемые перемежителем 330, генерируя вторые кодированные биты данных Dk, которые представляют собой вторые биты четности. По завершении генерирования вторых битов четности Dk вторым составным кодером 340 мультиплексор 350 мультиплексирует биты данных Ik, первые биты четности Ck и вторые биты четности Dk в интервале Т4.

Хотя на фиг.6 представлен пример параллельной обработки битов данных Ik, первых битов четности Сk и вторых битов четности Dk возможна также последовательная обработка выходных сигналов блока вставки битов 310, первого составного кодера 320 и второго составного кодера 340 в порядке генерирования битов.

Как явствует из вышеприведенного описания, в рекурсивном систематическом турбокодере, отвечающем первому варианту реализации, соответствующие составные кодеры не генерируют хвостовые биты для указания окончания, но, вместо этого, вставляют некоторое количество особых битов (т.е. нулевых битов) в битовые позиции, для которых выявлена более высокая вероятность ошибки.

Второй вариант реализации

Как и в первом варианте реализации канальный кодер, отвечающий второму варианту реализации настоящего изобретения, вставляет особые биты в битовые позиции, характеризующиеся более высокой вероятностью возникновения ошибки. Однако второй вариант реализации можно отличить от первого варианта реализации на том основании, что количество вставляемых битов устанавливается таким образом, чтобы превысить размер (или длину) кадра. В данном иллюстративном варианте реализации предполагается, что каждый кадр включает в себя 16 входных битов данных Ik и 12 вставленных битов. Данный вариант реализации предусматривает добавление четырех дополнительных вставленных битов. Поскольку, в целом, должно генерироваться 24 или 28 выходных битов данных Ik, битов четности Сk и Dk, избыточные биты четности Сk и Dk пробиваются из битов данных Ik в позициях вставки битов.

Фиг. 7 представляет собой схему канального кодера, отвечающего второму варианту реализации настоящего изобретения. Блок вставки битов 710 включает в себя генератор битов, предназначенный для генерирования особых битов путем обработки входных битов данных, и генерирует биты данных, превышающие кадровый размер, путем вставки особых битов, генерируемых генератором битов, в заранее заданные позиции вставки битов. Первый составной кодер 720 кодирует биты данных, выдаваемые блоком вставки битов 710, генерируя первые биты четности Сk. Перемежитель 730 перемежает на покадровой основе биты данных, выдаваемые блоком вставки битов 710, в соответствии с заранее определенным правилом, чтобы изменить расстановку (или последовательность) битов данных. Согласно иллюстративному варианту реализации в качестве перемежителя 730 используется диагональный перемежитель.

Второй составной кодер 740 кодирует на покадровой основе перемеженные биты данных, выдаваемые перемежителем 730, генерируя вторые биты четности Dk. В качестве первого и второго составных кодеров 720 и 740 можно использовать рекурсивные систематические сверточные кодеры. Мультиплексор 750 под управлением контроллера, который не изображен на фигуре, мультиплексирует выходные сигналы блока вставки битов 710, первого составного кодера 720 и второго составного кодера 740, генерируя кадр данных заранее заданной длины. В данном случае блок вставки битов 710 выдает биты данных 1k, первый составной кодер 720 выдает первые биты четности P1k, а второй составной кодер 740 выдает вторые биты четности Р2k.

В ходе работы, получив 16 выходных битов данных Ik, блок вставки битов 710 действует таким же образом, как блок вставки битов 310, отвечающий первому варианту реализации. Структура блока вставки битов 710 аналогична структуре, изображенной на фиг.4, за исключением того, что в его состав входит 12 схем задержки вместо 8. Поэтому блок вставки битов 710 вставляет 12 нулевых битов в кадре в 12 битовых позиций, характеризующихся более высокой вероятностью ошибки, благодаря наличию внутренних переключателей, работающих под управлением контроллера, не изображенного на фигуре. Итак, согласно данному варианту реализации блок вставки битов 710 выдает 28 битов данных Ik (т.е. 16 битов данных и 12 нулевых битов), которые одновременно поступают на мультиплексор 750, первый составной кодер 720 и перемежитель 730. Далее перемеженные биты данных Ik, выдаваемые перемежителем 730, поступают на второй составной кодер 740. В данном случае первый и второй составные кодеры 720 и 740 имеют структуру, изображенную на фиг.5, которая не позволяет генерировать хвостовые биты для указания окончания.

Первый составной кодер 720 кодирует выдаваемые блоком вставки битов 710 28 битов данных Ik со вставленными туда 12 нулевыми битами и выдает 28 первых битов четности Сk на мультиплексор 750. Перемежитель 730 перемежает 28 битов данных Ik, выдаваемые блоком вставки битов 710, и второй составной кодер 740 кодирует перемеженные биты данных таким же образом, что и первый составной кодер 720, генерируя 28 вторых битов четности Dk, которые поступают на мультиплексор 750. Мультиплексор 750 пробивает биты данных Ik, вставляя четыре первых бита четности Ck и четыре вторых бита четности Dk в позиции пробивки, после чего выдает оставшиеся 24 первых бита четности Ck и оставшиеся 24 вторых бита четности Dk.

Согласно фиг. 8 мультиплексор 750 сначала получает 28 битов данных Ik, выдаваемых блоком вставки битов 710. Затем переключатель 812 мультиплексора 750 подключается к схеме задержки 822, пока от блока вставки битов 710 не будут получены первые 24 бита данных из 28 битов данных Ik. Схема задержки 822 задерживает первые 24 полученных бита данных Ik. После этого переключатель 812 подключается к схеме задержки 824, пока от блока вставки битов 710 не будут получены оставшиеся 4 бита данных из 28 битов данных Ik. Схема задержки 824 задерживает оставшиеся 4 бита данных.

Таким же образом мультиплексор 750 получает 28 первых битов четности Ck, выдаваемых первым составным кодером 720. Затем переключатель 814 мультиплексора 750 подключается к схеме задержки 826, пока от первого составного кодера 720 не будут приняты первые 24 бита данных из 28 первых битов четности Ck, и схема задержки 826 задерживает полученные первые биты четности Ck. После этого переключатель 814 подключается к схеме задержки 828, пока от первого составного кодера 720 не будут получены оставшиеся 4 первых бита четности из 28 первых битов четности Ck, и схема задержки 828 задерживает полученные оставшиеся 4 первых бита четности.

После этого мультиплексор 750 получает 28 вторых битов четности Dk, выдаваемые вторым составным кодером 740. Затем переключатель 816 мультиплексора 750 подключается к схеме задержки 830, пока от второго составного кодера 740 не будут получены первые 24 бита данных из 28 вторых битов четности Dk, и схема задержки 830 задерживает полученные вторые биты четности Dk. Затем переключатель 816 подключается к схеме задержки 832, пока от второго составного кодера 740 не будут получены оставшиеся 4 вторых бита четности из 28 вторых битов четности Dk, и схема задержки 832 задерживает полученные оставшиеся 4 вторых бита четности.

Согласно описанному выше мультиплексор 750 последовательно получает 28 битов данных Ik, 28 первых битов четности Сk и 28 вторых битов четности Dk и по отдельности сохраняет первые 24 бита и оставшиеся 4 бита из соответствующих битов в соответствующих схемах задержки. Переключатели 812-816 действуют под управлением контроллера, не изображенного на фигуре. Далее каждая из схем задержки 822-832 состоит из каскадированных элементов памяти и хранит входные биты, пока не завершится соответствующий процесс задержки.

По завершении процесса задержки переключатель 844 подключается к переключателю 842, а переключатель 842 подключается к схеме задержки 822. Таким образом, выходной сигнал схемы задержки 822 выводится через переключатели 842 и 844. После вывода одного бита данных, хранящегося в схеме задержки 822, переключатель 842 подключается к схеме задержки 824, при этом переключатель 844 остается подключенным к переключателю 842. Тогда один из оставшихся битов данных, хранящийся в схеме задержки 824, выводится через переключатели 842 и 844. Таким образом, бит данных, хранящийся в схеме задержки 822, пробивается, и на его место выводится бит данных, хранящийся в схеме задержки 824. После этого переключатель 842 подключается к схеме задержки 822, при этом переключатель 844 все еще остается подключенным к переключателю 842. При 4-кратном повторении вышеозначенного процесса биты данных, хранящиеся в схеме задержки 822, пробиваются и четыре бита данных, хранящиеся в схеме задержки 824, вставляются в четыре позиции пробивки.

После этого переключатель 842 подключается к схеме задержки 822, при этом переключатель 844 остается подключенным к переключателю 842. Таким образом, выходной сигнал схемы задержки 822 выводится через переключатели 842 и 844. После вывода одного бита данных, хранящегося в схеме задержки 822, переключатель 842 подключается к схеме задержки 828, при этом переключатель 844 остается подключенным к переключателю 842. Тогда один из оставшихся четырех первых битов четности, хранящихся в схеме задержки 828, выводится через переключатели 842 и 844. После этого переключатель 842 вновь подключается к схеме задержки 822, при этом переключатель 844 все еще остается подключенным к переключателю 842. При 4-кратном повторении вышеозначенного процесса биты данных, хранящиеся в схеме задержки 822, пробиваются и четыре первых бита четности, хранящиеся в схеме задержки 828, вставляются в позиции пробивки.

Таким образом, биты данных и оставшиеся четыре первых бита четности выводятся попеременно. Затем переключатель 842 подключается к схеме задержки 822, при этом переключатель 844 остается подключенным к переключателю 842. Таким образом, выходной сигнал схемы задержки 822 выводится через переключатели 842 и 844. После вывода одного бита данных, хранящегося в схеме задержки 822, переключатель 842 подключается к схеме задержки 832, при этом переключатель 844 остается подключенным к переключателю 842. Тогда один из оставшихся четырех вторых битов четности, хранящихся в схеме задержки 832, выводится через переключатели 842 и 844. После этого переключатель 842 вновь подключается к схеме задержки 822, при этом переключатель 844 все еще остается подключенным к переключателю 842. При 4-кратном повторении вышеозначенного процесса биты данных, хранящиеся в схеме задержки 822, пробиваются и четыре вторых бита четности, хранящиеся в схеме задержки 832, вставляются в позиции пробивки.

Посредством вышеописанной процедуры 24 бита данных, хранящиеся в схеме задержки 822, пробиваются, в позиции пробивки вставляются 4 бита данных, хранящиеся в схеме задержки 824, 4 первых бита четности, хранящиеся в схеме задержки 828, и 4 вторых бита четности, хранящиеся в схеме задержки 832. Соответственно мультиплексор 750 пробивает биты данных Ik, выдаваемые блоком вставки битов 710, и вставляет в пробитые под вставку позиции 8 битов четности, тем самым выдавая 24 бита данных.

По завершении вышеозначенного процесса переключатель 844 подключается к схеме задержки 826. Таким образом, выводятся 24 первых бита четности Сk, хранящиеся в схеме задержки 826. После этого переключатель 844 подключается к схеме задержки 830 с целью вывода 24 вторых битов четности Dk, хранящихся в схеме задержки 830.

Согласно фиг.9 в кодере, изображенном на фиг.7, отвечающем второму варианту реализации, блок вставки битов 710 вставляет 12 битов в 16 входных битов данных, генерируя 28 битов данных Ik. Первый и второй составные кодеры 720 и 740 генерируют соответственно 28 первых битов четности Ck и 28 вторых битов четности Dk. Мультиплексор 750 пробивает 28 битов данных Ik в 12 позициях вставки, после чего вставляет туда избыточные биты данных, т.е. 4 избыточных бита данных, 4 избыточных первых бита четности и 4 избыточных вторых бита четности. После этого мультиплексор 750 последовательно выдает биты данных Ik, первые биты четности Ck и вторые биты четности Dk.

В процессе декодирования выходные значения мультиплексора 750 демультиплексируются на участок битов данных, участок первых битов четности и участок вторых битов четности, причем участок битов данных пробивается значением -5 на участке вставки бита. Обработанные таким образом биты данных декодируются существующим декодером. (См. Claude Berrou, Alain Glavieux and Punya Thitmajshima Near Shannon Limit Error-Correction Coding and Decoding: Turbo-Codes (1)).

Третий вариант реализации

Кодер, отвечающий третьему варианту реализации настоящего изобретения, вставляет биты данных, имеющие особую логику, среди битов данных в битовые позиции, характеризующиеся вероятностью возникновения ошибки выше нормы, причем базовые кодеры кодируют биты данных со вставленными особыми битами и генерируют хвостовые биты, добавляемые к кодированным битам данных. Таким образом, кодер, отвечающий третьему варианту реализации, осуществляет функцию указания окончания как путем вставки битов, так и путем добавления хвостовых битов.

Фиг. 10 представляет собой схему канального кодера, отвечающего третьему варианту реализации настоящего изобретения. Согласно фиг.10 блок вставки битов 1010 получает 16 входных битов и имеет ту же структуру, что и блок вставки битов 310, отвечающий первому варианту реализации. Блок вставки битов 1010 вставляет 8 нулевых битов в каждый кадр в 8 позиций битов данных, характеризующиеся вероятностью ошибки выше нормы, под управлением контроллера, не изображенного на фигуре. Соответственно в данном иллюстративном варианте реализации блок вставки битов 1010 выдает 24 бита данных Ik, которые одновременно поступают на мультиплексор 1050, первый составной кодер 1020 и перемежитель 1030.

Далее перемеженные биты данных Ik, выдаваемые перемежителем 1030, поступают на составной базовый кодер 1040. Первый базовый кодер 1020 представляет собой рекурсивный систематический базовый кодер, изображенный на фиг.11, структура которого предусматривает генерирование хвостовых битов, добавляемых к кодированным битам данных. Кроме того, первый составной кодер имеет структуру, не предусматривающую генерирование хвостовых битов для указания окончания, подобную той, что изображена на фиг.5, иллюстрирующей первый вариант реализации.

Ниже приведено описание работы первого составного кодера 1020 со ссылкой на фиг.11. Для кодирования переключатель 1111 подключает входной узел к логическому элементу "исключающее ИЛИ" 1131, переключатель 1113 поддерживается в состоянии ВЫКЛ, а переключатель 1115 подключается к логическому элементу "исключающее ИЛИ" 1135. Тогда 24 бита данных Ik последовательно поступают на схемы задержки 1121-1127 через переключатель 1111 и логический элемент "исключающее ИЛИ" 1131, при этом логический элемент "исключающее ИЛИ" 1135 выдает кодированные биты данных. После подобной кодировки всех битов данных Ik с помощью схем задержки 1121-1127 и логического элемента "исключающее ИЛИ" 1135 переключатель 1111 подключается к логическим элементам "исключающее ИЛИ" 1133 и 1131, переключатель 1113 переводится в состояние ВКЛ и переключатель 1115 подключается к переключателю 1113. Тогда биты данных, сохраненные в схемах задержки 1121-1127 подаются обратно, подвергаются операции "исключающее ИЛИ" и выводятся через переключатель 1115, и, таким образом, генерируются нулевые биты. В данном случае нулевые значения, хранящиеся в схемах задержки 1121-1127, становятся хвостовыми битами и выводятся через переключатель 1115. Количество генерируемых хвостовых битов соответствует количеству схем задержки в составном кодере 1020. Согласно фиг. 11 составной кодер 1020 генерирует 4 хвостовых бита на кадр и также генерирует кодированные биты для соответствующих хвостовых битов.

Соответственно первый составной кодер 1020 генерирует 24 первых бита четности Ck и, после обработки последнего бита данных (т.е. 24-го бита данных), переключатель 1111 подключается к логическому элементу "исключающее ИЛИ" 1133, переключатель 1113 подключается к переключателю 1111 и переключатель 1115 подключается к переключателю 1113; чтобы генерировать 4 хвостовых бита, нужно повторить тот же процесс четыре раза. В результате этой процедуры на мультиплексор 1050 выводится 28 битов четности Сk и 4 хвостовых бита.

Кроме того, перемежитель 1030 перемежает 24 бита данных Ik, выдаваемых блоком вставки битов 1010, и выдает перемеженные биты данных на второй составной кодер 1040. Второй составной кодер 1040 кодирует перемеженные биты данных таким же образом, как и первый составной кодер 1020, генерируя 24 вторых бита четности Dk, которые поступают на мультиплексор 1050.

Перемеженные на покадровой основе биты данных, выдаваемые перемежителем 1030, кодируются вторым составным кодером 1040, имеющим такую же структуру, что изображена на фиг. 5. Второй составной кодер 1040 представляет собой рекурсивный систематический сверточный кодер, изображенный на фиг. 5. Кроме того, второй составной кодер 1040 имеет структуру, которая не позволяет генерировать хвостовые биты.

Мультиплексор 1050 пробивает биты данных Ik, вставляет в позиции пробивки 4 первых бита четности Ck и избирательно выводит оставшиеся 24 первых бита четности Ck и 24 вторых бита четности Dk.

Фиг.12 представляет собой схему, иллюстрирующую мультиплексор 1050. Согласно фиг.12 мультиплексор 1050 сначала получает 24 бита данных Ik, выдаваемых блоком вставки битов 1010. Затем схема задержки 1222 мультиплексорa 1050 сохраняет полученные 24 бита данных Ik.

После этого мультиплексор 1050 получает 28 первых битов четности Сk, выдаваемых первым базовым кодером 1020. Затем переключатель 1212 мультиплексорa 1050 подключается к схеме задержки 1224, пока от первого составного кодера 1020 не будут приняты первые 24 из первых битов четности Ck, и схема задержки 1224 сохраняет полученные первые биты четности Ck. После этого переключатель 1212 подключается к схеме задержки 1226, пока от первого составного кодера 1020 не будут получены оставшиеся 8 битов из 32 первых битов четности Ck, и схема задержки 1226 сохраняет оставшиеся 8 из первых битов четности Ck.

После этого мультиплексор 1050 получает 24 вторых бита четности Dk, выдаваемых вторым составным кодером 1040. Затем схема задержки 1228 мультиплексора 1050 сохраняет полученные 24 вторых бита четности Dk.

Последовательно генерированные, таким образом, 24 бита данных Ik, 28 первых битов четности Ck и 24 вторых бита четности Dk поступают на мультиплексор 1050. Мультиплексор 1050 сохраняет последовательно получаемые биты данных Ik, первые биты четности Ck и вторые биты четности Dk в соответствующих схемах задержки в порядке получения, причем первые 24 бита и оставшиеся 4 бита из 28 первых битов четности Ck сохраняются по отдельности в соответствующих схемах задержки. Каждая из схем задержки 1222-1228 состоит из каскадированных элементов памяти и хранит соответствующие входные биты, пока не завершится вышеописанный процесс задержки.

По завершении вышеописанного процесса задержки переключатель 1236 подключается к переключателю 1234, а переключатель 1234 подключается к схеме задержки 1222. Таким образом, выходной сигнал схемы задержки 1222 выводится через переключатели 1234 и 1236. После вывода бита данных, хранящегося в схеме задержки 1222, в заранее заданной позиции, переключатель 1234 подключается к схеме задержки 1226, при этом переключатель 1236 остается подключенным к переключателю 1234. Тогда один из избыточных первых битов четности, хранящийся в схеме задержки 1226, выводится через переключатели 1234 и 1236. Таким образом, бит данных, хранящийся в схеме задержки 1222, пробивается и в позицию пробивки вставляется первый бит четности, хранящийся в схеме задержки 1226. После этого переключатель 1234 вновь подключается к схеме задержки 1222, при этом переключатель 1236 остается подключенным к переключателю 1234. Вышеозначенная операция повторяется 8 раз с целью пробивки восьми битов данных, хранящихся в схеме задержки 1222, и вставки в позиции пробивки 8 избыточных первых битов четности, хранящихся в схеме задержки 1226. В результате 24 бита данных Ik пробиваются с целью вставки 8 первых битов четности в позиции пробивки (т.е. позиции вставки) и, таким образом, выводится 24 бита.

После этого переключатель 1236 подключается к выходу схемы задержки 1224. Тогда 24 первых бита четности Сk, хранящиеся в схеме задержки 1224, выводятся через переключатель 1236. Затем переключатель 1236 переключается на схему задержки 1228 с целью вывода 24 вторых битов четности Dk, хранящихся в схеме задержки 1228.

Согласно фиг. 13 в кодере, изображенном на фиг.10, отвечающем третьему варианту реализации, блок вставки битов 1010 вставляет 8 битов в 16 входных битов данных, генерируя 28 битов данных Ik. В качестве составного кодера используется рекурсивный систематический составной кодер, генерирующий хвостовые биты. В этом случае базовый кодер генерирует, в сумме, 32 бита данных, в том числе 24 кодированных бита данных, 4 хвостовых бита и кодированные данные 4 хвостовых битов. При выводе 24 кодированных битов данных сначала пробиваются входные биты данных Ik с целью вставки оставшихся 8 первых битов четности (т. е. 4 хвостовых битов и кодированных данных 4 хвостовых битов) в позиции пробивки битов.

Канально-кодированные символы со вставленными особыми битами передаются по каналу, и затем приемник принимает и декодирует канально-кодированные символы. В процессе декодирования выходные значения мультиплексора 1050 демультиплексируются на участок битов данных, участок первых битов четности и участок вторых битов четности, причем участок битов данных пробивается значением, например, -5 на участке вставки бита. Обработанные таким образом биты данных декодируются существующим декодером. (См. Claude Berrou, Alain Glavieux and Punya Thitmajshima Near Shannon Limit Error-Correction Coding and Decoding: Turbo-Codes (1)).

В вышеприведенных соответствующих вариантах реализации предполагается, что кодер вставляет особые биты на последнем участке битового потока данных. Таким образом, кодер вставляет особые биты в концевой участок кадровых данных, подлежащих передаче. Поскольку биты данных, поступающие на второй составной кодер канального кодера, перемежаются перемежителем до подачи на второй составной кодер, последняя позиция бита данных, поступившего на первый составной кодер, может не совпадать с последней позицией бита данных, поступившего на второй составной кодер. Кроме того, поскольку позиции вставки особых битов, поступающих на второй составной кодер, зависят от размера и типа перемежителя, необходим способ определения последнего участка битового потока данных, поступающего на первый и второй составные кодеры канального кодера.

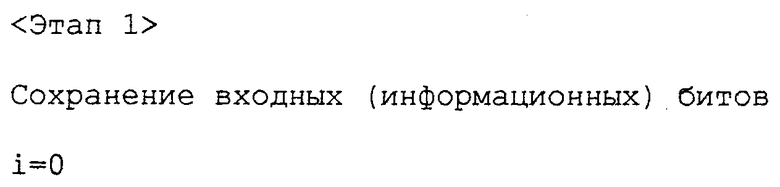

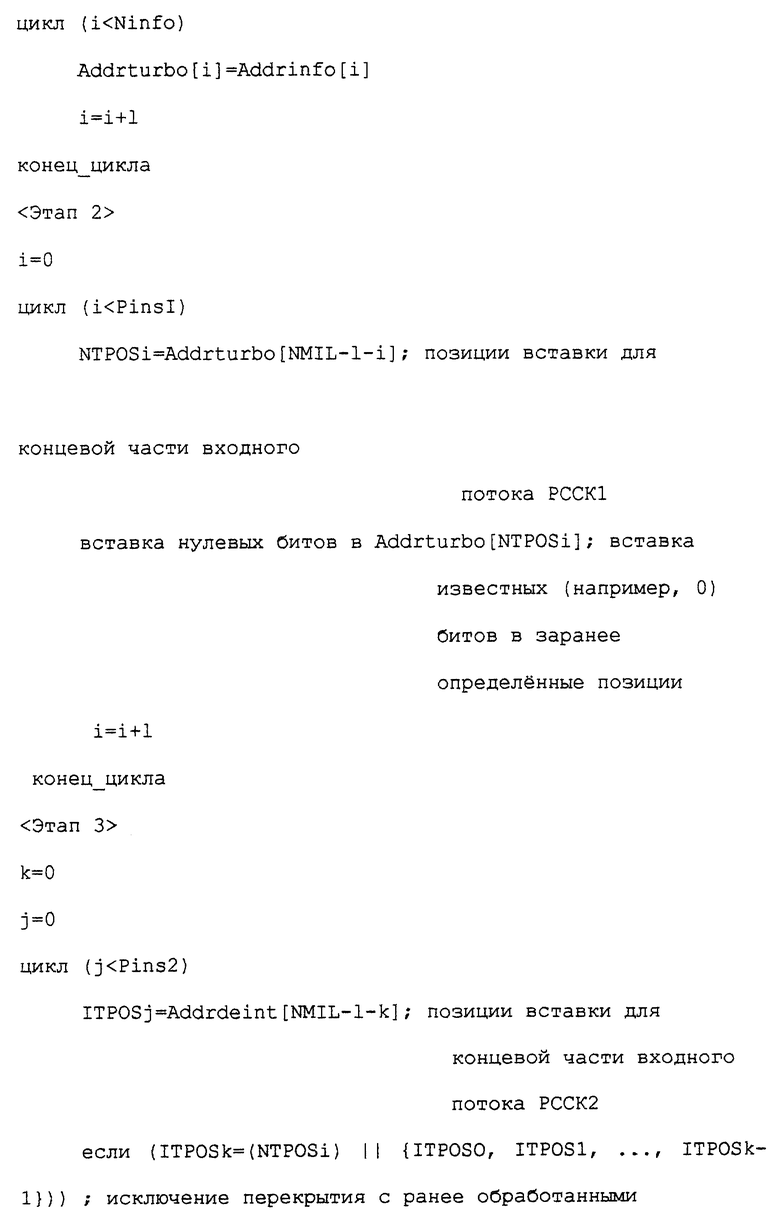

Настоящее изобретение предусматривает способ определения позиции вставки особого бита, которая зависит от перемежителя канального кодера. Фиг.14 иллюстрирует процедуру определения позиции вставки особого бита в канальном кодере. Блок-схема алгоритма, изображенная на фиг.14, описывает программу, которую должен выполнять канальный кодер, изображенный на фиг.3. В нижеследующем описании первый составной кодер соответствует первому составному кодеру 320, второй составной кодер соответствует второму составному кодеру 340, а перемежитель соответствует перемежителю 330. Кроме того, программа, представленная блок-схемой, изображенной на фиг.14, управляет работой блока вставки битов 310 по вставке особых битов. Когда блок вставки битов 310 имеет структуру, изображенную на фиг.4, блок-схема, изображенная на фиг.14, может выполняться контроллером, не изображенным на фигуре, который управляет работой переключателя 434 в блоке вставки битов 310. Таким образом, программа, представленная на фиг.14, управляет переключателем 434, задавая позицию вставки особого бита таким образом, чтобы особый бит, выдаваемый генератором битов 430, располагался на последнем участке битового потока данных.

Согласно фиг.14 на этапе 141 в качестве входных предусмотрены следующие значения: количество битов данных Ninfo, размер MIL-перемежителя NMIL, количество особых битов, подлежащих вставке в последнюю позицию бита данных, поступающего на первый составной кодер (Pins1), количество особых битов, подлежащих вставке в последнюю позицию бита данных, поступающего на второй составной кодер (Pins2), массивы Addrinfo[] и Addrdeint [] для хранения битовых позиций обращенно-перемеженных битов данных и переменных, массив Addrturbo[] для хранения позиций битов данных и переменные i и k, инициализируемые на "0". Затем, на этапе 142, выясняется, превышает ли переменная i количество битов данных Ninfo. Если i>Ninfo, программа переходит к этапу 144; иначе, программа переходит к этапу 143. Количество повторов этапа 143 равно количеству битов данных Ninfo. На этапе 143 позиции обращенно-перемеженных битов данных Addrinfo[] сохраняется в массиве Addrturbo[]. Этап 143 повторяется в соответствии с количеством битов данных Ninfo, чтобы сохранить все позиции битов данных Addrinfo[] в переменных Addrturbo[] для хранения позиций битов данных, после чего программа переходит к этапу 144, чтобы инициализировать i на "0".

После инициализации переменной i на этапе 145 выясняется, превышает ли переменная i количество битов Pins1, подлежащих вставке в последнюю позицию битового потока данных, поступающего на первый составной кодер. Количество повторов этапа 146 равно количеству Pins1 битов, подлежащих вставке в последнюю позицию битового потока данных. Если i≤Pins1, то программа переходит к этапу 146, на котором последняя позиция битового потока данных, поступающего на первый составной кодер, назначается позицией вставки особого бита и сохраняется в переменной NTPOSi. После повторения вышеупомянутой операции Pinsl раз, т.е. столько раз, сколько особых битов нужно вставить в последнюю позицию битового потока данных, поступающего на первый составной кодер, процесс переходит к этапу 147, на котором позиция особого бита, подлежащего вставке в последнюю позицию Pins4 битов данных, поступающих на первый составной кодер, сохраняется, после чего переменные k и j инициализируются на нуль.

После инициализации переменных k и j на этапе 148 выясняется, превышает ли переменная j количество Pins2 особых битов, подлежащих вставке в последнюю позицию битового потока данных, поступающего на второй составной кодер. Этапы 149, 150 и 151 повторяются столько раз, сколько особых битов нужно вставить в последнюю позицию битового потока данных, т.е. Pins2 раз. Если j≤Pins2, то процесс переходит к этапу 149, на котором позиции битов, расположенные на последнем участке битового потока данных, поступающего на второй составной кодер, выбираются позициями вставки особых битов и сохраняются в переменной ITPOSj. После этого, на этапе 150, выясняется, перекрываются ли значения позиций, хранящихся в переменной ITPOSj, со значениями позиций, хранящихся в переменной NTPOSi. Иными словами, в переменной ITPOSj хранится информация по позициям особых битов, подлежащих вставке в последнюю позицию битов данных, поступающих на второй составной кодер, а в переменной NTPOSi хранится информация по позициям особых битов, подлежащих вставке в последнюю позицию битов данных, поступающих на первый канальный кодер. Поэтому, когда информация, хранящаяся в ITPOSj, перекрывается с информацией, хранящейся в NTPOSi, это значит, что одни и те же особые биты вставлены с перекрытием на последним участке битов данных, поступающих на первый и второй базовые кодеры.

Поэтому на этапе 150 выясняется, перекрываются ли хранящиеся в ITPOSj позиции битов, подлежащих вставке в последнюю позицию битов данных, поступающих на второй составной кодер, с позициями, которые были выбраны и сохранены в NTPOSi на этапе 146. Если ITPOSj перекрываются с NTPOSi, то на этапе 153 переменная k получает единичное приращение. После приращения переменной k, программа возвращается к этапу 148. Поэтому, когда позиции особых битов, подлежащих вставке в последние позиции битов данных, поступающих на первый и второй составные кодеры, взаимно перекрываются, позиции вставки других особых битов, подлежащих вставке в последнюю позицию битов данных, поступающих на второй кодер, сохраняются в ITPOSj, после чего снова выполняется этап 150 чтобы выяснить, перекрываются ли позиции, хранящиеся в ITPOSj, с позициями, хранящимися в NTPOSi. Если позиции, хранящиеся в ITPOSj, не перекрываются с позициями, хранящимися в NTPOSi, то на этапе 151 обе переменные, k и i, получают единичное приращение. После этого программа возвращается к этапу 148. Количество повторов этапов 148-153 равно Pins2. После того как вышеупомянутые этапы повторены Pins2 раз (т.е., когда j>Pins2), осуществляется переход от этапа 148 к этапу 152, на котором производится вывод переменных ITPOSk и NTPOSk, в которых хранятся позиции вставки особых битов.

Поэтому, если на этапах 148 и 152 выясняется, что битовые позиции, хранящиеся в ITPOSj, перекрываются с позициями вставки особых битов, хранящимися в NTPOSi, то позиция особого бита, подлежащего вставке в последней позиции битового потока данных, поступающего на второй составной кодер, сдвигается с целью назначения на другую позицию. Если же они не перекрывают друг друга, то назначенная позиция, расположенная в последней позиции битового потока данных, поступающего на второй составной кодер, остается неизменной. Согласно данному варианту реализации, если битовые позиции, хранящиеся в ITPOSj, перекрываются с позициями вставки особых битов, хранящимися в NTPOSi, то изменяется позиция вставки особого бита в битовый поток данных, поступающий на второй составной кодер. Однако можно также изменять позицию вставки особого бита в битовый поток данных, поступающий на первый составной кодер.

Для лучшего понимания работы программы, представленной на фиг.14, опишем более подробно, как именно программа определяет позицию вставки особого бита в соответствии с перемежителем.

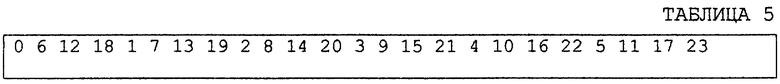

Прежде всего, если принять, что длина входного битового потока данных равна 16 битов и количество особых битов, подлежащих вставке, равно 8, то размер используемого перемежителя равен (длина битового потока данных)+(количество особых битов, подлежащих вставке) =16+8=24 бита. Поэтому в данном случае предполагается, что перемежитель имеет длину 24 бита, как показано в таблице 5.

В таблице 5 показаны положения битов, расположенные в порядке вывода из перемежителя. Таким образом, "0", находящийся в первой битовой позиции, означает, что первым выведен 0-й входной бит; "6", находящаяся во второй битовой позиции, означает, что следующим выведен шестой входной бит; и "12", находящаяся в третьей битовой позиции, означает, что после этого выведен двенадцатый входной бит.

Ниже, со ссылкой на фиг.14, приведено описание способа определения позиций вставки для перемежителя. На этапе 141 осуществляется ввод длины битового потока данных, Ninfo= 16, размера MIL-перемежителя, NMIL=24, количества особых битов, подлежащих вставке в конец битового потока данных, поступающего на первый составной кодер (Pinsl=4), количества особых битов, подлежащих вставке в конец битового потока данных, поступающего на второй составной кодер (Pins2=4), позиции битов данных Addrinfo[24], позиций обращенно-перемеженных битов данных и переменных Ad-drdeinst[24], Addrturbo[24] для хранения позиций битов данных, и переменные i и k инициализируются на "0".

После этого на этапе 142 выясняется, превышает ли переменная i количество битов данных Ninfo=16. Если i>Ninfo(=16), то программа переходит к этапу 144; иначе, программа переходит к этапу 143. В этом месте, этап 143 повторяется 16 раз, что соответствует количеству битов данных Ninfo=16, и 16 позиций битов данных Addrinfo[16] последовательно сохраняются в массиве Addrturbo[16]. После этого программа переходит к этапу 144 с целью инициализации переменной i на "0".

После инициализации переменной i на этапе 145 выясняется, превышает ли переменная i количество битов, подлежащих вставке в конец битового потока данных, поступающего на первый составной кодер (Pins1=4), Этап 146 повторяется столько раз, сколько битов (Pinsl=4) подлежит вставке в конец битового потока данных. Если i<Pinsl(=4), то программа переходит к этапу 146, на котором последняя позиция в битовом потоке данных, поступающем на первый составной кодер, назначается позицией вставки особого бита и затем сохраняется в переменных NTPOSi. Таким образом, позиции последних 4 битов до перемежения сохраняются в переменных NTPOSi. После того как вышеупомянутая операция повторена столько раз, сколько особых битов, Pins1=4, надлежит вставить в последнюю позицию битового потока данных, поступающего на первый составной кодер, процесс переходит к этапу 147, на котором позиция особого бита, подлежащего вставке в последнюю позицию Pins= 4 битов данных, поступающих на первый составной кодер, сохраняются, после чего переменные k и i инициализируются на нуль. В таблице 6 показаны позиции 4 битов, вставленных в последнюю позицию кадра битов данных до перемежения (т.е. 20, 21, 22 и 23).

Затем на этапе 148 выясняется, превышает ли переменная k количество Pins2= 4 особых битов, подлежащих вставке в последнюю позицию битового потока данных, поступающего на второй составной кодер. Этапы 149, 150 и 151 повторяются четыре раза, что соответствует количеству особых битов, подлежащих вставке в последнюю позицию битового потока данных (Pins2=4). Если j≤Pins2(= 4), то процесс переходит к этапу 149, на котором позиции последних 4 битов, расположенных на последнем участке битового потока данных, поступающего на второй составной кодер, выбираются в качестве позиций вставки особых битов и сохраняются в переменных ITPOSj. В таблице 7 показаны позиции вставки последних 4 битов, показанных в таблице 6, определенные для первого составного кодера до перемежения, совместно с позициями вставки последних четырех битов, определенными для второго составного кодера после перемежения.

В данном случае позиции вставки последних 4 битов до перемежения, определенные для первого составного кодера, это {20, 21, 22, 23}, а позиции вставки последних 4 битов после перемежения, определенные для второго составного кодера, это {5, 11, 17, 23}. Заметим, что определенные позиции вставки перекрываются только в позиции вставки "23". Таким образом, всего определено 7, а не 8, позиций вставки. Соответственно, чтобы определить еще один бит, на этапе 15 выясняется, перекрываются ли хранящиеся в переменной ITPOSj позиции битов, подлежащих вставке в последнюю позицию битового потока данных, поступающего на второй базовый кодер, с позициями, выбранными на этапе 146 и сохраненными в переменной NTPOSi. В данном случае, поскольку из таблиц 6 и 7 следует, что 23-я позиция является позицией перекрытия, программа переходит к этапу 148 через этап 151. Затем процесс переходит к этапу 149, на котором в ITPOSj сохраняется другая позиция вставки бита, подлежащего вставке в последнюю позицию битового потока данных, поступающего на второй составной кодер, с целью определения 19-й битовой позиции в качестве позиции вставки. После этого на этапе 150 вновь выясняется, перекрываются ли битовые позиции, хранящееся в ITPOSj, с битовыми позициями, хранящимися в NTPOSi. В данном случае, поскольку 19-ая битовая позиция не является позицией перекрытия, эта выбранная позиция непременно сохраняется. После этого этапы 148, 149, 150, 151 и 153 повторяются Pins2 раз. После повторения вышеперечисленных этапов на этапе 152 выводятся переменные ITPOSk и NTPOSk, в которых хранятся сохраненные позиции вставки. В таблице 8 показано 8 позиций вставки, выводимых из переменных ITPOSk и NTPOSk.

В данном случае программу, представленную на фиг.14, можно выразить следующим образом (см. в конце описания).

Согласно вышеприведенному описанию канальный кодер, отвечающий настоящему изобретению, включающий в себя рекурсивные систематические составные кодеры, может осуществлять функцию кодирования с использованием кадровой структуры, имеющей эффект указания окончания.

Изобретение относится к устройству и способу канального кодирования в системе заранее известных битов на входном каскаде канального кодирующего устройства. Технический результат - повышение скорости передачи информации и точности кодирования за счет уменьшения вероятности возникновения ошибки. Турбокодирующее устройство включает в себя блок вставки битов, предназначенный для вставки, по меньшей мере, одного заранее известного бита в последнюю позицию битового потока данных, поступающего на первый составной кодер, и вставки, по меньшей мере, одного заранее известного бита в последнюю позицию перемеженного битового потока данных, поступающего на второй составной кодер; первый составной кодер, предназначенный для кодирования битов данных со вставленными заранее известными битами для генерирования первых символов четности; перемежитель, предназначенный для перемежения битов данных со вставленными заранее известными битами; второй составной кодер, предназначенный для кодирования перемеженных битов данных для генерирования вторых символов четности, и мультиплексор, предназначенный для мультиплексирования выходных сигналов блока вставки битов, первого составного кодера и второго составного кодера. 2 с. и 4 з.п.ф-лы, 14 ил., 8 табл.

| US 5446747 А, 29.08.1995 | |||

| СПОСОБ ВЫДЕЛЕНИЯ ДОПОЛНИТЕЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ В ЦИФРОВОМ КАНАЛЕ СВЯЗИ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1995 |

|

RU2113767C1 |

| КАСКАДНЫЙ СОЛОМОТРЯС | 0 |

|

SU235477A1 |

| US 4394642 А, 19.07.1983 | |||

| US 5408502 А, 18.04.1995 | |||

| US 5233629 А, 03.08.1993. | |||

Авторы

Даты

2002-09-27—Публикация

1999-08-20—Подача