Область техники

Изобретение относится в общем случае к системе связи, в которой производят покадровую обработку данных, в частности к устройству канального кодирования и к способу его осуществления.

Уровень техники

В системах связи для обработки речевых сигналов, сигналов передачи символов, сигналов передачи изображения и видеосигналов передачу данных обычно осуществляют покадровым способом. Кадр определяет основной временной интервал в системе. Кроме того, в системе для осуществления связи посредством такой покадровой передачи данных канальный кодер также должен выполнять покадровое кодирование данных для исправления ошибок. В этом случае для обозначения завершения каждого кадра канальный кодер производит добавление равных нулю хвостовых битов для того, чтобы декодер, используя эту информацию, мог осуществлять эффективное декодирование кадров. Хвостовые биты кодера представляют собой фиксированную последовательность битов, которую добавляют в конец кадра данных для возврата сверточного кодера в известное состояние. В системе, отвечающей стандарту IS-95, для обозначения завершения кадра обычно используют нерекурсивный системный сверточный кодер, который добавляет в конец каждого кадра последовательность нулевых (0) битов, равную количеству устройств задержки. Однако, в отличие от нерекурсивного системного сверточного кодера, рекурсивный системный кодер не может для обозначения завершения кадра добавлять нулевые биты в конец кадра, поскольку входные биты подают обратно к устройствам задержки.

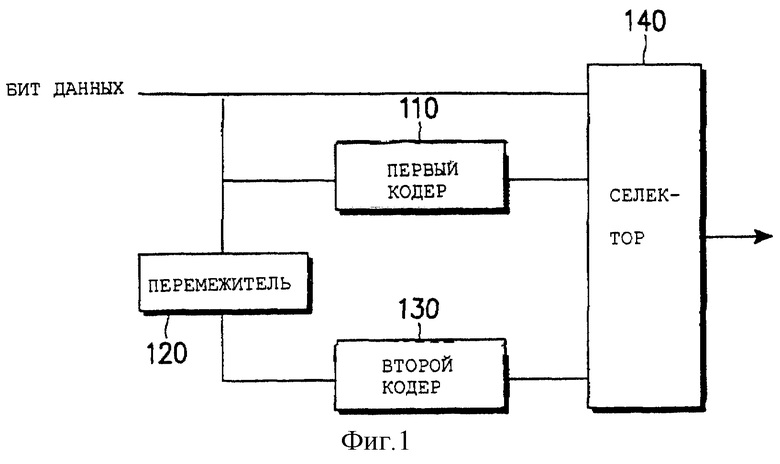

На фиг. 1 показана блок-схема обычного параллельного устройства турбокодирования, которое раскрыто в патенте US 5446747. Устройство кодирования из фиг. 1 представляет собой один из вариантов обычного рекурсивного системного устройства кодирования. Устройство турбокодирования осуществляет кодирование входного кадра из N бит в символы четности с использованием двух входящих в его состав простых кодеров и может иметь конфигурацию в виде либо параллельной, либо последовательной структуры. Кроме того, в устройстве турбокодирования фиг. 1 в качестве компонент кода используют рекурсивные системные сверточные коды.

Устройство турбокодирования из фиг.1 включает в себя перемежитель 120, помещенный между первым элементарным кодером 110 и вторым элементарным кодером 130. Перемежитель 120 имеет ту же емкость битов входных данных, что и длина кадра N, и осуществляет перестановку порядка следования битов данных, вводимых во второй элементарный кодер 130 для уменьшения корреляции между выходными сигналами первого и второго кодера.

Первый элементарный кодер 110 осуществляет кодирование битов входных данных, а перемежитель 120 осуществляет изменение чередования (или рандомизирует) биты потока входных данных в соответствии с заданным правилом таким образом, чтобы пакетные ошибки, вносимые каналом, могли быть преобразованы в случайные ошибки. Второй элементарный кодер 130 осуществляет кодирование выходного сигнала перемежителя 120.

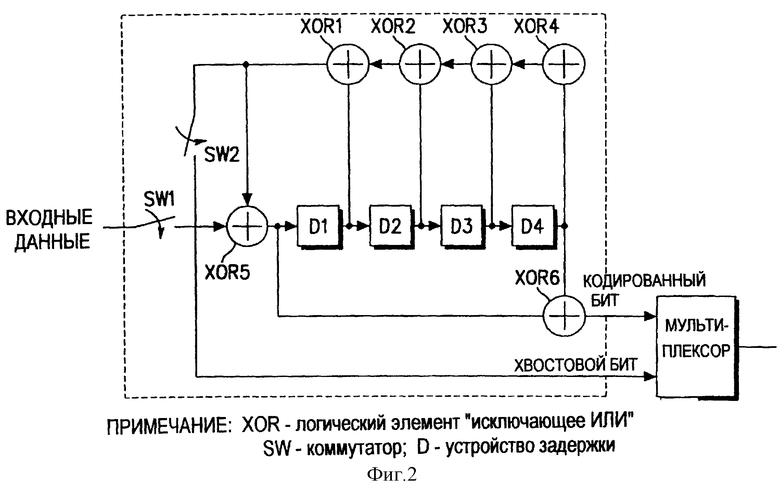

Фиг.2 представляет собой чертеж, на котором показана схема осуществления завершения в рекурсивном системном устройстве сверточного кодирования из фиг. 1. Для получения более подробной информации см. публикацию Д. Дивсалара и Ф. Поллара "О конструкции устройств автоматического установления исходящего соединения с повышенной скоростью", Доклад TDA о достигнутых результатах 42-123, 15 ноября 1995 г. Здесь установлено, что данные кадра, которые вводят в первый и второй элементарные кодеры 110 и 130, представляют собой данные, состоящие из 20 битов. На фиг.2 позициями D1-D4 обозначены устройства задержки, а позициями XOR1-XOR6 -логические элементы "исключающее ИЛИ".

Со ссылкой на фиг.2 для осуществления кодирования выполняют следующие операции. Коммутатор SW1 устанавливают в положение ВКЛ, а коммутатор SW2 устанавливают в положение ВЫКЛ. Затем входные данные кадра, состоящие из 20 битов, последовательно подают в устройства D1-D4 задержки и выполняют операцию "исключающее ИЛИ" посредством логических элементов XOR1-XOR6 "исключающее ИЛИ", осуществляя таким образом вывод кодированных битов на выходе логического элемента XOR6 "исключающее ИЛИ". Когда подобным образом осуществлено кодирование всех этих 20 битов данных, то для осуществления завершения кадра коммутатор SW1 устанавливают в положение ВЫКЛ, а коммутатор SW2 - в положение ВКЛ. Затем логические элементы XOR1-XOR4 "исключающее ИЛИ" выполняют логическую операцию "исключающее ИЛИ", соответственно, для битов выходных данных от устройств задержки и для соответствующих возвращенных битов данных, осуществляя таким образом вывод нулевых битов. Полученные в результате этого нулевые биты снова подают на входы устройств D1-D4 задержки и запоминают в них. Эти нулевые биты, введенные в устройства D1-D4 задержки, становятся теми хвостовыми битами, которые подают в мультиплексор.

Мультиплексор осуществляет мультиплексирование кодированных битов данных и хвостовых битов с выхода элементарного кодера. Количество сгенерированных хвостовых битов зависит от количества устройств задержки, включенных в состав элементарных кодеров 110 и 130. Схема осуществления завершения из фиг.2 генерирует 4 хвостовых бита для каждого кадра плюс дополнительные кодированные биты, генерацию которых производят для каждого из соответствующих хвостовых битов, что нежелательным образом увеличивает общее конечное число кодированных битов, приводящее к уменьшению скорости передачи данных. То есть, если скорость передачи данных определяют как:

Скорость Передачи Данных = (Количество Битов Входных Данных/(Количество Битов Выходных Данных),

то элементарный кодер, имеющий структуру согласно фиг.2, имеет скорость передачи данных, равную

Скорость Передачи Данных = (Количество Битов Входных Данных/{(Количество Закодированных Битов Данных) + (Количество Хвостовых Битов) + (Количество Закодированных Битов для Хвостовых Битов)}.

Следовательно, поскольку данные кадра состоят из 20 битов, а количество устройств задержки равно 4-м, то скорость передачи данных на фиг.2 равна 20/28.

Поэтому является очевидным тот факт, что эффективность рекурсивного системного сверточного кодера зависит от способа добавления хвостовых битов, поскольку сложно идеальным образом осуществить добавление в конец турбокодов.

Сущность изобретения

Исходя из этого, задачей настоящего изобретения является создание устройства и способа осуществления канального кодирования/декодирования с использованием в рекурсивном системном устройстве кодирования системы связи такой кадровой структуры, в которую вставляют заданные биты.

Другой задачей настоящего изобретения является создание рекурсивного системного устройства кодирования канала и способа вставки в данные кадра битов, имеющих определенное значение, в заданные места во время осуществления канального кодирования.

Еще одной задачей настоящего изобретения является создание устройства канального декодирования и способа декодирования кодированных данных канала, переданных из канального устройства кодирования, в котором при канальном кодировании осуществляют вставку битов, имеющих определенные значения, в заданные места данных кадра.

И еще одной задачей настоящего изобретения является создание устройства и способа вставки бита, имеющего определенное значение, в место, занимаемое определенным символом из кодированных символов канала, и осуществления декодирования с гибким выбором путем использования бита, имеющего определенное значение, для повышения производительности при канальном декодировании.

В соответствии с одним аспектом настоящего изобретения, предложено устройство канального декодирования для приемника, который осуществляет прием символов, кодирование которых выполнено посредством вставки в заданное место данных кадра, по меньшей мере, одного определенного бита. Устройство канального декодирования включает в себя блок вставки символов, принимающий символы, для вставки символа, имеющего определенное значение, в заданное место вставки определенного бита и вывода принятых символов, находящихся в остальных местах; и декодер для декодирования символов на выходе блока вставки символов.

В частности, устройство канального декодирования включает в себя демультиплексор, принимающий символы, для демультиплексирования принятых символов в символ данных, первый символ четности и второй символ четности; блок вставки символов для вставки символа, имеющего определенное значение, в заданное место вставки определенного бита в символе данных, и для вывода принятых символов, находящихся в остальных местах; первый декодер, в котором для генерации первого декодированного символа осуществлен гибкий выбор символа данных с выхода блока вставки символов и первого символа четности; первый перемежитель для перемежения выходного сигнала из первого декодера, второй декодер, в котором для генерации второго декодированного символа осуществлен гибкий выбор первого декодированного символа с выхода первого перемежителя и второго символа четности; элемент с жестким выбором для выполнения жесткого выбора вторых декодированных данных; и первый обращенный перемежитель для осуществления обращенного перемежения выходного сигнала элемента с жестким выбором.

В соответствии с другим аспектом настоящего изобретения, предложен способ канального декодирования для приемника, который осуществляет прием символов, кодирование которых выполнено посредством вставки в заданное место данных кадра, по меньшей мере, одного определенного бита. Способ канального декодирования включает в себя следующие операции: производят прием символов, осуществляют вставку символа, имеющего определенное значение, в заданное место вставки определенного бита и вывод принятых символов, расположенных в остальных местах; и осуществляют декодирование принятых символов, используя вставленный символ, имеющий определенное значение.

В частности способ канального декодирования включает в себя следующие операции: а) производят прием символов и демультиплексирование принятых символов с получением символа данных, первого символа четности и второго символа четности; б) осуществляют вставку символа, имеющего определенное значение, в заданное место вставки определенного бита в символе данных и вывод принятых символов, расположенных в остальных местах; в) для генерации первого декодированного символа осуществляют гибкий выбор того символа данных, в который вставлен символ, имеющий определенное значение, и первого символа четности; г) производят перемежение первого декодированного символа; д) для генерации второго декодированного символа осуществляют гибкий выбор первого перемеженного декодированного символа и второго символа четности; е) осуществляют обращенное перемежение второго декодированного символа; ж) во втором символе с обращенным перемежением устанавливают определенное значение соответствующего символа в месте вставки, возвращаются к операции в) и повторяют операции с в) по д); з) после выполнения операций с в) по д) осуществляют жесткий выбор вторых декодированных данных; и и) осуществляют обращенное перемежение второго декодированного символа, обработка которого произведена посредством жесткого выбора.

Краткое описание чертежей

Вышеуказанные и иные задачи, признаки и преимущества настоящего изобретения станут более очевидными из приведенного ниже подробного описания при его рассмотрении совместно с сопровождающими чертежами, в которых одинаковыми номерами ссылок обозначены одинаковые элементы. На чертежах:

фиг. 1 представляет собой блок-схему, на которой изображено устройство канального кодирования, известное из уровня техники и предназначенное для использования в системе беспроводной связи;

фиг.2 представляет собой подробную блок-схему, на которой изображен элементарный кодер, известный из уровня техники, показанный на фиг.1;

фиг. 3 представляет собой схему, на которой изображено устройство канального кодирования согласно первому варианту осуществления настоящего изобретения;

фиг. 4 представляет собой подробную схему, на которой изображен блок вставки битов из фиг.3;

фиг. 5 представляет собой подробную схему, на которой изображен элементарный кодер из фиг.3;

фиг. 6 представляет собой диаграмму, на которой показана процедура обработки бита согласно первому варианту осуществления настоящего изобретения;

фиг. 7 представляет собой схему, на которой показано устройство канального кодирования согласно второму варианту осуществления настоящего изобретения;

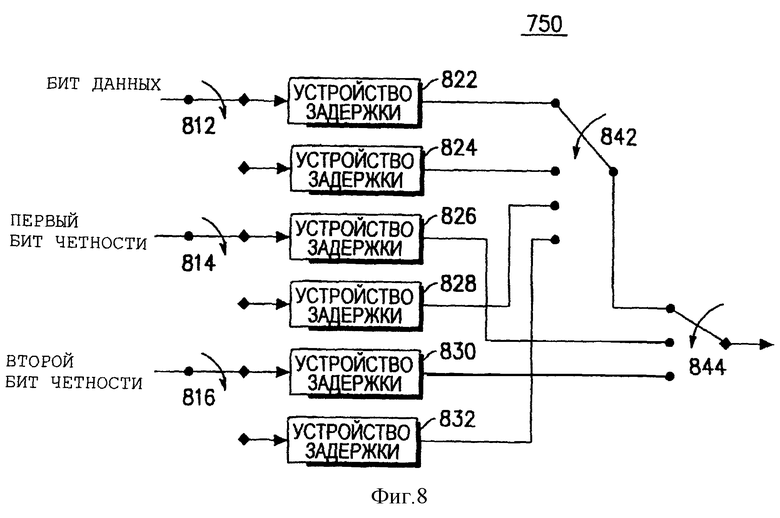

фиг. 8 представляет собой подробную схему, на которой изображен мультиплексор из фиг.7;

фиг. 9 представляет собой диаграмму, на которой показана процедура обработки бита согласно второму варианту осуществления настоящего изобретения;

фиг. 10 представляет собой схему, на которой изображено устройство канального кодирования канала согласно третьему варианту осуществления настоящего изобретения;

фиг. 11 представляет собой подробную схему, на которой изображен элементарный кодер из фиг.10;

фиг. 12 представляет собой подробную схему, на которой показан мультиплексор из фиг.10;

фиг.13 представляет собой диаграмму, на которой показана процедура обработки битов согласно третьему варианту осуществления настоящего изобретения;

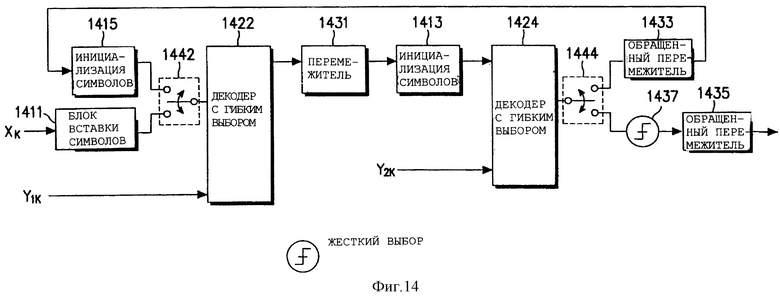

фиг. 14 представляет собой схему, на которой изображено устройство канального декодирования согласно варианту осуществления настоящего изобретения;

фиг.15 представляет собой подробную схему, на которой изображен инициализатор символа из фиг.14;

фиг. 16 представляет собой подробную схему, на которой изображено устройство канального декодирования согласно другому варианту осуществления настоящего изобретения.

Подробное описание предпочтительных вариантов осуществления изобретения

Описание предпочтительных вариантов осуществления настоящего изобретения будет приведено ниже со ссылкой на сопровождающие чертежи. В последующем описании не будет приведено подробного описания известных функций или конструкций, так как оно привело бы к неясностям в формулировках изобретения из-за излишних подробностей. Используемый здесь термин "бит данных" относится к незакодированным данным, а термин "бит четности" относится к данным, кодирование которых осуществлено элементарным кодером.

Обычно в системе связи передатчик осуществляет кодирование передаваемых данных с использованием устройства канального кодирования и передачу закодированных данных; а затем приемник осуществляет демодуляцию принятых из передатчика данных для преобразования принятых данных в исходные данные. Устройство канального кодирования осуществляет покадровое кодирование передаваемых данных и генерацию хвостовых битов, которые добавляют к каждому кадру для обозначения завершения кадра. В настоящем изобретении предложена структура кадра, воздействующая на завершение обработки в устройстве канального кодирования.

Структура кадра, воздействующая на завершение обработки, может быть осуществлена в соответствии с несколькими вариантами осуществления, описание которых приведено ниже:

Первый вариант осуществления: в каждый кадр канала осуществляют вставку нескольких определенных битов в тех местах, в которых существует более высокая вероятность возникновения ошибки, причем количество предназначенных для вставки битов задано количеством хвостовых битов. Поскольку элементарные рекурсивные кодеры не предназначены для генерации хвостовых битов, то вероятность возникновения ошибки определяют посредством эксперимента, а места вставок должны быть известны как устройству канального кодирования, так и устройству канального декодирования. В предпочтительном варианте определенные биты, предназначенные для вставки, должны представлять собой незначащие биты, которые оказывают либо незначительное воздействие на эффективность связи, либо не оказывают на нее никакого воздействия вне зависимости от того, осуществлена ли их передача или нет. Также они могут представлять собой заданные приемником кодированные биты или биты данных. Здесь считают, что они являются нулевыми битами.

Второй вариант осуществления; в каждый кадр канала осуществляют вставку нескольких битов в тех местах, в которых существует более высокая вероятность возникновения ошибки, причем количество предназначенных для вставки битов задано количеством хвостовых битов. Вставка определенных битов приводит к превышению заданной длины кадра. Введенные побитно биты данных кодируют с использованием элементарного кодера. Затем, при выводе кодированных данных канала осуществляют "прошивку" битов, превышающих длину кадра кодированных данных канала, в местах вставки битов во входных данных. Здесь рекурсивный системный кодер не осуществляет генерацию хвостовых битов, а устройство канального декодирования должно иметь известные сведения о местах вставки битов.

Третий вариант осуществления: в каждый кадр канала осуществляют вставку нескольких определенных битов в тех местах, в которых существует более высокая вероятность возникновения ошибки, причем количество предназначенных для вставки битов задано количеством хвостовых битов. Элементарный кодер осуществляет генерацию хвостовых битов завершения и соответствующих кодированных данных для хвостовых битов, после этого осуществляет "прошивку" битов данных в определенных местах вставки в каждом кадре канала для вставки хвостовых битов и кодированных данных для хвостовых битов в местах "прошивки", выбранных для вставки бита.

Первый вариант осуществления

Согласно первому варианту осуществления настоящего изобретения, для реализации функции завершения устройство кодирования не производит генерацию хвостовых битов, а выполняет вставку определенных битов в заданные места. В этом варианте осуществления один 24-битовый кадр включает в себя 16 битов данных и 8 определенных битов, где каждый из 8 определенных битов является нулевым битом, вставленным в кадр в местах расположения битов, имеющих более высокую вероятность ошибки. При этом места вставки бита определяют посредством экспериментального обнаружения тех мест, в которых возникает наибольшее количество ошибок при декодировании кодированных данных. Кроме того, в каждом элементарном кодере используют скорость кодирования, равную 1/3.

В этом варианте осуществления экспериментальное определение мест, имеющих более высокую вероятность ошибки при декодировании, осуществляют при кодировании данных 24-битового кадра (то есть, состоящего из 16-ти битов данных кадра плюс 8 определенных битов) с использованием турбокодера, имеющего скорость кодирования 1/3. Определяют места расположения восьми битов, имеющих относительно более высокую вероятность ошибки, и в определенные места производят вставку определенных битов. При этом, при декодировании кодированных данных кадра, в который вставлены определенные коды, декодирующему устройству известны места вставки битов.

Когда вставленные определенные биты являются нулевыми битами (в действительности, передачу этих битов, равных "0", осуществляют в виде "-1"), то для увеличения надежности значения нулевых битов в местах вставки перед декодированием заменяют на большое отрицательное значение (например, -5), имеющее сильное отклонение от "-1". Это выполняют для повышения производительности при декодировании, а значение вставленного определенного бита может быть изменено за время передачи по радиосвязи. Однако, поскольку для декодирующего устройства заранее известно местоположение принимаемого определенного бита, то в реальном процессе декодирования декодирующее устройство осуществляет вставку более высокого значения, отличающегося от "-1", для определенного бита. В этом случае для декодирующего устройства производительность декодирования может быть повышена посредством вставки определенного значения. Подробное описание этой операции декодирования будет приведено со ссылкой на фиг.14. Таким образом, декодирующему устройству, выполняющему декодирование битов, известны, по меньшей мере, 8 из 24 битов, поскольку их передачу осуществляют с большим отрицательным значением, что повышает производительность при декодировании. В этом варианте осуществления производительность возрастает при уменьшении длины кадра.

Фиг. 3 представляет собой схему, на которой изображено устройство турбокодирования, имеющее блок вставки битов для вставки определенных битов согласно первому варианту осуществления настоящего изобретения. Блок 310 вставки битов включает в себя генератор битов для генерации определенных битов посредством обработки битов входных данных и производит покадровую генерацию битов данных путем вставки определенных битов, генерация которых осуществлена генератором битов, в заданные места вставки битов. Первый элементарный кодер 320 кодирует биты данных, поступающие с выхода блока 310 вставки битов. Перемежитель 330 производит покадровое перемежение битов данных с выхода блока 310 вставки битов согласно заданному правилу, осуществляя изменение последовательности битов данных. В примере варианта осуществления в качестве перемежителя 330 используют диагональный перемежитель.

Второй элементарный кодер 340 осуществляет покадровое кодирование перемеженных битов данных с выхода перемежителя 330. В качестве первого и второго элементарных кодеров 320 и 340 могут быть использованы рекурсивные системные сверточные кодеры. Мультиплексор 350, управление которым производят посредством контроллера (не показан), осуществляет мультиплексирование выходных сигналов от блока 310 вставки битов, первого элементарного кодера 320 и второго элементарного кодера 340. При этом блок 310 вставки битов осуществляет вывод битов Iк данных. Первый элементарный кодер 320 осуществляет вывод первых битов Plk четности, а второй элементарный кодер 340 осуществляет вывод вторых битов P2k четности.

Фиг.4 представляет собой подробную блок-схему, на которой изображен блок 310 вставки битов из устройства турбокодирования, приведенного на фиг.3. Со ссылкой на фиг. 4 генератор 430 битов осуществляет генерацию определенных битов, которые предназначены для вставки в биты данных. При этом полагают, что определенные биты являются нулевыми битами. Устройства 412-426 задержки, которые могут состоять из запоминающих элементов, например, запоминающих триггеров, могут иметь структуру регистра последовательного сдвига для осуществления сдвига бита входных данных в соответствии с синхронизацией битов.

Для выбора выходных сигналов от устройств 412-426 задержки переключают коммутатор 432, управление которым осуществляют посредством не изображенного на чертеже контроллера (не показан). К тому же, под управлением не изображенного на чертеже контроллера осуществляют переключение коммутатора 432 на выходной сигнал следующего устройства задержки в тех местах, в которых осуществляют вставку в биты данных определенного бита с выхода генератора 430 битов. То есть, при вставке выбранного определенного бита в биты данных коммутатор 432 производит выбор бита данных с задержкой на один бит. Коммутатор 432 может быть реализован в виде мультиплексора. Для генерации битов Ik данных осуществляют под управлением не изображенного на чертеже контроллера переключение коммутатора 434 на выходные сигналы генератора 430 битов и коммутатора 432. Коммутатор 434, управляемый не изображенным на чертеже контроллером, производит выбор из битов данных определенных битов для вставки в заданные места.

Описание, относящееся к операции вставки определенных битов, будет приведено со ссылкой на фиг.4. Устройства 412-426 задержки осуществляют задержку битов входных данных в соответствии с синхронизацией битов. Сначала коммутатор 432 производит выбор битов входных данных (то есть, соединен с Полюсом 1), а коммутатор 434 первоначально соединен с коммутатором 432 (то есть, с Полюсом Б). Затем осуществляют вывод битов входных данных через коммутаторы 432 и 434. Между тем, когда место вставки бита определено, то под управлением контроллера коммутатор 432 соединяют с выходом устройства 412 задержки (то есть, с Полюсом 2), а коммутатор 434 соединяют с выходом генератора 430 битов (то есть, с Полюсом А). В результате, тракт для передачи битов данных отключают и вставляют нулевой бит с выхода генератора 430 битов в соответствующее место для бита. В том случае, когда после вставки нулевого бита нужно осуществлять непрерывный вывод битов данных, коммутатор 434 снова соединяют с коммутатором 432 посредством контроллера. То есть, поскольку после вставки нулевого бита выбор бита данных производят с задержкой на один бит, то вставка нулевого бита в заданное место может быть осуществлена без потери бита данных.

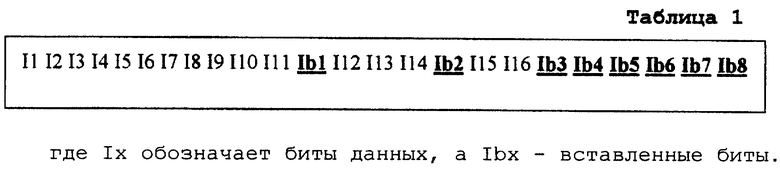

Вставку нулевых битов в биты данных для одного кадра производят путем повторения этого процесса. Когда после вставки нулевых битов получены биты данных для следующего кадра, то коммутатор 432 снова соединяют с узловой точкой входного бита (Полюс 1), а затем снова повторяют вышеописанный процесс. В том случае, когда для осуществления связи биты данных кодируют, вероятность возникновения ошибки статистически относительно более высока в хвостовой части потока битов данных, который вводят в соответствующие элементарные кодеры. Следовательно, места вставки нулевых битов с выхода генератора 430 битов могут находиться, в основном, в хвостовой части потока битов данных, как показано в примере из таблицы 1.

Причина, обуславливающая вставку определенных битов в поток битов данных, заключается в повышении производительности декодирования в приемнике. Поэтому предпочтительной является вставка определенных битов в те места расположения битов в кадре канала, которые имеют более высокую вероятность возникновения ошибки, причем количество вставленных битов определяется количеством хвостовых битов. В большинстве случаев места расположения битов с более высокой вероятностью возникновения ошибки находятся в хвостовой части потока битов данных, который подают в элементарные кодеры, что показано в таблице 1. Следовательно, вставку определенных битов осуществляют, в основном, в хвостовой части потоков битов данных. Измененный поток данных вводят, соответственно, в первый и второй элементарные кодеры 320 и 340. При этом, для второго элементарного кодера 340 вставка определенных битов должна быть осуществлена в хвостовую часть перемеженных битов данных выходного сигнала из перемежителя 330. Следовательно, это необходимо учитывать в устройстве вставки 310 битов при вставке определенных битов в биты данных, подаваемые во второй элементарный кодер 340.

Биты данных из таблицы 1, получаемые на выходе блока вставки 310 битов, подают параллельно и в первый элементарный кодер 320 и в перемежитель 330. Перемеженные биты данных одного кадра, полученные на выходе перемежителя 330, кодируют посредством второго элементарного кодера 340. На фиг.5 показана схема первого и второго элементарных кодеров 320 и 340 из фиг.3 в соответствии с первым вариантом осуществления. Показано, что первый и второй элементарные кодеры 320 и 340 представляют собой рекурсивные системные сверточные кодеры. Кроме того, как показано на фиг.5, элементарные кодеры 320 и 340 скомпонованы так, что не осуществляют генерацию хвостовых битов.

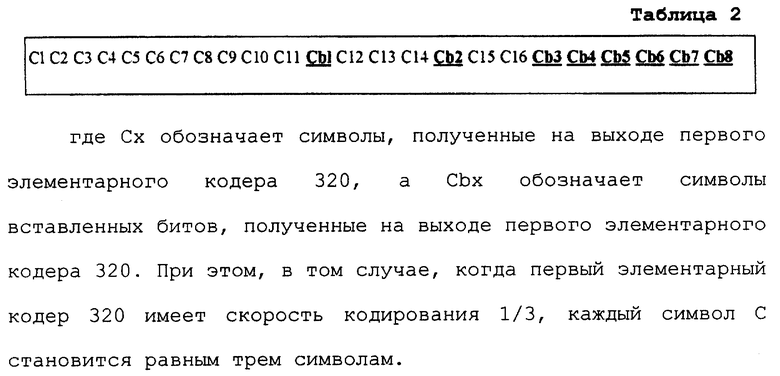

Первый элементарный кодер 320 осуществляет кодирование битов данных из таблицы 1, полученных на выходе блока вставки 310 битов. Кодированные биты данных, полученные на выходе первого элементарного кодера 320, показаны в таблице 2.

Тем временем, перемежитель 330 производит перемежение битов данных с выхода блока вставки 310 битов, а второй элементарный кодер 340 осуществляет кодирование перемеженных битов данных с выхода перемежителя 330. Кодированные биты данных, полученные на выходе второго элементарного кодера 340, показаны в таблице 3.

Хотя в действительности последовательность битов данных была изменена путем перемежения, для удобства объяснения последовательность в таблице 3 оставлена без изменений.

Затем мультиплексор 350 под управлением не изображенного на чертеже контроллера осуществляет мультиплексирование выходных сигналов от блока вставки 310 битов, от первого элементарного кодера 320 и от второго элементарного кодера 340. В таблице 4 показаны биты данных со вставленными определенными битами и выходные сигналы первого и второго элементарных кодеров 320 и 340. Мультиплексор 350 может осуществлять как покадровое, что показано в таблице 4, так и посимвольное мультиплексирование входных символов с последовательностью символов данных, первым символом четности и вторым символом четности.

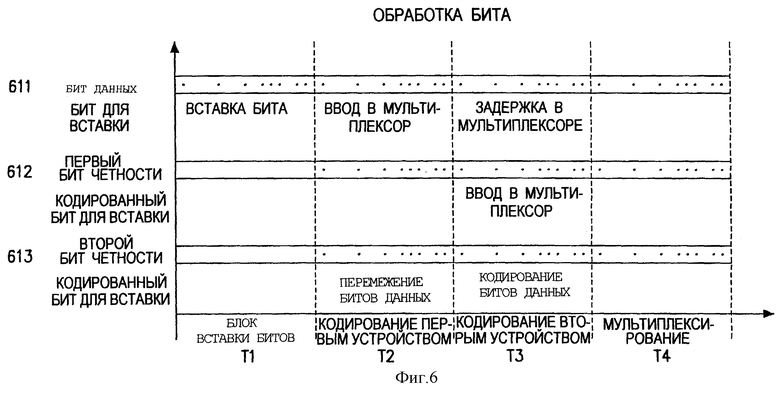

Фиг. 6 представляет собой временную диаграмму работы устройства турбокодирования из фиг. 3 в соответствии с первым вариантом осуществления настоящего изобретения. Со ссылкой на фиг.6, для осуществления генерации битов Ik данных из таблицы 1 блок 310 вставки битов в течение промежутка времени Т1 вставляет в кадр нулевые биты в заданные места расположения битов (см. 611). В течение промежутка времени Т2 биты Ik данных со вставленными нулевыми битами одновременно подают в мультиплексор 350, в первый элементарный кодер 320 и в перемежитель 330. Затем, в течение промежутка времени Т2 первый элементарный кодер 320 выполняет кодирование битов Ik данных со вставленными нулевыми битами, осуществляя генерацию первых кодированных битов Ck данных, которые являются первыми битами четности (см. 612), и в течение того же промежутка времени Т2 перемежитель 330 осуществляет перемежение битов Ik данных со вставленными нулевыми битами согласно заданному правилу (см. 613).

После этого, в течение промежутка времени Т3 мультиплексор 350 осуществляет задержку битов Ik данных с выхода блока 310 вставки битов на один период кадра, первый элементарный кодер 320 осуществляет ввод первых кодированных битов Ck данных в мультиплексор 350, а второй элементарный кодер 340 осуществляет кодирование перемеженных битов Ik данных с выхода перемежителя 330, осуществляя генерацию вторых кодированных битов Dk данных, которые представляют собой вторые биты четности. После окончания операции генерации вторых битов Dk четности вторым элементарным кодером 340 мультиплексор 350 в течение промежутка времени Т4 выполняет мультиплексирование битов Ik данных, первых битов Сk четности и вторых битов Dk четности.

Несмотря на то, что на фиг.6 показан пример параллельной обработки битов Ik данных, первые биты Ck четности и вторые биты Dk четности, также может быть осуществлен и последовательный вывод выходных сигналов блока 310 вставки битов, первого элементарного кодера 320 и второго элементарного кодера 340 в порядке выполнения генерации битов.

Из вышеприведенных описаний понятно, что в рекурсивном системном устройстве турбокодирования в соответствии с первым вариантом осуществления соответствующие элементарные кодеры не осуществляют генерацию хвостовых битов завершения, а вместо этого производят вставку некоторого количества определенных битов (то есть, нулевых битов) в те места, в которых обнаружена более высокая вероятность появления ошибки.

Второй вариант осуществления

Устройство канального кодирования согласно второму варианту осуществления настоящего изобретения осуществляет вставку определенных битов в те места расположения битов, в которых существует более высокая вероятность возникновения ошибки. Отличие второго варианта осуществления от первого варианта осуществления может заключаться в том, что количество вставленных битов устанавливают таким, чтобы превысить размер (или длину) кадра. В этом примере варианта осуществления считают, что каждый кадр включает в себя 16 битов Ik входных данных и 12 вставленных битов. Поскольку генерацию битов Ik выходных данных, битов Ck и Dk четности, которые должны быть равны 24-м битам и 28-ми битам, осуществляют совместно, то в местах вставки битов производят извлечение избыточных битов Ck и Dk четности из битов Ik данных путем "прошивки".

Фиг. 7 представляет собой схему, на которой показано устройство канального кодирования согласно второму варианту осуществления настоящего изобретения. Блок 710 вставки битов включает в себя генератор битов для генерации определенных битов путем обработки битов входных данных и осуществляет генерацию битов данных, превышающих размер кадра, посредством вставки определенных битов, генерация которых произведена генератором битов, в заданные места расположения битов. Для генерации первых битов Сk четности первый элементарный кодер 720 производит кодирование битов данных, полученных на выходе блока 710 вставки битов. Перемежитель 730 выполняет перемежение битов данных кадра, полученных на выходе блока 710 вставки битов, согласно заданному правилу, для изменения порядка расположения (или последовательности) битов данных. В примере варианта осуществления в качестве перемежителя 730 используют диагональный перемежитель.

Второй элементарный кодер 740 производит кодирование перемеженных битов данных кадра, полученных на выходе перемежителя 730, осуществляя генерацию вторых битов Dk четности. В качестве первого и второго элементарных кодеров 720 и 740 может быть использован рекурсивный системный сверточный кодер. Для генерации кадра данных заданной длины мультиплексор 750, управляемый не изображенным на чертеже контроллером, осуществляет мультиплексирование выходных сигналов блока 710 вставки битов, первого элементарного кодера 720 и второго элементарного кодера 740. При этом на выходе блока 710 вставки битов получают биты Ik данных, на выходе первого элементарного кодера 720 получают первые биты P1k четности, а на выходе второго элементарного кодера 740 получают вторые биты P2k четности.

При работе, после приема 16-ти битов Ik входных данных функционирование блока 710 вставки битов осуществляется таким же образом, как и блока 310 вставки битов из первого варианта осуществления. Блок 710 вставки битов имеет схему, подобную схеме из фиг.4, за исключением того, что он состоит из 12-ти устройств задержки. Поэтому блок 710 вставки битов осуществляет вставку в кадр 12-ти нулевых битов в 12-ти местах расположения битов, имеющих более высокую вероятность ошибки, посредством управления внутренними коммутаторами, находящимися под управлением контроллера. Следовательно, в этом варианте осуществления на выходе блока 710 вставки битов получают эти 28 битов Ik данных (то есть, 16 битов данных и 12 нулевых битов), которые одновременно подают в мультиплексор 750, в первый элементарный кодер 720 и в перемежитель 730. Затем перемеженные биты Ik данных с выхода перемежителя 730 подают во второй элементарный кодер 740. Здесь первый и второй элементарные кодеры 720 и 740 имеют такую же схему, как и на фиг.5, которая не производит генерацию хвостовых битов для осуществления завершения.

Затем первый элементарный кодер 720 выполняет кодирование этих 28-ми битов Ik данных, полученных на выходе блока 710 вставки битов, со вставленными в них 12-ю нулевыми битами и осуществляет вывод 28-ми первых битов Ck четности в мультиплексор 750. Перемежитель 730 осуществляет перемежение этих 28-ми битов Ik данных, полученных на выходе блока 710 вставки битов, а второй элементарный кодер 740 выполняет кодирование перемеженных битов данных тем же способом, что и первый элементарный кодер 720, осуществляя генерацию 28-ми вторых битов четности Dk, которые подают в мультиплексор 750. Мультиплексор 750 производит "прошивку" битов Ik данных, вставляя четыре первых бита Ck четности и четыре вторых бита Dk четности в местах "прошивки", а затем осуществляет вывод остальных 24-х первых битов Ck четности и остальных 24-х вторых битов Dk четности.

Со ссылкой на фиг.8 мультиплексор 750 сначала получает эти 28 битов Ik данных с выхода блока 710 вставки битов. Затем коммутатор 812 в мультиплексоре 750 соединяют с устройством 822 задержки до тех пор, пока из блока 710 вставки битов не будут получены первые 24 бита данных из этих 28-ми битов Ik данных. Устройство 822 задержки осуществляет задержку первых 24-х полученных битов Ik данных. После этого коммутатор 812 соединяют с устройством 824 задержки до тех пор, пока их блоки 710 вставки битов не будут получены остальные 4 бита данных из этих 28-ми битов Ik данных. Устройство 824 задержки осуществляет задержку остальных 4-х битов данных.

Подобным же образом мультиплексор 750 получает 28 первых битов Сk четности с выхода первого элементарного кодера 720. Затем коммутатор 814 в мультиплексоре 750 соединяют с устройством 826 задержки до тех пор, пока из первого элементарного кодера 720 не будут получены первые 24 бита данных из 28-ми первых битов Сk четности, а устройство 826 задержки осуществляет задержку полученных первых битов Ck четности. После этого коммутатор 814 соединяют с устройством 828 задержки до тех пор, пока из первого элементарного кодера 720 не будут получены остальные 4 первых бита четности из 28 первых битов четности Ck, а устройство 828 задержки осуществляет задержку полученных остальных 4-х первых битов четности.

После этого мультиплексор 750 получает 28 вторых битов Dk четности с выхода второго элементарного кодера 740. Затем коммутатор 816 в мультиплексоре 750 соединяют с устройством 830 задержки до тех пор, пока из второго элементарного кодера 740 не будут получены первые 24 бита данных из 28-ми вторых битов Dk четности, а устройство 830 задержки осуществляет задержку полученных вторых битов Dk четности. После этого коммутатор 816 соединяют с устройством 832 задержки до тех пор, пока из второго элементарного кодера 740 не будут получены 4 вторые бита четности из 28-ми вторых битов Dk четности, а устройство 832 задержки осуществляет задержку полученных остальных 4-х вторых битов четности.

Как описано выше, мультиплексор 750 осуществляет последовательный прием этих 28-ми битов Ik данных, 28-ми первых битов Ck четности и 28-ми вторых битов Dk четности и раздельное запоминание первых 24-х битов и остальных 4-х битов из соответствующих битов в соответствующих устройствах задержки. Управление коммутаторами 812-816 осуществляет не изображенный на чертеже контроллер. Затем в каждом из устройств 822-832 задержки, состоящих из каскадных запоминающих элементов, осуществляют запоминание входных битов до тех пор, пока не будет закончен соответствующий процесс задержки.

После окончания процесса задержки коммутатор 844 соединяют с коммутатором 842, а коммутатор 842 соединяют с устройством 822 задержки. Следовательно, вывод выходного сигнала устройства 822 задержки производят через коммутаторы 842 и 844. После вывода одного бита данных, хранящегося в устройстве 822 задержки, коммутатор 842 соединяют с устройством 824 задержки при сохранении соединения с коммутатором 844. Затем производят вывод одного из оставшихся битов данных, хранящихся в устройстве 824 задержки, через коммутаторы 842 и 844. То есть, осуществляют "прошивку" бита данных, хранящегося в устройстве 822 задержки, а затем производят вывод бита данных, хранящегося в устройстве 824 задержки. После этого коммутатор 842 соединяют с устройством 822 задержки при постоянном сохранении соединения с коммутатором 844. Путем четырехкратного повторения вышеуказанного процесса осуществляют "прошивку" битов данных, хранящихся в устройстве 822 задержки, а затем производят вставку в места "прошивки" оставшихся четырех битов данных, хранящихся в устройстве задержки 824.

Затем коммутатор 842 соединяют с устройством 822 задержки, сохраняя соединение с коммутатором 844. Затем осуществляют вывод выходного сигнала из устройства 822 задержки через коммутаторы 842 и 844. После вывода одного бита данных, хранящегося в устройстве 822 задержки, коммутатор 842 соединяют с устройством 828 задержки, сохраняя соединение с коммутатором 844. Затем осуществляют вывод одного из оставшихся четырех первых битов четности, хранящихся в устройстве задержки 828, через коммутаторы 842 и 844. После этого коммутатор 842 снова соединяют с устройством 822 задержки при постоянном сохранении соединения с коммутатором 844. Путем четырехкратного повторения вышеуказанного процесса осуществляют "прошивку" битов данных, хранящихся в устройстве 822 задержки, а затем производят вставку в места "прошивки" оставшихся четырех первых битов четности, хранящихся в устройстве 828 задержки.

Подобным же образом осуществляют поочередный вывод битов данных и остальных четырех первых битов четности. Затем коммутатор 842 соединяют с устройством 822 задержки, сохраняя соединение с коммутатором 844. Затем осуществляют вывод выходного сигнала из устройства задержки 822 через коммутаторы 842 и 844. После вывода одного бита данных, хранящегося в устройстве 822 задержки коммутатор 842 соединяют с устройством 832 задержки, сохраняя соединение с коммутатором 844. Затем осуществляют вывод одного из оставшихся четырех вторых битов четности, хранящихся в устройстве задержки 832, через коммутаторы 842 и 844. После этого коммутатор 842 снова соединяют с устройством 822 задержки, постоянно сохраняя соединение с коммутатором 844. Путем четырехкратного повторения вышеуказанного процесса осуществляют "прошивку" битов данных, хранящихся в устройстве 822 задержки, а затем производят вставку в места "прошивки" оставшихся четырех вторых битов четности, хранящихся в устройстве 832 задержки.

Посредством вышеописанной процедуры осуществляют "прошивку" 24-х битов данных, хранящихся в устройстве 822 задержки, а затем производят вставку в места "прошивки" оставшихся 4-х битов данных, хранящихся в устройстве 824 задержки, оставшихся 4-х первых битов четности, хранящихся в устройстве 828 задержки, и оставшихся 4-х вторых битов четности, хранящихся в устройстве 832 задержки. Следовательно, мультиплексор 750 производит "прошивку" битов Ik; данных, полученных на выходе блока 710 вставки битов, и вставку этих 8-ми битов четности в "прошитые" места вставки, осуществляя таким образом вывод 24-х битов данных.

После окончания вышеописанного процесса коммутатор 844 соединяют с устройством 826 задержки. Затем осуществляют вывод 24-х первых битов Сk четности, хранящихся в устройстве 826 задержки. После этого коммутатор 844 соединяют с устройством задержки 830 для вывода 24-х вторых битов Dk четности, хранящихся в устройстве 830 задержки.

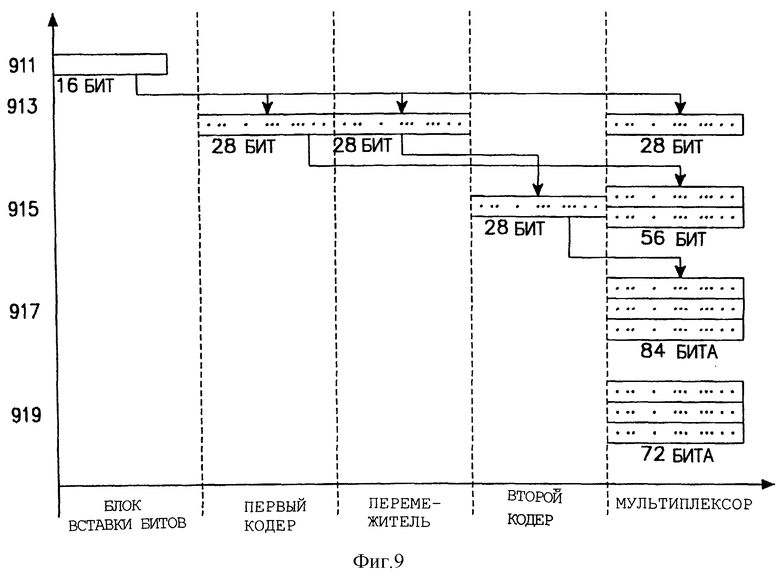

Со ссылкой на фиг.9 в устройстве кодирования из фиг.7, соответствующем второму варианту осуществления, для генерации этих 28-ми битов Ik данных блок 710 вставки битов производит вставку 12-ти битов в эти 16 битов входных данных. Первый и второй элементарные кодеры 720 и 740 осуществляют генерацию, соответственно, 28-ми первых битов Ck четности и 28-ми вторых битов Dk четности. Мультиплексор 750 выполняет "прошивку" этих 28-ми битов Ik данных в 12-ти местах вставки, а затем производит вставку в них оставшихся 4-х битов данных, оставшихся 4-х первых битов четности и оставшихся 4-х вторых битов четности. После этого мультиплексор 750 производит последовательный вывод битов Ik данных, первых битов Ck четности и вторых битов Dk четности.

В процессе декодирования осуществляют демультиплексирование значений выходного сигнала мультиплексора 750 с получением части, соответствующей битам данных, части, соответствующей первым битам четности, и части, соответствующей вторым битам четности, причем часть, соответствующая битам данных, является "прошитой" значением "-5" в месте вставки бита. Декодирование обработанных подобным образом битов данных осуществляют посредством существующего декодирующего устройства. (См. публикацию Клода Берру, Алена Главье и Пунья Титмайшима "Кодирование и декодирование с исправлением ошибок вблизи предела пропускной способности канала: турбокоды (1)").

Третий вариант осуществления

Устройство кодирования согласно третьему варианту осуществления настоящего изобретения осуществляет вставку битов, имеющих определенную логику битов данных, в те места расположения битов, в которых существует более высокая

вероятность возникновения ошибки, в котором элементарные кодеры осуществляют кодирование определенных вставленных побитно битов данных и генерацию хвостовых битов, которые добавляют к кодированным битам данных. То есть устройство кодирования согласно третьему варианту осуществления исполняет функцию завершения посредством вставки битов и добавления хвостовых битов.

Фиг. 10 представляет собой схему, на которой изображено устройство кодирования согласно третьему варианту осуществления настоящего изобретения. Со ссылкой на фиг.10 блок 1010 вставки битов получает 16 входных битов и устроен точно так же, как и блок 310 вставки битов согласно первому варианту осуществления. Блок 1010 вставки битов, управляемый не изображенным на чертеже контроллером, производит вставку в кадр 8-ми нулевых битов в те 8 мест расположения битов данных, в которых существует более высокая вероятность возникновения ошибки. Следовательно, в этом примере варианта осуществления блок 1010 вставки битов осуществляет вывод 24-х битов Ik данных, которые подают одновременно в мультиплексор 1050, в первый элементарный кодер 1020 и в перемежитель 1030.

Затем перемеженные биты Ik данных с выхода перемежителя 1030 подают во второй элементарный кодер 1040. Первый элементарный кодер 1020 представляет собой рекурсивный системный элементарный кодер, изображенный на фиг.11, который устроен таким образом, что осуществляет генерацию хвостовых битов, которые добавляют к кодированным битам данных. При этом первый элементарный кодер 1020 устроен таким образом, что, как и показанный на фиг.5 кодер из первого варианта осуществления, не осуществляет генерацию хвостовых битов для обозначения завершения.

Описание функционирования первого элементарного кодера 1020 будет приведено со ссылкой на фиг.11. Для осуществления кодирования коммутатор 1111 соединяет входной узел с логическим элементом 1131 "исключающее ИЛИ", коммутатор 1113 находится в состоянии ВЫКЛ, а коммутатор 1115 соединяют с логическим элементом 1135 "исключающее ИЛИ". Затем эти 24 бита Ik данных последовательно подают в устройства задержки 1121-1127 через коммутатор 1111 и логический элемент 1131 "исключающее ИЛИ", а логический элемент 1135 "исключающее ИЛИ" осуществляет вывод кодированных битов данных. После того как таким способом произведено кодирование всех битов Ik данных посредством устройств 1121-1127 задержки и логического элемента 1135 "исключающее ИЛИ", то коммутатор 1111 соединяют с логическими элементами 1133 и 1131 "исключающее ИЛИ", коммутатор 1113 устанавливают в положение ВКЛ, а коммутатор 1115 соединяют с коммутатором 1113. Затем осуществляют генерацию нулевых битов посредством операции "исключающее ИЛИ" с обратной связью по выходному сигналу, их запоминания в устройствах 1121-1127 задержки и вывода через коммутатор 1115. При этом запомненные в устройствах 1121-1127 задержки нулевые значения становятся хвостовыми битами и их вывод производят через коммутатор 1115. Количество сгенерированных хвостовых битов соответствует количеству устройств задержки в элементарном кодере 1020. На фиг.11 элементарный кодер 1020 осуществляет генерацию 4-х хвостовых битов в каждом кадре, а также генерацию кодированных битов для соответствующих хвостовых битов.

Таким образом, первый элементарный кодер 1020 осуществляет генерацию 24-х первых битов Ck четности и после обработки последнего бита данных (то есть, 24-го бита данных) соединяет коммутатор 1111 с логическим элементом 1133 "исключающее ИЛИ", коммутатор 1113 с коммутатором 1111 и коммутатор 1115 с коммутатором 1113; для генерации 4-х хвостовых битов этот процесс повторяют четыре раза. Посредством этой процедуры осуществляют вывод 28-ми первых битов Ck четности и 4-х хвостовых битов и их подачу в мультиплексор 1050.

Кроме того, перемежитель 1030 производит перемежение этих 24-х битов Ik данных с выхода блока 1010 вставки битов и подает перемеженные биты данных во второй элементарный кодер 1040. Затем второй элементарный кодер 1040 выполняет кодирование перемеженных битов данных тем же самым способом, что и первый элементарный кодер 1020, осуществляя генерацию 24-х вторых битов Dk четности, которые подают в мультиплексор 1050.

Кодирование перемеженных битов данных одного кадра, полученных с выхода перемежителя 1030, выполняют посредством второго элементарного кодера 1040, который устроен так же, как и показанный на фиг.5. Второй элементарный кодер 1040 представляет собой рекурсивный системный сверточный кодер, который показан на фиг.5. Кроме того, второй элементарный кодер 1040 устроен таким образом, что не осуществляет генерацию хвостовых битов.

Затем мультиплексор 1050 осуществляет "прошивку" битов Ik данных и вставляет 4 их первых битов Dk четности в места "прошивки" и производит селективный вывод остальных 24-х первых битов Ck четности) и 24-x вторых битов Dk четности.

Фиг. 12 представляет собой схему, на которой показан мультиплексор 1050. Со ссылкой на фиг.12 мультиплексор 1050 сначала получает эти 24 бита Ik данных с выхода блока 1010 вставки битов. Затем в устройстве 1222 задержки в мультиплексоре 1050 запоминают эти полученные 24 бита Ik данных.

После этого мультиплексор 1050 принимает 28 первых битов Ck четности с выхода первого элементарного кодера 1020. Затем коммутатор 1212 в мультиплексоре 1050 соединяют с устройством 1224 задержки до тех пор, пока из первого элементарного кодера 1020 не будут получены первые 24 бита из первых битов Ck четности, а в устройстве 1224 задержки запоминают принятые первые биты Ck четности. Затем коммутатор 1212 соединяют с устройством 1226 задержки до тех пор, пока из первого элементарного кодера 1020 не будут получены оставшиеся 8 битов из 32-х первых битов Ck четности, а в устройстве 1226 задержки напоминают оставшиеся 8 битов из первых битов Ck четности.

Потом мультиплексор 1050 осуществляет прием 24-х вторых битов Dk четности с выхода второго элементарного кодера 1040. А затем в устройстве 1228 задержки в мультиплексоре 1050 запоминают принятые 24 вторых бита Dk четности.

Эти полученные путем последовательной генерации 24 бита Ik данных, 28 первых битов Ck четности и 24 вторых бита Dk четности подают в мультиплексор 1050. Затем мультиплексор 1050 осуществляет запоминание в порядке приема в соответствующих устройствах задержки последовательно принятых битов Ik данных, первых битов Сk четности и вторых битов Dk четности, причем запоминание первых 24-х битов и остальных 4-х битов из 28-ми первых битов Сk четности производят раздельно в соответствующих устройствах задержки. Каждое из устройств 1222-1228 задержки состоит из каскадных запоминающих элементов и осуществляет запоминание соответствующих подаваемых на вход битов до тех пор, пока не будет закончен вышеуказанный процесс задержки.

После выполнения вышеуказанного процесса задержки коммутатор 1236 соединяют с коммутатором 1234, а коммутатор 1234 соединяют с устройством 1222 задержки. Таким образом, вывод выходного сигнала устройства 1222 задержки производят через коммутаторы 1234 и 1236. После вывода одного бита данных, хранящегося в устройстве 1222 задержки, коммутатор 1234 соединяют с устройством 1226 задержки, сохраняя соединение с коммутатором 1236. Затем производят вывод одного из оставшихся первых битов четности, хранящихся в устройстве 1226 задержки, через коммутаторы 1234 и 1236. То есть, осуществляют "прошивку" бита данных, хранящегося в устройстве 1222 задержки, а затем производят вставку первого бита четности, хранящегося в устройстве 1226 задержки, в место "прошивки". После этого коммутатор 1234 снова соединяют с устройством 1222 задержки, сохраняя соединение с коммутатором 1236. Для осуществления "прошивки" битов данных, хранящихся в 1222, и вставки в места "прошивки" оставшихся 8-ми первых битов четности, хранящихся в устройстве 1226 задержки, вышеописанную операцию повторяют 8 раз. В результате, осуществляют "прошивку" этих 24-х битов Ik данных для вставки в места "прошивки" (то есть, в места вставки бита) 8-ми первых битов четности и таким образом производят вывод 24-х битов.

После этого коммутатор 1236 соединяют с выходом устройства 1224 задержки. Затем производят вывод 24-х первых битов Ck четности, хранящихся в устройстве 1224 задержки, через коммутатор 1236. Затем коммутатор 1236 подключают к устройству 1228 задержки для вывода 24-х вторых битов Dk четности, хранящихся в устройстве 1228 задержки.

Со ссылкой на фиг. 13 для генерации этих 24-х битов Ik данных блок вставки битов 1010 из устройства кодирования, изображенного на фиг.10, в соответствии с третьим вариантом осуществления производит вставку 8-ми битов в 16 битов входных данных. В качестве элементарного кодера используют рекурсивный системный элементарный кодер, который выполняет генерацию хвостовых битов. В этом варианте элементарный кодер осуществляет генерацию всего 32-х битов данных, состоящих из 24-х кодированных битов данных, 4-х хвостовых битов и кодированных данных 4-х хвостовых битов. При выводе кодированных битов данных осуществляют "прошивку" битов Ik входных данных для вставки остальных 8-ми первых битов четности в местах "прошивки" бита.

В процессе декодирования осуществляют демультиплексирование значений выходного сигнала мультиплексора с получением части, соответствующей битам данных, части, соответствующей первым битам четности и части, соответствующей вторым битам четности, причем часть, соответствующая битам данных является "прошитой" значением "-5" в месте вставки бита. Декодирование обработанных подобным образом битов данных осуществляют посредством существующего декодирующего устройства. (См. публикацию Клода Берру, Алена Главье и Пунья Титмайшима "Кодирование и декодирование с исправлением ошибок вблизи предела пропускной способности канала: турбокоды (1)").

Несмотря на то, что было сделано допущение, что в этом варианте осуществления в качестве битов для вставки используют нулевые биты, также могут быть использованы кодированные биты или биты данных, которые заданы посредством приемника.

Четвертый вариант осуществления

Как описано с первого по третий вариант осуществления, вставку бита выполняют при наличии предварительного взаимодействия между передатчиком и приемником. То есть, передатчик производит вставку определенных битов в данные кадра в заданные места вставки бита до канального кодирования, а приемник выполняет декодирование принятых кодированных символов канала тогда, когда места вставки битов известны. Поэтому производительность приемника можно повысить путем использования в процессе декодирования информации о местах вставки бита. В этом варианте осуществления для повышения производительности при канальном декодировании в места вставки битов производят вставку символов, имеющих определенные значения. Затем, для осуществления канального декодирования, после вставки символов в места вставки битов при каждом итерационном процессе декодирования устанавливают определенное значение символов, расположенных в местах вставки бита. Декодирование символов с выхода демультиплексора, выполняющего операцию, обратную той, которую осуществляют мультиплексоры, производят посредством описанного ниже процесса декодирования. При этом демультиплексор выполняет демультиплексирование принятых кодированных символов канала, осуществляя генерацию символа Хk данных, первого символа Y1k четности и второго символа Y2k четности.

На фиг. 14 показано декодирующее устройство для декодирования кодированных символов канала, которые переданы из устройства кодирования, соответствующего вариантам осуществления с первого по третий. Для упрощения на фиг.14 не изображен демультиплексор для демультиплексирования полученных кодированных символов канала.

Со ссылкой на фиг. 14, блок 1411 вставки символов осуществляет прием демультиплексированных символов Хk данных. Для символа, не расположенного в месте вставки бита, блок 1411 вставки символов подает принятый символ в декодер 1422 с гибким выбором без его изменения; в противном же случае, для символа, расположенного в месте вставки бита, блок 1411 вставки символа производит выбор символа, имеющего определенное значение, генерация которого осуществлена внутренним генератором символов, и подает выбранный символ в декодер 1422 с гибким выбором. То есть блок 1411 вставки символа производит вставку символа, имеющего определенное значение и полученного посредством внутренней генерации, в то место, куда вставлен определенный бит, как показано в таблице 4, и осуществляет вывод принятых символов данных, находящихся в исходных местах расположения символов данных, без изменений. При этом, поскольку места вставки определенного бита заранее распределены между передатчиком и приемником, приемнику заранее известны места вставки определенного бита для символа данных. Инициализатор 1415 символов получает символы, которые возвращают обратно из обращенного перемежителя 1433, для осуществления итерационного декодирования. Инициализатор 1415 символов устанавливает определенное значение символа, расположенного в месте вставки бита, а выход остальных символов осуществляет без изменений. Коммутатор 1442 производит выбор одного из символов с выхода либо блока 1411 вставки символов, либо инициализатора 1415 символов, что зависит от положения коммутатора. В частности, после получения символа Хk данных коммутатор 1442 производит выбор выходного сигнала блока 1411 вставки символов, а в противном случае производит выбор выходного сигнала инициализатора 1415 символов. Декодер 1422 с гибким выбором принимает символы с выхода коммутатора 1442 и первый символ Y1k четности с выхода демультиплексора, и производит декодирование принятых символов с гибким выбором. При этом значение выходного сигнала декодера 1422 с гибким выбором используют в качестве дополнительной информации.

Перемежитель 1431 осуществляет перемежение выходного сигнала декодера 1422 с гибким выбором. Инициализатор 1413 символов, принимающий перемеженные декодированные данные от перемежителя 1413, устанавливает определенное значение (например, -5) символа, расположенного в месте вставки бита, а в противном случае осуществляет вывод символов, не расположенных в местах вставки бита, без их изменений. Декодер 1424 с гибким выбором производит декодирование выходного сигнала инициализатора 1413 символов и второго бита Y2k четности.

Коммутатор 1444 направляет декодированные данные с выхода декодера 1424 с гибким выбором либо к обращенным перемежителям 1433, либо к элементу 1437 с жестким выбором. Обращенный перемежитель 1433 осуществляет перемежение декодированных данных с выхода декодера 1424 с гибким выбором и подает перемеженные данные обратно в инициализатор 1415 символов. Элемент 1437 с жестким выбором осуществляет жесткий выбор декодированных данных, полученных с выхода коммутатора 1444. Обращенный перемежитель 1435 осуществляет обращенное перемежение выходного сигнала элемента 1437 с жестким выбором.

Каждый из декодеров 1422 и 1424 с гибким выбором может состоять из элементарного кодера, который подробно раскрыт в публикации Клода Берру, Алена Главье и Пунья Титмайшима "Кодирование и декодирование с исправлением ошибок вблизи предела пропускной способности канала: турбокоды (1)") и в патенте US 5446747.

Блок 1411 вставки символов может иметь такую же структуру, как и блок 310 вставки битов из фиг.4.

На фиг.15 показаны инициализаторы 1413 и 1415 символов, в которых генератор 1502 символов осуществляет генерацию символа, имеющего определенное значение символа, для увеличения достоверности вставленного бита. В этом варианте осуществления полагают, что определенное значение символа равно -5. В месте вставки определенного бита коммутатор 1504 переключают так, чтобы он осуществлял соединение с выходом генератора 1502 символов и выбор входных символов в других местах расположения символов. Затем, после приема данных первого символа коммутатор 1442 соединяет блок вставки 1411 символов с декодером 1422 с гибким выбором, и в течение итерационного декодирования обеспечивает соединение инициализатора 1415 символов с декодером 1422 с гибким выбором. Кроме того, в течение итерационного декодирования коммутатор 1444 соединяет декодер 1424 с гибким выбором с обращенным перемежителем 1433, а после окончания итерационного декодирования соединяет декодер 1424 с гибким выбором с решающим элементом 1437 с жестким выбором.

В рабочем режиме при вводе кодированных символов Xk, Y1k и Y2k канала, каждый из которых имеет значение +1 или -1, в устройство канального декодирования блок вставки 1411 символов, принимающий символ Xk данных, осуществляет вставку определенного значения (например, -5) в то место вставки бита, "прошивка" которого была произведена при канальном кодировании. В этом варианте осуществления считают, что определенное значение, имеющее отклонение от -1, равно -5, а символ, имеющий определенное значение, вставлен в место вставки. Здесь коммутатор 1442 соединяет блок вставки 1411 символов с декодером 1422 с гибким выбором. То есть, в течение времени ввода символа данных коммутатор 1422 соединяет выход блока вставки символов 1411 с декодером 1422 с гибким выбором, а в течение времени итерационного декодирования - соединяет выход инициализатора 1415 символов с декодером 1422 с гибким выбором. Затем блок вставки символов 1411 анализирует принятые символы данных и осуществляет вывод полученного посредством внутренней генерации символа, имеющего определенное значение (например, -5) в месте вставки определенного бита, и вывод символа Xk данных в остальных местах, в которых определенные биты не вставлены. Декодер 1422 с гибким выбором осуществляет декодирование символа Xk данных и первого символа Y1k четности, вычисляет отношение вероятности того, что бит данных для символов до кодирования является нулевым, к вероятности того, что бит данных является равным 1, и, исходя из вычисленного значения, осуществляет вывод скорректированного значения символа Xk данных в виде декодированного символа.

Перемежитель 1431 производит перемежение символов, полученных с выхода декодера 1422 с гибким выбором, а затем их подают в инициализатор 1413 символов. Когда декодированные посредством декодера 1422 с гибким выбором символы, расположенные в месте вставки, имеют значение (например, -3,1), отклоняющееся от -5 к -1, то инициализатор 1413 символов восстанавливает значение, равное -5.

Со ссылкой на фиг.15, после приема символов коммутатор 1504 инициализатора 1413 символов соединяет выход перемежителя 1431 с декодером 1424 с гибким выбором для вывода входных символов без изменения. Тем временем, в месте "прошивки" коммутатор 1504 переключают на генератор 1502 символов. В этот момент генератор 1502 символов осуществляет генерацию значения -5, которое выводят через коммутатор 1504. После этого коммутатор 1504 в инициализаторе символа 1413 снова соединяет перемежитель 1431 с декодером 1424 с гибким выбором для вывода входных символов без изменения. После того как значение символов, расположенных в местах вставки, посредством инициализатора 1413 символов установлено равным 5, выходные символы вместе со вторым битом Y2k четности подвергают декодированию с гибким выбором посредством декодера 1424 с гибким выбором.

Декодер 1424 с гибким выбором функционирует так же, как и декодер 1422 с гибким выбором, за исключением иной последовательности входных символов. Здесь коммутатор 1444 соединяет декодер 1424 с гибким выбором с обращенным перемежителем 1433, осуществляя вывод символов, декодирование которых с выхода обращенного перемежителя 1433 осуществляют посредством декодера 1424 с гибким выбором. Затем обращенный перемежитель 1433 производит обращенное перемежение входных декодированных данных и возвращает данные с обращенным перемежением обратно в инициализатор 1415 символов, который снова устанавливает исходное значение символов, расположенных в местах вставки, равное -5, для символов, полученных с выхода обращенного перемежителя 1433. Инициализатор 1415 символов, который функционирует так же, как и инициализатор 1413 символов, за исключением иной последовательности подаваемых обратно символов, устанавливает исходное значение символов в местах вставки. Для повторения вышеописанных операций коммутатор 1422 в этот момент соединяет инициализатор 1415 символов с декодером 1422 с гибким выбором, осуществляя ввод инициализированных символов в декодер 1422 с гибким выбором.

Когда после повторения вышеуказанных операций заданное количество раз из декодера 1424 с гибким выбором осуществлен вывод декодированного символа, коммутатор 1444 соединяет декодер 1424 с гибким выбором с элементом 1437 с жестким выбором. Элемент 1437 с жестким выбором выбирает значения декодированных символов, равные 1 и 0, а обращенный перемежитель 1435 осуществляет их обращенное перемежение и вывод в качестве конечных декодированных битов.

На фиг.16 показано декодирующее устройство согласно другому варианту осуществления настоящего изобретения. Понятно, что декодирующее устройство устроено так же, как и декодирующее устройство из фиг.14, за исключением иной последовательности расположения перемежителя 1431 и инициализатора 1413 символов.

Несмотря на то, что изобретение было продемонстрировано и описано со ссылкой на конкретный предпочтительный вариант его осуществления, для специалистов в данной области техники понятно, что могут быть произведены различные изменения, касающиеся формы и мелких подробностей, без отступления от сущности и объема изобретения, определяемых приложенной формулой изобретения.

Устройство канального декодирования для приемника, осуществляющего прием символов, кодирование которых произведено посредством вставки в заданное место данных кадра, по меньшей мере, одного определенного бита. В устройстве канального декодирования блок вставки символов, принимающий символы, производят вставку символа, имеющего определенное значение, в заданное место вставки определенного бита и осуществляет вывод тех принятых символов, которые расположены в других местах. Декодер выполняет декодирование символов, полученных на выходе блока вставки символов. 5 с. и 7 з.п.ф-лы, 16 ил., 4 табл.

| US 5446747 A, 29.08.1995 | |||

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| ТУРБИНА С МНОГОКРАТНЫМ ПЕРЕГРЕВОМ РАБОЧЕГО ТЕЛА | 0 |

|

SU310057A1 |

| US 4151373 A, 24.04.1979. | |||

Авторы

Даты

2002-10-10—Публикация

1999-08-06—Подача