Изобретение относится, в общем, к устройству и способу для кодирования данных в блоке кадра, а более конкретно - к устройству и способу канального кодирования.

Уровень техники

В системах связи для обеспечения обработки речевых и видеосигналов, сигналов символов и изображений данные обычно передаются в последовательных кадрах. Кроме того, в системе связи при таких данных кадра канальный кодер, предназначенный для исправления ошибок, должен также кодировать данные в блоке кадра. В этом случае канальный кодер производит вставку оконечного бита в конце кадра данных для сброса сверточного кодера в известное состояние и для предоставления возможности декодеру эффективно декодировать кадры с использованием этой информации. В системе IS-95 обычно используется нерекурсивный системный сверточный кодер, в котором последовательность нулевых (0) бит передается в конце каждого кадра с помощью количественного эквивалента числу ответвлений последовательности данных, последовательно задержанных во времени, для осуществления завершения кадра, так как входные биты подаются обратно с задержками.

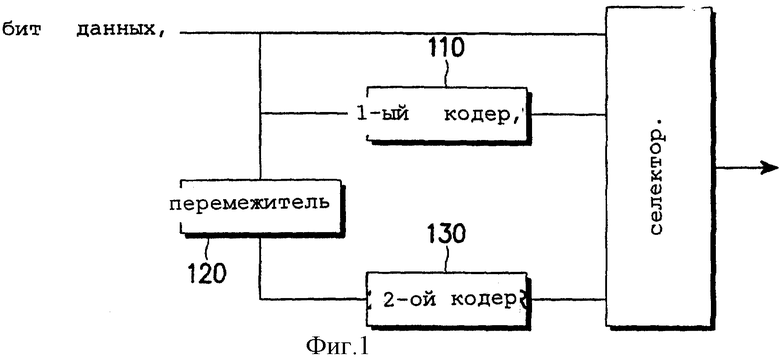

На фиг. 1 изображена блок-схема турбокодера, который является типичным рекурсивным системным кодером. Турбокодер кодирует N-битовый входной кадр в символы контроля четности с использованием двух простых составных кодеров и они могут иметь параллельную или последовательную структуру. Кроме того, турбокодер использует рекурсивные системные сверточные коды в качестве составных кодов.

На фиг.1 изображен известный параллельный турбокодер, который раскрыт в патенте США 5446747 Берроу (Berrou), представленный здесь в качестве ссылки. Турбокодер (фиг. 1) включает в себя перемежитель 120, расположенный между первым составным кодером 110 и вторым составным кодером 130. Перемежитель 120 имеет такой же размер, как и длина N кадра, бит входных данных и изменяет размещение бит данных, которые будут вводить во второй входной кодер 130 для уменьшения связи между битами четности.

Первый составной кодер 110 кодирует биты входных данных, и перемежитель 120 выполняет перемежение бит входных данных в соответствии со специфическим правилом для изменения размещения бит данных. Второй составной кодер 130 кодирует выходной сигнал перемежителя 120. Составной кодер 110 и 130 имеют одинаковую структуру.

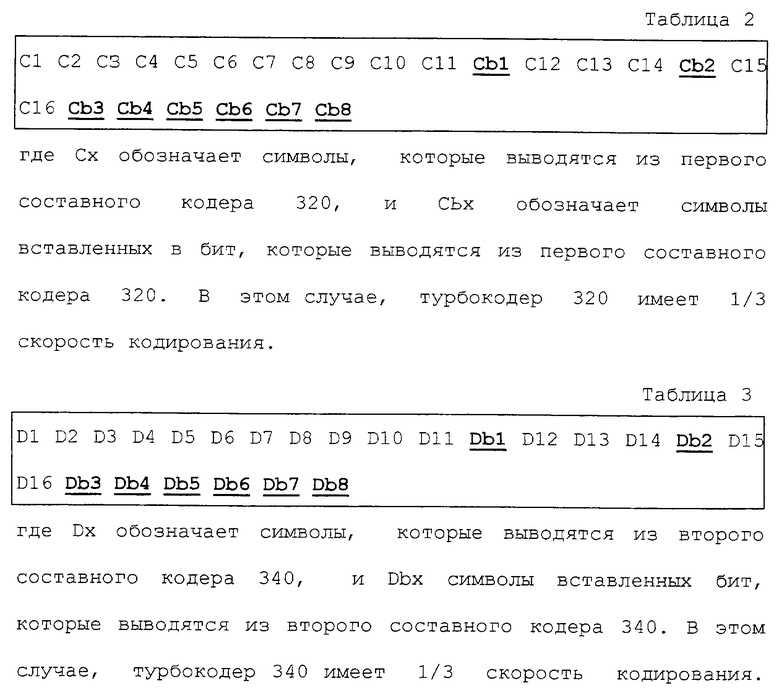

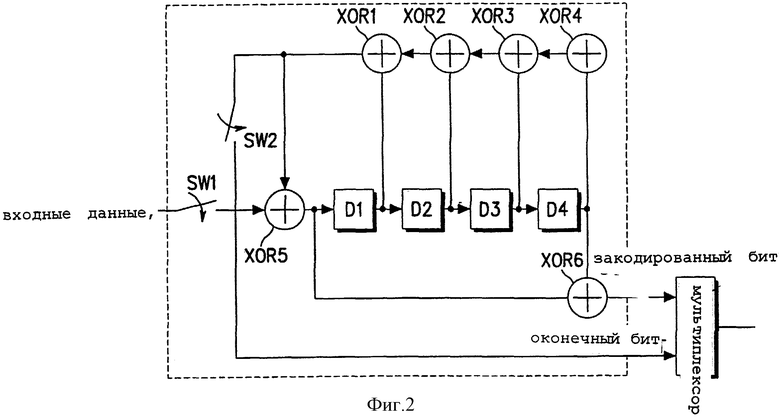

Фиг. 2 изображает схему, иллюстрирующую схему завершения в рекурсивном системном сверточном кодере (фиг.1). Для более подробной информации смотри работу Д. Дивсалара и Ф. Поллара "К вопросу о построении турбокодов", ТДА Прогресс Репорт 122-123, 15, 1995 (D. Divsalar and P. Pollara, "On the Design of Turbo codes", TDA Progress Report 42-123, Nov. 15, 1995), приведенную здесь в качестве ссылки. В этом случае данные одного кадра, которые вводятся в первый и второй составные кодеры 110 и 130, предполагаются 20-битовыми данными. На фиг.2 D1-D4 обозначают задержки логических элементов исключающее ИЛИ XOR1- XOR6.

Во время кодирования (фиг.2) коммутатор SW1 включен, коммутатор SW2 выключен. Затем данные 20-битового входного кадра подаются последовательно в задержки D1-D4 и выполняется операция исключающее ИЛИ с помощью логических элементов исключающее ИЛИ XOR1-XOR6, таким образом обеспечивая вывод закодированных бит в XOR6. Когда все 20-бит данных кодируются таким способом, коммутатор SW1 выключен и коммутатор SW2 включен в течение завершения кадра. Затем логические элементы исключающие ИЛИ XOR1-XOR4 выполняют логическую операцию исключающее ИЛИ бит выходных данных задержки и соответствующих бит данных обратной связи, соответственно, таким образом обеспечивая нулевые биты. Полученные в результате нулевые биты вводятся снова в задержки D1-D4 последовательно и сохраняются в них. Эти нулевые биты, которые вводятся в задержки D1-D4, становятся оконечными битами, и оконечные биты также кодируются с помощью составного кодера, который затем выводит оконечные биты четности, которые подаются в мультиплексор.

Мультиплексор мультиплексирует закодированные биты данных и оконечные биты контроля четности, которые выводятся из составного кодера. Число выработанных оконечных бит зависит от числа задержек, включенных в составные кодеры 110 и 130. Схема завершения (фиг.2) вырабатывает четыре оконечных бита в кадре и четыре закодированных бита (оконечные биты четности) для соответствующих оконечных бит, при этом нежелательно увеличивая число оконечных закодированных бит, которое ведет к уменьшению скорости передачи бит. То есть, когда скорость кодирования определяется как (число входных бит данных)/(число выходных бит данных), турбокод со структурой (фиг.1) имеет скорость кодирования (число входных бит данных)/{(число закодированных бит данных первого составного кодера + первые оконечные биты + первые оконечные биты четности) + (число закодированных бит данных второго составного кодера + вторые оконечные биты четности)}. Соответственно, так как данные кадра (фиг.1) состоят из 20 бит и числа задержек, равного 4, скорость передачи бит становится равной 20/{(20)+(20+4+4)+(20+4+4)}. Такой рекурсивный системный сверточный кодер имеет характеристики, которые зависят от способа получения оконечных бит, потому что трудно получить совершенные оконечные биты в турбокодах.

Сущность изобретения

Поэтому задача настоящего изобретения - предложить устройство и способ для выполнения канального кодирования с использованием структуры кадра, имеющей эффект завершения в рекурсивном системном кодере для системы связи.

Другая задача настоящего изобретения заключается в выполнении рекурсивного системного канального кодирующего устройства и способа для вставки бит, имеющих специфическое значение, в данные кадра в предварительно определенных положениях перед канальным кодированием для достижения эффекта завершения.

Другая задача настоящего изобретения заключается в выполнении рекурсивного системного канального кодирующего устройства и способа вставки бит, имеющих специфическое значение, в предварительно определенные положения потока бит данных входного кадра перед канальным кодированием, причем биты входных данных канального кодирования включают в себя вставленный бит, прокалывающий вставленные биты и закодированные биты данных, превышающие длину кадра в положениях вставки бит потока бит данных входного кадра.

Другая задача настоящего изобретения заключается в выполнении канального кодирующего устройства и способа вставки бит, имеющих специфическое значение, в предварительно определенные положения данных кадров для кодирования входных бит данных, включающих в себя вставленный бит, для выработки закодированного символа и оконечного бита контроля четности с использованием рекурсивного системного составного кодера и для прокалывания вставленных бит для того, чтобы производить вставку оконечного бита контроля четности в положение проколотых вставленных бит.

Для достижения вышеуказанных задач предложено канальное кодирующее устройство. В канальном кодирующем устройстве устройство для вставки бит вставляет биты, имеющие специфическое значение, в положениях, имеющих более высокую вероятность появления ошибок. Составной кодер кодирует выходной сигнал устройства для вставки бит. Селектор селектирует выходной сигнал устройства для вставки бит и входной сигнал составного кодера и выводит выбранное значение в качестве канальных закодированных данных.

Краткое описание чертежей

Сущность изобретения иллюстрируется ссылкой на сопроводительные чертежи, на которых:

Фиг. 1 изображает схему, иллюстрирующую сверточный канальный кодер для системы связи;

Фиг. 2 изображает схему, иллюстрирующую составной кодер (110 или 130) (фиг.1);

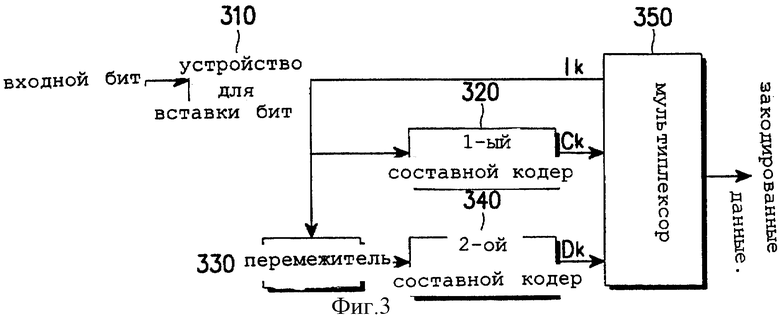

Фиг.3 изображает схему, иллюстрирующую канальный кодер, согласно первому варианту осуществления настоящего изобретения;

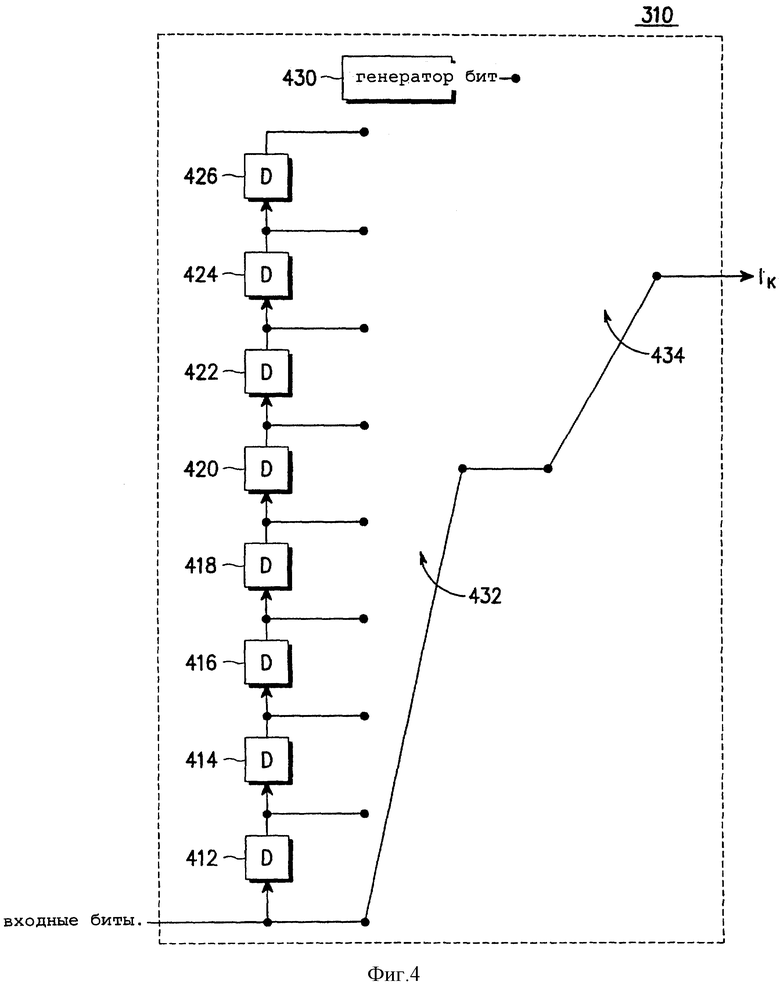

Фиг. 4 изображает подробную схему, иллюстрирующую устройство для вставки (310) бит (фиг.3);

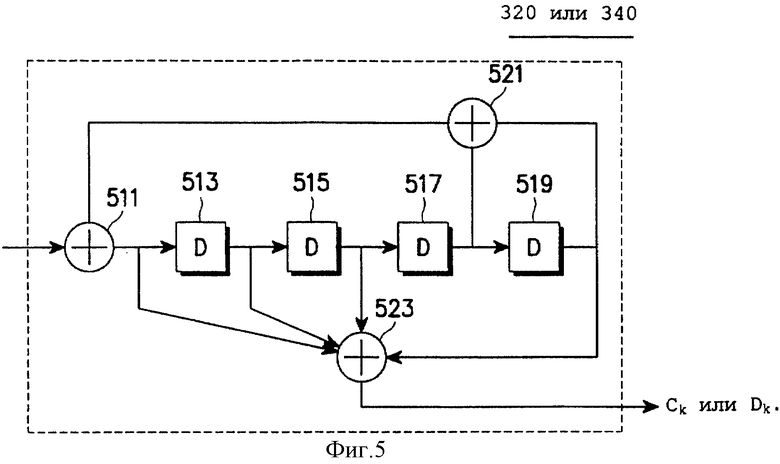

Фиг. 5 изображает подробную схему, иллюстрирующую составной кодер (320 или 340) (фиг.3);

Фиг. 6 изображает схему, объясняющую процедуру обработки бит во времени согласно первому варианту осуществления;

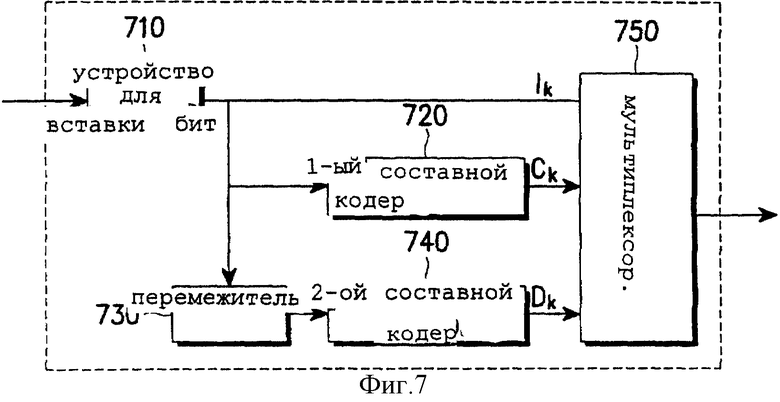

Фиг. 7 изображает схему, иллюстрирующую канальный кодер согласно второму варианту осуществления настоящего изобретения;

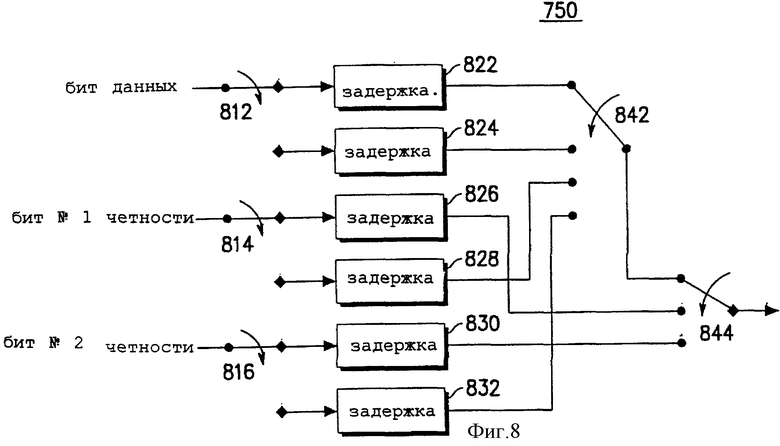

Фиг. 8 изображает подробную схему, иллюстрирующую мультиплексор (750) (фиг.7);

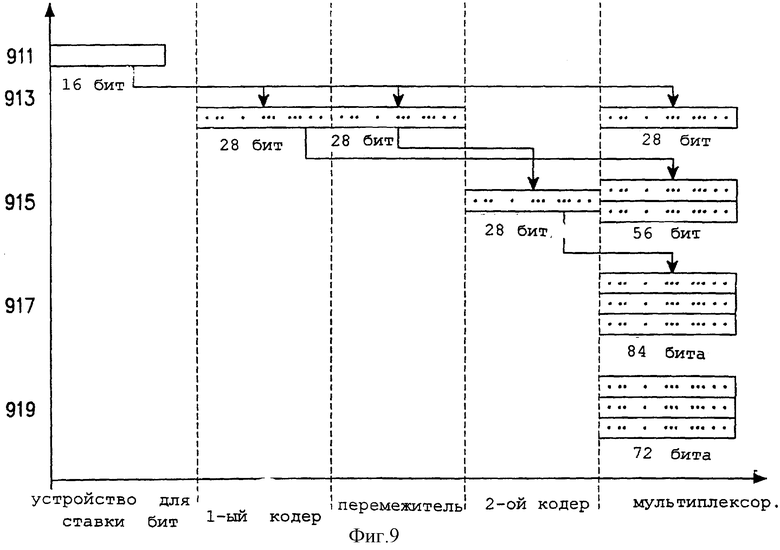

Фиг. 9 изображает схему, объясняющую процедуру обработки бит во времени согласно второму варианту осуществления;

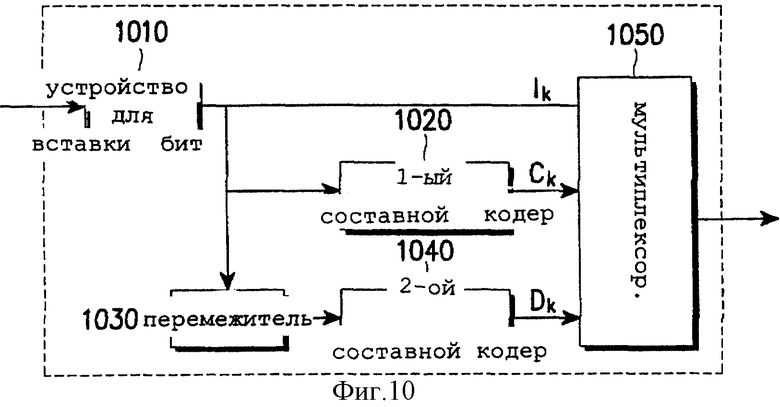

Фиг. 10 изображает схему, иллюстрирующую канальный кодер согласно третьему варианту осуществления настоящего изобретения;

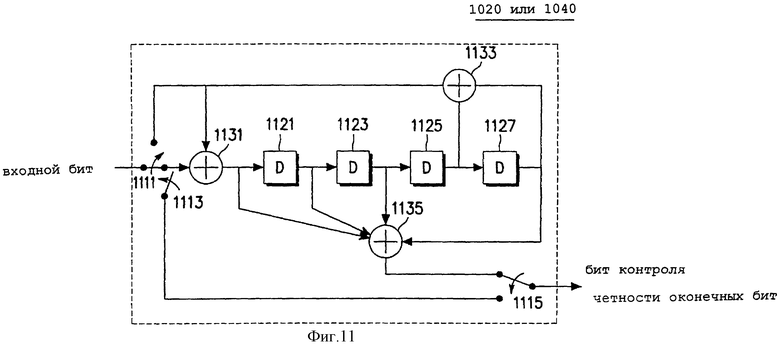

Фиг. 11 изображает подробную схему, иллюстрирующую составной кодер (1020 или 1040) (фиг.10);

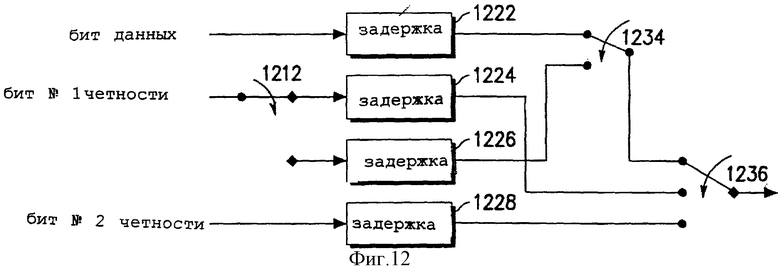

Фиг. 12 изображает подробную схему, иллюстрирующую мультиплексор (1050) (фиг.10);

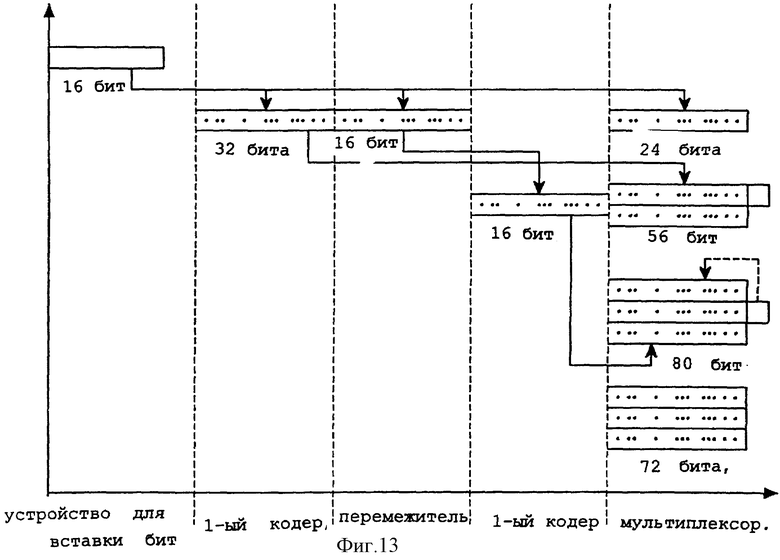

Фиг. 13 изображает схему, объясняющую процедуру обработки бит во времени согласно третьему варианту осуществления;

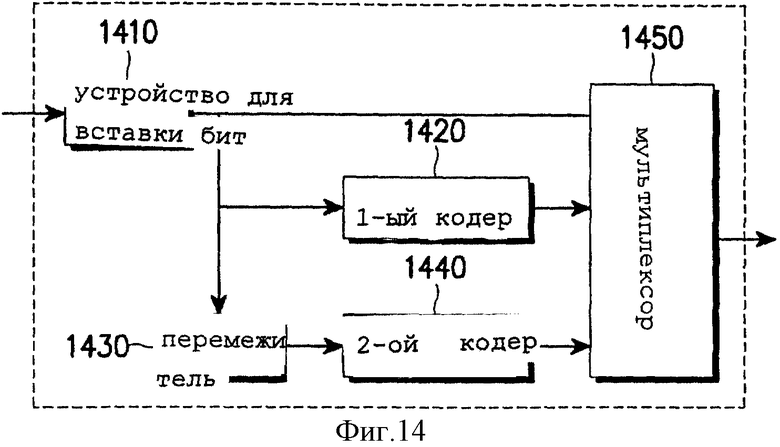

Фиг. 14 изображает схему, иллюстрирующую канальный кодер согласно четвертому варианту осуществления настоящего изобретения;

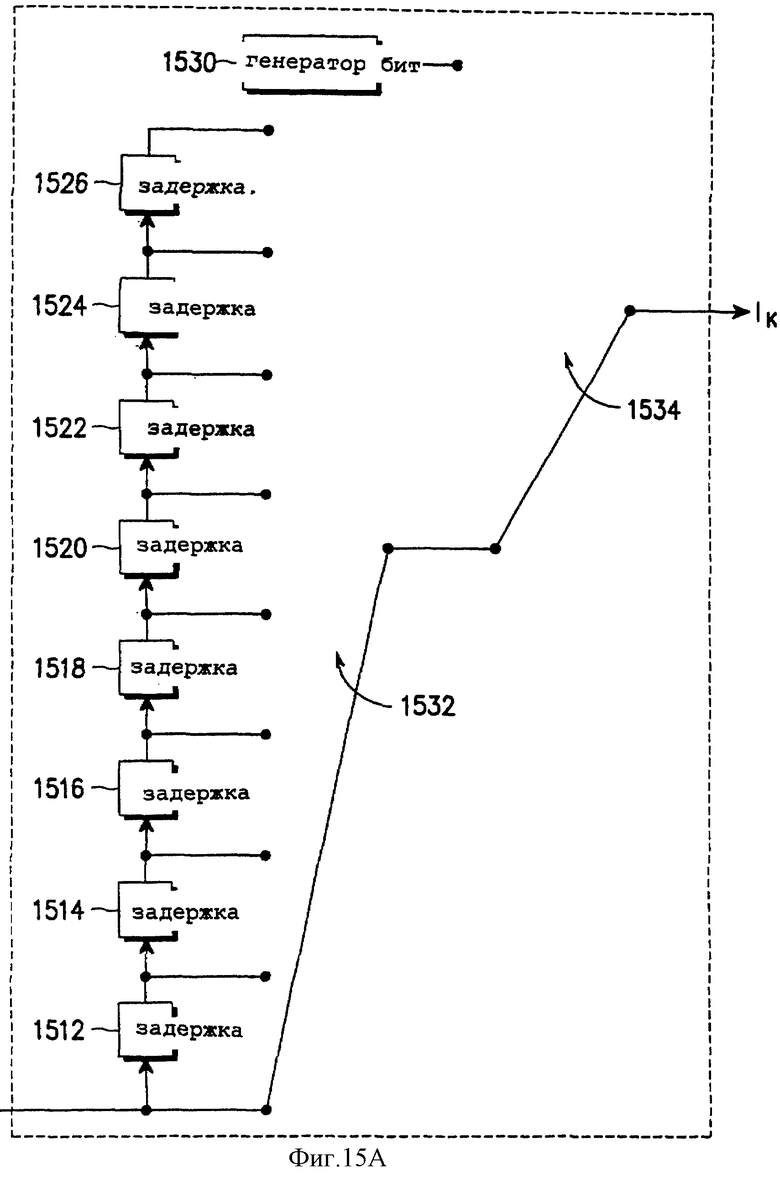

Фиг. 15А изображает подробную схему, иллюстрирующую устройство для вставки (1410) бит (фиг.14);

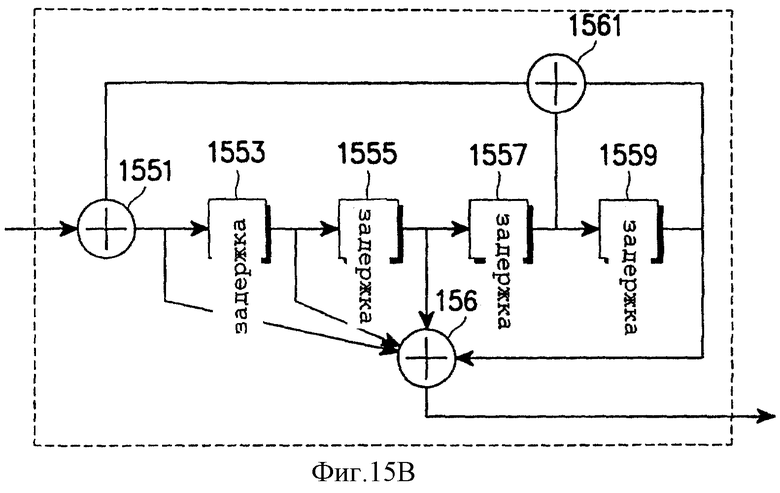

Фиг.15В изображает подробную схему, иллюстрирующую составной кодер (1420 или 1440) (фиг.14);

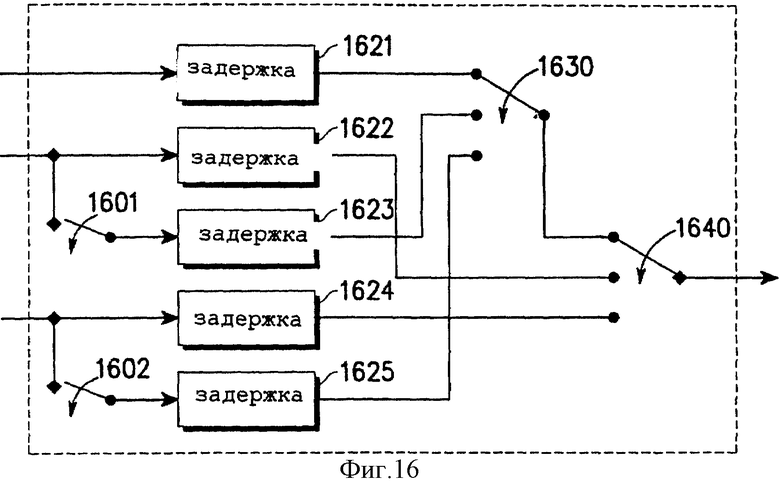

Фиг. 16 изображает подробную схему, иллюстрирующую мультиплексор (1450) (фиг.14);

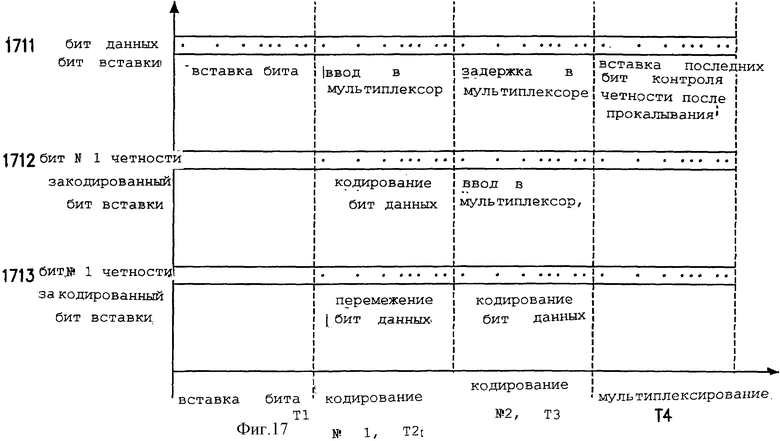

Фиг. 17 изображает схему, объясняющую процедуру обработки бит во времени согласно четвертому варианту осуществления;

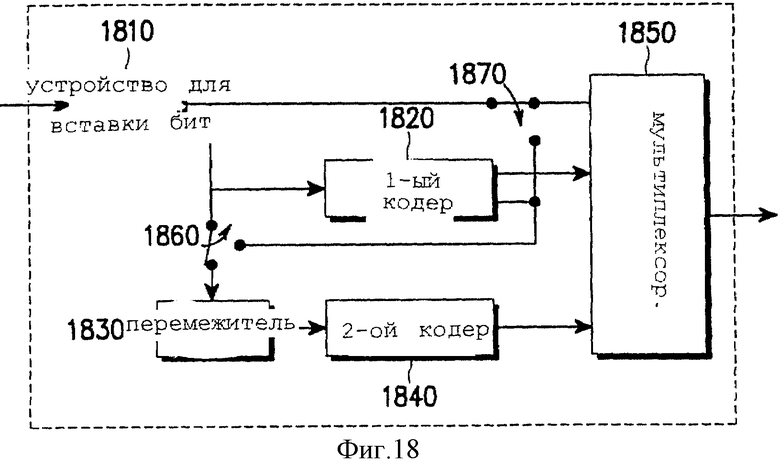

Фиг. 18 изображает схему, иллюстрирующую канальный кодер согласно пятому варианту осуществления настоящего изобретения;

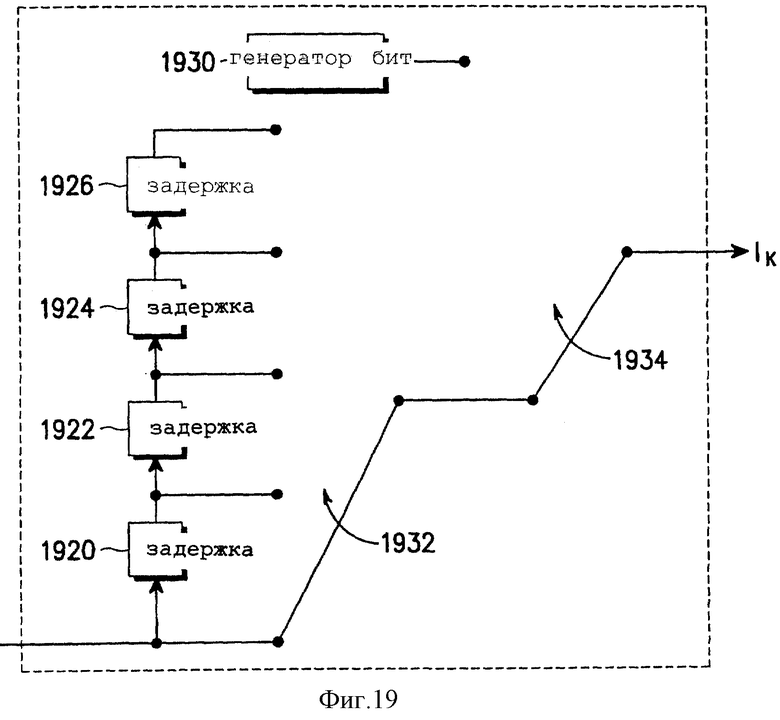

Фиг.19 изображает подробную схему, иллюстрирующую устройство для вставки (1810) бит (фиг.18);

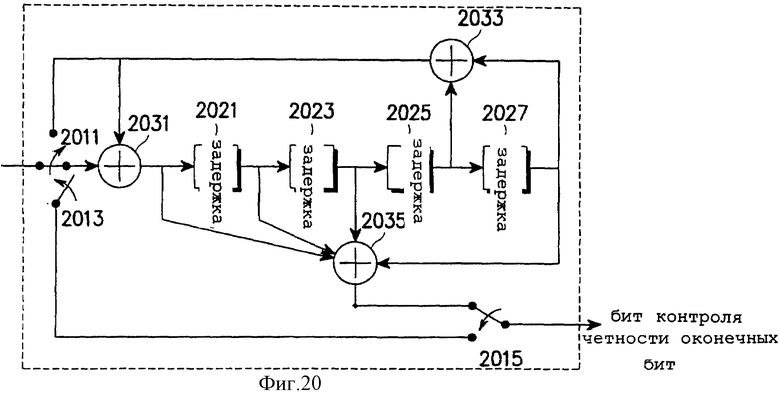

Фиг. 20 изображает подробную схему, иллюстрирующую составной кодер (1820 или 1840) (фиг.18);

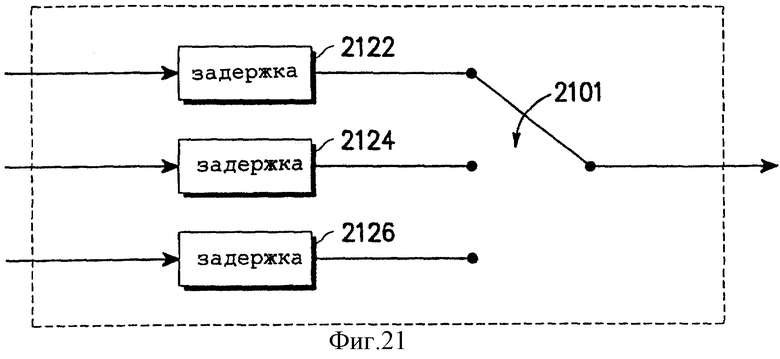

Фиг. 21 изображает подробную схему, иллюстрирующую мультиплексор (1850) (фиг.18);

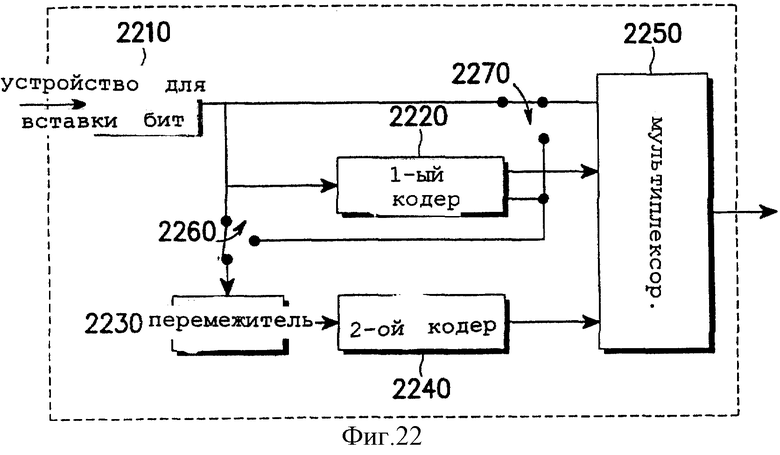

Фиг.22 изображает схему, иллюстрирующую канальный кодер согласно шестому варианту осуществления настоящего изобретения;

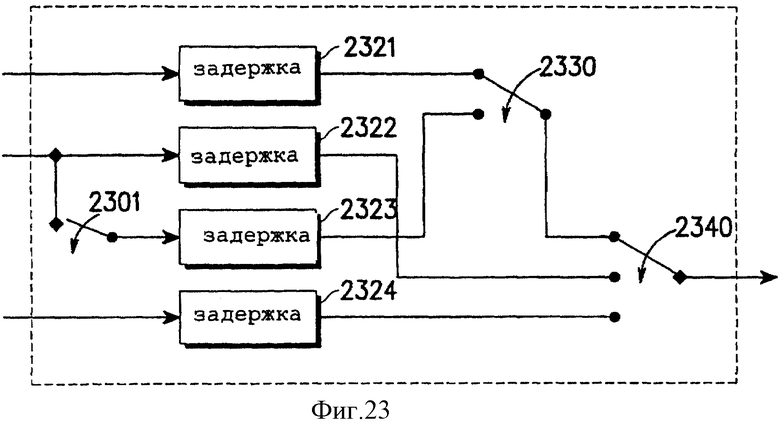

Фиг. 23 изображает подробную схему, иллюстрирующую мультиплексор (2250) (фиг.22);

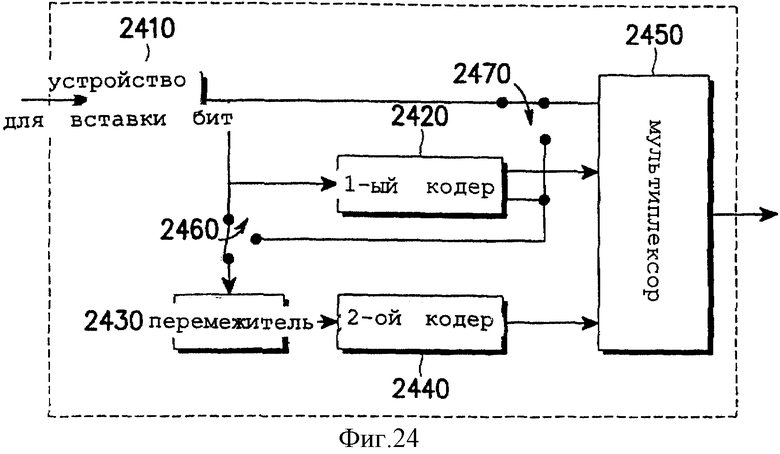

Фиг. 24 изображает схему, иллюстрирующую канальный кодер согласно седьмому варианту осуществления настоящего изобретения;

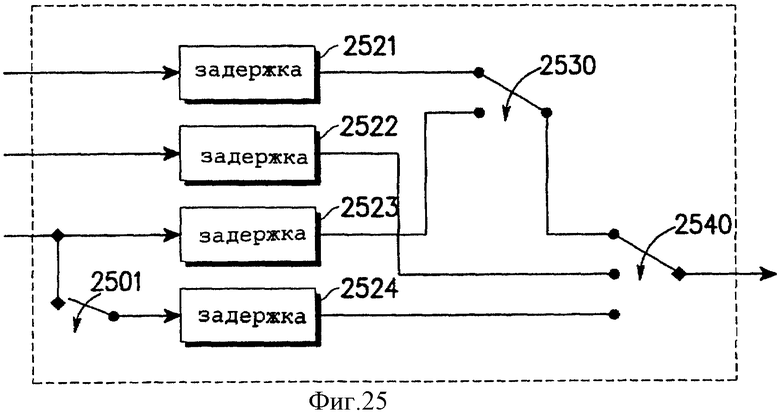

Фиг. 25 изображает подробную схему, иллюстрирующую мультиплексор (2450) (фиг.24);

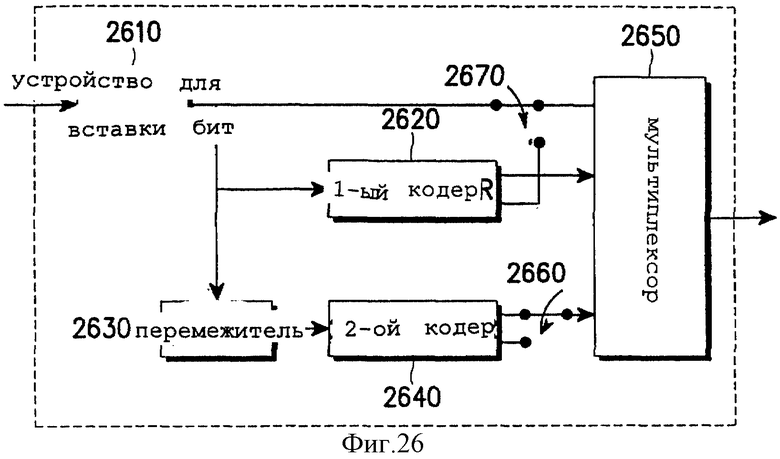

Фиг. 26 изображает схему, иллюстрирующую канальный кодер согласно восьмому варианту осуществления настоящего изобретения;

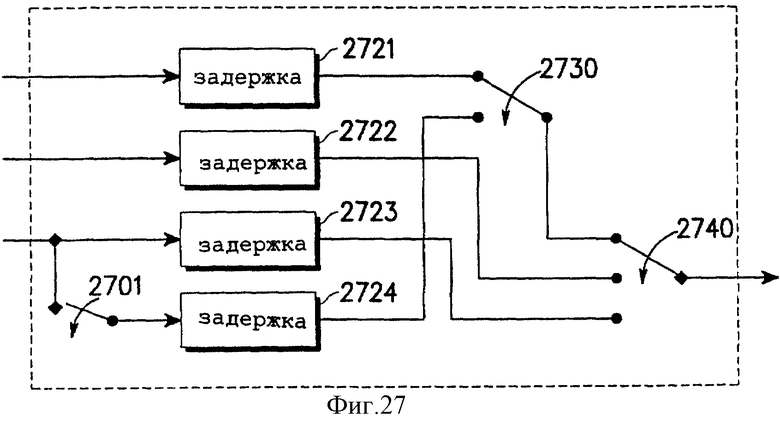

Фиг. 27 изображает подробную схему, иллюстрирующую мультиплексор (2650) (фиг.26);

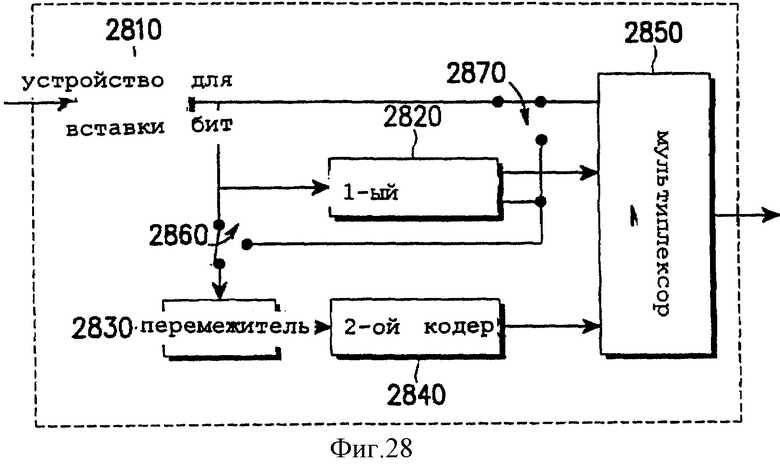

Фиг. 28 изображает схему, иллюстрирующую канальный кодер согласно девятому варианту осуществления настоящего изобретения;

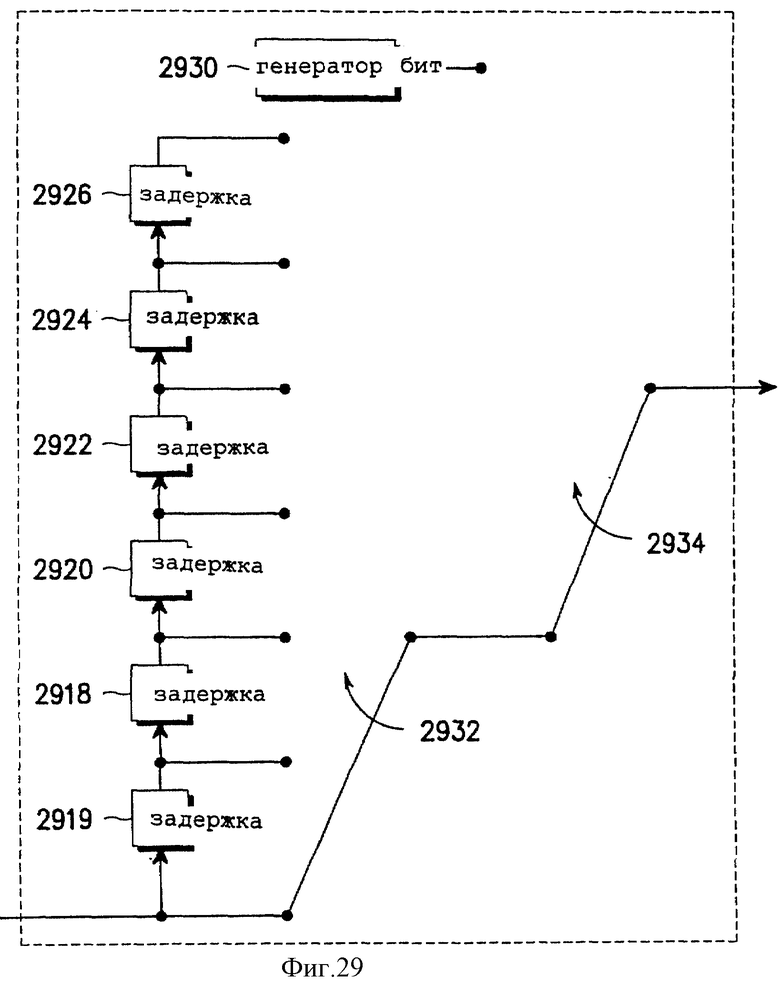

Фиг.29 изображает подробную схему, иллюстрирующую устройство для вставки (2810) бит (фиг.28); и

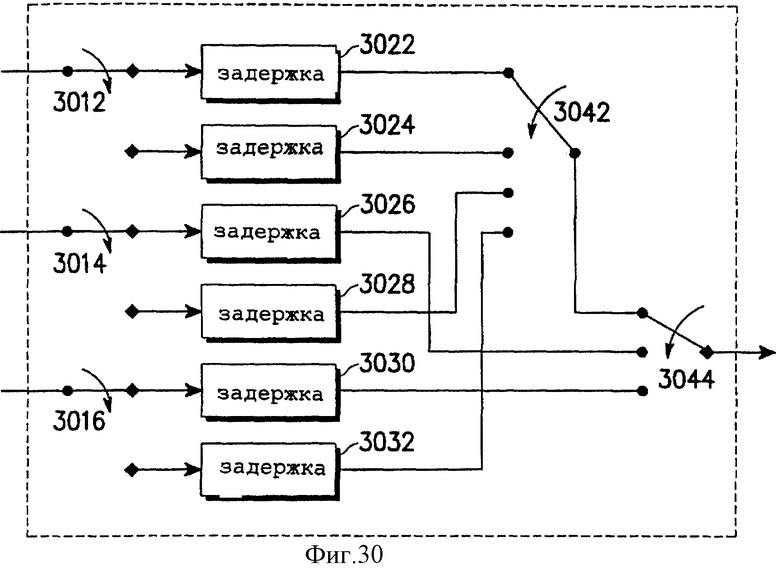

Фиг. 30 изображает подробную схему, иллюстрирующую мультиплексор (2850) (фиг.28).

Подробное описание предпочтительного варианта осуществления

Ниже описывается предпочтительный вариант осуществления настоящего изобретения со ссылкой на сопроводительные чертежи. В следующем ниже описании хорошо известные функции или конструкции не описываются подробно, поскольку они усложняют изобретение излишними подробностями.

Используемый в этом изобретении термин "бит данных" относится к данным, которые не кодируются, а термин "бит контроля четности" относится к данным, которые кодируются с помощью составного кодера.

В системе связи передатчик обычно кодирует передаваемые данные с использованием канального кодера и посылает закодированные данные, затем приемник демодулирует данные, которые поступают из передатчика для преобразования полученных данных в первоначальные данных. В этом случае канальный кодер кодирует передаваемые данные в блоке кадра и вырабатывает оконечные биты, которые добавляются в каждый кадр передаваемых данных для указания завершения кадра. Настоящее изобретение предлагает структуру кадра, которая имеет эффект завершения в канальном кодере.

Структуру кадра, имеющую эффект завершения, можно реализовать несколькими способами:

Во-первых, известные биты вставляются в один канальный кадр в положение, имеющее более высокую вероятность появления ошибок вплоть до числа оконечных бит. В этом случае рекурсивные системные составные кодеры не могут иметь структуру для выработки оконечных бит. Вероятность ошибки определяется с помощью экспериментов, и положения ставки должны быть известны как для канального кодера, так и для канального декодера. Положение бита вставки должно быть известно с помощью передачи соответствующего сообщения во время процедуры установления вызова или во время процедуры назначения канала. Известные биты, которые необходимо вставлять, могут быть незначащими битами, которые редко влияют на характеристики связи даже тогда, когда они не передаются. К тому же они могут кодировать биты или биты данных, предварительно определенных с помощью приемника. В этом случае предполагается, что они представляют собой нулевые биты.

Во-вторых, известные биты вставляются в канальный кадр в положение, имеющее более высокую вероятность появления ошибок вплоть до числа оконечных бит, в котором число известных вводимых бит превышает определенную длину кадра. Биты данных со вставленными битами кодируют с использованием составных кодеров. Затем при выводе канальных закодированных данных биты, превышающие длину кадра канальных закодированных данных прокалываются в положениях со вставленными битами входных данных. В этом случае рекурсивный системный кодер не вырабатывает оконечные биты и канальный кодер должен предварительно знать о положениях вставленных бит.

В-третьих, известные биты вставляются в канальный кадр в положения, имеющие более высокую вероятность вплоть до числа оконечных бит, при выработке канального закодированного сигнала с использованием структуры кадра, имеющей эффект завершения, составной кодер вырабатывает оконечные биты для завершения и закодированные данные для оконечных бит и после этого прокалывают биты данных в специфических вставленных положениях для вставки оконечных бит и закодированных данных для оконечных бит в проколотых положениях для вставки бит.

В-четвертых, оконечные биты не вырабатываются, и известные биты вставляются в канальный кадр в положения, имеющие более высокую вероятность ошибок. В положениях вставки бит множество закодированных бит данных повторяют и передают вместо вставленных бит.

В-пятых, для завершения биты, имеющие специфическую логику, вставляются в биты данных в положения бит, имеющие более высокую вероятность ошибок. Составной кодер кодирует биты данных со вставленными битами и вырабатывает оконечные биты, которые добавляются в закодированные биты данных. То есть, составной кодер выполняет функцию завершения с помощью вставки бит и добавления оконечных бит.

В-шестых, выполняется та же самая операция, как и в пятом способе. Кроме того, вставленные биты прокалываются в положениях вставки бит, и первый составной кодер повторно передает четыре оконечных бита контроля четности в проколотых положениях.

В-седьмых, выполняется та же самая операция, как и в шестом способе. Кроме того, вставленные биты прокалываются в положениях вставки бит, и второй составной кодер повторно передает последние четыре бита контроля четности в проколотых положениях.

В-восьмых, для завершения биты, имеющие специфическую логику, вставляются в биты данных в положениях бит, имеющих более высокую вероятность ошибок. Составной кодер кодирует биты данных со вставленными битами и первоначально вырабатывает оконечные биты, которые добавляются к закодированным битам данных.

В-девятых, для завершения 6 бит, имеющих специфическую логику, вставляют биты данных в положения бит, имеющие более высокую вероятность ошибок. Устройство для вставки бит прокалывает вставленные биты в положения для вставки бит. Первый составной кодер выполняет удаление оконечных бит в проколотых положениях и выполняет перемежение бит данных, которые включены в оконечные биты. При кодировании выходного сигнала первого составного кодера второй составной кодер вводит 6 бит, превышающих длину кадра в положениях вставки проколотых бит.

Ниже приводится ссылка на девять различных вариантов осуществления, использующих вышеуказанные способы вставки бит.

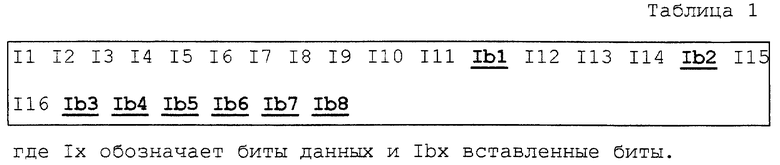

Первый вариант осуществления

Кодер согласно первому варианту осуществления настоящего изобретения не вырабатывает оконечные биты и вместо этого производит вставку известных бит в предварительно определенные положения для выполнения функции завершения. В этом варианте осуществления один кадр имеет 16 бит данных и 8 известных кодов бит, каждый из которых является нулевым битом, вставляются в кадр в положения бит, имеющие более высокую вероятность ошибок. В этом случае положения для вставки бит определяются с помощью экспериментального обнаружения положения, где происходит большинство ошибок при декодировании закодированных данных. Кроме того, в турбокодере используется 1/3 скорость кодирования.

В этом варианте осуществления положения, имеющие более высокую вероятность ошибок во время декодирования, определяются экспериментально в случае, когда 24-битовые данные кадра (16 бит данных кадра плюс 8 известных бит) кодируют с использованием турбокодера, имеющего 1/3 скорость кодирования. Положения 8 бит, имеющие относительно высокую вероятность ошибок, определяют и в определенных положениях вставляют известные биты в биты данных кадра. В этом случае кодеру известно о положении со вставленными битами в случае, когда закодирование закодированных данных кадра, в которых вставлены специфические коды.

Когда известные биты представляют собой нулевые биты (на практике "0" биты передаются в виде "-1"), нулевые биты во вставленных положениях заменяются на большое отрицательное значение (например, -5) перед декодированием для того, чтобы увеличить надежность. В этом способе декодер декодирует биты, при этом зная 8 бит, которые представляют собой 1/3 24 бит, таким образом обеспечивая улучшение технических характеристик. В этом случае увеличивается производительность, так как кадр становится короче.

Фиг. 3 изображает схему, иллюстрирующую турбокодер, имеющий устройство для вставки бит для вставки известных бит согласно первому варианту осуществления настоящего изобретения. Устройство для вставки 310 бит включает в себя генератор бит для выработки известных бит с помощью обработки входных бит данных и вырабатывает биты данных в блоке кадра с помощью вставки известных бит, которые вырабатываются с помощью генератора бит в предварительно определенных положениях для вставки бит. Первый составной кодер 320 кодирует биты данных, которые выводятся из устройства для вставки 310 бит. Перемежитель 330 выполняет перемежение бит данных в блоке кадра, который выводится из устройства вставки 310 бит в соответствии с предварительно определенным правилом для того, чтобы изменить размещение (или последовательность бит данных). В образцовом варианте осуществления диагональный перемежитель используется для перемежителя 330. Второй составной кодер 340 кодирует чередующиеся биты данных в блоке кадра, которые выводятся из перемежителя 330. Рекурсивные системные сверточные кодеры можно использовать для первого и второго составных кодеров 320 и 340. Мультиплексор 350 мультиплексирует выходной сигнал устройства вставки 310 бит, первого составного кодера 320 и второго составного кодера 340 под управлением неизображенного контроллера. В этом случае устройство для вставки 310 бит выводит поток Ik бит данных, первый составной кодер 320, первые биты P1k контроля четности и второй составной кодер 340, вторые биты Р2k контроля четности.

Фиг. 4 изображает схему, иллюстрирующую устройство для вставки 310 бит в турбокодер (фиг.3). На фиг.4 генератор 430 бит вырабатывает известные биты, которые необходимо ввести в биты данных. В этом случае известные биты предполагаются равными нулевым битам. Задержки 412-426, которые могут состоять из элементов памяти, таких как триггеры, могут иметь структуру регистра с последовательным сдвигом для сдвига входных бит данных в соответствии с тактовым сигналом бит. Коммутатор 432 коммутируется для того, чтобы выбрать выходные сигналы задержек 412-426 под управлением неизображенного контроллера. К тому же коммутатор 432 коммутируется на выходе следующей задержки в положениях, где известный бит, который выводится из генератора 430 бит, вставляется в биты данных под управлением неизображенного контроллера. То есть коммутатор 432 выбирает бит данных, который задерживается на один бит, когда выбранный известный бит вставляется в биты данных. Коммутатор 432 можно реализовать с помощью мультиплексора. Коммутатор 434 коммутируется на выходах генератора 430 бит и коммутатор 432 для выработки бит Ik данных под управлением неизображенного контроллера. Коммутатор 434 производит вставку известных бит во входных битах данных в предварительно определенных положениях под управлением контроллера.

Ниже приводится описание операции вставки известных бит в биты данных со ссылкой на фиг. 4. Входные биты данных задерживаются с помощью задержек 412-426 в соответствии с тактовым сигналом бит. В исходном состоянии коммутатор 432 выбирает входные биты данных, и коммутатор 434 подсоединяется к коммутатору 432. Затем входные биты данных выводятся через коммутаторы 432 и 434. Между тем, если положение для вставки бит определено, коммутатор 432 подсоединяется к выходу задержки 412, и коммутатор 434 подсоединяется к выходу генератора 430 бит под управлением контроллера. В результате путь бит данных отсекается и нулевой бит, который выводится из генератора 430 бит, вставляется в соответствующие положения бит. В случае, когда биты данных необходимо непрерывно выводить после вставки нулевого бита, коммутатор 434 снова подсоединяется к коммутатору 432 с помощью контроллера. То есть, так как бит данных с задержкой на один бит выбирается после вставки нулевого бита, нулевой бит можно вставить в предварительно определенное положение без потери бита данных.

Нулевые биты вставляют в биты данных для одного кадра с помощью повторения этого процесса. После приема бит данных для следующего кадра после вставки нулевых бит коммутатор 432 подсоединяется ко входному узлу бит данных и затем вышеуказанный процесс повторяется снова. В случае, когда биты данных кодируются для связи, вероятность ошибки является относительно высокой в задней части потока бит данных, который вводится в соответствующие составные кодеры. Соответственно, положение, где нулевые биты, которые выводятся из генератора 430 бит, вставляются, можно в наибольшей степени расположить в задней части потока бит данных так, как показано в таблице 1 с помощью примера.

Причиной вставки известных бит в поток бит данных является улучшение характеристик декодирования в приемнике. Поэтому предпочтительно производить вставку известных бит в положение бит в кадре канала, имеющем более высокую вероятность проявления ошибок, вплоть до числа и оконечных бит. В большинстве случаев положения бит, имеющие более высокую вероятность в проявлении ошибок, распределяются в задней части потока бит данных, которые вводятся в составные декодеры (таблица 1). Соответственно, известные биты вставляются в заднюю часть потоков бит данных, которые вводятся в первый и второй составные кодеры 320 и 340. В этом случае для второго составного кодера 340 известные биты необходимо ввести в заднюю часть чередующихся бит данных, которые выводятся из перемежителя 330. Соответственно, в устройство для вставки 310 бит должно поступать это с учетом вставки известных бит в бит данных, которые подаются на второй составной кодер 340.

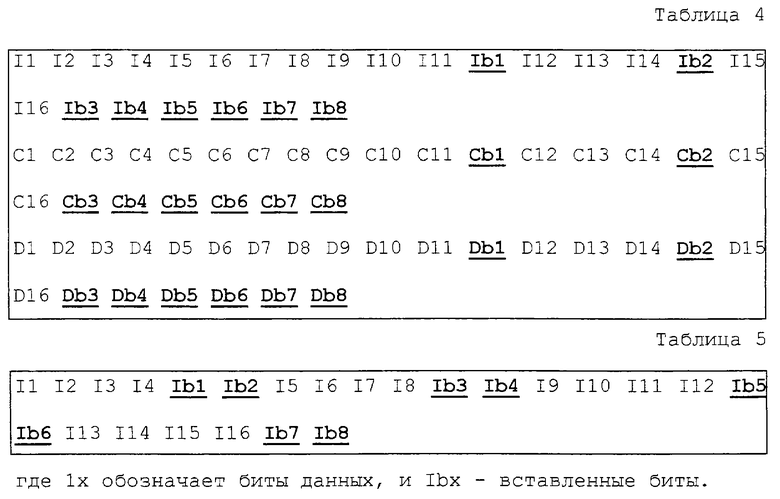

Биты данных (таблица 1), которые выводятся из устройства вставки 310 бит, подаются на первый составной кодер 320 и перемежитель 330. Чередующиеся биты данных в блоке кадра, которые выводятся из перемежителя 310, кодируются с помощью второго составного кодера 340. На фиг.5 изображена структура первого и второго составных кодеров 320 и 340 (фиг.3). Как изображено на чертеже, первый и второй составные кодеры 320 и 340 являются рекурсивными системными сверточными кодерами. Кроме того, составные кодеры 320 и 340 имеют структуру, которая не позволяет вырабатывать оконечные биты, как показано на фиг.5.

Первый составной кодер 320 кодирует биты данных (таблица 1), которые выводятся из устройства вставки 310 бит. Закодированные биты данных, которые выводятся из первого составного кодера 320, показаны в таблице 2.

Между тем перемежитель 330 выполняет перемежение бит данных, которые выводятся из устройства вставки 310 бит, и второй составной кодер 340 кодирует чередующиеся биты данных, которые выводятся из перемежителя 330. Закодированные биты данных, которые выводятся из второго составного кодера 340, показаны в таблице 3.

Хотя последовательность бит данных была реально переразмещена с помощью перемежения, для удобства объяснения последовательность оставлена неизменной в таблице 3.

Мультиплексор 350 затем мультиплексирует выходные сигналы устройства вставки 310 бит, первого составного кодера 320 и второго составного кодера 340 под управлением неизображенного контроллера. В таблице 4 показаны канальные закодированные биты данных, которые выводятся из мультиплексора 350.

Характеристики канального кодера могут изменяться вплоть до положений вставки известных бит. Например, можно улучшить характеристики канального кодера с помощью вставки известных бит во входной поток бит данных на регулярных интервалах, как показано в таблице 5.

Соответственно, как показано в таблице 5, известные биты предпочтительно непрерывно вставлять во входной поток бит данных на регулярных интервалах вплоть до числа устройств памяти в составных кодерах (например, для длины кодового ограничения 3 непрерывно вводят два известных бита).

Фиг.6 изображает временную диаграмму турбокодера (фиг.3) согласно первому варианту осуществления настоящего изобретения. На фиг.6 показано, что в интервале времени Т1 устройство для вставки 310 бит выполняет вставку нулевых бит в кадр в предварительно определенное положение бит для выработки бит Ik данных (таблица 1, смотри 611). В интервал 12 биты Ik данных с нулевыми вставленными битами одновременно подаются в мультиплексор 350, первый составной кодер 320 и перемежитель 330. Затем первый составной кодер 320 кодирует биты Ik данных с нулевыми вставленными битами для выработки первых закодированных бит Сk данных, которые являются первыми битами (смотри 612) контроля четности, и перемежитель 330 выполняет перемежение бит Ik данных с нулевыми вставленными битами в соответствии с предопределенным правилом (смотри 613). Поэтому в интервале Т3 мультиплексор 350 задерживает биты Ik данных, которые выводятся из устройства вставки 310 бит с помощью одного периода кадра, составной кодер 320 вводит первые закодированные биты Ck данных в мультиплексор 350, и второй составной кодер 340 кодирует чередующиеся биты Ik данных, которые выводятся из перемежителя 330 для выработки вторых закодированных данных Dk данных, которые являются вторыми битами контроля четности. После того как второй составной кодер выработал вторые биты Dk контроля четности, мультиплексор 350 мультиплексирует биты Ik данных, первые биты Сk контроля четности и вторые биты Dk контроля четности в интервале Т4.

Хотя на фиг.6 показан пример параллельной обработки бит Ik данных, первых бит Сk контроля четности и вторых бит Dk контроля четности, можно также последовательно выводить выходные сигналы устройства вставки 310 бит, первого составного кодера 320 и второго составного кодера 340 в порядке выработки бит.

Из предыдущего описания можно оценить, что в рекурсивном системном турбокодере согласно первому варианту осуществления соответствующие составные кодеры не вырабатывают оконечные биты для завершения и вместо этого производят вставку известных бит (то есть нулевых бит) в положение бит, имеющих более высокую вероятность ошибок.

Второй вариант осуществления

Канальный кодер согласно второму варианту осуществления настоящего изобретения производит вставку известных бит в положения бит, имеющих более высокую вероятность появления ошибок, в котором число вставленных бит устанавливается с превышением размера кадра (или длины). В этом образцовом варианте осуществления предполагается, что каждый кадр включает в себя 16 входных бит данных и 12 вставленных бит. Так как выходные биты Ik данных, биты Ck и Dk контроля четности должны иметь 28 бит, вставленные биты удаляются и избыточные биты Ck и Dk контроля четности вставляются в положение удаленных бит.

Число вставленных бит определяется с помощью числа входных бит данных кодера, числа выходных символов кода и скорости передачи кода. То есть, когда число входных бит данных кодера составляет N, число выходных символов кода кодера составляет М и скорость передачи кода составляет 1/К, число вставленных бит составляет (М-KN)/(K-1). Из этого следует, когда число входных бит данных кодера составляет 16, число выходных символов кода составляет 72 и скорость передачи кода составляет 1/3, число вставленных бит равно 12.

Действительно, так как число вставленных бит увеличивается, кодер имеет более высокие характеристики. Кодер согласно этому варианту осуществления позволяет максимально улучшить свои характеристики с помощью вставки известных бит насколько это возможно, с заданным числом входных бит данных и числом выходных символов кода. В этом варианте осуществления, когда используется 12 вставленных бит и биты данных передаются после кодирования, можно улучшить характеристики кодера с помощью передачи только закодированных символов без передачи вставленных бит для максимальной вставки бит.

Фиг. 7 изображает схему, иллюстрирующую канальный кодер согласно второму варианту осуществления настоящего изобретения. Устройство для вставки 710 бит включает в себя генератор бит для выработки известных бит с помощью обработки входных бит данных и вырабатывает биты данных, которые превышают размер кадра, с помощью вставки известных бит, которые вырабатываются с помощью генератора бит, в предварительно определенные положения бит. Первый составной кодер 720 кодирует биты данных, которые выводятся из устройства вставки 710 бит, для выработки первых бит Ck контроля четности. Перемежитель 730 выполняет перемежение бит данных в блоке кадра, который выводится из устройства вставки 710 бит, в соответствии с предопределенным правилом для того, чтобы изменять размещение (или последовательность) бит данных. В образцовом варианте осуществления диагональный перемежитель используется для перемежителя 730. Второй составной кодер 740 кодирует чередующиеся биты данных в блоке кадра, которые выводятся из перемежителя 730, для выработки вторых бит Dk контроля четности. Рекурсивный системный сверточный кодер можно использовать для первого и второго составных кодеров 720 и 740. Мультиплексор 750 мультиплексирует выходные сигналы устройства вставки 710 бит, первого составного кодера 720 и второго составного кодера 740 для выработки кадра данных с предварительно определенной длиной под управлением неизображенного контроллера. В этом случае устройство для вставки 710 бит выводит биты Ik данных, первый составной кодер 720 первые биты P1k контроля четности и второй составной кодер 740 вторые биты Р2k контроля четности.

В рабочем состоянии после получения 16 входных бит данных устройство для вставки 710 бит работает так же, как и устройство для вставки 310 бит первого варианта осуществления. Устройство для вставки 710 бит имеет структуру, подобную той, которая изображена на фиг. 4, за исключением того, что он состоит из 12 задержек. Поэтому устройство для вставки 710 бит производит вставку 12 нулевых бит в кадр в положения 12 бит, имеющие более высокую вероятность ошибок, путем управления внутренних коммутаторов под управлением контроллера. Соответственно, в этом варианте осуществления устройство для вставки 710 бит выводит 28 бит Ik данных, которые одновременно подаются в мультиплексор 750, первый составной кодер 720 и перемежитель 730. Кроме того, чередующиеся биты Ik данных, которые выводятся из перемежителя 730, подаются во второй составной кодер 740. В этом случае первый и второй составные кодеры 720 и 740 имеют структуру (фиг.5), которая не вырабатывает оконечные биты для завершения.

Первый составной кодер 720 затем кодирует 28 бит Ik данных с 12 нулевыми битами, которые вставляются в них и выводятся из устройства для вставки 710 бит, и выводит 28 первых бит Ck контроля четности в мультиплексор 750. Перемежитель 730 выполняет перемежение 28 бит Ik данных, которые выводятся из устройства вставки 710 бит, и второй составной кодер 740 кодирует чередующиеся биты данных тем же самым способом, как и у первого составного кодера 720 для выработки 28 вторых бит Dk контроля четности, которые подаются в мультиплексор 750.

Мультиплексор 750 выполняет прокалывание вставленных бит из бит Ik данных для вставки шести первых бит Ck контроля четности и шести вторых бит Dk контроля четности в проколотые положения и затем выводит оставшиеся 22 первых бита Ck контроля четности и оставшиеся 22 вторых бита Dk контроля четности.

На фиг.8 показано, что мультиплексор 750 первым получает 28 бит Ik данных, которые выводятся из устройства вставки 710 бит. Затем коммутатор 812, расположенный в мультиплексоре 750, подсоединяется к задержке 822 перед тем, как первые 22 бита данных из 28 бит Ik данных поступают из устройства вставки 710 бит, и задержка 822 задерживает принятые биты Ik данных. Поэтому коммутатор 812 подсоединяется к задержке 824 перед тем, как оставшиеся четыре бита данных из 28 бит Ik данных поступают из устройства вставки 710 бит, и задержка 824 задерживает принятые оставшиеся шесть бит данных.

Мультиплексор 750 получает тем же самым способом 28 первых бит Сk контроля четности, которые выводятся из первого составного кодера 720. Затем коммутатор 814 в мультиплексоре 750 подсоединяется к задержке 826 перед тем, как первые 22 бита данных из 28 первых бит Сk контроля четности поступают из первого составного кодера 720, и задержка 826 задерживает принятые первые биты Сk контроля четности. Поэтому коммутатор 814 подсоединяется к задержке 828 перед тем, как оставшиеся 6 первых бит контроля четности из 28 первых бит Ck контроля четности поступают из составного кодера 720, и задержка 828 задерживает принятые оставшиеся 6 первых бит контроля четности.

Поэтому мультиплексор 750 получает 28 вторых бит Dk контроля четности, которые выводятся из второго составного кодера 740. Затем коммутатор 816 в мультиплексоре 750 подсоединяется к задержке 830 перед тем, как первые 22 бита данных из 28 вторых бит Dk контроля четности поступают из второго составного кодера 740, и задержка 830 задерживает принятые вторые биты Dk контроля четности. Поэтому коммутатор 816 подсоединяется к задержке 832 перед тем, как оставшиеся 6 вторых бит контроля четности из 28 первых бит Dk контроля четности поступают из второго составного кодера 740, и задержка 832 задерживает принятые оставшиеся 6 вторых бит контроля четности.

Как описано выше, мультиплексор 750 последовательно получает 28 бит Ik данных, 28 первых бит Ck контроля четности и 28 вторых бит Dk контроля четности и отдельно сохраняет первые 22 бита и оставшиеся 6 бит из соответствующих бит в соответствующих задержках. Коммутаторы 812-816 управляются с помощью неизображенного контроллера. Кроме того, каждая задержка 822-832 состоит из каскадных элементов памяти и сохраняет входные биты до тех пор, пока не завершится соответствующий процесс задержки.

После завершения процесса задержки коммутатор 844 подсоединяется к коммутатору 842 и коммутатор 842 подсоединяется к задержке 822. Поэтому выходной сигнал задержки 822 выводится через коммутаторы 842 и 844. Когда выводится один бит данных, который сохраняется в задержке 822, коммутатор 842 подсоединяется к задержке 824, поддерживая соединение с коммутатором 844. Затем один из оставшихся битов данных, сохраненных в задержке 824, выводится через коммутаторы 842 и 844. То есть бит данных, который сохраняется в задержке 822, прокалывается, и затем выводится бит данных, который сохраняется в задержке 824. После этого коммутатор 842 подсоединяется к задержке 822, постоянно поддерживая соединение с коммутатором 844. Повторяя вышеописанный процесс 6 раз, биты данных, которые сохраняются в задержке 822, прокалываются и затем оставшиеся шесть бит данных, которые сохраняются в задержке 824, вставляются в проколотые положения.

Впоследствии коммутатор 842 подсоединяется к задержке 822, поддерживая соединение с коммутатором 844. Затем выходной сигнал задержки 822 выводится через коммутаторы 842 и 844. Когда выводится один бит данных, который сохраняется в задержке 822, коммутатор 842 подсоединяется к задержке 828, поддерживая соединение с коммутатором 844. Затем один из оставшихся шести первых бит контроля четности, сохраненных в задержке 828, выводится через коммутаторы 842 и 844. После этого коммутатор 842 снова подсоединяется к задержке 822, непрерывно поддерживая соединение с коммутатором 844. Повторяя вышеописанный процесс 6 раз, биты данных, которые хранятся в задержке 822, прокалываются, и затем оставшиеся шесть первых бит контроля четности, которые сохраняются в задержке 828, вставляются в проколотые положения.

Таким же способом поочередно выводятся биты данных и оставшиеся шесть первых бит контроля четности. Затем коммутатор 842 подсоединяется к задержке 822, поддерживая соединение с коммутатором 844. Затем выходной сигнал задержки 822 выводится через коммутаторы 842 и 844. Когда выводится один бит данных, сохраненный в задержке 822, коммутатор 842 подсоединяется к задержке 832, поддерживая соединение с коммутатором 844. Затем один из оставшихся шести вторых бит контроля четности, которые сохраняются в задержке 832, выводятся через коммутаторы 842 и 844. После этого коммутатор 842 снова подсоединяется к задержке 822, постоянно поддерживая соединение с коммутатором 844. Повторяя вышеописанный процесс 6 раз, биты данных, которые сохраняются в задержке 822, прокалываются, и затем оставшиеся шесть вторых бит контроля четности, которые сохраняются в задержке 832, вставляются в проколотые положения.

С помощью вышеописанной процедуры прокалываются 22 бита данных, которые сохраняются в задержке 822, и затем оставшиеся 6 бит данных, которые сохраняются в задержке 824, оставшиеся 6 первых бит контроля четности, которые сохраняются в задержке 828, и оставшиеся 6 вторых бит контроля четности, которые сохраняются в задержке 832, вставляются в проколотые положения. Соответственно, мультиплексор 750 прокалывает вставленные биты из бит Ik данных, которые выводятся из устройства для вставки 710 бит, и производит вставку 8 бит контроля четности в проколотые вставленные положения, таким образом обеспечивая вывод 24 бит данных.

После завершения вышеописанного процесса коммутатор 844 подсоединяется к задержке 826. Затем выводятся 22 первых бита Сk контроля четности, которые сохраняются в задержке 826. После этого коммутатор 844 подсоединяется к задержке 832 для вывода 22 вторых бит Dk контроля четности, которые сохраняются в задержке 830.

На фиг.9 в кодере (фиг.7) согласно второму варианту осуществления устройство для вставки 710 бит производит вставку 12 бит в 16 входных бит данных для выработки 28 бит Ik данных. Таким образом, первый и второй составные кодеры 720 и 740 вырабатывают 28 первых бит Ck контроля четности и 28 вторых бит Dk контроля четности соответственно. Мультиплексор 750 прокалывает 28 бит Ik данных в 12 вставленных положениях и затем производит вставку в них оставшихся 6 бит данных, оставшихся 6 первых бит контроля четности и оставшихся 6 вторых бит контроля четности. После этого мультиплексор 750 последовательно выводит биты Ik данных, первые биты Сk контроля четности и вторые биты Dk контроля четности.

В процессе декодирования выходные значения мультиплексора 750 демультиплексируются в часть бит данных, в первую часть бит контроля четности и вторую часть бит контроля четности, в котором часть бит данных прокалывается со значением "-5" в части вставки бит. Такие обработанные биты данных декодируются с помощью существующего декодера (смотри Клауди Берроу, Алаин Главиюкс и Панья Титмашима "Кодирование и декодирование с исправлением ошибок в ближнем пределе Шеннона: турбокоды (I)" (D. Divsalar and P. Pollara, "On the Design of Turbo codes", TDA Progress Report 42-123, Nov. 15, 1995).

Третий вариант осуществления

Кодер согласно третьему варианту осуществления настоящего изобретения производит вставку бит, имеющих специфическую логику в битах данных в положениях бит, имеющих более высокую вероятность появления ошибок, в котором составные кодеры кодируют известные биты данных со вставленными битами и вырабатывают оконечные биты, которые будут вставлены в закодированные биты данных. То есть кодер согласно третьему варианту осуществления выполняет функцию завершения с помощью вставки бит и добавления оконечных бит.

Фиг.10 изображает схему, иллюстрирующую кодер согласно третьему варианту осуществления настоящего изобретения. На фиг.10 устройство для вставки 1010 бит получает 16 входных бит и имеет ту же самую структуру, как и устройство для вставки 310 бит согласно первому варианту осуществления. Устройство для вставки 1010 бит производит вставку 8 нулевых бит в кадр в 8 положениях бит данных, имеющих более высокую вероятность ошибок, под управлением неизображенного контроллера. Соответственно, в этом образцовом варианте осуществления устройство для вставки 1010 бит выводит 24 бита Ik данных, которые подаются в общем в мультиплексор 1050, составной кодер 1020 и перемежитель 1030. Кроме того, чередующиеся биты Ik данных, которые выводятся из перемежителя 1030, подаются во второй составной кодер 1040. Первый составной кодер 1020 является рекурсивным системным составным кодером (фиг.11), который имеет структуру для выработки оконечных бит, которые будут добавляться в закодированные биты данных. Кроме того, второй составной кодер 1040 имеет структуру, которая не позволяет вырабатывать оконечные биты для завершения, как в случае, изображенном на фиг.5, первого варианта осуществления.

На фиг.11 описана работа первого составного кодера 1020. Для кодирования коммутатор 1111 подсоединяет входной узел к логическому элементу 1131 исключающее ИЛИ, коммутатор 1113 поддерживает состояние "выключено", и коммутатор 1115 подсоединяется к логическому элементу 1135 исключающее ИЛИ. Затем 24 Ik данных последовательно подаются в задержки 1121-1127 через коммутатор 1111 и логический элемент 1131 исключающее ИЛИ, и логический элемент 1135 исключающее ИЛИ выводит закодированные биты данных. Когда все биты Ik данных кодируются с помощью задержек 1121-1127 и логического элемента 1135 исключающее ИЛИ тем же самым способом, коммутатор 1111 подсоединяется к логическим элементам 1133 и 1131 исключающее ИЛИ, коммутатор 1113 находится в состоянии "включено", и коммутатор 1115 подсоединяется к коммутатору 1113. Затем нулевые биты вырабатываются с помощью операции исключающее ИЛИ на выходах обратной связи, сохраняются в задержках 1121-1127 и выводятся через коммутатор 1115. В этом случае нулевые значения, которые сохраняются в задержках 1121-1127, становятся оконечными битами и выводятся через коммутатор 1115. Число оконечных бит соответствует числу задержек в составном кодере 1020. На фиг.11 первый составной кодер 1020 вырабатывает 4 оконечных бита в кадр, а также вырабатывает закодированные биты для соответствующих оконечных бит контроля четности. Поэтому первый составной код выводит первые 24 бита четности, 4 оконечных бита и 4 оконечных бита четности.

Соответственно, первый составной кодер 1020 вырабатывает 24 первых бита четности Сk и после обработки последнего бита данных (то есть 24-го бита данных) подсоединяет коммутатор 1111 к логическому элементу 1133 исключающее ИЛИ, коммутатор 1113 к коммутатору 1111 и коммутатор 1115 к коммутатору 1113, причем тот же самый процесс повторяется четыре раза для выработки 4 оконечных бита. Следуя этой процедуре, 28 первых бит Ck контроля четности и 4 оконечных бита подаются в мультиплексор 1050.

Кроме того, перемежитель 1030 выполняет перемежение 24 бит Ik данных, которые выводятся из устройства вставки 1010 бит, и обеспечивает подачу чередующихся бит данных во второй составной кодер 1040. Второй составной кодер 1040 затем кодирует чередующиеся биты данных тем же самым способом, как и первый составной кодер 1020, для выработки 24 вторых бит Dk контроля четности, которые подаются в мультиплексор 1050.

Чередующиеся биты данных в блоке кадра, которые выводятся из перемежителя 1030, кодируются с помощью второго составного кодера 1040, который имеет ту же самую структуру, как и на фиг.5. Второй составной кодер 1040 является рекурсивным системным сверточным кодером (фиг.5). Кроме того, второй составной кодер 1040 имеет структуру, которая не вырабатывает оконечные биты.

Мультиплексор 1050 затем прокалывает вставленные биты из бит Ik данных и производит вставку 4 первых бит Ck контроля четности в проколотое положение и выборочно выводит оставшиеся 24 первых бита Сk контроля четности и 24 вторых бита Dk контроля четности.

Фиг. 12 изображает схему, иллюстрирующую мультиплексор 1050. На фиг.12 мультиплексор 1050 первым получает 24 бита Ik данных, которые выводятся из устройства вставки 1010 бит. Задержка 1222 в мультиплексоре 1050 затем сохраняет полученные 24 бита Ik данных.

После этого мультиплексор 1050 получает 28 первых бит Сk контроля четности, которые выводятся из первого составного кодера 1020. Коммутатор 1212 в мультиплексоре 1050 затем подсоединяется к задержке 1224 до тех пор, пока первые 24 бита из первых бит Ck контроля четности не поступят из первого составного кодера 1020, и задержка 1224 сохраняет полученные первые биты Ck контроля четности. Впоследствии коммутатор 1212 подсоединяется к задержке 1226 до тех пор, пока оставшиеся 8 бит из 32 первого выхода составного кода не поступят из первого составного кодера 1020, и задержка 1226 сохраняет оставшиеся 8 бит первого выхода составного кода.

Затем в мультиплексор 1050 поступают 24 вторых бита Dk контроля четности, которые выводятся из второго составного кодера 1040. Задержка 1228 в мультиплексоре 1050 затем сохраняет принятые 24 вторых бита Dk контроля четности.

Таким образом, последовательно выработанные 24 бита Ik данных, 28 первых бит Сk контроля четности и 24 вторых бита Dk контроля четности подаются в мультиплексор 1050. Мультиплексор 1050 затем сохраняет последовательно полученные биты Ik данных, первые биты Сk контроля четности и вторые биты Dk контроля четности в соответствующих задержках в порядке поступления, в котором первые 24 бита и оставшиеся 4 бита из 28 первых бит Сk контроля четности сохраняются отдельно в соответствующих задержках. Каждая из задержек 1222-1228 состоит из каскадных элементов памяти и сохраняет соответствующие входные биты до тех пор, пока не завершился вышеописанный процесс задержки.

После вышеописанного процесса задержки коммутатор 1236 подсоединяется к коммутатору 1234 и коммутатор 1234 подсоединяется к задержке 1222. Таким образом, выходной сигнал задержки 1222 выводится через коммутаторы 1234 и 1236. Когда выводится один бит данных, который сохраняется в задержке 1222, коммутатор 1234 подсоединяется к задержке 1226, поддерживая соединение с коммутатором 1236. Затем один из оставшихся первых бит контроля четности, которые сохраняются в задержке 1226, выводятся через коммутаторы 1234 и 1236. То есть бит данных, который сохраняется в задержке 1222, прокалывается, и затем первый бит контроля четности, который сохраняется в задержке 1226, вставляется в проколотое положение. После этого коммутатор 1234 снова подсоединяется к задержке 1222, поддерживая соединение с коммутатором 1236. Вышеописанная операция повторяется 8 раз для прокалывания бит данных, которые сохраняются в 1222 и вводятся в проколотые положения оставшихся 8 первых бит контроля четности, которые сохраняются в задержке 1226. В результате, в 24 битах Ik данных 8 вставленных бит прокалываются для вставки 8 первых бит контроля четности в проколотых положениях (то есть в положениях вставленных бит), таким образом обеспечивая вывод 24 бита.

После этого коммутатор 1236 подсоединяется к выходу задержки 1224. Затем 24 первых бита Сk контроля четности, которые сохраняются в задержке 1224, выводятся через коммутатор 1236. Затем коммутатор 1236 коммутируется с задержкой 1228 для вывода 24 вторых бит Dk контроля четности, которые сохраняются в задержке 1228.

На фиг. 13 в кодере (фиг.10) согласно третьему варианту осуществления устройство для вставки 1010 бит производит вставку 8 бит и 16 входных бит данных для выработки 24 бит Ik данных. Рекурсивный системный составной кодер, который вырабатывает оконечные биты, используется для составного кодера. В этом случае первый составной кодер вырабатывает в общем 32 бита данных, которые состоят из 24 закодированных бит данных, 4 оконечных бит и закодированных данных 4 оконечных бит. При выводе закодированных бит данных входные биты Ik данных 8 вставленных бит прокалываются для вставки оставшихся 8 первых бит контроля четности в положениях проколотых бит.

В процессе декодирования выходные значения мультиплексора 1050 демультиплексируются в части бит данных, первой части бит контроля четности и второй части бит контроля четности, в котором часть бит данных прокалывается со значением "-5" в части вставки бит. Такие обработанные биты данных декодируются с помощью существующего декодера (смотри Клауди Берроу, Алаин Главиюкс и Панья Титмашима "Кодирование и декодирование с исправлением ошибок в ближнем пределе Шеннона: турбокоды (I)" (See Claude Berrou, Alain Glavieux and Punya Thitmajshuma "Near Shannon Limit Error-Correction Coding and Decoding: Turbo-Codes (1)").

Хотя предполагается, что в этом варианте осуществления используются нулевые биты в качестве вставляемых бит, также можно использовать закодированные биты или биты данных, предварительно определенные приемником.

В этом третьем варианте осуществления второй составной код может также завершать имеющийся оконечный бит, который вырабатывается так же, как и первый составной код. И вторые оконечные биты, и оконечные биты четности также вставляются в положение удаленных бит. Первый составной код и второй составной код выводят биты четности, и оконечные биты, и оконечные биты четности. Вставленные биты могут быть частью первого выхода составного кода и частью второго выхода составного кода.

Четвертый вариант осуществления

Кодер согласно четвертому варианту осуществления настоящего изобретения выполняет функцию завершения посредством вставки специфических бит данных в предварительно определенные положения для вставки бит без выработки оконечных бит. Специфическое число закодированных бит вместо вставленных бит повторяют во вставленных положениях. В этом образцовом варианте осуществления один кадр включает в себя 16 бит данных, и восемь известных бит, которые являются нулевыми битами, вставляются в кадр в положения бит, имеющих более высокую вероятность ошибок. В этом случае положения известных бит определяют путем экспериментального обнаружения положения, где происходит наибольшее число ошибок во время декодирования закодированных данных. Кроме того, предполагается, что соответствующие составные кодеры имеют 1/3 скорость кодирования.

В этом варианте осуществления положения, имеющие более высокую вероятность ошибок во время декодирования, определяют экспериментальным образом, когда 24-битовые данные кадра (16 бит данных кадра плюс 8 известных бит) кодируют с использованием турбокодера, имеющего 1/3 скорость кодирования. Определяют восемь положений бит, которые имеют относительно высокую вероятность ошибок, и в определенных положениях вставляют известные биты в биты данных. После кодирования последние 4 бита из соответствующих бит контроля четности повторяют для вставки повторенных бит в положения для вставки бит вместо известных бит. В этом случае кодер узнает положения вставленных бит контроля четности при декодировании закодированных данных кадра, в которых вставлены специфические коды. Для кодирования биты рекомбинируют на биты четности.

Когда известные биты являются нулевыми битами (на практике "О" биты передаются в виде "-1"), нулевые биты во вставленных положениях изменяются на достаточно отрицательное значение (например, -5) перед декодированием для того, чтобы увеличить надежность. Таким способом, декодер декодирует биты, узнавая при этом восемь бит, которые представляют собой 1/3 24 бит, таким образом повышая рабочие характеристики. В этом случае качество характеристик увеличивается, так как кадр становится короче.

Фиг. 4 изображает схему, иллюстрирующую турбокодер, имеющий устройство для вставки бит, для вставки известных бит согласно четвертому варианту осуществления настоящего изобретения. Устройство для вставки 1410 бит включает в себя генератор бит для выработки известных бит с помощью обработки входных бит данных и вырабатывает биты данных в блоке кадра с помощью вставки известных бит, которые вырабатываются генератором бит в предварительно определенных положениях бит. Первый составной кодер 1420 кодирует биты данных, которые выводятся из устройства вставки 1410 бит. Перемежитель 1430 выполняет перемежение бит данных в блоке кадра, которые выводятся из устройства вставки 1410 бит в соответствии с предварительно определенным правилом для того, чтобы изменять размещение (или последовательность) бит данных. В образцовом варианте осуществления диагональный перемежитель используется для перемежителя 1430. Второй составной кодер 1440 кодирует биты данных в блоке кадра, которые выводятся из перемежителя 1430. Рекурсивный системный сверточный кодер можно использовать для первого и второго составных кодеров 1420 и 1440. Мультиплексор 1450 мультиплексирует выходные сигналы устройства вставки 1410 бит, первого составного кодера 1420 и второго составного кодера 1440 под управлением неизображенного контроллера. В этом случае устройство для вставки 1410 бит выводит биты Ik данных, первый составной кодер 1420 - первые биты Р1k контроля четности и второй составной кодер 1440 - вторые биты Р2k контроля четности.

Фиг.15А изображает схему, иллюстрирующую устройство для вставки 1410 бит в турбокодере (фиг.14). На фиг.15А генератор 1530 бит вырабатывает известные биты, которые будут вводиться в биты данных. В этом случае предполагается, что известные биты являются нулевыми битами. Задержки 1512-1526, которые могут состоять из элементов памяти, таких как триггеры, могут иметь структуру регистров последовательного сдвига для сдвига входных бит данных в соответствии с тактовым сигналом бит. Коммутатор 1532 коммутируется для выбора выходов задержек 1512-1526 под управлением неизображенного контроллера. К тому же коммутатор 1532 коммутируется на выходе следующей задержки в положениях, где известные биты, которые выводятся из генератора 1530 бит, вставляются в биты данных под управлением неизображенного контроллера. То есть коммутатор 1532 выбирает биты данных, которые задержаны на один бит, когда выбранный известный бит вставляется в биты данных. Коммутатор 1532 можно реализовать с помощью мультиплексора. Коммутатор 1534 коммутируется на выходах генератора 1530 бит и коммутатора 1532 для выработки бит Ik данных под управлением неизображенного контроллера. Коммутатор 1534 производит вставку известных бит в предварительно определенные положения бит данных с помощью контроллера.

Ниже приводится описание операции вставки известных бит в биты данных со ссылкой на фиг. 15А. Входные биты данных задерживаются с помощью задержек 1512-1526 в соответствии с тактовым сигналом бит. В исходном состоянии коммутатор 1532 выбирает входные биты данных, и коммутатор 1534 подсоединяется к коммутатору 1532. Затем входные биты данных выводятся через коммутаторы 1532 и 1534. Между тем, если положения для вставки бит определено, коммутатор 1532 подсоединяется к выходу задержки 1512, и коммутатор 1534 подсоединяется к выходу генератора 1530 бит под управлением контроллера. В результате путь для бит данных отсекается и нулевой бит, который выводится из генератора 1530 бит, вставляется в соответствующие положения бит. В случае, когда биты данных необходимо постоянно выводить после вставки нулевого бита, коммутатор 1534 подсоединяется к коммутатору 1532 контроллера. То есть, так как бит данных с задержкой на один бит выбирается после вставки нулевого бита, нулевой бит можно вставить в предварительно определенное положение без потери бита данных.

Нулевые биты вставляются в биты данных для одного кадра путем повторения этого процесса. После получения бит данных для следующего кадра после вставки нулевых бит коммутатор 1532 подсоединяется ко входному узлу бит данных и затем вышеописанный процесс повторяется снова. В случае, где биты данных кодируются для связи, вероятность ошибок является относительно высокой в задней части кадра. Соответственно, положение, где вставляются нулевые биты, которые выводятся из генератора 1530, можно в большей степени разместить в задней части кадра.

Биты данных, которые выводятся из устройства вставки 1410 бит, подаются в первый составной кодер 1420 и перемежитель 1430. Чередующиеся биты данных в блоке кадра, которые выводятся из перемежителя 1430, кодируют с помощью второго составного кодера 1440. Фиг.15В иллюстрирует структуру первого и второго составных кодеров 1420 и 1440 (фиг.14). Как изображено на чертеже, первый и второй составные кодеры 1420 и 1440 являются рекурсивными системными сверточными кодерами. Кроме того, составные кодеры 1420 и 1440 имеют структуру, которая не вырабатывает оконечные биты (фиг.15В).

Когда первый составной кодер 1420 кодирует биты данных, которые выводятся из устройства вставки 1410 бит, перемежитель 1430 выполняет перемежение бит данных, которые выводятся из устройства вставки 1410 бит, и второй составной кодер 1440 кодирует чередующиеся биты данных, которые выводятся из перемежителя 1430.

Мультиплексор 1450 затем мультиплексирует выходные сигналы устройства вставки 1410 бит, первого составного кодера 1420 и второго составного кодера 1430 под управлением неизображенного контроллера.

На фиг.16 мультиплексор 1450 последовательно получает 24 бита Ik данных, 24 первых бита Сk контроля четности и 24 вторых бита Dk контроля четности, сохраняет первые 24 бита в соответствующих битах в соответствующих задержках и сохраняет оставшиеся четыре бита соответствующих битов четности в соответствующих задержках. Коммутаторы 1601-1640 управляются с помощью неизображенного контроллера. Кроме того, каждая задержка 1621-1625 имеет структуру каскадных элементов памяти и биты, которые вводятся в задержки, сохраняются до тех пор, пока не завершится процесс задержки.

После завершения процесса задержки коммутатор 1640 подсоединяется к коммутатору 1630 и коммутатор 1630 подсоединяется к задержке 1621. Поэтому выходной сигнал задержки 1621 выводится через коммутаторы 1630 и 1640. При выводе одного бита данных, который сохраняется в задержке 1621, коммутатор 1630 подсоединяется к задержке 1623, поддерживая соединение с коммутатором 1640. Затем один из оставшихся бит данных, которые сохраняются в задержке 1623, выводится через коммутаторы 1630 и 1640. То есть бит данных, который сохраняется в задержке 1621, прокалывается и затем бит данных, который сохраняется в задержке 1623, вставляется в проколотое положение. После этого коммутатор 1630 подсоединяется снова к задержке 1621, непрерывно поддерживая соединение с коммутатором 1640. Повторяя вышеописанный процесс 4 раза, биты данных, которые сохраняются в задержке 1621, прокалываются и затем оставшиеся 4 первых бита четности, которые сохраняются в задержке 1623, вставляются в проколотые положения.

Впоследствии коммутатор 1630 подсоединяется к задержке 1621, поддерживая соединение с коммутатором 1640. Затем выходной сигнал задержки 1621 выводится через коммутаторы 1630 и 1640. При выводе одного бита данных, который сохраняется в задержке 1621, коммутатор 1630 подсоединяется к задержке 1625, поддерживая соединение с коммутатором 1640. Затем один из оставшихся 4 вторых бит контроля четности, которые сохраняются в задержке 1625, выводятся через коммутаторы 1630 и 1640. После этого коммутатор 1630 подсоединяется снова к задержке 1621, непрерывно поддерживая соединение с коммутатором 1640. Повторяя вышеописанный процесс 4 раза, биты данных, которые сохраняются в задержке 1621, прокалываются и затем оставшиеся четыре вторых бита четности, которые сохраняются в задержке 1625, вставляются в проколотые положения.

С помощью вышеописанной процедуры 8 вставленных бит из 24 бит данных, которые сохраняются в задержке 1621, прокалываются и затем оставшиеся 4 первых бита четности, которые сохраняются в задержке 1623, и оставшиеся 4 вторых бита четности, которые сохраняются в задержке 1625, поочередно вставляются в проколотые положения, таким образом обеспечивая вывод 24 бита. Соответственно, мультиплексор 1450 прокалывает 8 вставленных бит из бит Ik данных, которые выводятся из устройства вставки 1410 бит, и вставляет 8 бит контроля четности в проколотые положения вставки, таким образом обеспечивая вывод 24 бита данных.

После завершения вышеописанного процесса коммутатор 1640 подсоединяется к задержке 1622. Затем выводятся 24 первых бита Ck контроля четности, которые сохраняются в задержке 1622. После этого коммутатор 1640 подсоединяется к задержке 1624 для вывода 24 вторых бита Dk контроля четности, которые сохраняются в задержке 1624.

Фиг.17 изображает временную диаграмму турбокодера (фиг.14) согласно четвертому варианту осуществления настоящего изобретения. На фиг.17 в интервале Т1 устройство для вставки 1410 бит выполняет вставку нулевых бит в кадр в предварительно определенных положениях бит для выработки бит Ik данных (смотри 1711). В интервале Т2 биты Ik данных с нулевым введенным битом одновременно подаются в мультиплексор 1450, первый составной кодер 1420 и перемежитель 1430. Затем первый составной кодер 1420 кодирует биты Ik данных с нулевым введенным битом для выработки первых закодированных бит Сk данных, которые являются первыми битами четности (смотри 1712), и перемежитель 1430 выполняет перемежение бит Ik данных с нулевым введенным битом в соответствии с предопределенным правилом (смотри 1713). После этого в интервале ТЗ мультиплексор 1450 задерживает биты Ik данных, которые выводятся из устройства вставки 1410 бит с помощью одного периода кадра, первый составной кодер 1420 вводит первые закодированные биты Ck данных в мультиплексор 1450, и второй составной кодер 1440 кодирует чередующиеся биты Ik данных, которые выводятся из перемежителя 1430 для выработки вторых закодированных бит Dk данных, которые являются вторыми битами четности. После того как второй составной кодер 1440 вырабатывает вторые биты Dk контроля четности, мультиплексор 1450 мультиплексирует биты Ik данных, первые биты Сk контроля четности и вторые биты Dk контроля четности в интервале Т4.

Хотя на фиг. 17 показан пример параллельной обработки бит Ik данных, первые биты Ck контроля четности и вторые биты Dk контроля четности, можно также последовательно выводить выходные сигналы устройства вставки 1410 бит, первого составного кодера 1420 и второго составного кодера 1440 в порядке выработки.

Как можно оценить из предыдущего описания, в рекурсивном системном турбокодере согласно четвертому варианту осуществления соответствующие составные кодеры не вырабатывают оконечные биты для завершения и вместо этого вставляют известные биты (то есть нулевые биты) в положения бит, имеющие более высокую вероятность ошибок.

Пятый вариант осуществления

Кодер согласно пятому варианту осуществления настоящего изобретения производит вставку бит, имеющих специфическую логику в битах данных, в предварительно определенных положениях для вставки бит, имеющих более высокую вероятность появления ошибок. Составные кодеры кодируют биты данных со вставленными битами и вырабатывают оконечные биты, которые будут добавляться в закодированные биты данных. То есть кодер согласно пятому варианту осуществления выполняет функцию завершения с помощью вставки бит и добавления оконечных бит.

Число вставленных бит определяется с помощью числа входных бит данных кодера, числа выходных символов кода, длины кодового ограничения и скорости передачи кода. То есть, когда число входных бит данных кодера равно N, число выходных символов кода кодера составляет М, длина кодового ограничения равна L и скорость передачи кода составляет 1/К, число вставленных бит равно (M-KN-2(K-1)(L-1))/(К-1). Из этого следует, что, когда число входных бит данных кодера равно 16, число выходных символов кода равно 72, длина кодового ограничения равна 5 и скорость передачи кода равна 1/3, число вставленных бит составляет 4.

Действительно, так как число вставленных бит увеличивается, кодер имеет повышенные характеристики. Кодер согласно этому варианту осуществления может максимально улучшить свои характеристики с помощью вставки известных бит, насколько это возможно, с помощью заданного числа входных бит данных и числа выходных символов кода. В этом варианте осуществления, когда используется 12 вставленных бит и биты данных передаются после кодирования, можно улучшить характеристики кодера с помощью передачи только закодированных символов без передачи вставленных бит для максимальной вставки бит.

Фиг. 18 изображает схему, иллюстрирующую кодер согласно пятому варианту осуществления настоящего изобретения. На фиг.18 устройство для вставки 1810 бит получает 16 входных бит. В этом случае устройство для вставки 1810 бит имеет структуру, подобную устройству вставки 1410 бит (фиг.15А) за исключением того, что он включает в себя 4 памяти, как показано на фиг.19. Устройство для вставки 1810 бит производит вставку 4 нулевых бит в 4 предварительно определенные положения бит в кадре, который имеет более высокую вероятность ошибок, под управлением неизображенного контроллера. Структура устройства вставки 1810 бит показана на фиг.19.

В этом варианте осуществления устройство для вставки 1810 бит выводит 20 бит Ik данных, которые подаются в общем в мультиплексор 1850, первый составной кодер 1820 и перемежитель 1830. Чередующиеся биты Ik данных, которые выводятся из перемежителя 1830, подаются во второй составной кодер 1840. В этом случае первый составной кодер 1820 является рекурсивным системным составным кодером (фиг. 20), который имеет структуру для выработки оконечных бит, которые будут добавляться к закодированным битам. Кроме того, кодер, показанный на фиг.18В, имеющий структуру, которая не вырабатывает оконечные биты для завершения, используется для второго составного кодера 1840.

Со ссылкой на фиг.20 описывается работа первого составного кодера 1820. Для кодирования коммутатор 2011 подсоединяет входной узел к логическому элементу 2031 исключающее ИЛИ, коммутатор 2013 поддерживает состояние "выключено" и коммутатор 2015 подсоединяется к логическому элементу 2035 исключающее ИЛИ. Затем 20 бит Ik данных последовательно подаются в задержки 2021-2027 через коммутатор 2011 и логический элемент 2031 исключающее ИЛИ, и логический элемент 2035 исключающее ИЛИ выводит закодированные биты данных. Когда все биты Ik данных кодируются с помощью задержек 2021-2027 и логического элемента 2035 исключающее ИЛИ тем же самым способом, коммутатор 2021 подсоединяет логический элемент 2033 исключающее ИЛИ к логическому элементу 2031 исключающее ИЛИ для завершения. Затем нулевые биты вырабатываются с помощью операции исключающее ИЛИ выходных сигналов, которые подаются обратно по обратной связи, которые сохраняются в задержках 2021-2027 и выводятся через коммутатор 2015. В этом случае нулевые значения, которые сохраняются в задержках 2021-2027, становятся оконечными битами и выводятся через коммутатор 2015. Число оконечных бит соответствует числу задержек в составном кодере 1820. На фиг.20 составной кодер 1820 вырабатывает четыре оконечных бита в кадр и также вырабатывает 4 оконечных бита четности (закодированные биты для соответствующих оконечных бит).

Соответственно, первый составной кодер 1820 вырабатывает 20 первых бит Ck четности и после обработки последних бит данных (то есть 20-го бита данных), подсоединяет коммутатор 2011 к логическому элементу 2033 исключающее ИЛИ, коммутатор 2013 к коммутатору 2011 и коммутатор 2015 к коммутатору 2013, при этом тот же самый процесс повторяется четыре раза для выработки 4 оконечных бит Tk. Следуя этой процедуре, 24 первых бита Сk контроля четности и 4 оконечных бита выводятся в мультиплексор 1850. Коммутатор 1860 коммутируется в перемежителе 1830 для подачи оконечных бит Тk в перемежителе 1830 и коммутатор 1870 подсоединяется к мультиплексору 1850 для подачи оконечных бит Tk в мультиплексор 1850.

Кроме того, перемежитель 1830 выполняет перемежение 20 бит Ik данных, которые выводятся из устройства для вставки 1810 бит, и четыре оконечные бита, которые выводятся из первого составного кодера 1820 и обеспечивает подачу 24 чередующихся бита данных во второй составной кодер 1840. Второй составной кодер 1840 затем кодирует чередующиеся биты данных тем же самым способом, как и первый составной кодер 1440 (фиг.14), для выработки 24 вторых бит Dk контроля четности, которые подаются в мультиплексор 1850.

Чередующиеся биты данных в блоке кадра, которые выводятся из перемежителя 1830, кодируются с помощью второго составного кодера 1840, который имеет ту же самую структуру, как и кодер, показанный на фиг.18В. Второй составной кодер 1840 является рекурсивным системным сверточным кодером (фиг.15В). Кроме того, второй составной кодер 1840 имеет структуру, которая не вырабатывает оконечные биты.

Мультиплексор 1850 затем выполняет прокалывание 4 вставленных бита бит Ik данных и вводит 4 первых бита Сk контроля четности в проколотое положение, а также выборочно выводит оставшиеся 24 первых бита Ck контроля четности и 24 вторых бита Dk контроля четности. Вставленные 4 бита могут быть первыми составными закодированными оконечными битами или оконечными битами контроля четности.

Фиг. 21 изображает схему, иллюстрирующую мультиплексор 1850. На фиг.21 мультиплексор 1850 первым получает 20 бит Ik данных, которые выводятся из устройства вставки 1810 бит. Задержка 2122 в мультиплексоре 1850 затем сохраняет полученные 20 бит Ik данных.

После этого мультиплексор 1850 сохраняет 24 первых бита Ck контроля четности, которые выводятся из первого составного кодера 1820 в задержке 2124, и сохраняет 4 оконечных бита Tk, которые выводятся из первого составного кодера 1820 в задержке 2122. Затем мультиплексор 1850 сохраняет 24 вторых бита Dk контроля четности, которые выводятся из второго составного кодера 1840 в задержке 2126.

Каждая задержка 1222-1228 состоит из каскадных элементов памяти и сохраняет соответствующие входные биты до тех пор, пока не завершится вышеописанный процесс задержки.

После выполнения вышеописанного процесса задержки коммутатор 2101 подсоединяется к задержке 2122 для вывода бит, сохраненных в задержке 2122. Впоследствии коммутатор 2101 подсоединяется к задержке 2124 для вывода бит, сохраненных в задержке 2124. После этого коммутатор 2101 подсоединяется к задержке 2126 для вывода бит, сохраненных в задержке 2126.

Шестой вариант осуществления

Кодер согласно шестому варианту осуществления настоящего изобретения работает так же, как и в пятом варианте осуществления, и выполняет прокалывание бит данных для вставки известных бит в проколотые положения вставленных бит, и 4 оконечных бита четности из первого составного кодера повторно передают в положения. Фиг.22 изображает схему, иллюстрирующую кодер согласно шестому варианту осуществления настоящего изобретения, в котором последовательность операций мультиплексора 2250 является той же самой, как и в пятом варианте осуществления.

На Фиг. 23 мультиплексор 2250 первым получает 20 бит Ik данных, которые выводятся из устройства вставки 2210 бит. Задержка 2321 в мультиплексоре 2250 затем сохраняет полученные 20 бит Ik данных. После этого мультиплексор 2250 сохраняет 24 первых бита Сk контроля четности, которые выводятся из первого составного кодера 2220 в задержке 2322, сохраняет последние 4 первых бита четности в задержке 2323 и сохраняет 4 оконечных бита Тk, которые выводятся из первого составного кодера 2220 в задержке 2321. Затем мультиплексор 2250 сохраняет 24 вторых бита Dk контроля четности, которые выводятся из второго составного кодера 2240 в задержке 2324.

Каждая задержка 2322-2328 состоит из каскадных элементов памяти и сохраняет соответствующие входные биты до тех пор, пока не завершится вышеописанный процесс задержки.

После выполнения вышеописанного процесса задержки коммутатор 2340 подсоединяется к коммутатору 2330 и коммутатор 2330 подсоединяется к задержке 2321. Таким образом, выходной сигнал задержки 2321 выводится через коммутаторы 2330 и 2340. Когда выводится один бит данных, который сохраняется в задержке 2321, коммутатор 2330 подсоединяется к задержке 2323, поддерживая соединение с коммутатором 2340. Затем один из оставшихся первых битов четности, которые сохраняются в задержке 2323, выводятся через коммутаторы 2330 и 2340. То есть бит данных, который сохраняется в задержке 1121, прокалывается и затем первый бит контроля четности, который сохраняется в задержке 2323, вставляется в проколотое положение. После этого коммутатор 2330 подсоединяется снова к задержке 2321, поддерживая соединение с коммутатором 2340. Вышеописанная операция повторяется 4 раза для прокалывания бит данных, которые сохраняются в 2321, и производится вставка в проколотые положения оставшихся четырех первых бит контроля четности, которые сохраняются в задержке 2323.

Таким же способом 24 бита Ik данных, которые сохраняются в задержке 2321, прокалываются для вставки в проколотые положения оставшихся 4 первых бит контроля четности, которые сохраняются в задержке 2323, таким образом обеспечивая вывод 24 бит. В результате мультиплексор 2250 выполняет прокалывание 24 бит Ik данных, которые выводятся из устройства вставки 2210 бит, для вставки 4 бит контроля четности в проколотые положения для вставки бит, таким образом обеспечивая вывод 24 бит данных.

После этого коммутатор 2340 подсоединяется к выходу задержки 2322. Затем 24 первых бита Сk контроля четности, которые сохраняются в задержке 2322, выводятся через коммутатор 2340. Затем коммутатор 2340 коммутируется в задержке 2324 для вывода 24 вторых бит Dk контроля четности, которые сохраняются в задержке 2324.

Седьмой вариант осуществления

Кодер согласно седьмому варианту осуществления настоящего изобретения работает так же, как и в пятом варианте осуществления, и прокалывает биты данных для вставки известных бит в проколотые положения для вставки бит, и 4 оконечных бита четности из второго составного кодера повторно передаются в положения. Фиг. 24 изображает схему, иллюстрирующую кодер согласно седьмому варианту осуществления настоящего изобретения, в котором последовательность операций перед мультиплексором 2450 является той же самой, как и в пятом варианте осуществления.

На фиг. 24 мультиплексор 2450 первым получает 20 бит Ik данных, которые выводятся из устройства вставки 2410 бит. Задержка 2521 в мультиплексоре 2450 затем сохраняет полученные 20 бит Ik данных. После этого мультиплексор 2450 сохраняет 24 первых бита Сk контроля четности, которые выводятся из первого составного кодера 2420 задержки 2522, и сохраняет 4 оконечных бита Tk, которые выводятся из первого составного кодера 2420 задержки 2521. Затем мультиплексор 2450 получает 24 вторых бита Dk контроля четности, которые выводятся из второго составного кодера 2440. Мультиплексор 2450 сконструированный так, как показано на фиг.25, мультиплексирует биты Ik данных и биты Сk и Dk контроля четности, которые выводятся соответственно из устройства для вставки 2410 бит, первого составного кодера 2420 и второго составного кодера 2440.

Фиг. 25 изображает схему, иллюстрирующую мультиплексор 2450 согласно седьмому варианту осуществления настоящего изобретения.

На фиг. 25 задержка 2523 сохраняет вторые биты Dk контроля четности, и задержка 2524 сохраняет последние 4 бита вторых бит Dk контроля четности. Коммутатор 2501 управляется с помощью неизображенного контроллера. Кроме того, каждая задержка 2521-2524 состоит из каскадных элементов памяти и сохраняет соответствующие входные биты до тех пор, пока не завершается вышеописанный процесс задержки.

После завершения процесса задержки коммутатор 2540 подсоединяется к коммутатору 2530 и коммутатор 2530 подсоединяется к задержке 2521. Таким образом, выходной сигнал задержки 2521 выводится через коммутаторы 2530 и 2540. Когда выводится один бит данных, который сохраняется в задержке 2521, коммутатор 2540 подсоединяется к задержке 2524 для вывода одного из последних 4 бит контроля четности, которые сохраняются в задержке 2524. То есть бит данных прокалывается, и затем второй бит контроля четности, который сохраняется в задержке 2524, вводится в проколотое положение для вставки бит. После этого коммутатор 2530 подсоединяется снова к задержке 2521, поддерживая соединение с коммутатором 2540. Вышеописанная операция повторяется 4 раза для прокалывания бит данных, которые сохраняются в 2521, и производится вставка в проколотые положения для вставки бит последних 4 бит контроля четности, которые сохраняются в задержке 2524.

Тем же самым способом 24 бита Ik данных, которые сохраняются в задержке 2521, прокалываются поочередно для вставки последних 4 вторых бита четности, которые сохраняются в задержке 2524, таким образом обеспечивая вывод 24 бит. В результате, мультиплексор 2450 прокалывает 24 бита Ik данных, которые выводятся из устройства вставки 2410 бит для вставки 4 вторых бит контроля четности в проколотые положения для вставки бит, таким образом обеспечивая вывод 24 бит данных.

После этого коммутатор 2540 подсоединяется к выходу задержки 2522. Затем 24 первых бита Ck контроля четности, которые сохраняются в задержке 2522, выводятся через коммутатор 2540. Затем коммутатор 2540 коммутируется в задержке 2524 для вывода 24 вторых бит Dk контроля четности, которые сохраняются в задержке 2524.

Восьмой вариант осуществления

Кодер согласно восьмому варианту осуществления настоящего изобретения производит вставки бит, имеющие специфическую логику в битах данных в положениях бит, имеющих более высокую вероятность появления ошибок. Составной кодер кодирует биты данных со вставленными битами и независимо или внутренним образом вырабатывает оконечные биты, которые будут добавляться в закодированные биты данных. То есть кодер согласно этому варианту осуществления выполняет функцию завершения с помощью вставки бит и добавления оконечных бит.

Фиг.26 изображает схему, иллюстрирующую кодер согласно восьмому варианту осуществления настоящего изобретения. На фиг.26 устройство для вставки 2610 бит получает 16 входных бит. В этом случае устройство для вставки 2610 бит имеет структуру, подобную устройству вставки 1810 бит (фиг.19). Устройство для вставки 2610 бит производит вставку 4-х нулевых бит в 4-х положениях бит данных в кадре, которые имеют более высокую вероятность ошибок, под управлением неизображенного контроллера. Соответственно, в этом варианте осуществления устройство для вставки 2610 бит выводит 20 бит Ik данных, которые в общем подаются в мультиплексор 2650, первый составной кодер 2620 и перемежитель 2630. Кроме того, чередующиеся биты Ik данных, которые выводятся из перемежителя 2630, подаются во второй составной кодер 2640. В этом случае первый составной кодер 2620 и второй составной кодер 2640 являются рекурсивными системными составными кодерами (фиг.20), которые вырабатывают оконечные биты, которые добавляются к закодированным битам данных.