Изобретение относится к устройству и способу сегментации и повторной сборки трафика с постоянной битовой скоростью в сети с асинхронным режимом переноса информации (АТМ) и касается, в частности, устройства и способа сегментации и повторной сборки трафика с постоянной битовой скоростью, в которых выполняются операция преобразования трафика с постоянной битовой скоростью, заключенного в кадре сигнала Т1 (северо-американского стандарта со скоростью передачи 1544 кбит/с) / Е1 (европейского стандарта со скоростью передачи 2048 кбит/с), в ячейку АТМ и обратная ей операция, а именно, операция преобразования ячейки АТМ в трафик с постоянной битовой скоростью и транспортировка трафика с постоянной битовой скоростью в кадре сигнала Т1/Е1.

Известные технические решения

Обычно известные системы сегментации трафика с постоянной битовой скоростью и его повторной сборки требуют использования ряда модулей, чтобы получить эффективное соединение между телефонной сетью общего пользования (ТФОП) и сетью АТМ. По этой причине такие известные системы сегментации и повторной сборки трафика с постоянной битовой скоростью увеличивают стоимость и объем оборудования.

Сущность изобретения

Следовательно, целью изобретения является создание устройства и способа сегментации и повторной сборки трафика с постоянной битовой скоростью в сети АТМ, в котором достигается стандартизированный и простой переход между различными режимами работы и тем самым уменьшается стоимость и объем оборудования.

Для достижения этой цели данное изобретение предусматривает устройство для сегментации и повторной сборки трафика с постоянной скоростью передачи битов в сети с асинхронным режимом переноса информации, содержащее модуль формирования ячейки АТМ для считывания значения, содержащегося в поступающем извне кадре сигнала Т1/Е1, и формирования ячейки АТМ на основе считанного значения и модуль формирования кадра сигнала Т1/Е1 для считывания поступающей извне ячейки АТМ и формирования кадра сигнала Т1/Е1 на основе считанной ячейки АТМ.

В соответствии с представленным изобретением модуль формирования ячейки АТМ содержит блок синхронизации состояния для приема внешних сигналов синхронизации (8 кГц, N•8 кГц и CLK), образующий при этом конечный автомат и множество счетчиков, последовательно-параллельный преобразователь для приема внешних сигналов синхронизации (N•8 кГц и N•8•8 кГц) и последовательных данных из приемопередатчика сигнала Т1/Е1 и для преобразования принятых последовательных данных в 8-разрядные параллельные данные, блок преобразования данных временного интервала в ячейку, предназначенный для считывания параллельных данных из последовательно-параллельного преобразователя синхронно с сигналом синхронизации (N•8 кГц), подаваемым на него через блок синхронизации состояния, выделения данных временного интервала входного кадра сигнала Т1/Е1, определения, должны или нет выделенные данные быть отброшены, на основе считывания информации управления из буфера передаваемых ячеек, записи выделенных данных в соответствующий буфер передаваемых ячеек, если выделенные данные являются полезными, и записи идентификатора соответствующего буфера ячейки в очередь полных ячеек, когда ячейки АТМ полностью накоплены в соответствующем буфере передаваемых ячеек, блок управления передаваемой ячейкой для проведения поиска в полной очереди ячеек в ответ на сигнал, характеризующий состояние конечного автомата, образованного блоком синхронизации состояния, и выполнения посредством этого записи АТМ ячеек (CELL_ WR и CELL_DATA) соответствующего буфера передаваемых ячеек во внешний буфер ячеек, блок доступа к центральному процессору для управления доступом к центральному процессору и буферу передаваемых ячеек в ответ на сигнал, характеризующий состояние конечного автомата, образованного блоком синхронизации состояния, и приема посредством этого сигналов (CPU_CS, CPU_RW и CPU_ ADDR) от соответствующих центральных процессоров при обмене данными центрального процессора (CPU_DATA) с соответствующими центральными процессорами и блок доступа к буферу передаваемых ячеек для управления доступом к буферу передаваемых ячеек для блока преобразования данных временного интервала в ячейку, блока управления передаваемой ячейкой и блока доступа к центральному процессору в соответствии с сигналом, характеризующим состояние конечного автомата, образованного блоком синхронизации состояния, и посредством этого подачи сигналов буфера передаваемых ячеек (TCB_CS, TCB_RW и TCB_ADDR) в буфер передаваемых ячеек при обмене данными буфера передаваемых ячеек (TCB_ DATA) с буфером передаваемых ячеек.

В соответствии с настоящим изобретением модуль формирования кадра Т1/Е1 содержит блок синхронизации состояния для приема внешних сигналов синхронизации (8 кГц, N•8 кГц и CLK), образующий при этом конечный автомат и множество счетчиков, блок управления принимаемой ячейкой для считывания входной ячейки АТМ (CELL_DATA) в ответ на сигнал, характеризующий состояние конечного автомата в блоке синхронизации состояния, с определением посредством этого, является полезной или нет входная ячейка АТМ, и записи считанных данных (CELL_ RD) в виде ячейки АТМ в соответствующий буфер принимаемых ячеек, если входная ячейка АТМ является полезной, блок преобразования ячейки в данные временного интервала для считывания буферов принимаемых ячеек синхронно с сигналом синхронизации (N•8 кГц), подаваемым на него через блок синхронизации состояния, и для формирования параллельных данных, соответствующих считанным данным, для записи считанных данных в соответствующий временной интервал кадра сигнала Т1/Е1, который должен быть сформирован, параллельно-последовательный преобразователь для приема внешних сигналов синхронизации (N•8 кГц и N•8•8 кГц), преобразования параллельных данных, полученных от блока преобразования ячейки в данные временного интервала, в последовательные данные, и записи последовательных данных в соответствующий временной интервал кадра Т1/Е1, блок доступа к центральному процессору для управления доступом к центральному процессору и к буферу передаваемых ячеек в ответ на сигнал, характеризующий состояние конечного автомата, образованного блоком синхронизации состояния, для приема посредством этого сигналов центрального процессора (CPU_CS, CPU_RW и CPU_ADDR) от соответствующих центральных процессоров при обмене данными центрального процессора (CPU_DATA) с соответствующими центральными процессорами и блок доступа к буферу принимаемых ячеек для управления доступом к буферу принимаемых ячеек для блока управления принимаемой ячейкой, блока доступа к центральному процессору и блока преобразования ячейки в данные временного интервала в соответствии с сигналом, характеризующим состояние конечного автомата, образованного блоком синхронизации состояния, и посредством этого подачи сигналов буфера принимаемых ячеек (RCB_CS, RCB_RW и RCB_ADDR) в буфер принимаемых ячеек при обмене данными буфера принимаемых ячеек (RCB_DATA) с буфером принимаемых ячеек.

Краткое описание чертежей

Другие цели и аспекты изобретения станут очевидными из следующего подробного описания форм осуществления изобретения, приводимого вместе с чертежами.

На фиг.1 показана блок-схема, иллюстрирующая действующее соединение между сетью АТМ и телефонной сетью общего пользования, для которого применяется настоящее изобретение;

на фиг.2 показана блок-схема, иллюстрирующая устройство для сегментации и повторной сборки трафика с постоянной битовой скоростью в сети АТМ в соответствии с настоящим изобретением;

фиг. 3 является схемой, показывающей шесть состояний конечного автомата, образованного в устройстве на фиг.2;

на фиг. 4 показана временная диаграмма внешних сигналов, подаваемых на устройство, показанное на фиг.2;

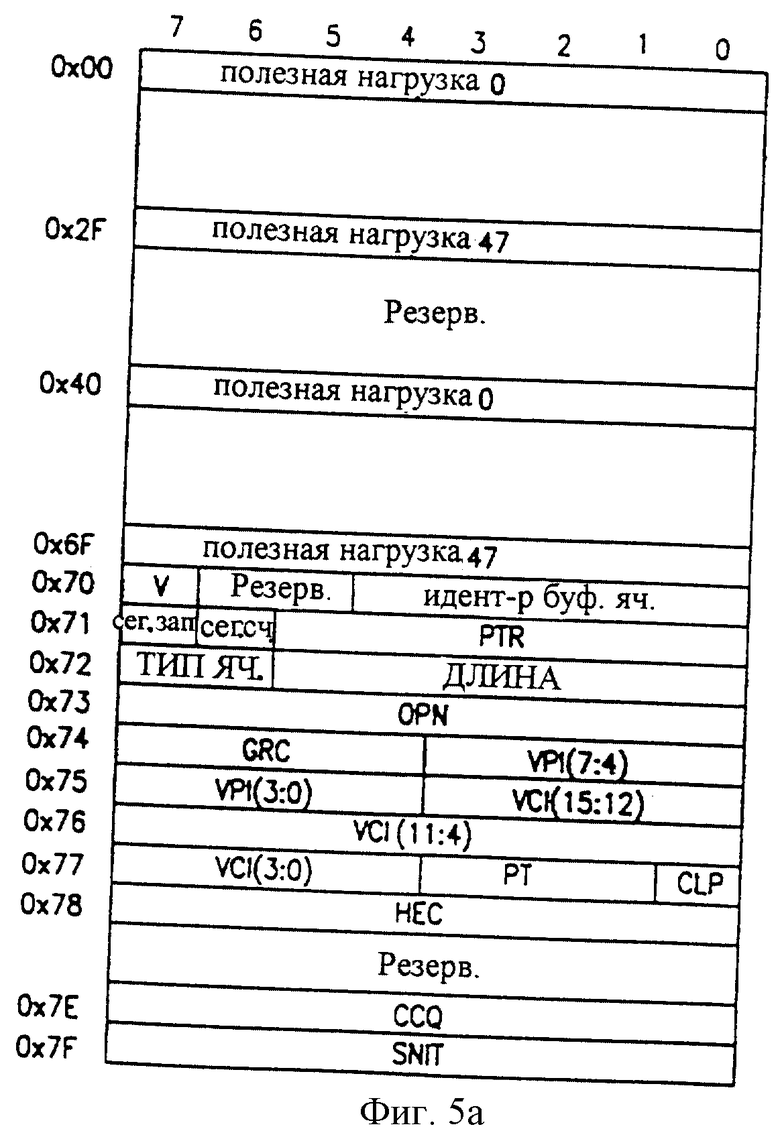

на фиг. 5a, 5b - схемы, иллюстрирующие конфигурацию блока передаваемой ячейки, которая соответствует структуре ячейки АТМ, используемой в устройстве на фиг.2;

фиг. 6а, 6b - схемы, иллюстрирующие конфигурацию блока принимаемой ячейки, которая соответствует структуре ячейки АТМ, используемой в устройстве на фиг.2;

на фиг. 7 показана схема, иллюстрирующая всю карту распределения памяти для буферов передаваемых ячеек, используемых в устройстве на фиг.2;

на фиг. 8 показана схема, иллюстрирующая всю карту распределения памяти для буферов принимаемых ячеек, используемых в устройстве на фиг.2;

фиг.9 представляет собой схему, которая поясняет запись центральным процессором таблицы индексов последовательных номеров в карту, показанную на фиг.7 или 8;

на фиг.10 показана схема, поясняющая структуру ячейки АТМ, используемой в устройстве на фиг.2; и

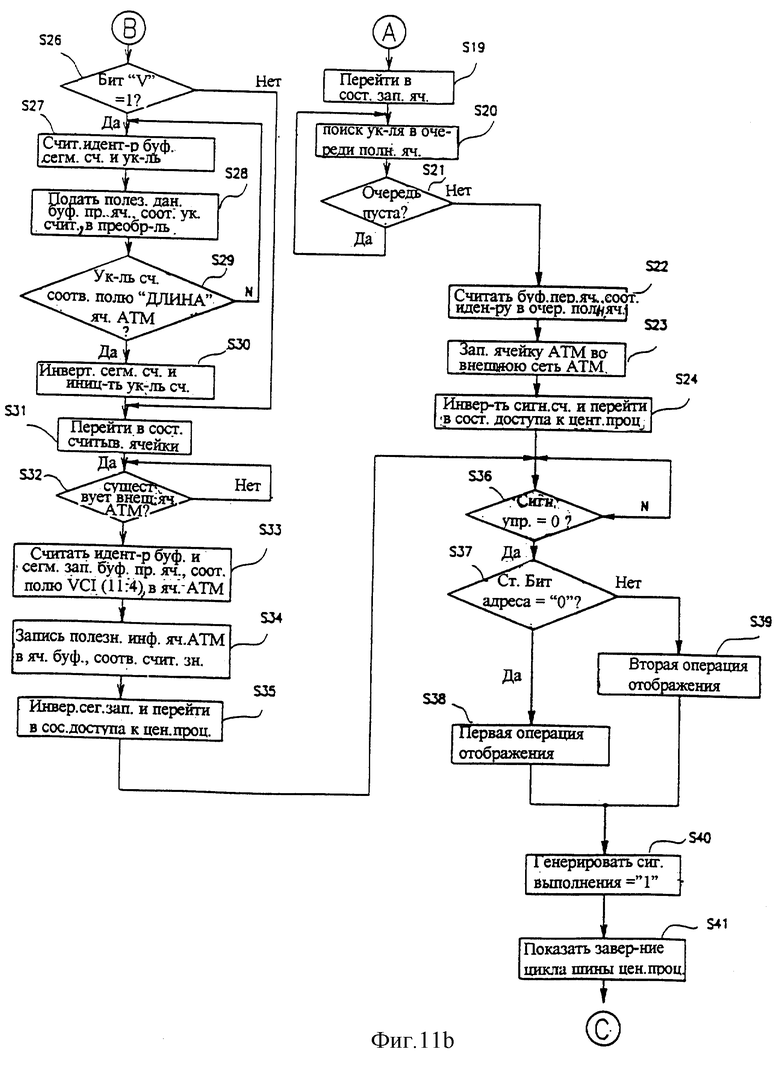

фиг. 11а, 11b - блок-схемы, поясняющие способ сегментации и повторной сборки трафика с постоянной битовой скоростью в сети АТМ согласно настоящему изобретению.

Подробное описание предпочтительных вариантов осуществления изобретения

Обратимся к фиг.2, на которой показано устройство для сегментации и повторной сборки трафика с постоянной битовой скоростью в сети АТМ в соответствии с одной из форм осуществления настоящего изобретения. Как показано на фиг.2, устройство сегментации и повторной сборки трафика с постоянной битовой скоростью в основном включает два модуля, а именно, модуль 10 формирования ячейки АТМ для считывания с постоянной битовой скоростью данных, принимаемых от внешнего приемопередатчика 31 сигнала Т1/Е1 (фиг.1), и преобразования считанных данных с постоянной битовой скоростью в ячейку АТМ и модуль 20 формирования кадра Т1/Е1, служащий для считывания ячейки АТМ, полученной от внешнего приемопередатчика 36 АТМ (фиг.1), преобразования считанной ячейки АТМ в кадр Т1/Е1 и передачи кадра Т1/Е1 в приемопередатчик 31 сигнала Т1/Е1.

Модуль 10 формирования ячейки АТМ содержит блок 11 синхронизации состояния, последовательно-параллельный преобразователь 12, блок 13 преобразования данных временного интервала в ячейку, блок 14 управления передаваемой ячейкой, блок 15 доступа к центральному процессору и блок 16 доступа к буферу передаваемой ячейки.

Блок 11 синхронизации состояния получает извне сигналы синхронизации 8 кГц, N•8 кГц и CLK, образуя при этом конечный автомат и множество счетчиков. Сигнал синхронизации 8 кГц является синхронизирующим сигналом сети, сигнал синхронизации N•8 кГц синхронизирующим сигналом временных интервалов, а сигнал синхронизации CLK - рабочим тактовым сигналом.

Последовательно-параллельный преобразователь 12 получает извне сигналы синхронизации N•8 кГц и N•8•8 кГц. Преобразователь 12 получает также последовательные данные от приемопередатчика 31 сигнала Т1/Е1 и преобразует принятые последовательные данные в 8-разрядные параллельные данные. Сигнал синхронизации N•8•8 кГц является тактовым сигналом, синхронизирующим биты временных интервалов.

Блок 13 преобразования данных временного интервала в ячейку получает параллельные данные из последовательно-параллельного преобразователя 12 синхронно с сигналом синхронизации N•8 кГц, подаваемым на него через блок 11 синхронизации состояния. Блок 13 считывает полученные параллельные данные и извлекает данные временного интервала кадра Т1/Е1. Блок 13 также определяет, должны или нет выделенные данные быть отброшены, основываясь на информации управления для соответствующего буфера передаваемой ячейки. Если выделенные данные полезны, то они записываются в соответствующий буфер передаваемой ячейки. Когда ячейки АТМ полностью накоплены в необязательном отдельном буфере передаваемой ячейки, соответствующий идентификатор буфера ячейки записывается в очередь полных ячеек.

Блок 14 управления передаваемой ячейкой служит для поиска в очереди полных ячеек и для записи посредством этого данных соответствующих буферов передаваемых ячеек во внешний буфер ячеек.

Блок 15 доступа к центральному процессору управляет доступом центральных процессоров и внутренних блоков модуля 10 формирования ячейки АТМ к буферу передаваемой ячейки.

Блок 16 доступа к буферу передаваемой ячейки управляет доступом внутренних блоков модуля 10 формирования ячейки АТМ к буферу передаваемой ячейки в соответствии с сигналом, показывающим состояние конечного автомата, который образован блоком 11 синхронизации состояния.

С другой стороны, модуль 20 формирования кадра Т1/Е1 содержит блок 21 синхронизации состояния, блок 22 управления принимаемой ячейкой, блок 23 преобразования ячейки в данные временного интервала, параллельно-последовательный преобразователь 24, блок 25 доступа к центральному процессору и блок 26 доступа к буферу принимаемой ячейки.

Блок 21 синхронизации состояния принимает внешние сигналы синхронизации 8 кГц, N•8 кГц и CLK, образуя при этом конечный автомат и множество счетчиков.

Блок 22 управления принимаемой ячейкой считывает входную ячейку АТМ, определяя при этом, является ли входная ячейка АТМ полезной. Если входная ячейка АТМ полезна, блок 22 управления принимаемой ячейкой записывает ячейку АТМ в соответствующий буфер принимаемых ячеек.

Блок 23 преобразования ячейки в данные временного интервала считывает данные из каждого буфера принимаемой ячейки синхронно с сигналом синхронизации N•8 кГц, подаваемым на него через блок 21 синхронизации состояния, и записывает считанные данные в соответствующий временной интервал кадра Т1/Е1.

Параллельно-последовательный преобразователь 24 получает извне сигналы синхронизации N•8 кГц и N•8•8 кГц. Параллельно-последовательный преобразователь 24 также получает параллельные данные из блока 23 преобразования ячейки в данные временного интервала и преобразует полученные параллельные данные в последовательные данные.

Блок 25 доступа к центральному процессору управляет доступом центральных процессоров и внутренних блоков модуля 20 формирования кадра Т1/Е1 к буферу принимаемой ячейки.

Блок 26 доступа к буферу принимаемой ячейки управляет доступом внутренних блоков модуля 20 формирования кадра Т1/Е1 к буферу принимаемой ячейки в соответствии с сигналом, показывающим состояние конечного автомата, образуемого блоком 21 синхронизации состояния.

Ниже будет описана работа устройства сегментации и повторной сборки трафика с постоянной битовой скоростью, имеющего вышеупомянутую конфигурацию согласно настоящему изобретению.

Как показано на фиг.3, состояние конечного автомата может соответствовать одному из шести состояний. Сигнал, характеризующий состояние конечного автомата, генерируется блоком 11 синхронизации состояния. Как показано на временной диаграмме на фиг.4, блок 11 синхронизации состояния инициализирует значение сигнала состояния конечного автомата в точке b при увеличении значения в точке а счетчиком временных интервалов. Сигнал состояния, сформированный блоком 11, передается на другие блоки.

Буферы принимаемых ячеек и буферы передаваемых ячеек, являющиеся буферами для хранения ячеек АТМ, которые должны быть приняты от внешней сети АТМ и переданы в эту сеть, сконфигурированы как показано на фиг.5 и 6 соответственно. Для каждого временного интервала выделяется один буфер принимаемой ячейки и один буфер передаваемой ячейки. Каждый блок ячеек сохраняет в себе две ячейки АТМ. Как показано на фиг.5 и 6, каждая АТМ ячейка имеет свой тип полезной нагрузки, определяемый на основе значения, записанного в ее поле "ТИП ЯЧЕЙКИ". Длина полезной нагрузки каждой ячейки АТМ определяется значением, записанным в поле "ДЛИНА" ячейки АТМ.

На фиг. 5а показан единичный буфер передаваемой ячейки, в котором сохраняются ячейки АТМ, имеющие тип ячейки "01", в то время как на фиг.5b показан единичный буфер передаваемой ячейки, в котором сохраняются ячейки АТМ, имеющие тип ячейки "10". На фиг.6а показан единичный буфер принимаемой ячейки, в котором сохраняются ячейки АТМ, имеющие тип ячейки "01", в то время как на фиг.6b показан единичный буфер принимаемой ячейки, в котором сохраняются ячейки АТМ, имеющие тип ячейки "10".

На фиг. 7 и 8 показаны общие карты распределения памяти для буферов передаваемых ячеек и буферов принимаемых ячеек соответственно. Как показано на фиг. 7 и 8, таблица индексов порядковых номеров (SNIT) записывается в каждой карте распределения памяти по отдельному адресу. Таблица индексов порядковых номеров является таблицей, в которой объединены вместе индикаторы подуровня конвергенции (SCI), порядковые номера (SN) и данные защиты порядковых номеров (SNP). Очередь полных ячеек (CCQ) для хранения идентификатора буфера полной АТМ ячейки также записывается в каждую карту распределения памяти по отдельному адресу. Таблица индексов порядковых номеров записывается центральным процессором в стадии начальной загрузки системы. Запись этой таблицы выполняется в виде, показанном на фиг.9.

В то время как блок 16 доступа к буферу передаваемой ячейки управляет доступом к буферам передаваемых ячеек в каждом состоянии конечного автомата в соответствии с внутренним сигналом состояния, поступающим из блока 11 синхронизации состояния, блок 26 доступа к буферу принимаемой ячейки управляет доступом к буферам принимаемых ячеек в каждом состоянии конечного автомата в соответствии с внутренним сигналом состояния, поступающим из блока 21 синхронизации состояния.

Например, блок 16 доступа к буферу передаваемой ячейки и блок 26 доступа к буферу принимаемой ячейки позволяют блоку 13 преобразования данных временного интервала в ячейку и блоку 23 преобразования ячейки в данные временного интервала получать доступ к буферам передаваемых ячеек и буферам принимаемых ячеек в состоянии считывания/записи временного интервала соответственно. В состоянии считывания/записи ячейки блок 16 доступа к буферу передаваемой ячейки и блок 26 доступа к буферу принимаемой ячейки позволяют блоку 14 управления передаваемой ячейкой и блоку 22 управления принимаемой ячейкой осуществлять доступ к буферам передаваемых ячеек и буферам принимаемых ячеек, соответственно. В состоянии доступа к центральному процессору блок 16 доступа к буферу передаваемой ячейки и блок 26 доступа к буферу принимаемой ячейки позволяют блокам 15 и 25 доступа к центральному процессору осуществлять доступ к буферам передаваемых ячеек и буферам принимаемых ячеек соответственно. Буферы ячеек АТМ для буферов передаваемых ячеек и буферов принимаемых ячеек имеют одинаковый тип поля управления.

Работа устройства сегментации и повторной сборки трафика с постоянной битовой скоростью согласно настоящему изобретению, соответственно связанная с шестью состояниями конечного автомата, будет описана со ссылкой на блок-схему, показанную на фиг.11а, 11b.

Сначала каждый из блоков 11 и 21 синхронизации состояния определяет, имеет ли прикладываемый к нему сигнал сброса значение "0" или "1" (Шаг S1).

Если сигналы сброса имеют значение "0", то текущее состояние конечного автомата меняется на состояние сброса (Шаг S2). В состоянии сброса все внешние выходные сигналы выключены (Шаг S3). Если сигнал сброса имеет значение "1", то текущее состояние меняется на состояние инициализации (Шаг S4).

В состоянии инициализации биты "достоверно" (V) буферов передаваемых ячеек и буферов принимаемых ячеек преобразуются так, чтобы они имели значение "0" (Шаг S5). После этого определяется, завершена или нет инициализация буферов передаваемых ячеек и буферов принимаемых ячеек после преобразования значения бита достоверности "V" (Шаг S6). После инициализации всех буферов передаваемых ячеек или буферов принимаемых ячеек текущее состояние меняется на состояние ожидания (Шаг S7).

В состоянии ожидания все сигналы внешнего вывода выключены (Шаг S8). В состоянии, когда все сигналы, выводимые из блока 11 или 21 синхронизации состояния, выключены, определяется, изменяется ли из "0" в "1" внешний сигнал синхронизации N•8 кГц (Шаг S9). Как лучше всего видно на временной диаграмме фиг. 4, текущее состояние меняется на состояние считывания/записи временного интервала в момент времени "а", когда сигнал синхронизации N•8 кГц переключается из "0" в "1" (Шаг S10). Бит достоверности "V" показывает, установлено соединение или нет. Когда соединение установлено, бит "V" имеет значение "1".

После того, как текущее состояние меняется на состояние считывания/записи временного интервала, определяется, соответствует ли текущее состояние состоянию считывания временного интервала или состоянию записи временного интервала (Шаг S11).

В состоянии считывания временного интервала блок 13 преобразования данных временного интервала в ячейку считывает бит "V" из буфера передаваемой ячейки, соответствующего входному временному интервалу (шаг S12) и определяет, имеет считанный бит "V" значение "0" или "1" (Шаг S13).

Если считываемое значение соответствует "0", то текущее состояние меняется на состояние записи ячейки. С другой стороны, если считываемое значение соответствует "1", то текущее состояние меняется на состояние считывания ячейки. В состоянии считывания ячейки считывается вся информация, связанная со вводом данных в последовательно-параллельный преобразователь 12: идентификатор буфера ячейки, записываемый интервал и указатель (Шаг S14). Потом входные данные записываются в буфер передаваемой ячейки в соответствии с указателем считывания (Шаг S15). Затем определяется, имеет ли указатель считывания значение, соответствующее полю "ДЛИНА" ячейки АТМ (Шаг S16).

Идентификатор буфера ячейки представляет позицию буфера, в которой сохраняются данные входного кадра Т1/Е1. Сегмент записи представляет один буфер, выбранный из двух буферов ячеек. Блок 13 преобразования данных временного интервала в ячейку модуля 10 формирования ячейки АТМ инвертирует значение записываемого сегмента после того, как одна ячейка будет полностью записана. Указатель представляет позицию в 48-битовой полезной нагрузке, куда данные входного кадра Т1/Е1 записываются блоком 13 преобразования данных временного интервала в ячейку в модуле 10 формирования ячейки АТМ.

Если указатель считывания имеет значение, не соответствующее значению поля "ДЛИНА", шаг считывания идентификатора буфера ячейки, сегмента записи и указателя выполняется несколько раз, до тех пор, пока указатель считывания не будет иметь значение, соответствующее значению поля "ДЛИНА". Если указатель считывания имеет значение, соответствующее значению поля "ДЛИНА", значение сегмента записи инвертируется (Шаг S17). На шаге S17 также инициализируется указатель. Затем идентификатор буфера ячейки записывается в очередь полных ячеек (Шаг S18). После завершения этих шагов текущее состояние меняется на состояние записи ячейки (Шаг S19).

В состоянии записи ячейки разыскивается указатель в очереди полных ячеек (Шаг S20). Затем определяется, является ли очередь пустой (Шаг S21). Если очередь пуста, поиск указателя в очереди полных ячеек выполняется до тех пор, пока не будет определено, что очередь не пуста. Если очередь не пуста, считывается буфер передаваемой ячейки, соответствующий идентификатору буфера ячейки, хранящемуся в очереди полных ячеек (Шаг S22). В этом состоянии соответствующая ячейка АТМ записывается во внешнюю сеть АТМ (Шаг S23). После завершения этой операции значение соответствующего сегмента считывания инвертируется (Шаг S24). После инвертирования значения сегмента считывания текущее состояние меняется на состояние доступа к центральному процессору (Шаг S24). Сегмент считывания представляет один буфер, выбранный из двух буферов ячеек. Блок 14 управления передаваемой ячейкой модуля 10 формирования ячейки АТМ и блок 23 преобразования ячейки в данные временного интервала модуля 20 формирования кадра Т1/Е1 соответственно инвертируют значение сегмента считывания после полного считывания одной ячейки.

В состоянии записи временного интервала считывается бит "V" буфера принимаемой ячейки, соответствующий входному временному интервалу (Шаг S25). После этого определяется, имеет считанный бит достоверности "V" значение "0" или "1"(Шаг S26). Если считываемое значение соответствует "0", то текущее состояние просто меняется на состояние считывания ячейки. С другой стороны, если считываемое значение соответствует "1", то считывается вся информация, связанная со входным временным интервалом: идентификатор буфера ячейки, сегмент считывания и указатель (Шаг S27). Вслед за этим считываются полезные данные, а именно, полезная нагрузка из буфера принимаемой ячейки, соответствующего указателю считывания.

Считываемая полезная нагрузка подается на параллельно-последовательный преобразователь 24 (Шаг S28). Затем определяется, имеет или нет указатель считывания значение, соответствующее полю "ДЛИНА" ячейки АТМ (Шаг S29). В случае буферов принимаемых ячеек, идентификатор буфера ячейки представляет позицию буфера, в которой сохраняются данные входной ячейки АТМ. Сегмент записи представляет собой один буфер, выбранный из двух буферов ячеек. Блок 23 преобразования ячейки в данные временного интервала в модуле 20 формирования кадра Т1/Е1 инвертирует значение сегмента записи после того, как полностью считывается одна ячейка. Указатель представляет позицию в 48-битовой полезной нагрузке, откуда данные выходного кадра Т1/Е1 считываются блоком 23 преобразования ячейки в данные временного интервала в модуле 20 формирования кадра Т1/Е1.

Если указатель считывания имеет значение, не соответствующее значению поля "ДЛИНА", то шаг считывания идентификатора буфера ячейки, сегмента считывания и указателя выполняется несколько раз до тех пор, пока указатель считывания не будет иметь значение, соответствующее значению поля "ДЛИНА". Если указатель считывания имеет значение, соответствующее значению поля "ДЛИНА", значение сегмента считывания инвертируется (Шаг S30). На шаге S30 также инициализируется указатель. После завершения этих шагов текущее состояние меняется на состояние считывания ячейки (Шаг S31).

В состоянии считывания ячейки блок 22 управления принимаемой ячейкой определяет, имеется или нет внешняя ячейка АТМ (Шаг S32). Если внешняя АТМ ячейка имеется, то считываются идентификатор буфера ячейки и сегмент записи буфера принимаемой ячейки, соответствующие полю идентификатора виртуального канала VCI (11:4) (фиг.10) в АТМ ячейке (Шаг S33). Полезные нагрузки ячейки АТМ, от 0 до 47, записываются в ячейки памяти буфера принимаемой ячейки, соответствующие считываемым значениям (Шаг S34). После выполнения этой операции записи сегмент записи инвертируется (Шаг S35). В этом положении текущее состояние меняется на состояние доступа к центральному процессору.

На фиг. 10 "OPN" является номером выходного порта для ячеек АТМ, выбранным для назначения пути коммутации. Выходные порты устанавливаются в соответствие с битами выходных данных один за другим. Например, если выбран выходной порт, соответствующий OPN 7, выводятся данные "1000000". Для данных "1111111" выбираются все выходные порты. Идентификатор виртуального канала VCI (11: 4) содержит VCI (11:9), указывающий кадр Т1/Е1, и VCI (8:4), указывающий временной интервал. VCI (15:12) также включен в структуру ячейки АТМ для будущего расширения. Тип полезной нагрузки (РТ) тоже включен в структуру ячейки АТМ. Тип полезной нагрузки используется, чтобы определить будущую обработку для ячеек режима и управления (ОАМ) и ячеек сигнализации. Однако настоящее изобретение такой РТ не использует. Структура ячейки АТМ включает также общее управление потоком данных (GFC), приоритет потери ячейки (CLP), VCI (7: 4) и VCI (3:0), которые в настоящем изобретении не используются.

В состоянии доступа к центральному процессору блок 15 доступа к центральному процессору определяет, имеет сигнал управления CPU_CS, сформированный центральным процессором, значение "0" или "1" (Шаг S36). Если сигнал управления CPU_CS имеет значение "0", то затем определяется, имеет ли старший бит сигнала адреса CPU_ADDR, сформированный центральным процессором, значение "0" или "1" (Шаг S37).

Если старший бит сигнала адреса CPU_ADDR имеет значение "0", блок 15 доступа к центральному процессору выполняет первую операцию отображения для преобразования сигналов CPU_CS, CPU_RW, CPU_DATA и CPU_ADDR, сформированных центральным процессором, в сигналы буфера передаваемой ячейки: TCB_CS, TCB_ RW, TCB_DATA и TCB_ADDR (Шаг S38). С другой стороны, если старший бит сигнала адреса CPU_ADDR имеет значение "1", блок 15 доступа к центральному процессору выполняет вторую операцию отображения для преобразования сигналов CPU_ CS, CPU_ RW, CPU_DATA и CPU_ADDR в сигналы буфера принимаемой ячейки: RCB_ CS, RCB_ RW, RCB_DATA, и RCB_ADDR (Шаг S39). После завершения операции отображения блок 15 доступа к центральному процессору генерирует сигнал выполнения CPU_ DONE, имеющий значение "1" (Шаг S40). Этот сигнал выполнения CPU_DONE подается на центральный процессор, чтобы он был информирован о завершения цикла работы шины центрального процессора (Шаг S41). После этого текущее состояние меняется на состояние ожидания.

Вышеупомянутая работа устройства сегментации и повторной сборки трафика с постоянной битовой скоростью повторяется между последовательными состояниями ожидания, а именно, между соседними точками а, показанными на временной диаграмме на фиг.4.

В соответствии с настоящим изобретением получается стандартизированный и простой переход от одного режима работы к другому. Соответственно можно увеличить число соединений Т1/Е1. Устройство в соответствии с настоящим изобретением может быть также оперативно подключено к коммутатору АТМ, такому как АТМ приемопередатчик 36. В этом случае можно заменить коммутатором АТМ обычные коммутаторы звуковых сигналов системы с временным мультиплексированием каналов, предназначенные для пространственной и временной коммутации данных, передаваемых с помощью импульсно-кодовой модуляции. Соответственно достигается значительное уменьшение стоимости и объема оборудования больших коммутаторов звуковых сигналов.

Как ясно из вышеупомянутого описания, в соответствии с настоящим изобретением внешние ячейки АТМ записываются в буферы при условии, что определенные поля управления добавляются к таким АТМ ячейкам модулем формирования кадра Т1/Е1. Также данные кадра Т1/Е1 считываются и преобразуются в ячейку АТМ модулем формирования ячейки АТМ согласно настоящему изобретению. АТМ ячейка затем записывается в буфер. Ячейки АТМ, сохраненные в буфере, считываются последовательным образом.

Считанные данные записываются в отдельный временной интервал кадра Т1/Е1 или передаются в АТМ сеть. Соответственно можно уменьшить объем оборудования и стоимость аппаратуры сегментации и повторной сборки трафика с постоянной битовой скоростью в сети АТМ.

Устройство согласно настоящему изобретению также может быть оперативно подключено к коммутатору АТМ, например к приемопередатчику АТМ. В этом случае можно заменить на коммутатор АТМ коммутаторы звуковых сигналов обычной системы передачи с временным мультиплексированием, предназначенные для пространственной и временной коммутации данных, передаваемых с помощью импульсно-кодовой модуляции. Соответственно достигается значительная экономия в стоимости и объеме оборудования больших коммутаторов звуковых сигналов.

Хотя выше для пояснения описаны лишь предпочтительные формы осуществления изобретения, специалистам ясно, что изобретение этим не ограничивается и что различные варианты его осуществления могут иметь место в пределах его сущности и объема, определяемых формулой изобретения.

Предлагаются способ и устройство сегментации и повторной сборки трафика с постоянной скоростью передачи битов, в котором выполняется операция преобразования трафика с постоянной скоростью передачи битов, содержащегося в кадре сигнала Т1/Е1, в ячейку АТМ и обратная ей операция, а именно, операция преобразования ячейки АТМ в трафик с постоянной скоростью передачи битов и транспортировки трафика с постоянной скоростью передачи битов в кадре Т1/Е1. Обычные системы сегментации и повторной сборки трафика с постоянной скоростью передачи битов требуют использования ряда модулей для обеспечения оперативного соединения между телефонной сетью общего пользования и сетью АТМ. По этой причине такие стандартные системы сегментации и повторной сборки трафика с постоянной скоростью передачи битов увеличивают стоимость и объем аппаратуры. В соответствии с представленным изобретением достигается стандартизированный и простой переход между различными режимами работы. Соответственно можно увеличить число соединений Т1/Е1. Устройство согласно настоящему изобретению также может быть оперативно подключено к коммутатору АТМ, например к приемопередатчику АТМ. В этом случае можно заменить коммутатором АТМ коммутаторы звуковых сигналов стандартной системы с временным мультиплексированием, предназначенной для пространственной и временной коммутации данных, передаваемых методом импульсно-кодовой модуляции. Соответственно достигается значительная экономия в стоимости и объеме аппаратуры больших коммутаторов звуковых сигналов. 3 с. и 4 з.п. ф-лы, 14 ил.

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| Способ передачи дискретных сигналов и устройство для его осуществления | 1975 |

|

SU858582A3 |

| Экономайзер | 0 |

|

SU94A1 |

| ЕР 0493176 A1, 01.07.1992 | |||

| US 5204857 А, 20.04.1993. | |||

Авторы

Даты

2002-12-10—Публикация

1997-11-03—Подача