Изобретение относится к устройству для выдачи сообщений, предназначенному для систем коммутации, а более конкретно, к устройству для выдачи сообщений для системы коммутации, которое позволяет повысить эффективность каналов речевого обслуживания.

Обычно система коммутации содержит устройство для выдачи речевого сообщения вызывающей стороне, когда произведен вызов. Речевое сообщение информирует вызывающую сторону о состоянии вызываемой стороны или о затруднениях при соединении вызова.

На фиг. 1 изображена блок-схема известного устройства для выдачи сообщений для системы коммутации. Как показано на фиг. 1, известное устройство для выдачи сообщений содержит главный процессор 10, процессор 11 фиксированного речевого сигнала и процессор 12 редактированного речевого сигнала. Процессор 11 фиксированного речевого сигнала, реагируя на команду от главного процессора 10, выдает фиксированные (неизменные) речевые сообщения для информирования вызывающей стороны о состоянии отказа линии при соединении вызова. Процессор 12 редактированного речевого сигнала, реагируя на команду от главного процессора 10, выдает сигнал редактированного речевого сообщения для обеспечения вызывающей стороны специальным обслуживанием, например, информацией об изменении номера, об отказе от входящих вызовов, информацией, выдаваемой при отсутствии абонента и т.п. Процессор 12 редактированного речевого сигнала формирует на выходе сигнал редактированного речевого сообщения и подает его через субмагистрали SHW0 и SHW1 на устройство временной коммутации системы коммутации. Процессор 11 фиксированного речевого сигнала формирует на выходе сигнал фиксированного речевого сообщения и подает его через субмагистрали SHW3 и SHW4 на устройство временной коммутации системы коммутации. Процессор 11 фиксированного речевого сигнала и процессор 12 редактированного речевого сигнала могут выдавать соответствующие сигналы речевого сообщения только в пределах максимальных диапазонов назначенных им каналов речевого обслуживания. Поэтому в случае, когда у процессоров 11 и 12 запрашивают соответствующие сигналы речевого сообщения сверх этих максимальных диапазонов каналов речевого обслуживания, процессоры должны ожидать, пока имеющиеся каналы вывода речевого сигнала освободятся. Затем, когда незанятые каналы появляются, процессор 11 фиксированного речевого сигнала и процессор 12 редактированного речевого сигнала выдают соответствующие сигналы речевого сообщения через незанятые каналы. Пока вызывающая сторона ожидает, когда процессор 11 фиксированного речевого сигнала и процессор 12 редактированного речевого сигнала выдадут соответствующие сигналы речевого сообщения, ей транслируется музыкальная передача.

Как отмечено выше, в известных устройствах для выдачи сообщений для системы коммутации процессор 11 фиксированного речевого сигнала и процессор 12 редактированного речевого сигнала могут выдавать соответствующие сигналы речевого сообщения только в пределах максимальных диапазонов назначенных им каналов речевого обслуживания. Предположим, например, что в данный момент некоторые из каналов речевого обслуживания, назначенные процессору 11 фиксированного речевого сигнала, находятся в незанятом состоянии, а все каналы речевого обслуживания, назначенные процессору 12 редактированного речевого сигнала, осуществляют передачу речевых сообщений, обеспечивая речевое обслуживание. Получив от главного процессора 10 команду вывода речевого сигнала, процессор 12 редактированного речевого сигнала ожидает, пока по меньшей мере один из его каналов речевого обслуживания перейдет в незанятое состояние, и только затем передает соответствующий сигнал речевого сообщения через этот канал, несмотря на то, что имеются незанятые каналы у процессора 11 фиксированного речевого сигнала. В связи с этим недостатком известного устройства для выдачи сообщений для системы коммутации является то, что каналы речевого обслуживания используются недостаточно эффективно.

Поэтому, исходя из вышеизложенного, целью настоящего изобретения является создание устройства для выдачи сообщений для системы коммутации, которое способно повысить эффективность каналов речевого обслуживания.

Согласно настоящему изобретению эта и другие цели могут быть достигнуты с помощью устройства для выдачи сообщений для системы коммутации, которое содержит первое устройство управления для управления выводом сигналов речевого сообщения для всех каналов речевого обслуживания, первое запоминающее устройство для хранения данных адреса вывода речевого сигнала, причем эти данные адреса вывода речевого сигнала соответствуют данным команды вывода речевого сигнала из первого устройства управления, второе устройство управления, реагирующее на сигнал прерывания, для запоминания данных адреса вывода речевого сигнала, соответствующих данным команды вывода речевого сигнала из первого устройства управления, в первом запоминающем устройстве и для выдачи данных состояния вывода речевого сигнала, второе запоминающее устройство для передачи данных команды вывода речевого сигнала из первого устройства управления во второе устройство управления и передачи данных состояния вывода речевого сигнала из второго устройства управления в первое устройство управления, запоминающее устройство фиксированного речевого сигнала для хранения данных фиксированных речевых сообщений и для выдачи в параллельной форме данных одного из фиксированных речевых сообщений, хранимых в ячейке, соответствующей данным адреса вывода речевого сигнала из первого запоминающего устройства, запоминающее устройство редактированного речевого сигнала для хранения данных редактированных речевых сообщений и для выдачи в параллельной форме данных одного из редактированных речевых сообщений, хранимых в его ячейке, соответствующей данным адреса вывода речевого сигнала из первого запоминающего устройства, и устройство управления памятью/обработки речевого сигнала для выдачи во второе устройство управления сигнала прерывания, считывания данных адреса вывода речевого сигнала из первого запоминающего устройства, выдачи считанных данных адреса вывода речевого сигнала в запоминающее устройство фиксированного речевого сигнала или запоминающее устройство редактированного речевого сигнала, преобразования параллельных данных сигнала речевого сообщения, полученных из запоминающего устройства фиксированного речевого сигнала или запоминающего устройства редактированного речевого сигнала, в последовательные данные и передачи последовательных преобразованных данных через субмагистраль в коммутационное устройство коммутационной системы.

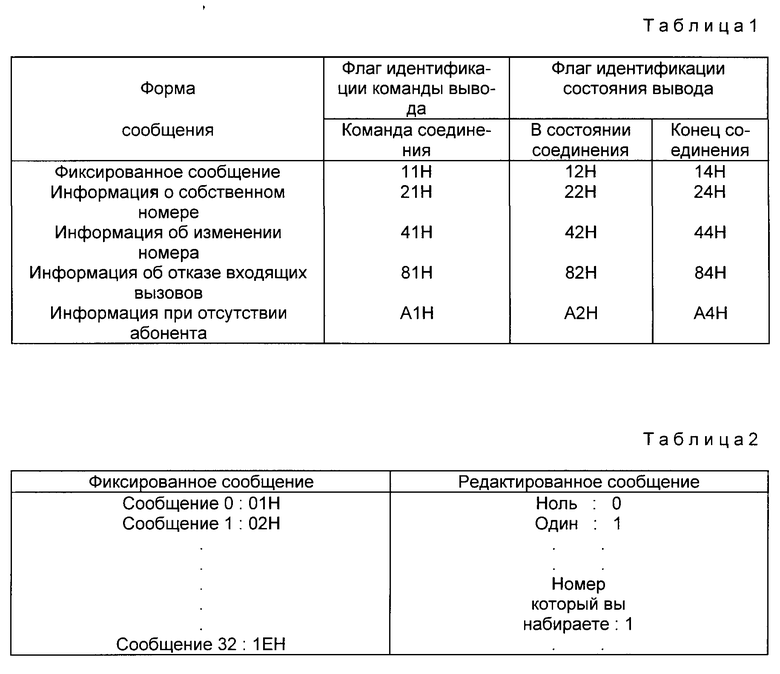

Данные команд вывода речевого сигнала, которые передаются из первого устройства управления через второе запоминающее устройство во второе устройство управления, содержат флаг идентификации команды вывода и флаг идентификации сообщения. Данные о состоянии вывода речевого сигнала, которые передаются из второго устройства управления через второе запоминающее устройство в первое устройство управления, содержат флаг идентификации состояния вывода.

Второе запоминающее устройство содержит первую область памяти для хранения флага идентификации сообщения и третью область памяти для хранения флага идентификации состояния вывода. Устройство управления памятью/обработки речевого сигнала в каждый из заранее заданных моментов времени формирует на выходе сигнал прерывания для второго устройства управления.

Реагируя на сигнал прерывания от устройства управления памятью/обработки речевого сигнала, второе устройство управления периодически повторяет операции считывания из второго запоминающего устройства данных команды вывода речевого сигнала, записи данных адреса вывода речевого сигнала, соответствующих данным команды вывода речевого сигнала, в первое запоминающее устройство и записи данных состояния вывода речевого сигнала во второе запоминающее устройство.

Устройство управления памятью/обработки речевого сигнала периодически повторяет операции считывания из первого запоминающего устройства данных адреса вывода речевого сигнала, подачи считанных данных адреса вывода речевого сигнала в запоминающее устройство фиксированного речевого сигнала или запоминающее устройство редактированного речевого сигнала, преобразования параллельных данных речевого сообщения, полученных из запоминающего устройства фиксированного речевого сигнала или запоминающего устройства редактированного речевого сигнала, в последовательные данные и передачи преобразованных последовательных данных через субмагистраль в устройство коммутации системы коммутации. Структура адресации первого запоминающего устройства такова, что второе устройство управления и устройство управления памятью/обработки речевого сигнала не могут получить доступ к одной и той же ячейке памяти одновременно.

Описанные выше цели, признаки и преимущества настоящего изобретения будут более подробно раскрыты в последующем описании и чертежах, где

на фиг. 1 изображена блок-схема известного устройства для выдачи сообщений для системы коммутации;

на фиг. 2 изображена блок-схема устройства для выдачи сообщений для системы коммутации согласно изобретению;

на фиг. 3 изображен пример, иллюстрирующий использование общей памяти, показанной на фиг. 2, и

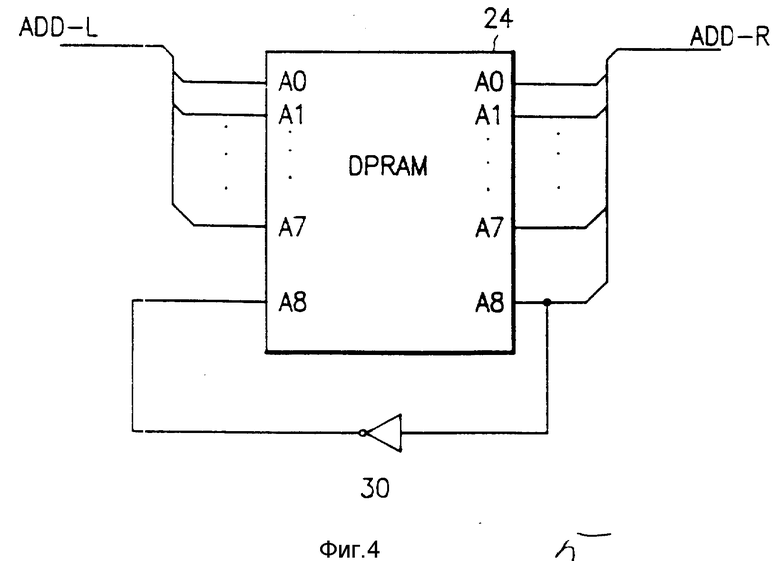

на фиг. 4 изображен пример, иллюстрирующий использование двухпортовой памяти с произвольной выборкой, показанной на фиг. 2.

На фиг. 2 изображена блок-схема устройства для выдачи сообщений для системы коммутации согласно изобретению. Как показано на этом чертеже, устройство для выдачи сообщений содержит главный процессор 21, общую память 22, центральный процессор 23 (CPU), двухпортовую память 24 с произвольной выборкой (DPRAM), блок 25 управления памятью/обработки речевого сигнала, память 26 фиксированного речевого сигнала и память 27 редактированного речевого сигнала. Главный процессор 21 выдает данные команд вывода речевого сообщения в общую память 22 и получает из общей памяти 22 данные состояния вывода речевого сообщения. Общая память 22 передает данные команд речевого сообщения из главного процессора 21 в центральный процессор 23. Общая память 22 также передает данные состояния вывода речевого сообщения из центрального процессора 23 в главный процессор 21. Центральный процессор 23, реагируя на сигнал прерывания из блока 25 управления памятью/обработки речевого сигнала, записывает данные адреса вывода речевого сигнала в двухпортовую память 24 с произвольной выборкой. Данные адреса вывода речевого сигнала соответствуют данным команды вывода речевого сообщения из общей памяти 22. Центральный процессор 23 также записывает в общую память 22 данные состояния вывода речевого сообщения. Блок 25 управления памятью/обработки речевого сигнала периодически выдает в центральный процессор 23 сигнал прерывания. Кроме того, блок 25 управления памятью/обработки речевого сигнала считывает из двухпортовой памяти 24 с произвольной выборкой данные адреса вывода речевого сигнала и выдает эти данные в память 26 фиксированного речевого сигнала или память 27 редактированного речевого сигнала. Дополнительно блок 25 управления памятью/обработки речевого сигнала преобразует параллельные данные речевого сообщения, поступившие из памяти 26 фиксированного речевого сигнала или памяти 27 редактированного речевого сигнала, в последовательные данные и подает последовательные преобразованные данные через субмагистраль SHW в устройство 28 временной коммутации системы коммутации.

Главный процессор 21 и центральный процессор 23 передают и принимают через общую память 22 данные команд вывода речевого сообщения и данные состояния вывода речевого сообщения и обратно. Данные команд вывода речевого сообщения, которые передаются из главного процессора 21 в центральный процессор 23, содержат флаг идентификации команды вывода (см. табл. 1) и флаг идентификации сообщения (см. табл. 2). Данные состояния вывода речевого сообщения, которые передаются из центрального процессора 23 в главный процессор 21, содержат флаг идентификации состояния вывода (см. табл. 1). Для приема и выдачи описанных выше данных общая память 22 содержит область флага передачи (TFA), область флага приема (RFA) и область данных (DTA), как показано на фиг. 3. Флаг идентификации команды вывода, поступающий из главного процессора 21, записывается в область TFA флага передачи общей памяти 22. Флаг идентификации состояния вывода, поступающий из центрального процессора 23, записывается в область RFA флага приема общей памяти 22. Флаг идентификации сообщения, поступающий из главного процессора 21, записывается в область DTA данных общей памяти 22. Флаг идентификации команды вывода, записанный в область флага передачи, занимает 1 байт для каждого канала речевого обслуживания. Флаг идентификации состояния вывода, записанный в область флага приема, занимает 1 байт для каждого канала речевого обслуживания. Флаг идентификации сообщения, записанный в область данных общей памяти 22, занимает 16 байтов для каждого канала речевого обслуживания.

В табл. 1 показаны флаг идентификации команды вывода, поступающий из главного процессора 21, и флаг идентификации состояния вывода, поступающий из центрального процессора 23, а в табл. 2 показан флаг идентификации сообщения, поступающий из главного процессора 21. В табл. 1 фиксированное сообщение - это сообщение, которое выдается в неизменной форме, а информация о собственном номере, изменении номера, отказе от входящих выводов и информация, выдаваемая при отсутствии абонента, представляет собой редактированные сообщения, которые выдаются в различной форме.

Сначала главный процессор 21 записывает в область TFA флага передачи общей памяти 22 флаг идентификации команды вывода, указывающий, какое сообщение должно быть выдано. Кроме того, главный процессор 21 записывает в область DTA данных общей памяти 22 флаг идентификации сообщения, соответствующий тому сообщению, которое должно быть выдано. Центральный процессор 23 считывает соответственно из области TFA флага передачи общей памяти 22 - флаг идентификации команды вывода, а из области DTA данных общей памяти 22 - флаг идентификации сообщения. Затем центральный процессор 23 через линию DT1 данных подает данные адреса вывода речевого сигнала, соответствующие считанному флагу идентификации сообщения, в порт DA1 данных двухпортовой памяти 24 с произвольной выборкой. Кроме того, центральный процессор 23 через линию ADD-L адреса подает адрес в порт A1 адреса двухпортовой памяти 24. В результате данные адреса вывода речевого сигнала из центрального процессора 23 поступают в ячейку двухпортовой памяти 24, соответствующую адресу, поступившему из центрального процессора 23. Затем центральный процессор 23 записывает в область RFA флага приема общей памяти 22 флаг идентификации состояния вывода, который показывает, что сообщение находится в состоянии соединения. Данные адресов вывода речевого сигнала, хранящиеся в двухпортовой памяти 24 с произвольной выборкой, охватывают все каналы речевого обслуживания (предпочтительно 128 каналов). Центральный процессор 23 осуществляет описанные выше операции в течение 128 мс для того, чтобы записать данные адреса вывода речевого сигнала для всех каналов речевого обслуживания в двухпортовую память 24. Блок 25 управления памятью/обработки речевого сигнала периодически, или каждые 128 мс, подает адрес через линию ADD-R адреса в порт A2 адреса двухпортовой памяти 24 для считывания данных адреса вывода речевого сигнала из ячейки двухпортовой памяти 24, соответствующей поданному адресу. Блок 25 управления памятью/обработки речевого сигнала принимает считанные данные адреса вывода речевого сигнала из порта DA2 данных. Затем блок 25 управления памятью/обработки речевого сигнала подает считанные данные адреса вывода речевого сигнала в память 26 фиксированного речевого сигнала или память 27 редактированного речевого сигнала в качестве адреса. Память 26 фиксированного речевого сигнала или память 27 редактированного речевого сигнала выдает, в параллельной форме, данные речевого сообщения, хранящиеся в ячейке памяти, соответствующей адресу, поступившему из блока 25 управления памятью/обработки речевого сигнала. Блок 25 управления памятью/обработки речевого сигнала преобразует параллельные данные речевого сообщения, поступающие из памяти 26 фиксированного речевого сигнала или памяти 27 редактированного речевого сигнала, в последовательные данные и передает последовательные преобразованные данные через субмагистраль SHW на устройство 28 временной коммутации системы коммутации. После того, как закончится операция выдачи речевого сигнала, с учетом всех 128 каналов для одного периода прерывания (128 мс), блок 25 управления памятью/обработки речевого сигнала подает в центральный процессор 23 следующий сигнал прерывания. Реагируя на этот сигнал прерывания из блока 25 управления памятью/обработки речевого сигнала, центральный процессор 23 записывает данные адреса вывода речевого сигнала для всех 128 каналов в двухпортовую память 24 и записывает флаг идентификации состояния вывода для каждого канала в область RFA флага приема общей памяти 22. Главный процессор 21 считывает информацию, записанную в область RFA флага приема общей памяти 22 для распознавания состояния вывода речевого сигнала. Затем главный процессор 21 управляет операцией выдачи речевого сигнала в соответствии с распознанным состоянием вывода речевого сигнала.

Блок 25 управления памятью/обработки речевого сигнала периодически, через 128 мс, подает в центральный процессор 23 сигнал прерывания. Реагируя на сигнал прерывания от блока 25 управления памятью/обработки речевого сигнала, центральный процессор 23 осуществляет обработку данных адреса вывода речевого сигнала для всех каналов речевого обслуживания. Кроме того, центральный процессор 23 записывает флаг идентификации состояния вывода для каналов в область RFA флага приема общей памяти 22. Затем центральный процессор 23 ожидает из блока 25 управления памятью/обработки речевого сигнала следующий сигнал прерывания. Операции считывания данных адреса вывода речевого сигнала из двухпортовой памяти 24 и записи в нее этих данных осуществляются одновременно. Для предотвращения конфликтной ситуации для адресов, поступающих от центрального процессора 23 и от блока 25 управления памятью/обработки речевого сигнала, между левыми и правыми адресными контактами A8 двухпортовой памяти 24 включен инвертор 30, как показано на фиг. 1. Использование инвертора 30 предотвращает одновременный доступ центрального процессора 23 и блока 25 управления памятью/обработки речевого сигнала к одной и той же ячейке двухпортовой памяти 24. На фиг. 4 левые адресные контакты A0-A7 двухпортовой памяти 24 соединены с центральным процессором 23 через линию ADD-L адреса. Правые адресные контакты A0-A8 двухпортовой памяти 24 соединены с блоком 25 управления памятью/обработки речевого сигнала через линию ADD-R адреса.

Как видно из приведенного описания, согласно настоящему изобретению для выдачи фиксированных и редактированных речевых сообщений обычно распределяют все 128 каналов речевого обслуживания. Например, 28 из всех 128 каналов речевого обслуживания могут использоваться для выдачи редактированных речевых сообщений, а остальные 100 каналов могут использоваться для выдачи фиксированных речевых сообщений. Поэтому устройство для выдачи сообщений согласно настоящему изобретению увеличивает эффективность использования каналов речевого обслуживания по сравнению с известным устройством.

Предпочтительные варианты осуществления настоящего изобретения были описаны в качестве иллюстрации, специалистам в данной области понятно, что возможны разные модификации изобретения, не затрагивающие его сути и объема.

Устройство для выдачи сообщений для системы коммутации содержит главный процессор для управления выводом речевых сообщений для всех каналов речевого обслуживания, двухпортовую память с произвольной выборкой для хранения данных адреса вывода речевого сигнала, центральный процессор, реагирующий на сигнал прерывания, для записи данных адреса вывода речевого сигнала в двухпортовую память с произвольной выборкой и выдачи данных о состоянии вывода речевого сигнала, общую память для передачи данных команды вывода речевого сигнала от главного процессора в центральный процессор и передачи данных о состоянии вывода речевого сигнала из центрального процессора в главный процессор, память фиксированного речевого сигнала для хранения данных фиксированных речевых сообщений, память редактированного речевого сигнала для хранения данных редактированных речевых сообщений и блок управления памятью/обработки речевого сигнала для подачи в центральный процессор сигнала прерывания, считывания данных адреса вывода речевого сигнала из двухпортовой памяти с произвольной выборкой, подачи считанных данных адреса вывода речевого сигнала в память фиксированного речевого сигнала или память редактированного речевого сигнала, преобразования параллельных данных сигнала речевого сообщения, полученных из памяти фиксированного речевого сигнала или памяти редактированного речевого сигнала в последовательные данные и передачи последовательных преобразованных данных через субмагистраль в устройство временной коммутации коммутационной системы. 7 з.п. ф-лы, 4 ил., 2 табл.

| US, патент, 5127004, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-03-10—Публикация

1995-11-02—Подача