Настоящее изобретение относится к системе коммутации, более конкретно к устройству и способу коммутации для асинхронного режима передачи (АРП).

В общем случае коммутатор асинхронного режима передачи (АРП-коммутатор), который асинхронно пересылает информацию различных видов, имеет преимущество, состоящее в том, что скорость пересылки информации весьма велика по сравнению со скоростью в известном синхронном режиме передачи. Соответственно в последнее время исследовалось применение АРП-коммутатора в широкополосной ISDN цифровой сети с комплексными услугами (ISDN) и соответственно создалась новая тенденция к стандартизации различных интерфейсов.

Однако внедрение высокоскоростной передачи информации во всех уже оборудованных сетях связано с их заменой на сети АРП, что требует огромных затрат.

Соответственно предложено использовать совместно сеть с мультиплексированием за счет временного разделения каналов (МВРК) и сеть АРП. Однако поскольку способ взаимодействия сети режима МВРК с сетью АРП до сих пор не разработан, создание высокоскоростной информационной сети является трудной задачей.

Задачей настоящего изобретения является создание устройства и способа коммутации АРП для коммутационной системы, которая работает совместно с сетью МВРК и сетью АРП.

Также задачей настоящего изобретения является создание устройства и способа коммутации АРП, обеспечивающих возможность приема как можно большего количества магистральных линий связи при идентичной скорости преобразования данных.

Для достижения указанного технического результата устройство коммутации для АРП включает в себя множество блоков соединения с магистральными линиями связи, соединенных с сетью с МВРК; блок соединения АРП, соединенный с сетью АРП; и блок преобразования посылок АРП, обеспечивающий преобразование данных магистральных линий связи, вводимых через блоки соединения с магистральными линиями связи, в посылку АРП и выдачу посылки АРП в блок соединения АРП, а также преобразование посылки АРП, вводимой через блок соединения АРП, данные магистральных линий связи и выдачу данных магистральных линий связи в блоки соединения с магистральными линиями связи.

Указанный технический результат достигается в соответствии с изобретением в заявленном способе коммутации для АРП, включающем этапы инициализации операции для установки таблицы связей, таблицы управления буферами посылок и таблицы заголовков посылок, обеспечиваемых в блоке памяти; считывания номера буфера посылки путем обращения к таблице связей в блоке памяти в соответствии с номером магистральной линии связи и номером временного интервала (слота), которые подаются из блока генерации сигналов состояния/привязки по времени; считывания бита сегмента записи, указателя записи и эффективной длины полезной нагрузки из таблицы управления буферами посылок путем использования номера буфера посылки, считанного на предыдущем этапе заполнения полезной нагрузки посылки путем записи мультиплексированных данных магистральных линий связи в соответствующем буфере посылки, пока указатель записи и эффективная длина полезной нагрузки, которые были считаны, не примут идентичное значение; записи соответствующего номера буфера посылки в очередь, когда полезная нагрузка посылки заполнена; считывания из очереди номера буфера посылки, в котором заполнена полезная нагрузка посылки, и считывания соответствующего заголовка посылки из таблицы заголовков посылок на основе номера буфера посылки, который был считан; и передачи заголовка посылки и заполненной полезной нагрузки посылки через блок FIFO, обеспечивающий обработку данных в порядке поступления в коммутационную систему с АРП.

Изобретение поясняется ниже на примере осуществления со ссылками на чертежи, на которых одинаковые ссылочные позиции относятся к одинаковым элементам:

фиг.1 - блок-схема, иллюстрирующая АРП коммутатор для коммутационной системы согласно первому варианту осуществления настоящего изобретения;

фиг.2А-2С - диаграммы, иллюстрирующие соответствующие кадры данных магистральных линий связи;

фиг.3А-3D - диаграммы, иллюстрирующие данные, мультиплексированные с временным разделением каналов, на протяжении одного временного интервала;

фиг.4 - диаграмма, иллюстрирующая таблицу связей;

фиг.5 - иллюстрация таблицы управления буферами посылок;

фиг.6 - иллюстрация таблицы заголовков посылок;

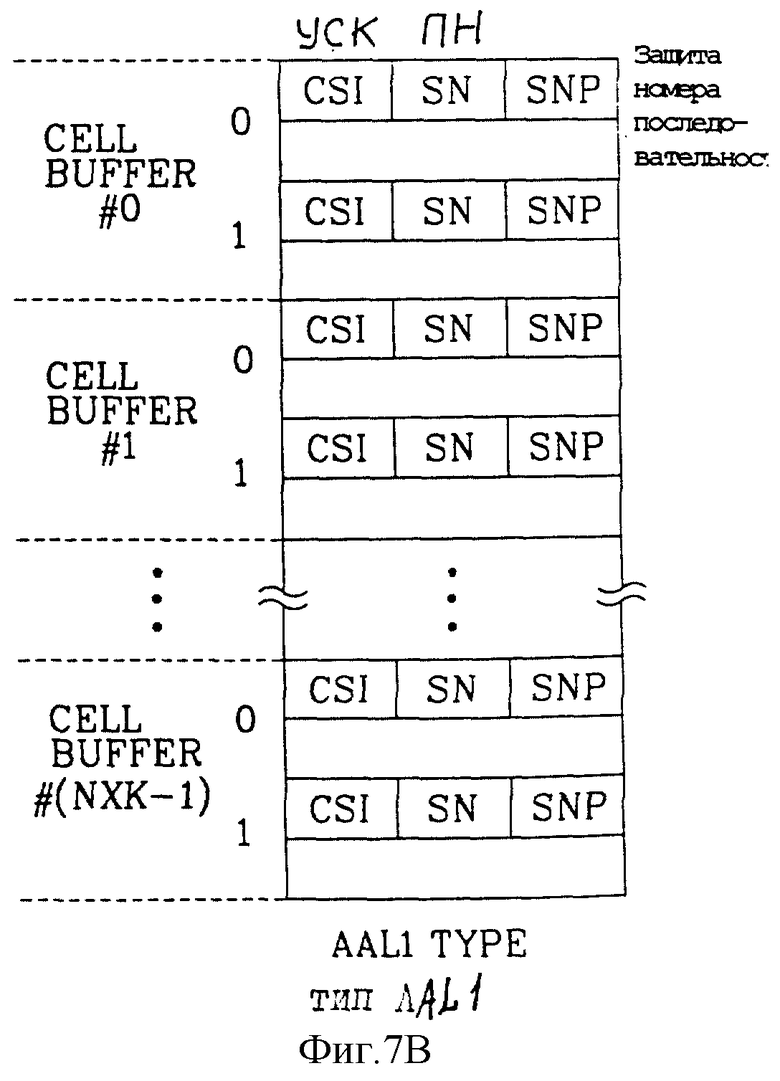

фиг.7А-7В - диаграммы, показывающие буферы посылок;

фиг.8 - диаграмма, показывающая очередь из номеров буферов заполненных посылок;

фиг.9 - диаграмма, иллюстрирующая распределения памяти блока памяти на фиг.1;

фиг.10 - блок-схема, иллюстрирующая операцию преобразования блока преобразования данных на фиг.1;

фиг.11 - блок-схема, иллюстрирующая устройство коммутации для АРП коммутационной системы согласно второму варианту осуществления настоящего изобретения; и

фиг.12А-12D - диаграммы, показывающие кадры между блоком мультиплексирования/демультиплексирования данных и блоком хранения данных на фиг.11.

На фиг.1 показано устройство коммутации для АРП согласно первому варианту осуществления настоящего изобретения.

Как показано на чертеже, блок последовательно-параллельного преобразования 10 преобразует последовательные данные, которые принимаются через множество магистральных линий связи в соответствии с сигналом кадровой синхронизации, в 8-разрядные параллельные данные и, наоборот, и выводит результирующие данные в магистральные линии связи. Множество магистральных линий связи соответственно соединены с множеством блоков соединения с магистральными линиями связи системы мультиплексирования с временным разделением каналов (МДРК магистралями).

Блок мультиплексирования/демультиплексирования данных 11 выполняет операцию мультиплексирования с временным разделением каналов для параллельных данных, подаваемых из блока последовательно-параллельного преобразования 10. Блок преобразования данных 12 запоминает 8-разрядные данные МВРК, которые подаются из блока мультиплексирования/демультиплексирования 11 данных в блоке памяти 15 в виде посылки через интерфейс памяти 14 в соответствии с сигналом кадровой синхронизации, или считывает посылку, запомненную в блоке памяти 15, и выводит результирующие данные в блок мультиплексирования/демультиплексирования 11 данных. Блок генерации 13 сигналов состояния/привязки по времени генерирует сигнал кадровой синхронизации, тактовый сигнал, сигнал состояния, номер магистрали и номер временного интервала (слота) при управлении от центрального процессора (ЦП).

Блок управления 16 передачей посылок формирует АРП посылку путем считывания посылок и информации в заголовках, запомненных в блоке памяти 15, и передает посылку в блок соединения АРП через блок 17 обработки данных в порядке поступления (FIFO), либо запоминает посылку АРП, которая принимается через блок FIFO 18, в блоке памяти. 15. Здесь следует отметить, что пара блоков FIFO 17, 18 по существу соединена с блоком соединения АРП. Интерфейс 14 памяти согласует сигналы, которые передаются в блок памяти 15 через блок преобразования 12 данных, блок управления 16 передачей посылок и интерфейс 19 ЦП, причем блок памяти 15 содержит таблицу связей, таблицу управления буферами посылок, таблицу заголовков посылок, буфер посылки и очередь, которые распределяются в соответствии с номером магистрали и номером временного интервала, как показано на фиг.9. Вдобавок отметим, что интерфейс 19 ЦП обеспечивает сопрежение сигналов между ЦП и интерфейсом 14 памяти.

Ниже описана работа устройства коммутации для АРП, предназначенного для системы, согласно первому варианту осуществления настоящего изобретения.

Как показано на фиг.1, в соответствии с сигналом кадровой синхронизации, подаваемым от блока генерации 17 сигналов состояния/привязки по времени, блок последовательно-параллельного преобразования 10 выводит каждый элемент данных магистральных линий связи, который подается через К магистралей (с O-й по К-ую), путем преобразования в 8-разрядные параллельные данные на каждом временном интервале. То есть, каждый элемент данных магистральной линии связи имеет вид кадра, как показано на фиг.2, в соответствии с сигналом кадровой синхронизации, подаваемым из блока генерации 13 сигналов состояния/привязки по времени. Поскольку в одном временном интервале существует К данных временного интервала (например, k каналов 1), К данных временного интервала посредством блока 10 последовательно-параллельного преобразования образуют кадр 8-разрядных параллельных данных.

Блок мультиплексирования/демультиплексирования 11 данных синхронизируется с помощью сигнала кадровой синхронизации и выполняет МВРК для К данных временного интервала, которые подаются из блока последовательно-параллельного преобразования 10 в одном временном интервале, как показано на фиг.3А-3С, для получения на выходе 8-разрядных МВРК данные, как показано на фиг.3D.

Затем в соответствии с сигналом состояния, генерируемым в блоке генерации 13 сигналов состояния/привязки по времени на одном временном интервале, приводится в действие механизм состояния блока преобразования данных 12 и выполняется запоминание 8-разрядных данных, которые были подвергнуты операции МВРК в блоке мультиплексирования/демультиплексирования данных 11, в соответствующем буфере посылки согласно соответствующему номеру магистрали и номеру временного интервала. То есть, блок преобразования данных 12 выполняет переход, иллюстрируемый блок-схемой на фиг.10, за время которого один временной интервал делится на К, и запоминает данные, которые были мультиплексированы, в соответствии с номером магистрали и номером используемого канала.

Ниже со ссылками на фиг.10 описана операция запоминания блоком 12 преобразования данных мультиплексированных 8-разрядных данных в соответствующем буфере посылки.

В начальном состоянии, как показано на фиг.9, ЦП выполняет инициализацию, посредством которой в блоке памяти 15 обеспечиваются таблицы, такие как таблица связей, таблица управления буферами посылок и таблица заголовков посылок (101), и приводит механизм состояния в блоке преобразования 12 данных в состояние ожидания, тем самым переводя в состояние ожидания блок преобразования 12 данных.

Затем блок преобразования 12 данных обращается к таблице связей (фиг.4) в соответствии с номером магистрали и номером временного интервала (номером канала), которые подаются из блока генерации 13 сигналов состояния/привязки по времени каждый нарастающий фронт тактового сигнала, который составляет один временной интервал, поделенный на К. Например, блок преобразования 12 данных считывает разряд Y установки вызовам и номер #1 буфера посылки, которые соответствуют каналу 1 магистрали #0 (103).

Если разряд (Y) установки вызова, который был считан, установлен в "I", то блок преобразования 12 данных считывает из таблицы управления буферами посылок (фиг.5) разряд сегмента записи РСЕГЗ, указатель записи УКЗЗ и эффективную длину полезной нагрузки ДПН путем использования в качестве адреса доступа (103, 105) номера #1 буфера посылки, который был считан из таблицы связей. Если разряд Y установки вызова установлен в "О", то блок преобразования 12 возвращается в состояние ожидания.

Следует отметить, что случай, когда разряд Y установки вызова установлен в "I", означает, что в данных соответствующего временного интервала (канал 1) установлен вызов.

Затем блок преобразования данных 12 сравнивает указатель записи УКЗЗ с эффективной длиной полезной нагрузки ДПН, которая была считана. Если значения УКЗЗ и ДПН отличаются друг от друга, то блок преобразования данных записывает мультиплексированные данные (канал 1 магистрали #0), которые подаются из блока 11 мультиплексирования/демультиплексирования данных, в буфере #1 посылки (111), увеличивает на "1" указатель записи УКЗЗ путем обращения к таблице управления буферами посылок (фиг.5) и затем повторно выполняет операцию после состояния ожидания (113, 115). Здесь причиной увеличения указателя записи УКЗЗ на "1" является необходимость записать следующие мультиплексированные данные в оставшуюся область записи буфера #1 посылки.

Когда значения указателя записи УКЗЗ и эффективной длины полезной нагрузки ДПН идентичны друг другу, блок преобразования данных 12 записывает мультиплексированные данные (канал 1 магистрали #0) в буфере #1 досылки, чтобы тем самым заполнить 48-разрядную полезную нагрузку посылки (117), и путем повторного обращения к таблице управления буферами посылок преобразует разряд сегмента записи РСЕГЗ, а также устанавливает указатель записи УКЗЗ в "О", чтобы подготовить тем самым новый буфер #1 посылки (119).

На фиг.7А и 7В показаны соответственно буферы посылок необработанного типа и буферы посылок типа AAL1 (уровня 1 адаптации АРП). В этом описании буфер посылки типа AAL1 объясняется как удобный пример.

Блок 12 преобразования данных записывает порядковый номер ПН в первый байт буфера #1 посылки, который определяется соответствующим разрядом сегмента записи РСЕГЗ таблицы управления буферами посылок (121), затем записывает в очередь, как показано на фиг.8, номер буфера #1 заполненной посылки (123) и таким образом заканчивает операцию, записывая мультиплексированные данные (канал 1), относящиеся к магистрали #0. Здесь следует отметить, что если буфер посылки относится к посылкам необработанного типа, то ПН не записывается.

И затем в соответствии с вышеописанным процессом завершается операция записи, посредством которой канал 1 каждой из всех других магистралей, от магистрали #1 до магистрали #k-l мультиплексируются в течение данного временного интервала.

Когда операция записи мультиплексированных данных завершена, блок управления 16 передачей посылок идентифицирует номер буфера завершенной посылки путем считывания очереди блока памяти 15 на основе указателя записи УКЗЗ, который подается из блока преобразования 12 данных и указателя считывания УКЗСЧ, которым управляет сам блок управления 16, и увеличивает на "1" указатель считывания УКЗСЧ.

Затем блок управления 16 передачей посылок считывает заголовок посылки из 5 байтов, соответствующий номеру буфера посылки, из таблицы заголовков посылок, показанной на фиг.6, затем считывает 48-разрядную полезную нагрузку посылки из буфера посылки путем считывания разряда сегмента посылки РСЕГСЧ из таблицы управления буферами посылок и преобразует разряд сегмента считывания РСЕГСЧ, в то время как интерфейс памяти 14 выполняет сопрежение сигналов, вводимых в блок памяти 15 и выводимых из него, как это требуется для блока преобразования 12 данных, блока управления передачей посылок 16 и интерфейса 19 ЦП. Соответственно блок управления 17 передачей посылок объединяет 5-байтовый заголовок посылки и 48-байтовую полезную нагрузку посылки и подает 53-байтовый пакет фиксированной длины (посылка АРП) в блок соединения АРП через блок 17 FIFO. Наоборот, посылка АРП, которая принимается через блок соединения АРП и блок 18 FIFO, запоминается в блоке памяти 15 в соответствии с блоком передачи посылок, в то время как сохраненная посылка АРП считывается побайтно блоком преобразования данных 12, а данные, которые были считаны, демультиплексируются в параллельные данные в блоке 11 мультиплексирования/демультиплексирования данных. Демультиплексированные таким образом 1-байтные параллельные данные преобразуются в последовательные данные в блоке последовательно-параллельного преобразования 10 и выводятся через К магистралей в соответствующий блок соединения магистралей.

Как описано выше, согласно первому варианту осуществления настоящего изобретения данные МВРК, введенные через множество магистралей, преобразуются в данные АРП и подаются в коммутационную систему АРП, а посылка АРП, которая подается из коммутационной системы АРП, преобразуется в данные МВРК для соответствующего вывода во множество магистралей. В результате возможна совместная работа сети МВРК и сети АРП, что создает высокоскоростную сеть.

На фиг.11 показан АРП-коммутатор для коммутационной системы согласно второму варианту осуществления настоящего изобретения, в котором между блоком 11 мультиплексирования/демультиплексирования данных и блоком преобразования 12 данных дополнительно подсоединен блок хранения 20 данных, который играет роль буфера.

Блок хранения 20 данных, который делится на первую и вторую группы, выравнивает разность рабочих скоростей двух блоков 11 и 12. Также первая и вторая группы используются блоками 11 и 12 попеременно.

Блок преобразования 12 данных обрабатывает N байт данных за один цикл в соответствии с сигналом синхронизации преобразования, выдаваемом из блока генерации 17 сигналов состояния/привязки по времени. Следует отметить, что цикл сигнала синхронизации преобразования в N раз больше, чем у сигнала кадровой синхронизации, как показано на фиг.12.

Ниже описана работа устройства коммутации для АРП, предназначенного для коммутационной системы согласно второму варианту осуществления настоящего изобретения.

Сначала последовательные данные, которые вводятся во множество магистралей, преобразуются в блоке последовательно-параллельного преобразования 10 в параллельные данные в соответствии с сигналом кадровой синхронизации, и блок 11 мультиплексирования/демультиплексирования данных выполняет операцию МВРК для параллельных данных в каждой магистрали. Мультиплексированные таким образом данные запоминаются в блоке хранения 20 данных в соответствии с первоначально использованными номером магистрали, номером временного интервала и номером кадра. Здесь следует отметить, что номер кадров повторяется от 0 до N-1 на основе N кадров (опорный кадр) сигнала кадровой синхронизации и таким образом создается одна группа.

Затем блок 11 мультиплексирования/демультиплексирования данных и блок преобразования 12 данных обращаются к первой и второй группам блока хранения 20 данных попеременно. В частности, данные, которые подаются из блока 11, записываются в первой группе в течение периода опорного кадра, в то время как магистральные данные из N байт, запоминаемые во второй группе, считываются блоком преобразования 12 данных. То есть, блок преобразования 12 данных приводится в действие сигналом синхронизации преобразования (опорный кадр) в виде одного цикла, а механизм состояния обрабатывает магистральные данные в объеме N байтов на каждом одном цикле временного интервала.

Здесь количество магистральных данных TDN, которые подаются в блок преобразования 12 данных в течение одного цикла (опорного кадра) сигнала синхронизации преобразования, может быть представлено следующим уравнением (1).

TDN = количество магистралей х количество временных интервалов в кадре х N (1)

Кроме того, количество временных интервалов TSN в опорном кадре может быть выражено следующим образом:

TSN = количество временных интервалов в кадре х N (2)

В вышеуказанных уравнениях (1) и (2) N указывает количество кадров в опорном кадре.

С другой стороны, во втором варианте осуществления настоящего изобретения количество магистральных данных TDBN N-байтного блока, которые подаются в блок преобразования 12 данных в течение опорного кадра, может быть выражено следующим уравнением:

TDBN=TDN/N = количество магистралей × количество временных интервалов в кадре (3)

Кроме того, в случае первого варианта осуществления изобретения, количество магистральных данных, которое должно быть обработано за один временной интервал, может быть также получено путем использования вышеуказанных уравнений (1) и (2) следующим образом:

TDN/TSN = количество магистралей (4)

Вдобавок, во втором варианте количество данных из N-байтных блоков, которое должно быть обработано за один временной интервал, может быть получено путем использования уравнений (2) и (3) следующим образом:

TDBN/TSN = количество магистралей (5)

Что же касается объема данных, обрабатываемых механизмом состояния в течение одного временного интервала по отношению к количеству магистралей из уравнений (4) и (5), то очевидно, что устройство согласно второму варианту обрабатывает лишь 1/N от всего количества магистралей по сравнению с первым вариантом. Это указывает на то, что, если механизм состояния по каждому (первому или второму) варианту обрабатывает один и тот же объем магистралей в течение одного временного интервала, устройство согласно второму варианту может содержать в N раз большее количество магистралей, чем в первом варианте. Согласно второму варианту настоящего изобретения можно умножить количество магистралей на N без увеличения скорости обработки механизма состояния.

Кроме того, когда блок преобразования 12 данных обрабатывает магистральные данные, где установлен вызов, количество магистралей может быть увеличено более чем в N раз. Это может сопровождаться блокированием некоторого количества вызовов.

С другой стороны, посылка АРП, которая подается из коммутационной системы АРП через блок соединения АРП и блок 18 FIFO запоминается в блоке памяти 15 в виде посылки в соответствии с управляющими воздействиями блока передачи 16 посылок, а посылка, запомненная в блоке памяти 15, считывается по N байт блоком преобразования данных 1.2, для записи в соответствующую область согласно номеру магистрали и номеру канала приемной части блока хранения 20 данных.

Блок 11 мультиплексирования/демультиплексирования данных считывает магистральные данные побайтно из блока хранения данных 20, в соответствии с номером магистрали, номером канала и номером кадра, а данные, которые были считаны, демультиплексируются в параллельные данные. Демультиплексированные таким образом однобайтные параллельные данные преобразуются в последовательные данные в блоке 10 последовательно-параллельного преобразования и выводятся в блок соединения с магистральными линиями связи через соответствующие магистрали.

Как описано выше, устройство коммутации для АРП согласно настоящему изобретению обеспечивает преимущество, заключающееся в возможности совместной работы сети МВРК и сети АРП путем преобразования данных МВРК, подаваемых через множество блоков соединения с магистральными линиями связи, в посылку АРП и вывода посылки в блок соединения АРП, и преобразования посылки АРП, подаваемой через блок соединения АРП, и вывода результата преобразования в блоки соединения с магистральными линиями связи, в результате чего в конечном счете создается высокоскоростная сеть. Кроме того, настоящее изобретение обеспечивает возможность возрастания количества магистралей более чем в N раз без увеличения скорости обработки блока преобразования данных.

Специалистам в данной области техники видно, что в устройстве преобразования посылок АРП для коммутационной системы, соответствующей настоящему изобретению, можно выполнить различные модификации и изменения без отклонения от сущности или объема изобретения. Таким образом, подразумевается, что настоящее изобретение охватывает модификации и изменения данного изобретения, при условии, если они находятся в рамках объема формулы изобретения и ее эквивалентов.

Изобретение относится к устройству коммутации для синхронного режима передачи (АРП) для коммутационной системы. Технический результат – обеспечение возможности приема как можно большего количества магистральных линий связи при идентичной скорости преобразования данных – достигается тем, что устройство подсоединено между множеством блоков соединения с магистральными линиями связи, соединенных с сетью, использующей мультиплексирование путем временного разделения каналов (МВРК), и блоком соединения АРП, соединенным с сетью АРП. Блок преобразования посылок АРП преобразует магистральные данные, которые вводятся через блоки соединения с магистральными линиями связи в посылку АРП, которая вводится в блок соединения АРП, или преобразует посылку АРП, подаваемую из блока соединения АРП, в магистральные данные, которые выводятся в блоки соединения с магистральными линиями связи. 3 н. и 15 з.п. ф-лы, 12 ил.

| УСТРОЙСТВО АСИНХРОННОГО ПРЕОБРАЗОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2024205C1 |

| Коммутатор асинхронных импульсных каналов | 1977 |

|

SU650246A1 |

| US 5491691 А, 13.02.1996 | |||

| US 5636215 А, 03.06.1997 | |||

| DE 4332824 G1, 16.03.1995. | |||

Авторы

Даты

2004-07-20—Публикация

1998-12-18—Подача