Настоящее изобретение относится к масштабируемому устройству обработки данных, в частности к устройству хранения данных, содержащему один или более тонкопленочных приборов, которые формируют плоский слой, образованный несколькими сложенными в стопку подслоями одинакового размера из тонкопленочного материала, причем эти подслои каждого тонкопленочного прибора содержат электроизоляционные и/или проводящие и/или полупроводниковые структуры и структуры со способностью хранить информацию, реализованные в тонкопленочном материале в подслое, при этом эти структуры точно подогнаны или электрически подключены к другим структурам этого вида в смежных подслоях в стопке, образующей тонкопленочный прибор, для реализации активных и пассивных элементов электронных схем или логических ячеек в тонкопленочном приборе, причем эти активные и пассивные схемные элементы в тонкопленочном приборе реализуются в трехмерной архитектуре и проходят через два или более ее подслоев, кроме того, эти схемные элементы электрически соединяются горизонтальными электропроводными структурами в одном или более подслоев и вертикальными электропроводными структурами, проходящими через один или более подслоев, при этом обеспечиваются два или более тонкопленочных прибора.

Известны устройства памяти (запоминающие приборы) в виде тонкопленочных схем, уложенных в стопку, в которых запоминающий прибор может дополнительно объединяться с процессорами для управления, возбуждения и адресации памяти, но с последующей реализацией в неорганических полупроводниковых материалах как в виде единых кристаллических жестких структур, так и/или тонкой пленки, выполненной на несущей подложке, которая с большим успехом может быть исключительно тонкой, к примеру, сформированной в виде пленок двуокиси кремния. Законченный запоминающий прибор со схемами обработки создается наложением слоев и зачастую с переносом тонкопленочных схем посредством специальных способов. Для того чтобы обеспечить соединения между слоями, используются сквозные соединения через набор отверстий в этих слоях и, возможно, объединяются с напылением металла для создания необходимых токовых дорожек. Далее, из международной заявки PCT/NO99/00180, которая принадлежит заявителю по настоящей заявке и которая приведена в качестве ссылки, известен интегральный масштабируемый прибор обработки данных, который образует законченный компьютер с массовой памятью и объединенным модулем процессора и памяти и в котором либо в отдельных процессорных слоях, либо в отдельных запоминающих слоях, или же в объединенных процессорных и запоминающих слоях предусмотрены так называемые интеллектуальные оперативные запоминающие устройства (ИОЗУ) (IRAM) и процессоры, которые реализуют функцию центрального процессора (ЦП) (CPU) компьютера или которые реализуют функции управления и связи в компьютере. Чтобы обеспечить короткозамкнутые дорожки, используются трехмерные электрические структуры для создания соединений между компонентами в отдельных слоях и между самими слоями. Весь прибор обработки данных выполняется на подложке, которая также содержит высокоскоростные схемы для целей управления и связи, которые реализуются неорганическими полупроводниковыми материалами с помощью обычной технологии, тогда как различные слои прибора обработки данных или в ином случае все они реализуются в тонкопленочной технологии независимо от того, содержат ли они процессоры или память.

Можно упомянуть примеры и других аналогов. Патент США 5714768 (Ovshinsky et al.) рассматривает вычислительный прибор с процессором и частной матрицей памяти в тонкопленочной структуре, установленной на этом процессоре наверху прибора, а также использование носителя памяти на базе различных неорганических материалов, которые могут достигать различных значений электрического сопротивления в ответ на выбранные электрические входные сигналы в отдельные запоминающие ячейки. В частности, Ovshinsky et al. рассматривают специальные запоминающие элементы в виде так называемых запоминающих блоков на элементах Овшинского, которые основаны на электрическом фазовом переходе и выполнены из неорганических халькогенидных составов в качестве переключателей. Каждый запоминающий элемент считается одним блоком и окружается и взаимно изолируется изолирующим материалом, к примеру из SiO2 или Si3N4. Эти запоминающие элементы размещаются в плоской матричной структуре, которая с одной стороны соединяется подлежащей сеткой электродных структур, причем электродная структура в каждой сетке ориентирована перпендикулярно к электродной структуре другой сетки. Двумерные запоминающие матрицы этого вида могут теперь складываться в стопку с должной взаимной изоляцией для образования интегрированной по вертикали запоминающей структуры на подложке, которая может быть логическим обрабатывающим прибором, содержащим электронную схему. Ovshinsky et аl. не делают никаких намеков или предположений по поводу складывания в пакет тонкопленочных приборов, выполненных из тонкопленочных подслоев тонкопленочного материала одинакового размера, или в которых тонкопленочные приборы содержат как схемные области с активными цепями, так и запоминающие области с запоминающими модулями, реализованными с помощью подслоев из тонкопленочного материала с функциональными характеристиками, соответствующими назначению. Кроме того, ферроэлектрический запоминающий прибор, в котором двумерная матрица запоминающих ячеек собрана в пакет для образования волюметрического запоминающего прибора, известен из уровня техники, например из патента США 5329485 (Isono et аl.) и патента США 5375085 (Gnade et al.). Предложено также использование ферроэлектрических полимерных материалов для памяти со стиранием информации, в частности выполнения, основанные на использовании сополимеров поли(винилиден-хлорида) или поли(винилиден-трифторэтилена), например в IBM Technical Disclosure Bulletin 37:421-424, 11 (1994). Эти полимеры могут быть получены как очень тонкие пленки, а носитель памяти - как непрерывный слой тонкопленочного материала с наборами параллельных проводящих электродов, нанесенных на каждую сторону и ориентированных взаимно перпендикулярно. Такие двумерные пассивные ферроэлектрические матрицы могут складываться в стопку для образования трехмерной структуры. Однако ни одна из вышеперечисленных публикаций не рассматривает тонкопленочные приборы, содержащие подслои с функциональными характеристиками, которые позволяют реализовать как активные цепи, так и пассивные запоминающие модули в тонкопленочных приборах.

Наконец, трехмерные структуры с памятью и процессором, основанные на перенесенных тонкопленочных схемах, рассматриваются в публикации международной заявки WO 95/09438 (Zavracky et al.) и патенте США 5656549 с теми же изобретателями, причем обе публикации основаны на одной и той же патентной заявке США с серийным номером 130033, поданной 30 сентября 1993, которая была отозвана из рассмотрения экспертизой. В частности, эти публикации рассматривают схемные слои памяти и процессора, сложенные в стопку или перемежающиеся для образования трехмерной структуры, причем отдельные функциональные элементы этих схем изготовлены нанесением рисунка на тонкопленочные материалы с помощью обычных технологий плоскостных схем и взаимного соединения по вертикали посредством, к примеру, металлических соединений, проходящих через эти структуры.

Хотя известные приборы для обработки данных и хранения, основанные на тонкопленочной технологии, и имеют некоторые преимущества в отношении скорости и различных функций, они все же очень дороги для хранения данных и оказываются, в частности, сложными для производства. Эффективное управление памятью требует далее значительной производительности обработки: к примеру, для управления, связи и адресации выделяются схемы, которые часто назначаются большому запоминающему блоку или нескольким отдельным запоминающим блокам с большой емкостью памяти.

Объектом настоящего изобретения является масштабируемое устройство обработки данных, в частности, устройство хранения данных, которое относительно просто и недорого в изготовлении и которое в принципе позволяет почти неограниченное масштабирование емкости хранения данных без усложнения управления и работы запоминающего блока.

Масштабируемое устройство обработки данных реализовано, в частности, как устройство хранения данных практически по тонкопленочной технологии, что обеспечивает воплощение поддерживающих функций для управления и адресации запоминающих блоков, реализованных по тонкопленочной технологии, причем электронные схемы для упомянутых целей интегрируются с запоминающими блоками в тонкопленочном приборе.

Настоящее изобретение также реализовано в виде волюметрического прибора хранения данных с большой плотностью хранения, имеющего быстрый доступ к данным и высокую скорость передачи данных, опционально объединенного с параллельным вводом данных в запоминающем данные устройстве и быстрым параллельным считыванием данных из него.

Масштабируемое устройство обработки данных согласно изобретению отличается тем, что каждый тонкопленочный прибор содержит, по меньшей мере, одну запоминающую область, которая образует, по меньшей мере, один матричный адресуемый запоминающий блок, каждый с носителем памяти в подслое в контакте с первым набором электродов в виде полосообразных электропроводных структур или электродных структур и со вторым набором электродов в виде соответствующих электродных структур, ориентированных по существу перпендикулярно электродным структурам первого набора электродов, причем эти наборы электродов соответственно образованы другими подслоями, примыкающими к упомянутому подслою носителя памяти с каждой его стороны, посредством чего адресуемые запоминающие ячейки создаются в носителе памяти на пересечениях между электродными структурами в первом и втором наборе электродов, каждый тонкопленочный прибор содержит также схемные области, которые образуют электронную тонкопленочную схему для управления, возбуждения и адресации запоминающих ячеек в, по меньшей мере, одном запоминающем блоке, причем упомянутая электронная схема соединяется с электродными структурами в соответствии с первым и вторым наборами электродов в токовых дорожках памяти, которые образуются как электропроводные структуры, по существу, в тех же самых подслоях, где образованы наборы электродов, и каждый тонкопленочный прибор имеет соответствующий интерфейс к каждому другому тонкопленочному прибору в устройстве, причем упомянутые интерфейсы реализуются связными (коммуникационными) и сигнальными линиями и поддерживающей схемой для обработки, а упомянутые линии снабжены соответствующими предназначенными для интерфейсов областями в тонкопленочном приборе.

В предпочтительном выполнении устройства согласно изобретению носитель памяти в, по меньшей мере, одном запоминающем блоке содержит материалы, выбранные среди молекулярных материалов в виде мономеров, олигомеров или полимеров, углеродосодержащие материалы в неорганическом или органическом виде, либо наложение или смесь из таких материалов. В этой связи предпочтительно, чтобы носитель памяти содержал запоминающий материал, который в запоминающей ячейке обеспечивает нелинейную характеристику ток/напряжение, причем упомянутая нелинейная характеристика ток/напряжение генерируется неорганическими или органическими диодами либо материалом с пороговым переключением.

В другом предпочтительном выполнении устройства согласно изобретению носитель памяти содержит переключаемый материал, который является энергонезависимым материалом, выбранным соответственно как ферроэлектрический материал или органический комплекс с переносом заряда, либо носитель памяти может быть переключаемым и иметь нелинейную характеристику ток/напряжение.

Электронная схема согласно изобретению может предпочтительно содержать неорганические и/или органические полупроводниковые материалы.

В предпочтительном выполнении устройства по изобретению интерфейсная область в, по меньшей мере, одном тонкопленочном приборе образована интегрированной в краевом положении этого прибора или этих приборов, причем упомянутые краевые положения в случае, если упомянутое устройство содержит более одного тонкопленочного прибора, взаимно совмещаются. В этой связи предпочтительно, чтобы интерфейсная область в краевом положении дополнительно содержала интерфейс ввода/вывода для соответствующего тонкопленочного прибора или, опционально, для устройства в целом и воплощала функции для передачи данных и сигналов с внешних и/или периферийных приборов.

Предпочтительно в устройстве согласно изобретению тонкопленочный прибор или собранная в стопку конфигурация таких приборов может быть образована на подложке, которая содержит активные электронные схемы для воплощения дополнительных функций управления, возбуждения и связи в устройстве, при этом каждый тонкопленочный прибор соединяется со схемой над отдельной интерфейсной областью, которая в каждом случае проходит в вертикальном направлении через тонкопленочные приборы, которые расположены между рассматриваемым тонкопленочным прибором и подложкой. В этой связи предпочтительно, чтобы подложка содержала интерфейсную часть, которая проходит, по существу, горизонтально в подложке и параллельно образованному над ней тонкопленочному прибору или смежно с ним и которая электрически соединяется с интерфейсными частями в тонкопленочном приборе или в тонкопленочных приборах, предусмотренных над этой подложкой и, в частности, предпочтительно, чтобы эта интерфейсная часть содержала далее интерфейс ввода/вывода, воплощающий функции для передачи данных и сигналов с внешних и/или периферийных приборов.

Также предпочтительно, чтобы подложка была изготовлена из полупроводникового материала, в частности из неорганического однокристального полупроводникового материала, и даже более конкретно, из такого однокристального полупроводникового материала как кремний, и, в частности, в этой связи предпочтительно, чтобы электронные схемы в подложке были реализованы по КМОП технологии. Далее, в этой связи предпочтительно, чтобы электрические соединения между электронными схемами в подложке и ее интерфейсной частью или над этой интерфейсной частью с интерфейсными областями в вышележащих тонкопленочных приборах были реализованы как металлические межсоединения, совместимые с КМОП схемами.

В предпочтительном выполнении устройства согласно изобретению, в котором это устройство содержит, по меньшей мере, два тонкопленочных прибора, эти тонкопленочные приборы имеют одинаковые размеры и взаимно совмещаются в стопке, составленной из них. В этой связи предпочтительно образовать, по меньшей мере, один разделительный слой, образованный между смежными тонкопленочными приборами и воплощающий либо раздельно, либо выборочно комбинации соответственно электрической, тепловой, оптической или механической изолирующей функции или выравнивающей функции, и чтобы при этом упомянутые интерфейсные области в соответствующих тонкопленочных приборах в каждом случае электрически соединялись по сквозным соединениям в соответствующем разделительном слое.

В другом предпочтительном выполнении устройства согласно изобретению оно содержит, по меньшей мере, два тонкопленочных прибора, которые взаимно сдвинуты в стопке, составленной из них.

Предпочтительно электрические соединения между тонкопленочными приборами и/или между опциональной подложкой проходят затем горизонтально и вертикально по ступеням в этой стопке со сдвигом.

Затем предпочтительно также образовать, по меньшей мере, один разделительный слой, вставленный между смежными тонкопленочными приборами, и раздельно или выборочно комбинации, воплощающие соответственно электрическую, тепловую, оптическую или механическую изолирующую функцию или выравнивающую функцию, и чтобы эти разделительные слои были образованы только в перекрывающейся части двух смежных тонкопленочных приборов, при этом интерфейсные области соответствующих тонкопленочных приборов предпочтительно образовать над открытыми поверхностными частями тонкопленочных приборов в их области расположения со сдвигом, чтобы разделительные слои между тонкопленочными приборами образовывали неразрывный слой без сквозных соединений для электрических соединений между отдельными тонкопленочными приборами.

Наконец, устройство согласно изобретению может быть предпочтительно выполнено на несущей подложке, сформированной из фольгообразного материала или такого жесткого материала как кремний, причем упомянутая несущая подложка в каждом случае располагается смежно с нижележащим тонкопленочным прибором в собранной в стопку конфигурации или, опционально, с предусмотренной подложкой с электронными схемами.

Масштабируемое устройство обработки данных, в частности устройство хранения данных, согласно изобретению будет теперь рассмотрено подробнее в нижеследующем описании со ссылкой на приведенные в качестве примера варианты выполнения и сопровождающие чертежи.

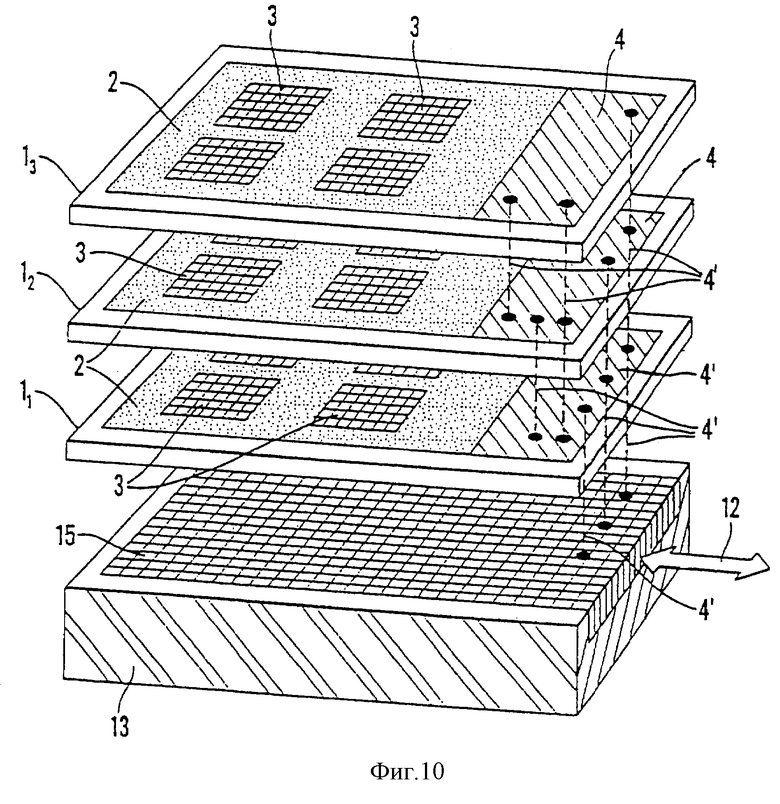

Фиг. 1а показывает вид сверху тонкопленочного прибора, используемого в устройстве согласно настоящему изобретению.

Фиг. 1b является сечением первого выполнения тонкопленочного прибора по фиг.1а, взятым вдоль линии А-А.

Фиг. 1с является сечением второго выполнения тонкопленочного прибора по фиг.1а, взятым вдоль линии А-А.

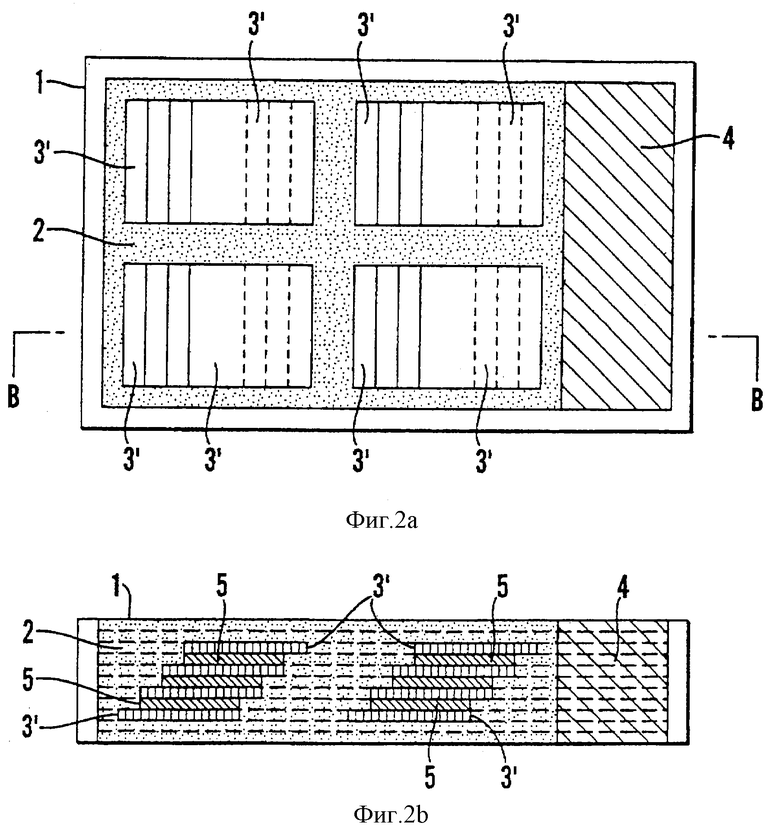

Фиг. 2а является видом сверху третьего выполнения тонкопленочного прибора, используемого в устройстве согласно настоящему изобретению.

Фиг.2b является сечением тонкопленочного прибора по фиг.2а, взятым вдоль линии В-В.

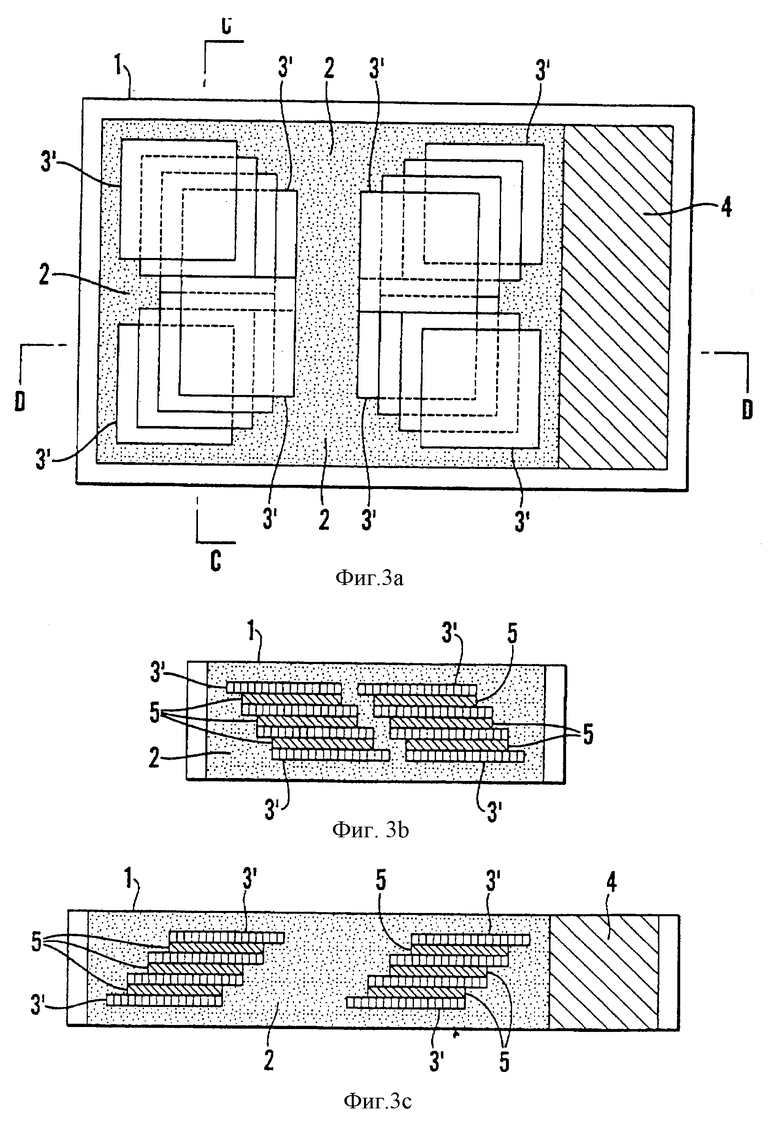

Фиг. 3а является четвертым выполнением тонкопленочного прибора, используемого в устройстве согласно настоящему изобретению.

Фиг.3b является сечением тонкопленочного прибора по фиг.3а, взятым вдоль линии С-С.

Фиг. 3с является другим сечением тонкопленочного прибора по фиг.3а, взятым вдоль линии D-D.

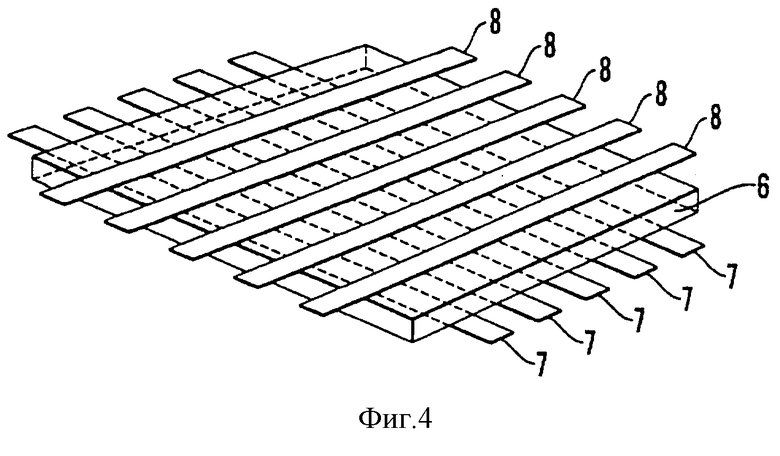

фиг. 4 схематически и в перспективе показывает выполнение матрично адресуемого запоминающего блока, когда он используется в тонкопленочном приборе по одной из фиг.1-3.

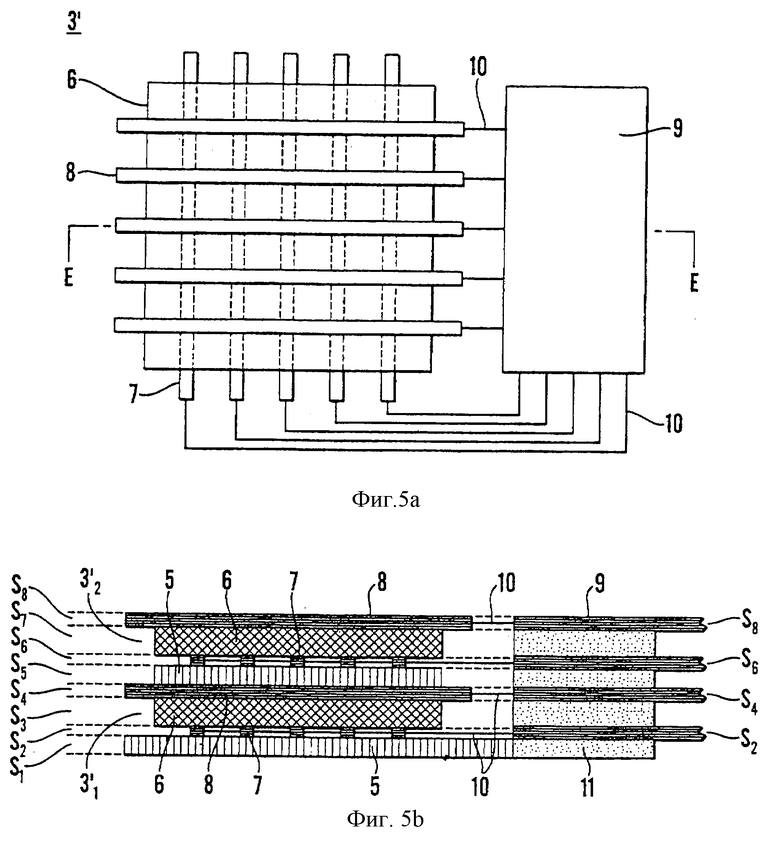

Фиг.5а является видом сверху матрично адресуемого запоминающего блока по фиг. 4, соединенного с активной электронной схемой в тонкопленочном приборе, показанном на одной из фиг.1-3.

Фиг. 5b является условным сечением запоминающего блока по фиг.5а, взятым вдоль линии Е-Е.

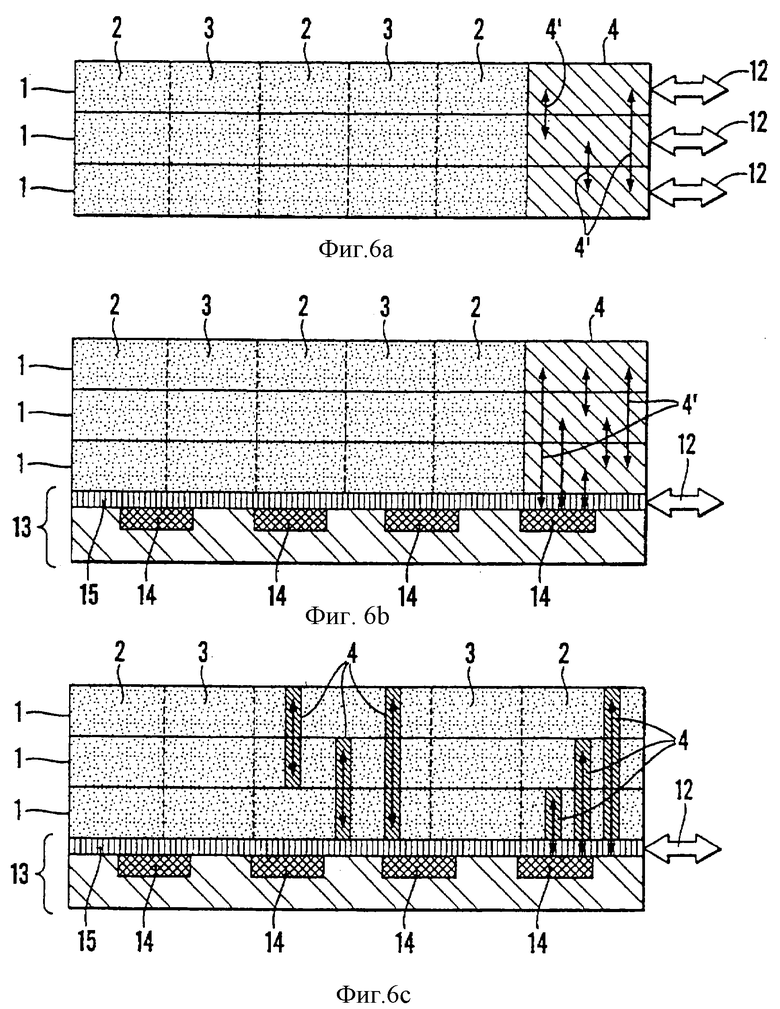

Фиг.6а представляет собой первое выполнение устройства согласно настоящему изобретению.

Фиг.6b представляет собой второе выполнение устройства согласно настоящему изобретению.

Фиг.6с представляет собой третье выполнение устройства согласно настоящему изобретению.

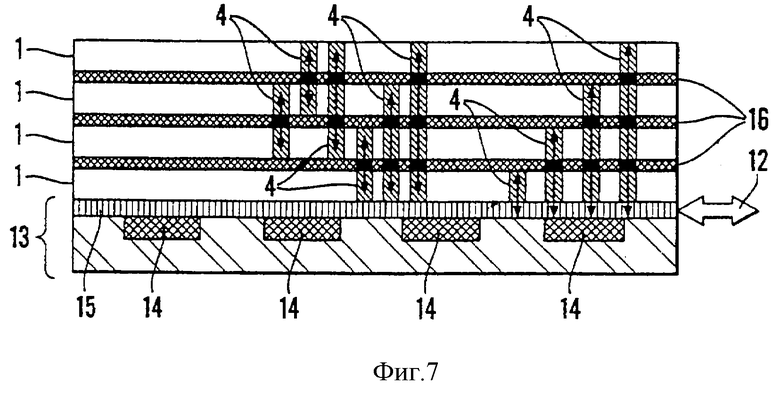

Фиг. 7 представляет собой четвертое выполнение устройства согласно настоящему изобретению.

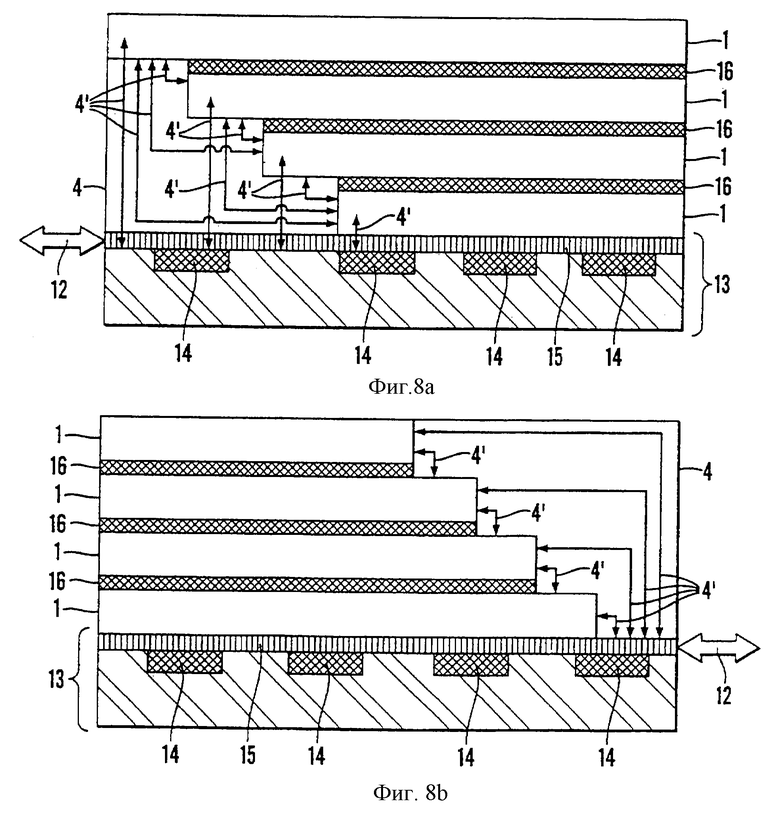

Фиг. 8а и 8b являются вариантами пятого выполнения устройства согласно настоящему изобретению.

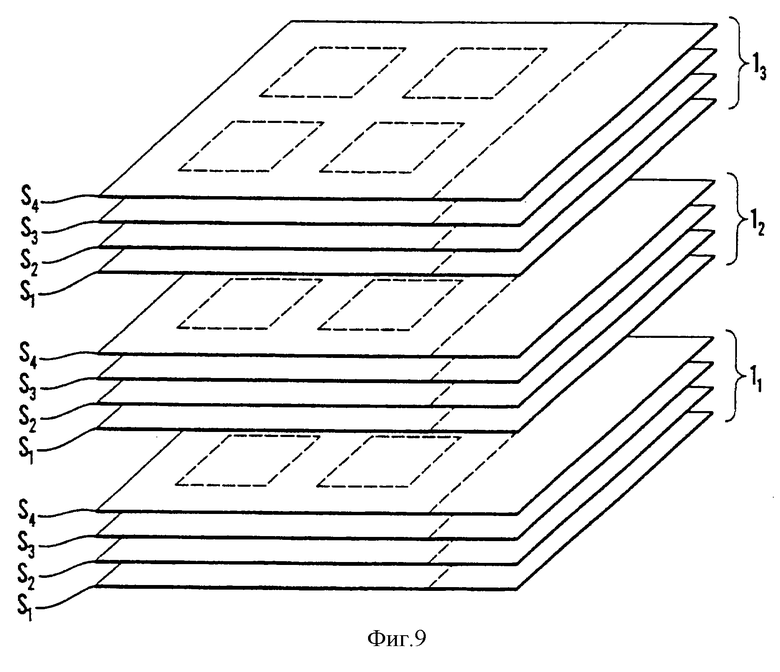

Фиг. 9 схематически показывает присоединение подслоев по тонкопленочной технологии в тонкопленочный прибор, используемый в настоящем изобретении, и соединение нескольких таких тонкопленочных приборов в устройство согласно изобретению.

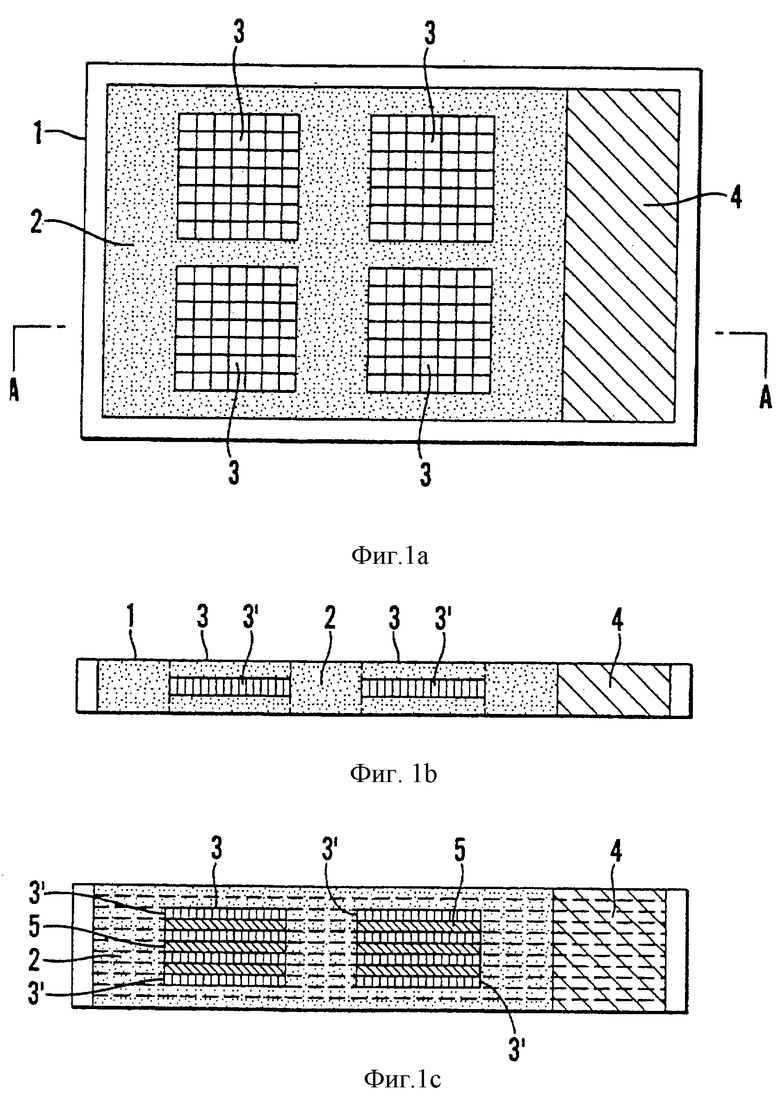

Фиг. 10 схематически показывает предпочтительное выполнение устройства согласно настоящему изобретению, разобранного на основные составляющие.

Основная цель настоящего изобретения состоит в разработке устройства хранения данных, которое далее рассматривается как реализация запоминающего прибора и называется "устройством". Основой настоящего изобретения является устройство, которое можно реализовать в виде взаимно смежных и, по существу, параллельных уложенных в стопку слоев, причем каждый из этих уложенных в стопку слоев сформирован как тонкопленочный прибор, который, в свою очередь, состоит из множества подслоев из тонкой пленки с конкретными и различными функциями, и, возможно, выполненных из различных материалов.

Тонкопленочный прибор 1, используемый в настоящем изобретении, показан в виде сверху на фиг. 1а. Этот тонкопленочный прибор 1 организуется соответственно в схемной области 2, запоминающей области 3 и интерфейсной области 4. На фиг.1b показано сечение тонкопленочного прибора по фиг.1а, взятое вдоль линии А-А. Запоминающие области 3, которые содержат запоминающие блоки 3', реализованные по тонкопленочной технологии, показаны здесь снабженными схемной областью 2, которая содержит основанную на тонких пленках электронную схему для воплощения функций управления, связи и адресации для запоминающих блоков. В зависимости от вида запоминающего блока функция адресации будет, к примеру, содержать запись, считывание и стирание в запоминающем блоке, а также передачу в запоминающий блок или из него через интерфейсную область 4. Фиг. 1с показывает сечение тонкопленочного прибора по фиг.1а, также взятое вдоль линии А-А, но здесь уже иное выполнение, нежели на фиг. 1b, здесь запоминающие области 3 показаны с уложенными в стопку по вертикали тонкопленочными запоминающими блоками 3' в схемной области 2, но взаимно изолированными посредством электроизоляционных слоев 5. В этой связи следует понимать также, что каждый отдельный запоминающий блок 3' состоит, разумеется, из нескольких отдельных подслоев, как будет подробнее рассмотрено ниже, и далее, что не показанная, в частности, электронная схема в схемной области 2 через интерфейсную область 4 используется не только для управления и адресации запоминающих блоков в отдельном тонкопленочном приборе, но также осуществляет связь с соответствующей схемой и другими запоминающими блоками в предусмотренных смежно тонкопленочных приборах 1.

Если каждый отдельный тонкопленочный прибор 1 составлен из большого числа подслоев, обычно, например, нескольких десятков, не требуется, чтобы отдельный запоминающий блок 3' содержал более чем четыре или пять подслоев, что позволяет укладывать несколько запоминающих блоков 3' в стопку либо по вертикали, как показано на фиг.1с, либо в ином преимущественном выполнении, как показано на виде сверху на фиг.2а и на b, взятой в сечении вдоль линии В-В на фиг.2а. Здесь отдельные запоминающие блоки 3' в тонкопленочном приборе 1 снова выполнены уложенными в стопку, но со взаимным сдвигом. На фиг. 2а и 2b показаны четыре стопки запоминающих блоков с четырьмя запоминающими блоками 3', взаимно изолированными посредством электроизолирующих слоев 5. Лишь самые нижние и самые верхние на фиг.2b запоминающие блоки в каждой стопке обозначены ссылочной позицией 3'.

На фиг. 3а показано другое выполнение тонкопленочного прибора 1, используемого в настоящем изобретении, которое, по существу, соответствует выполнению по фиг.2а и со стопками запоминающих блоков, созданных сдвинутыми запоминающими блоками, но в данном варианте выполнения - вдоль диагоналей так, что стопка получается такой, как показано на виде сверху по фиг.3а, в сечении по фиг.3b, взятом вдоль линии С-С на фиг.3а, и в сечении по фиг.3с, взятом вдоль линии D-D на фиг.3а. Размещение запоминающих блоков в стопке, как показано соответственно на фиг.2а и 3а, может быть предпочтительным для лучшего использования полезной площади в схемной области 2, тогда как сдвигание может упростить межсоединение между запоминающими блоками и электронной схемой в схемной области 2. Разумеется, следует понимать, что взаимное размещение запоминающих блоков 3' в запоминающей области 2 в схемной области 2, по существу, не ограничивается какой-то конкретной геометрией, но может изменяться в границах, заданных выполнением и коэффициентом формы тонкопленочного прибора 1.

Фиг.4 схематически показывает выполнение по существу пассивного матрично адресуемого запоминающего блока 3'. Запоминающий блок этого вида рассматривается, например, в заявке PCT/NO98/00185, которая принадлежит заявителю по настоящей заявке и которая приведена в качестве ссылки. На фиг.4 носитель 6 памяти выполнен в виде сандвича с соответственно нижележащим набором электродов, состоящим из параллельных полосковых электродов 7, и вышележащим набором электродов, состоящим из параллельных полосковых электродов 8. Путем приложения напряжения к соответствующему нижележащему и вышележащему электродам 7, 8 в носителе 6 памяти на пересечении между этими электродами получится изменение импеданса. Сам по себе носитель 6 памяти предпочтительно выполнен из молекулярного материала либо углеродосодержащего неорганического или органического материала. Обычно целесообразно, чтобы носитель памяти имел нелинейную импедансную характеристику, и при адресации не показанной запоминающей ячейки, образованной в пересечении между нижележащим электродом 7 и вышележащим электродом 8, целесообразно предотвратить генерирование так называемых паразитных токов в других запоминающих ячейках в запоминающей матрице. Этого можно достичь предпочтительно путем придания носителю памяти выпрямляющих свойств, предпочтительно путем встраивания слоя, который образует диодный переход, или с помощью самого носителя 6 памяти, самопроизвольно образующего диодный переход с электродным материалом.

Если материал 6 запоминающего блока является полимерным, его способность хранить информацию может зависеть от изменения его импедансного значения при приложении тока или напряжения и удержания этого измененного импедансного значения также после выключения тока или напряжения. Запоминающий блок может быть выполнен также из переключаемого материала, к примеру из ферроэлектрического материала в виде полимера, поляризационное состояние которого затем может представлять конкретное логическое состояние, или из металлоорганического комплекса с переносом заряда, такого как M(TCNQ). В общем случае из уровня техники известно несколько различных материалов, которые можно использовать в матрично адресуемых запоминающих блоках, и в этой связи можно, к примеру, сослаться на упомянутую выше публикацию PCT/NO98/00185. На фиг.4 запоминающий блок выполнен в виде сандвича, однако это не является обязательным условием, и в целом можно применять иную конфигурацию электродов, например мостовую конфигурацию, как рассмотрено в заявке PCT/NO98/00212, которая принадлежит заявителю по настоящей заявке и где нижележащий электрод 8 будет взаимно изолирован в пересечении, а материал 6 запоминающего блока размещен над электродами, что, конечно же, требует, чтобы материал запоминающего блока имел свойства, которые обеспечивают его способность хранить информацию также и в этом случае. Обычно в этом случае материал запоминающего блока может быть сопряженным полимером.

Соединение между запоминающим блоком 3' и схемой 9 в схемной области 2 схематически показано на виде сверху по фиг.5а. Каждый из электродов 7, 8 в матрице соединяется со схемой 9 по числовым и разрядным шинам 10. В сечении, взятом вдоль линии Е-Е на фиг.5а, размещение по фиг.5а, образованное как подслои S1-S8 в тонкопленочном приборе 1, представлено на фиг.5b, где показаны два сложенных в стопку запоминающих блока 3'1, 3'2 и схема 9, которая в целом реализуется по тонкопленочной технологии. В частности, можно наблюдать, что токовые дорожки и проводниковые дорожки для запоминающего блока 3', т.е. нижележащие и вышележащие электроды 1, 8, а также шины 10, которые соединяют электроды схемы 9, по существу, все выполнены в одном и том же подслое, к примеру, здесь это S2, S4, S6 и S8, что позволяет облегчить генерирование таких токовых дорожек в виде электропроводных структур в одном и том же подслое в соответствии с назначением.

Фиг. 6а показывает, как несколько тонкопленочных приборов 1, в данном случае три, соединяются в стопочную конфигурацию. Как и прежде, схемные области обозначены позицией 2, а запоминающие области обозначены позицией 3 и на этом чертеже показаны со взаимным совмещением, но это не является обязательным условием. Интерфейсная область 4 образована на стороне схемных областей и соответственно совмещается, при этом электрические соединения между тонкопленочными приборами 1 схематически обозначены стрелками 4' и проходят вертикально через интерфейсную область 4. Далее, интерфейсная область 4 может быть образована с интерфейсами 12 ввода/вывода, которые соединяют тонкопленочные приборы 1 с непоказанными внешними приборами или периферийными приборами для ввода и вывода данных.

Фиг.6b вновь показывает тонкопленочные приборы 1 сложенными в стопку, но в данном варианте реализации размещенными на подложке 13 с активными электронными схемами 14. Эта подложка может быть реализована в неорганическом полупроводниковом материале, к примеру, кремнии или модификациях кремния, а активные электронные схемы для этого случая реализуются по КМОП технологии. Эти активные электронные схемы 14 в подложке 13 предназначены для задач управления и связи при управлении запоминающими блоками в тонкопленочных приборах и приспособлены для совместной работы с тонкопленочными схемами в схемной области 2 тонкопленочных приборов 1. Это оставляет больше места в тонкопленочных приборах 1 для целей запоминания, т.к. тонкопленочные схемы в схемной области 2 в этом случае могут быть ограничены до того, что необходимо, чтобы поддерживать эффективное управление и возбуждение запоминающего блока, тогда как задачи обработки, к примеру в отношении параллельного ввода и вывода данных для запоминающего блока и для исправления ошибок, перераспределения памяти и т.п., могут выполняться приборами обработки, воплощенными активными электронными схемами 14 в подложке. Вертикальные межсоединения 4' в интерфейсной области 4 в уложенных в стопку тонкопленочных приборах осуществляют связь с интерфейсной частью 15 на подложке 13, а электрическое соединение через эту интерфейсную часть и между схемами 14 и вертикальными межсоединениями 4' может, к примеру, обеспечиваться металлическими сквозными соединениями, образованными в интерфейсной части 15, но это должно иметь место в процессе, совместимом с КМОП технологией, если на подложке предусмотрены КМОП схемы. Вместо создания интерфейса 12 ввода/вывода в интерфейсной области 4 в уложенных в стопку тонкопленочных приборах этот интерфейс 12 ввода/вывода может быть выполнен в соединении с интерфейсом 15 подложки.

Другое выполнение устройства согласно изобретению показано на фиг.6с. Здесь, как и ранее, тонкопленочные приборы уложены в стопку на подложке 13, но вместо обеспечения интерфейсной области 4 тонкопленочных приборов 1 в ее краевой части образованы отдельные интерфейсные области 4 для создания вертикальных межсоединений между тонкопленочными приборами 1 и между ними и интерфейсом 15 в подложке 13. Это, в свою очередь, может привести к топологически выгодному размещению в схемной области в отдельном тонкопленочном приборе и исключить необходимость в нем в горизонтальных токовых дорожках.

В варианте выполнения по фиг.6с устройство может быть реализовано, как показано на фиг.7. Здесь предусмотрены отдельные слои 16 между каждым тонкопленочным прибором 1, как, к примеру, такие слои, как известные из патентной заявки Норвегии 980781, которая принадлежит заявителю по настоящей заявке и которая приведена в качестве ссылки. Эти отдельные слои могут либо по отдельности, либо в выбранных комбинациях воплощать, например, электрическую, тепловую, оптическую или механическую изолирующую функцию. В стопочной конфигурации они могут также использоваться как выравнивающие слои. Когда интерфейсные области 4 в тонкопленочных приборах 1 выполнены так, как показано на фиг.7, это, однако, заранее предполагает, что они проходят через разделительные слои 16, а это должно осуществляться межсоединениями, к примеру, в виде сквозных соединений в разделительных слоях, что в отношении изолирующей функции может быть нецелесообразным и вести к дополнительному удорожанию операций изготовления. Один способ избежать этого состоит в том, чтобы выполнить тонкопленочные приборы 1, как и прежде, в стопочной конфигурации, но теперь взаимно сдвинутыми.

Выполнение этого показано на фиг.8а, где тонкопленочные приборы снова образованы на подложке 13 и взаимно разделены разделительными слоями 16, но где интерфейсная область 4 предусмотрена между интерфейсом 15 в подложке 13 и над открытыми ступенями в тонкопленочных приборах на ее стороне. Соединения между тонкопленочными приборами 1 или между ними и подложкой 15 схематически обозначены соответствующими горизонтальными и вертикальными межсоединениями 4'.

Выполнение по фиг.8а может далее предусмотреть непоказанную несущую подложку смежно с тонкопленочным прибором 1 на противоположной стороне стопочной конфигурации. При изготовлении может далее иметь место размещение тонкопленочных приборов 1 от непоказанной несущей подложки вверх, после чего подложка 13 с активными электронными схемами 14 образуется на вершине стопочной конфигурации в качестве последнего шага в процессе изготовления. Это подразумевает, что межсоединения над интерфейсной областью 4 и к интерфейсной части 15 реализуются после размещения тонкопленочных приборов 1 в предыдущем шаге изготовления, что в некоторых случаях может оказаться полезным как с точки зрения стоимости, так и для упрощения в создании этих межсоединений.

Фиг.8b показывает выполнение, примерно соответствующее тому, что показано на фиг.8а, с тонкопленочными приборами 1, взаимно разделенными разделительными слоями 16 и вновь смещенными в стопочной конфигурации так, что тонкопленочный прибор 1, ближайший к подложке 13, не покрывает ее полностью, но образует ступеньку к поверхности подложки. Затем опять могут быть предусмотрены интерфейсная область 4 над ступенчатыми частями стопочной конфигурации и межсоединения 4' между тонкопленочными приборами 1 или между ними и интерфейсом 15 в подложке 13, проходящие горизонтально и вертикально над ступенями стопочной конфигурации.

Фиг. 9 показывает совершенно схематично, как каждый отдельный тонкопленочный прибор 11, 12, 13 составлен из нескольких подслоев, показанных здесь как четыре подслоя S1-S4. Горизонтальные электрические межсоединения могут быть образованы как составная часть подслоя S путем преобразования тонкопленочного материала в этом подслое, и соответствующие вертикальные электрические межсоединения могут создаваться через подслои S совмещением частей электропроводного материала в тонкой пленке. При частных условиях такие электропроводные или полупроводниковые структуры могут быть образованы на месте в уже сформированных тонкопленочных стопках либо они могут быть образованы отдельно в каждом отдельном подслое S, который затем может ламинироваться или иным образом соединяться в стопку, которая образует тонкопленочный прибор 1. В заявке PCT/NO99/00023, которая принадлежит заявителю по настоящей заявке и которая приведена в качестве ссылки, рассматривается способ образования горизонтальных и вертикальных электропроводных структур на месте посредством, к примеру, светового излучения или излучения частиц, для создания тем самым трехмерных электропроводных и полупроводниковых структур в уложенном в пачку тонкопленочном приборе. Образование таких структур может, однако, также иметь место посредством электрических полей, которые прикладываются с пространственной модуляцией для создания рисунка отдельного подслоя S с помощью специального генераторно-модуляторного устройства, такого как описанное в заявке PCT/NO99/00022, которая принадлежит настоящему заявителю и которая приведена в качестве ссылки.

Устройство согласно настоящему изобретению показано в разобранном виде на свои основные составные части на фиг.10, где оно представлено как три тонкопленочных прибора 11, 12, 13, а интерфейсная область 4 предусмотрена на краевой части тонкопленочных приборов. Устройство по фиг.10 показано с помощью подложки 13, которая содержит непоказанные активные электронные схемы и интерфейс 15, а также образует интерфейс 12 ввода/вывода для всего устройства. Использование подложки 13 этого вида в устройстве согласно настоящему изобретению, однако, необязательно, и конфигурация в виде стопки из тонкопленочных приборов 1 может также быть образована только на пассивной несущей подложке, к примеру, сформированной из фольгообразного материала или жесткого материала, такого как кремний.

Выполнение по фиг.10 имеет признаки, одинаковые с соответствующими выполнениями, показанными в упомянутой выше международной патентной заявке PCT/NO99/00185. В этой патентной заявке более подробно рассматривается матрично адресуемое запоминающее средство, которое будет пригодно для использования в устройстве согласно изобретению, а также рассматривается то, как можно реализовать схемы со сложенными в стопку тонкопленочных слоев и с помощью трехмерной технологии. Это средство может содержать диоды, транзисторы, схемы на комплементарных транзисторах и логические вентили, реализованные по тонкопленочной технологии, что, однако, не рассматривается более подробно здесь. Следует также понимать, что запоминающие блоки в отдельном тонкопленочном приборе могут конфигурироваться в виде одного или более запоминающих устройств, например ОЗУ, ПЗУ, ЗУ с однократной записью, стираемого или перезаписываемого ЗУ, либо комбинаций таких запоминающих устройств. Это также рассматривается подробнее в упомянутой выше патентной заявке и потому не будет далее описываться здесь.

Каждый тонкопленочный прибор 1 в устройстве согласно изобретению может встраиваться на соответствующий разделительный слой 16 перед тем, как имеет место соединение в стопку. Отдельные подслои в тонкопленочном приборе 1 могут иметь толщину менее 1 мкм, например, 0,1 мкм, что подразумевает, что тонкопленочный прибор 1, выполненный на несущей подложке или просто подложке, которая в значительной степени может соответствовать разделительному слою 16, будет составлять вместе с ней толщину, к примеру, 20 мкм и может в этом случае содержать больше 100 подслоев, что будет достаточно для реализации относительно сложных электронных схем по тонкопленочной технологии и одновременно позволит укладывать в стопку десятки отдельных запоминающих блоков 3' в каждой запоминающей области 3. При размере запоминающей ячейки 1 мкм2 единственный запоминающий блок объемом, например, 1 см2 может содержать 108 запоминающих ячеек этого вида, а следовательно, хранить по меньшей мере 108 бит. Тонкопленочный прибор размером с кредитную карточку будет, к примеру, содержать 40 таких отдельных запоминающих блоков и, следовательно, хранить 0,5 Гбайт. Если далее устройство, которое может быть, к примеру, воплощено как карточка, подобная карточке по стандарту PCMCIA, с толщиной 3 мм, может содержать 100 сложенных в стопку тонкопленочных приборов, то можно видеть, что это устройство способно хранить 50 Гбайт при условиях, заданных коэффициентом формы. Увеличенная способность хранения может быть получена при лучшем использовании полезной площади каждого тонкопленочного прибора, т.е. увеличения размеров запоминающих областей 3, но также и снижением размера отдельной запоминающей ячейки, поскольку размер, по меньшей мере, до 0,25 мкм•0,25 мкм является реальным. В этом случае емкость хранения может быть прямо увеличена до 800 Гбайт, и будет видно, что это устройство согласно настоящему изобретению, реализованное таким образом, могло бы воплотить массовый запоминающий прибор или замену жесткого диска, которые могли бы использоваться в большинстве современных персональных компьютеров или рабочих станций.

При условиях, которые следуют из данной плотности хранения данных, видно, что полная плотность хранения данных будет задаваться коэффициентом формы, площадью и толщиной устройства. В основном и по существу, масштабирование до запроектированной плотности хранения будет иметь место с помощью достаточного числа тонкопленочных приборов. Встроенное, к примеру, в карточку 3 типа PCMCIA устройство согласно изобретению могло бы затем заменить обычный запоминающий блок на жестком диске в этой карточке. Если заданный стандарт не создает ограничений на размеры, устройство согласно изобретению могло бы заменить известные решения на жестких дисках, например, в персональных компьютерах, и при соответствующем масштабировании предложить емкость массовой памяти в диапазоне Гбайт.

Наконец, нужно отметить, что даже хотя устройство согласно изобретению реализуется в виде планарной стопки, его можно реализовать и как конфигурацию в виде стопки, образованной отличной от этого геометрией. Когда тонкие пленки выполнены из гибкого материала, и если используется не подложка с активными схемами и на базе неорганических полупроводников, а, например, только гибкая несущая подложка в виде фольгообразного материала, все устройство может быть реализовано, например, свернутым в цилиндрическую или трубообразную конфигурацию, если это даст преимущество для такой цели. В любом случае, очевидно, что устройство согласно изобретению, реализованное в гибких материалах, может встраиваться в другие объекты, где требования плоскостности или жесткости больше не являются критическими, а потому использоваться для воплощения приложений в полностью отличных обстоятельствах, нежели те, которые рассматриваются как попадающие в объем традиционной компьютерной технологии.

Использование: микроэлектроника. Сущность изобретения: масштабируемое устройство обработки данных, в частности устройство хранения данных, содержит один или более тонкопленочных приборов, которые образуют, по существу, плоский слой, формируемый множеством подслоев тонкопленочного материала. При этом два или более тонкопленочных прибора образуют интегральную стопку, состоящую, по существу, из плоских слоев, которые формируют тонкопленочные приборы, образуя тем самым стопочную конфигурацию. Каждый тонкопленочный прибор содержит одну или более запоминающих областей, которые образуют матрично адресуемые памяти, и схемные области, которые образуют электронную тонкопленочную схему для управления, возбуждения и адресации запоминающих ячеек в одной или более памятях. Каждое устройство имеет интерфейс к каждому другому тонкопленочному прибору в устройстве, причем упомянутые интерфейсы реализуются со связными и сигнальными шинами и поддерживающей схемой для обработки, проходящими вертикально через предназначенные для интерфейсов области в тонкопленочном приборе. 1 с. и 19 з.п.ф-лы, 10 ил.

| US 5714768 А, 02.03.1998 | |||

| WO 9509438 A1, 06.04.1995 | |||

| US 5656548 А, 12.08.1997 | |||

| US 5383269 А, 24.01.1995 | |||

| ЭЛЕМЕНТ ПАМЯТИ | 1991 |

|

RU2029391C1 |

Авторы

Даты

2003-03-27—Публикация

1999-12-03—Подача