Настоящее изобретение относится к устройству хранения и обработки данных согласно преамбуле к пункту 1 или к пункту 9 формулы изобретения, а также к способу его изготовления согласно преамбуле к пункту 25 формулы изобретения.

В частности, изобретение относится к устройству хранения и обработки данных для трехмерной наращиваемой одно- и многослойной памяти с модулями и устройствами обработки данных; и, в особенности, к устройствам, которые основаны на адресации блоков ПЗУ (постоянного запоминающего устройства) (ROM) и/или устройств ОЗМС (WORM) (с однократной записью и многократным считыванием) и/или ПЕРЕЗАПИСЫВАЕМЫХ (REWRITABLE) в пассивной матричной схеме.

В настоящей заявке на изобретение подтвержден приоритет заявки на патент Норвегии 982518, имеющей название "Наращиваемое интегрированное устройство обработки данных"("Scalable integrated data-processing device"), права на который были переданы заявителю настоящего изобретения. Указанное наращиваемое интегрированное устройство обработки данных, в частности микроЭВМ, содержит в себе блок обработки с по меньшей мере одним процессором и блок памяти с по меньшей мере одним запоминающим устройством. Устройство обработки данных создают на несущей подложке, и оно содержит в себе, по существу, параллельные слои, примыкающие один к другому и расположенные в виде многослойной структуры один над другим. Каждый из блоков обработки и блоков памяти создают в одном или в большем количестве таких слоев и/или в слоях, которые сформированы с выбранным количеством процессоров и запоминающих устройств в выбранных комбинациях. В каждом слое создают горизонтальные электрические проводящие структуры, которые образуют внутренние электрические соединения в слое, а помимо этого каждый слой содержит в себе дополнительные электрические проводящие структуры, которые обеспечивают электрические соединения с другими слоями и с наружной частью устройства обработки данных. В слое указанные дополнительные электрические структуры создают по меньшей мере на боковом торце слоя в виде торцевых соединителей и/или в предпочтительном варианте в виде вертикальных проводящих структур, которые образуют электрическое соединение в направлении поперек слоя и перпендикулярно к его плоскости для обеспечения контакта с электрическими проводящими структурами в других слоях. В частности, слои могут быть образованы множеством подслоев, изготовленных из органических тонкопленочных материалов. Некоторые слои или подслои могут также быть изготовлены как из органических, так и из неорганических тонкопленочных материалов. На фиг.1 изображен предпочтительный вариант осуществления устройства обработки данных согласно приоритетной заявке на изобретение. Предпочтительный вариант содержит процессоры и запоминающие устройства, созданные в одном и том же слое, причем последние представляют собой, например, выделенные процессорам ОЗУ (оперативные запоминающие устройства) (RAM). На подложке S создают интерфейс 3 процессора и интерфейс 8 ввода-вывода, а выше интерфейса 3 процессора расположен слой P1 процессоров с по меньшей мере одним процессором. Как интерфейс 3 процессора, так и слой P1 процессоров, будучи в устройстве обработки данных самыми нижними слоями, смежными с подложкой, могут быть реализованы посредством обычной технологии, например технологии изготовления кремниевых приборов. Выше слоя P1 процессоров создают первый слой M1 запоминающих устройств, конфигурация которого может иметь одно или более ОЗУ 6, выделенных процессорам 5 из нижележащего слоя P1 процессоров. При этом на фиг.1 особо отмечены отдельные ОЗУ 6 в слое M1 запоминающих устройств. С другой стороны показано, каким образом запоминающие устройства в слое M1 запоминающих устройств могут быть напрямую соединены с нижележащим слоем P1 процессоров посредством шин 7, причем многослойная конфигурация позволяет создавать большое количество таких шин 7 путем их осуществления в виде вертикальных проводящих структур, а конфигурация "слой на слое" позволяет создавать большое количество таких шинных соединений между слоем P1 процессоров и слоем M1 запоминающих устройств, имеющих к тому же короткий путь прохождения сигнала. Представляется понятным, что, в отличие от рассмотренного варианта, компоновка путем их размещения рядом на поверхности потребовала бы наличия более длинных соединений и, следовательно, более длительных времен пересылки данных. Показанное устройство обработки данных дополнительно содержит в себе объединенные слои MP1, MP2, МР3 запоминающих устройств и процессоров, снабженные процессорами, которые соединены между собой и с интерфейсом 3 процессора через одну и ту же шину 4 процессора. Все объединенные слои МР запоминающих устройств и процессоров формируют по меньшей мере один процессор 5 и по меньшей мере одно ОЗУ 6. Над объединенными слоями МР запоминающих устройств и процессоров создают интерфейс 1 запоминающих устройств с интерфейсом 9 ввода-вывода на внешние устройства, а над интерфейсом 1 запоминающих устройств расположено требуемое большое количество слоев М2, М3,... запоминающих устройств, которые могут быть осуществлены в виде массовой памяти устройства обработки данных. Указанные слои М2, М3 и т.д. запоминающих устройств, в свою очередь, соединены с интерфейсом 1 запоминающих устройств через шины памяти, осуществленные в виде вертикальных проводящих структур 2, проходящих через слои М2, М3....

Интегрированное устройство обработки данных имеет такую наращиваемую архитектуру, что его конфигурация, в принципе, может иметь практически неограниченную емкость памяти и количество процессоров. В частности, в устройстве обработки данных могут быть осуществлены различные типы параллельной наращиваемой архитектуры с единой оптимальной трехмерной схемой межкомпонентных соединений.

Помимо того, что блок памяти устройства обработки данных содержит в себе оперативные запоминающие устройства, он должен также содержать в себе запоминающие устройства типа ПЗУ, ОЗМС или ПЕРЕЗАПИСЫВАЕМЫЕ, либо их комбинации.

В частности, в настоящем изобретении показаны пути реализации трехмерной наращиваемой одно- и многослойной памяти и модулей обработки данных посредством структур и способов обработки, что делает их пригодными для использования в наращиваемом интегрированном устройстве обработки данных вышеуказанного типа, но изобретение не ограничивается этим.

Ниже приводится краткое описание предпосылок создания изобретения.

В опубликованной заявке на международный патент WO95/09438 (Заврацки и др. (Zawracky & al.), права на который переданы Копин Корпорейшн (Kopin Corp. )) раскрыто устройство интегральной схемы в виде многослойной структуры, в частности микропроцессора, разделенного на функциональные блоки, такие как блок арифметических вычислений, контроллер, элементы памяти и т.д., которые изготавливают в одной и той же или в отдельных полупроводниковых пластинах, а затем создают из них многослойную структуру. Функциональные блоки устройства схемы соединений разделены на части, причем одна часть расположена на монокристаллической микросхеме, а остальные части - на покрывающей ее тонкой пленке, при этом электрическое соединение составных частей осуществляют через промежуточный изолирующий слой. Устройство схемы соединений содержит в себе как объемный монокристалл, так и тонкопленочные полупроводниковые слои, при этом элементы схемы могут быть сформированы как в объемном неорганическом полупроводниковом материале, так и в виде многослойных структур, содержащих в себе объемный кремний и/или тонкопленочный арсенид галлия. Различные слои устройства схемы соединений могут быть уложены в виде многослойной структуры путем изготовления каждого из слоев схемы на отдельной подложке из тонкопленочного материала с последующим переносом слоев в многослойную структуру и использования отдельных межкомпонентных соединений, проходящих вертикально через изолирующие слои, которые отделяют каждый слой схемы в многослойной структуре. Согласно одному предпочтительному варианту осуществления устройство схемы соединений выполнено в виде объемного процессорного устройства с микропроцессором и ОЗУ в отдельных и расположенных в виде находящихся один над другим чередующихся слоев, имеющих вертикальные соединения, образованные металлическими сквозными перемычками, проходящими через слои. Однако в заявке Заврацки и др. нет никаких указаний на то, каким образом можно выполнить модули памяти, например, типа ПЗУ или ОЗМС (WORM), а предусмотренная конструкция устройства схемы соединений не обеспечивает возможность формирования модулей памяти, имеющих элементы памяти с пассивной матричной адресацией.

В патенте США 5714768 (Овшински и др.)(Ovshinsky & аl.), по существу, раскрыт вариант объединения запоминающего устройства с устройством логической обработки, причем запоминающее устройство создают в виде одной или более матриц памяти, расположенных в верхней части логического устройства обработки. Каждая матрица памяти состоит из упорядоченных в виде матрицы ячеек памяти, адресацию которых осуществляют посредством битов, слов и шин, образующих электроды адресации ячеек памяти, которые раскрыты как отдельные функциональные блоки.

В частности, ячейки памяти реализуют из запоминающего материала, изменяющего фазу под действием электричества и основанного на неорганических составах типа халькогенида, нанесение которого может быть осуществлено посредством процесса низкотемпературного осаждения.

В настоящее время существуют демонстрационные кристаллы усовершенствованных динамических ОЗУ (DRAM) в модулях по 1 гигабиту (Гбит), полученные по 0,18 мкм технологии и имеющие площадь микросхемы 570 мм2. Для обычной ячейки динамического ОЗУ с одним транзистором необходима площадь приблизительно 10λ2 (где λ - минимальный размер элемента микросхемы), хотя использование технологии обработки может значительно ее уменьшить (на 40%). Однако принимая во внимание тот факт, что существенную часть площади занимает кристалл динамического ОЗУ, на этой площади кремния не могут быть одновременно расположены дешифраторы строк и столбцов, формирователи, усилители считывания и логика исправления ошибок. Более важным является то, что в существующих схемных решениях динамических ОЗУ до настоящего времени не была доказана возможность их наращивания до трехмерной многослойной архитектуры. По своей конструкции динамические ОЗУ высокой плотности также непригодны для использования в качестве памяти ПЗУ. Для обычного ПЗУ на основе логического элемента ИЛИ-НЕ необходима номинальная площадь ячейки 70λ2 (хотя она опять может быть уменьшена путем использования новых технологических приемов при обработке), что ограничивает значения плотности величиной <108 бит/см2 даже при наиболее жестких допущениях в отношении литографии. Более высокие значения плотности могут быть достигнуты только путем использования плотной металлизации в обоих устройствах (минимальный шаг металлизации) совместно с трехмерной интеграцией. Пока еще не появились эффективные с технической и коммерческой точек зрения устройства подобного типа, несмотря на то, что огромный коммерческий потенциал стимулировал проведение большого количества научно-исследовательских и опытно-конструкторских работ в электронной промышленности, что, в свою очередь, породило появление обширной патентной литературы.

Трехмерное устройство хранения данных. Для достижения высоких значений объемной и поверхностной плотности была предпринята попытка многослойной укладки тонких слоев запоминающего устройства поверх друг друга посредством использования, например, технологии обратной литографии для схем на тонкой неорганической пленке. Однако известный уровень техники обусловил тот факт, что устройства оказались слишком сложными или дорогостоящими для того, чтобы иметь коммерческий успех. В Патенте США 5375085 "Трехмерная сегнетоэлектрическая интегральная схема без изолирующего слоя между слоями запоминающих устройств" Б. Е. Гнейда и др. ("Three dimensional ferroelectric integrated circuit without insulation layer between memory layers"'; B.E. Gnade et al. ), раскрыто запоминающее устройство с пассивной адресацией в виде многослойной структуры, основанное на использовании сегнетоэлектрического запоминающего вещества. Однако в нем не приведено никакой конкретной информации, относящейся, в частности, к возможности многоуровневой обработки, которая поясняла бы то, каким образом могут быть выполнены законченные запоминающие устройства, содержащие в себе всю необходимую активную вспомогательную цепь. Заявителем подано несколько заявок на патент, относящихся к многослойной укладке тонкопленочных запоминающих устройств и т.д., и которые имеют отношение к настоящему изобретению. Они включают в себя заявки на патент Норвегии 973993, 980781, вышеупомянутую заявку 982518, 980602 и 990867.

Схемы с плотной металлизацией. Пассивная матричная адресация обеспечивает плотность, соответствующую площади единичной ячейки блока, приблизительно, в 4λ2.

Существует ряд патентов, где в устройствах ПЗУ используют схемы пассивной матричной адресации, например патент США 4099260 Д.Н. Лайнса и др. "Биполярное постоянное запоминающее устройство, имеющее самоизолирующие разрядные шины" (D.N. Lynes et al., "Bipolar read-only-memory unit having self-isolating bit-lines"); патент США 4400713 К. Дж. Божа и П.Б. Мольера "Матрица полупроводниковых элементов" (K.G. Ваugе and. P.В. Mollier, "Matrix array of semiconducting elements"); патент США 5170227 М. Канеко и К. Ногучи "ПЗУ с масочным программированием, имеющее монокристаллические кремниевые проводники" (М. Kaneko and К. Noguchi "Mask ROM having monocrystalline silicon conductors"); патент США 5464989 С. Мори и др. "ПЗУ с масочным программированием, использующее обнаружение туннельного тока, для хранения данных и способ его изготовления" (5. Mori et al., "Mask ROM using funnel current detection to store data and a method of manufacturing thereof"); патент США 5811337 Дж. Вена "Способ изготовления полупроводникового постоянного запоминающего устройства для постоянного хранения данных многопозиционного кодирования" (J. Wen, "Method of fabricating a semiconductor read-only memory device for permanent storage of multilevel coded data") и патента РСТ WO 96/41381 Ф. Гонсалеса и др. "Диод с многослойной структурой и канавками для использования с материалом, имеющим проводимость по нескольким направлениям, в ячейке энергонезависимой памяти" (F. Gonzalez et al., "A stack/trench diode for use with a multistate material in a non-volatile memory cell"). Однако подобные схемы явно основаны на традиционной обработке кремниевой подложки, к которой относятся, например, термическая обработка, процессы имплантации и травления, которые несовместимы с целями настоящего изобретения, то есть с низкой стоимостью и с возможностью создания устройства хранения данных с иерархической структурой.

В вышеуказанном патенте США 5375085 раскрыты устройства, основанные на пассивной матричной адресации, но ограниченные особым случаем сегнетоэлектрических запоминающих материалов. Однако было доказано, что сегнетоэлектрические материалы, указанные в этом патенте в качестве примеров, непригодны для схем запоминающего устройства с простой пассивной матричной адресацией из-за потери поляризации в невыбранных ячейках при их неоднократном частичном переключении. Эта проблема преодолена в сегнетоэлектрических ОЗУ (СЭОЗУ)(FERAM) с одним и двумя транзисторами, но они не позволяют осуществлять простое трехмерное наращивание.

В патенте США 5441907 "Процесс изготовления ПЗУ с подключаемой диодной маской" ("Process for manufacturing a plug-diode mask ROM", H-C. Sung and L. Chen) Г-К. Санга и Л. Чена раскрыто ПЗУ с пассивной матричной адресацией, в котором осуществляют кодировку двоичных данных в точке пересечения каждой матрицы посредством наличия или отсутствия диодного подключения.

Однако согласно указанному патенту, способы, в которых описано изготовление устройств, включают в себя несколько высокотемпературных операций, в том числе окончательный отжиг, что препятствует созданию многослойной структуры и не позволяет использовать дешевые материалы, пригодные для низких температур.

Тонкопленочные ПЗУ. В Патенте Великобритании 2066566 "Аморфный диод и ПЗУ или ЭСППЗУ (электрически стираемое программируемое ПЗУ) с его использованием" С. Г. Холмберга и Р.А. Флэска ("Amorphous diode and ROM or EEPROM device utilizing same", S.H. Holmberg and R.A. Flasck) раскрыты тонкопленочные запоминающие устройства, основанные на фторсодержащем аморфном кремнии. В патенте США 5272370 "Тонкопленочные ПЗУ и их изготовление" И.Д. Френча ("Thin-film ROM devices and their manufacture", I.D. French) раскрыто ПЗУ, основанное на тонкопленочных ячейках памяти в устройстве с пассивной матричной адресацией. Явно подчеркнуто осуществление многоуровневого (то есть, многоразрядное) хранения данных в каждой ячейке памяти посредством создания многослойных структур, выбор которых может быть выполнен отдельно для каждой ячейки памяти.

В основу настоящего изобретения поставлена задача создания таких конфигураций и технических решений, при которых плотные двумерные комбинации однобитовых ячеек могут быть объединены в трехмерные структуры памяти с использованием легко осуществимых и недорогих промышленных технологий.

Другой задачей настоящего изобретения является создание ПЗУ, запоминающих устройств ОЗМС и ПЕРЕЗАПИСЫВАЕМЫХ, имеющих короткие времена произвольной выборки, высокие скорости передачи данных и низкую потребляемую мощность. В настоящем документе термин "ПЕРЕЗАПИСЫВАЕМАЯ" следует применять для ячеек памяти, в которых может быть осуществлена замена запомненной информации на новую информацию посредством операции стирания/записи или прямой перезаписи. В зависимости от варианта применения может быть осуществлено либо только однократное, либо многократное выполнение этой операции.

Еще одной задачей настоящего изобретения является создание объединенных устройств хранения и обработки данных, в которых создание запоминающих структур и конструкций устройств может быть осуществлено в очень плотных структурах, отличающихся тем, что они имеют короткие двух- и трехмерные тракты межкомпонентных соединений с высокой степенью распараллеливания.

Наконец, задачей изобретения также является создание способа изготовления устройства хранения и обработки данных, в котором используют низкотемпературные процессы и пригодные для них материалы.

Поставленные задачи решаются, в частности, тем, что в устройстве хранения и обработки данных каждый основной слой модуля запоминающего устройства и/или модуля обработки данных содержит в себе многослойную структуру из функциональных подслоев, причем каждый функциональный подслой осуществляет одну или большее количество конкретных схемных функций; в основном слое или в основных слоях создают по меньшей мере часть активной схемы, и по меньшей мере некоторые из функциональных слоев содержат в себе совокупность пленочных органических материалов, обладающих низкотемпературной совместимостью, и неорганических пленок, обладающих низкотемпературной совместимостью.

Целесообразно, чтобы в заявленном устройстве по меньшей мере один из основных слоев содержал в себе модули запоминающего устройства с элементами памяти, имеющими пассивную матричную адресацию, осуществленными в материале запоминающего устройства в местах пересечения между электродами из первого набора параллельных электродов, созданного на поверхности материала запоминающего устройства, и из второго набора параллельных электродов, созданного на противоположной поверхности материала запоминающего устройства и пересекающегося с первым набором электродов, причем элементы памяти были осуществлены в виде находящихся в местах пересечения элементов с нелинейным импедансом, а каждый из элементов памяти для улучшения их адресуемости был снабжен логическим значением, задаваемым посредством коэффициента электрического импеданса материала запоминающего устройства между пересекающимися электродами. Предпочтительными элементами с нелинейным импедансом являются выпрямительные диоды, то есть диоды, изготовленные из одного или из нескольких материалов, в частности кремния, арсенида галлия или германия, в аморфной, поликристаллической, микрокристаллической, объемной или в определяемой технологическим процессом монокристаллической форме, либо из органических полупроводниковых материалов, включающих в себя молекулы, олигомеры или полимеры, или их комбинации; либо тонкопленочные транзисторы, изготовленные из одного из таких материалов, как кремний, арсенид галлия или германий, в аморфной, поликристаллической, микрокристаллической, объемной или в определяемой технологическим процессом монокристаллической форме, либо из органических полупроводниковых материалов, включающих в себя молекулы, олигомеры или полимеры, или их комбинации. В данном варианте осуществления устройства предпочтительно, чтобы по меньшей мере один основной слой содержал в себе сдвоенные модули запоминающего устройства с пассивной матричной адресацией в отдельных подслоях, причем один вышележащий и один нижележащий модули запоминающего устройства совместно использовали набор электродов строк или столбцов и чтобы было создано более одного слоя, два из основных слоев содержали в себе общие электронные схемы формирования строк или столбцов, а также факультативные электронные схемы считывания, соединенные с ними посредством общих шин. Целесообразно также использовать более одного основного слоя, каждый из которых содержал бы в себе более одного модуля запоминающего устройства, причем модули запоминающего устройства были созданы в виде расположенных рядом сегментов, уложенных поверх аналогичных сегментов из нижележащего основного слоя, образуя на общей подложке две или более расположенные рядом многослойные структуры, а часть каждого сегмента в каждой многослойной структуре была соединена с частью подложки и имеет электрическую связь со схемой, созданной на ней или в ней.

Полезно, чтобы в устройстве согласно изобретению было создано более одного основного слоя, а каждый основной слой содержал в себе более одного модуля запоминающего устройства, причем модули запоминающего устройства были бы созданы в виде расположенных рядом сегментов, уложенных в шахматном порядке поверх аналогичных сегментов из нижележащего основного слоя таким образом, что каждый модуль запоминающего устройства в многослойной структуре был расположен в шахматном порядке по отношению к примыкающим соседним модулям, а часть каждого сегмента в каждой многослойной структуре была соединена с частью подложки и имеет электрическую связь со схемой, созданной на ней или в ней.

Предпочтительно, чтобы в заявленном устройстве множество проходящих насквозь электрических проводников или сквозных перемычек, обеспечивающих соединения для подачи электропитания и сигнала между основными слоями и между последними и подложкой, имели шахматный порядок распределения в поперечном направлении.

Целесообразно, чтобы по меньшей мере один из модулей запоминающего устройства представлял собой ПЗУ с масочным программированием, либо ПЗУ с шаблонным программированием, либо устройство ОЗМС, либо содержал в себе ячейки памяти ПЕРЕЗАПИСЫВАЕМОГО типа.

Предпочтительно, чтобы один или более модулей запоминающего устройства содержал в себе совокупность по меньшей мере двух различных типов запоминающих устройств в виде ПЗУ, устройства ОЗМС или ПЕРЕЗАПИСЫВАЕМОГО, которые интегрированы по меньшей мере в один основной слой многослойной структуры.

Предпочтительно, чтобы по меньшей мере часть подложки, находящейся ниже расположенных поверх нее одного или большего количества основных слоев, содержала в себе схему, электрически соединенную с одним или большим количеством основных слоев. В этом случае предпочтительно, чтобы содержащая в себе схему часть подложки была сформирована из полупроводниковых материалов в легированном или нелегированном виде, которые были бы созданы в монокристалле или в виде тонкой пленки на пассивном кристаллодержателе, и чтобы выбор полупроводниковых материалов был осуществлен из одного или из нескольких материалов, таких как кремний, арсенид галлия и германий, в аморфной, поликристаллической, микрокристаллической, объемной или в определяемой технологическим процессом монокристаллической форме, либо из органических полупроводниковых материалов, включающих в себя молекулы, олигомеры или полимеры, или их комбинации.

Целесообразно, чтобы в качестве неорганического пленочного материала был использован кремний, соединения кремния, металлы или соединения металлов, либо их комбинации.

Предпочтительно получать находящуюся на подложке схему посредством одной или большего количества следующих технологий, а именно,КМОП, n-МОП, или р-МОП (CMOS, NMOS, PMOS), и предпочтительно, чтобы созданная на или в подложке схема также содержала бы одно или более устройств кэш-памяти в виде статического ОЗУ, динамического ОЗУ и/или сегнетоэлектрического ОЗУ (СЭОЗУ) (SRAM, DRAM, FERAM).

Полезно, чтобы созданная на подложке или внутри нее схема могла сама или в совокупности содержать в себе процессоры для обнаружения и исправления ошибок и неисправностей в модулях запоминающего устройства в основном слое или в слоях, и/или процессоры для перераспределения неисправных модулей запоминающего устройства в основном слое или в слоях, и/или процессоры для динамического перераспределения модулей запоминающего устройства в основном слое или в слоях с целью оптимизации производительности и срока службы указанных модулей.

Предпочтительно, чтобы схемы заявленного устройства в основных слоях полностью были осуществлены посредством тонкопленочной технологии.

Поставленная задача решается также тем, что в рамках способа изготовления предложенного в изобретении устройства хранения и обработки данных осуществляют нанесение и обработку указанных слоев в таком тепловом режиме, при котором уже нанесенный и обработанный нижележащий слой или слои не подвергают воздействию статической температуры, превышающей величину в пределах диапазона температур 150-450oС, либо динамических температур, превышающих предел динамической устойчивости полимерных материалов, где указанный предел динамической устойчивости установлен равным менее 500oС в течение не более 10 мс, либо химического разрушения, вызванного технологическим процессом, причем материалы для слоев выбирают из тонких пленок аморфного, поликристаллического или микрокристаллического кремния или германия, окислов и других диэлектрических материалов и металлов или их комбинаций, а нанесение осуществляют посредством одного из следующих способов, в частности распыления, напыления, химического осаждения из газовой фазы или плазменного химического осаждения из газовой фазы, нанесения покрытия путем центрифугирования; осуществляют обработку нанесенного слоя посредством традиционной технологии производства полупроводников, совместимой с указанным тепловым режимом, причем в качестве технологии производства полупроводников используют фотолитографию, либо жидкостное травление, либо сухое травление, в том числе реактивное ионное или плазменное травление, либо химико-механическую полировку, либо ионное легирование, либо совокупность указанных технологий; осуществляют обработку нанесенного слоя посредством кратковременного нагрева импульсным лазером или пучками частиц для стимулирования кристаллизации нанесенных аморфных пленок, уменьшения зернистости нанесенных пленок и внедрения и активирования в нем легирующих примесей; и осуществляют нанесение молекулярных олигомерных или полимерных материалов для слоев посредством технологий с использованием растворителей, напыления, распыления или других вакуумных технологий, или технологий переноса пленки, или их совокупности.

Предпочтительно изготавливать тонкопленочные схемы и транзисторы на основе кремния посредством низкотемпературного процесса с использованием кристаллизации и активирования легирующей примеси тонкопленочных транзисторов под действием лазерного излучения.

Целесообразно модуль запоминающего устройства в виде запоминающего устройства с матричной адресацией, снабженного разделительными диодами, создавать путем формирования разделительных диодов как в вертикальной, так и в планарной конфигурации, путем непосредственного нанесения пленок аморфного микрокристаллического или поликристаллического кремния n- и р-типа или германия и непосредственного нанесения тонких пленок органического полупроводника, олигомера или полимера; либо путем формирования разделительных диодов посредством лазерного плавления и отвердевания аморфных или микрокристаллических пленок неорганического полупроводникового материала n- и р-типа, нанесенных непосредственно на нижележащий слой или слои, обладающие низкотемпературной совместимостью. Тогда в последнем случае полезно осуществлять защиту нижележащего слоя или слоев от воздействия расплавленного полупроводникового материала при лазерной кристаллизации путем создания тонкопленочного диффузионного барьера, а также осуществлять запланированную реакцию между расплавленным полупроводниковым материалом и нижележащим слоем или слоями, что обеспечивает образование устойчивого химического соединения, обладающего электропроводностью, например, силицида.

Целесообразно формировать разделительные диоды посредством лазерного плавления и отвердевания нанесенной аморфной или микрокристаллической неорганической пленки, и формировать р-n переход диодов с компенсацией легирования, причем р-n переходы получать либо из нанесенного слоя, находящегося на нижележащем металлизированном покрытии, либо путем так называемого автолегирования посредством использования легирующих элементов в металлизированном покрытии пассивной матрицы; или же путем формирования разделительных диодов посредством лазерного плавления и отвердевания нанесенной аморфной или микрокристаллической неорганической пленки и формирования диода с барьером Шотки с нижележащей металлизированной структурой или с химическим соединением, образованным путем реакции с нижележащей металлизированной структурой.

В дальнейших предпочтительных вариантах осуществления изобретения лазерная кристаллизация ограничена режимом взрывной кристаллизации, соответственно, для чего требуется только кратковременный расплав поверхности на пленке и образование самораспространяющейся жидкой пленки для кристаллизации остального объема пленки, а изолирующие структуры формируют из высокорезистивных или анизотропных контактирующих материалов, которые используют в качестве разделительного диода в вертикальном направлении и непроводящего межслойного диэлектрика в горизонтальном направлении относительно слоев.

В последнем случае предпочтительно и разделительный диод, и непроводящий межслойный диэлектрик формировать путем химической или термической модификации указанных контактирующих материалов, а в таком случае химическая или термическая модификация может возникнуть путем автолегирования высокорезистивного аморфного кремния и лазерной кристаллизации высокорезистивного аморфного кремния.

Целесообразно, чтобы модуль запоминающего устройства был реализован в виде запоминающего устройства с матричной адресацией, снабженного разделительными диодами, путем формирования диода в пространственно ограниченных областях, например, в точках пересечения матрицы и одновременного создания боковой изоляции между диодами посредством процесса самосовмещения, ограничивающего формирование диодных переходов пространственно ограниченными областями посредством только одного из следующих процессов, а именно лазерной кристаллизации с модуляцией поглощенной энергии лазерного излучения элементами нижележащих слоев или структур, лазерной кристаллизации с модуляцией поглощенной лазерной энергии просветляющими или отражающими тонкими пленками, ограничения образования центров кристаллизации при лазерной кристаллизации теми областями, в которых находится металл; управления поверхностью межслойного диэлектрика; использования нижележащих слоев или структур в качестве источников легирующей примеси для формирования диодного перехода посредством взрывной кристаллизации, или выборочное химическое или физическое осаждение из паровой фазы аморфных или микрокристаллических пленок, на которые воздействует поверхностная модификация поверхности межслойного диэлектрика.

Предпочтительно разделять функциональные подслои посредством выравнивающего слоя диэлектрика, сформированного способом центрифугирования или другими способами нанесения покрытия и химико-механической полировкой, причем указанный слой диэлектрика выполнен из олигомерного, полимерного или из неорганического материала, а также осуществлять инициацию индуцированной кристаллизации посредством иных источников с направленной энергией, чем лазеры, в том числе импульсных ионных и электронных пучков.

Поставленная задача решается с использованием новых материалов и процессов, которые позволяют создать устройства с новыми двух- и трехмерными структурами. В связи с этим, отличительными признаками являются следующие.

1. Модули запоминающего устройства изготавливают с использованием процессов и материалов, обеспечивающих низкотемпературную совместимость, то есть полимеров или низкотемпературной обработки поликристаллического, или микрокристаллического, или аморфного кремния. В данном случае термин "низкотемпературная совместимость" относится к процессам, при которых статические температуры не превышают значений, пригодных для полимероподобных подложек, или к процессам кратковременного нагрева, которые ограничены временами, достаточно короткими для обеспечения подобной пригодности. Например, при лазерной кристаллизации тонкопленочного кремния температура во внешнем слое в действительности весьма высока, но вследствие короткой продолжительности теплового импульса и суммарной плотности энергии, тепло быстро перераспределяется в поддерживающие слои. Вследствие калориметрических эффектов после достижения определенной глубины высоких температур в них не возникает. Для простоты, описанные выше процессы и материалы, обладающие низкотемпературной совместимостью, далее могут быть упомянуты как "низкотемпературная обработка" и "низкотемпературные материалы".

2. Низкотемпературная обработка предоставляет возможность создания модулей запоминающего устройства в одном суперслое или в многослойной структуре из суперслоев, не повреждая ни нижележащие схемы, ни другие слои запоминающих устройств из многослойной структуры. Это применимо для устройств, основанных как на традиционных монокристаллических кремниевых подложках, так и на пластмассовых подложках с активными тонкопленочными схемами. (Оказывается, что в последнем случае короткая продолжительность теплового импульса, обычно используемого при лазерной перекристаллизации, предотвращает повреждение пластмассы даже при таких температурах, при которых длительная тепловая нагрузка вызвала бы повреждение).

3. Из 1. и 2. вытекает ряд полезных следствий.

Возможность осуществления многослойной структуры приводит к высокой объемной плотности данных и к наличию коротких вертикальных межкомпонентных соединений, имеющих высокую плотность, что приводит к высокой пропускной способности при передаче данных, наличию межкомпонентных соединений с низкой емкостью и сопротивлением вследствие малого расстояния; высокой степени параллелизма (много вертикальных соединений) для слов с большой разрядностью, использованию областей в монокристалле подслоя или высокоэффективного поликристаллического, аморфного или микрокристаллического слоя, расположенного под модулями запоминающего устройства, для задач, требующих наличия высокоскоростной активной цепи.

В качестве примеров можно привести интегрированный кэш данных статического ОЗУ (SRAM), электронные схемы формирователя и интерфейса, встроенные блочно-ориентированные схемы обнаружения и исправления ошибок для повышения надежности работы слоев запоминающих устройств, высокую плотность записи данных по площади в каждом слое, обусловленную пассивной матричной адресацией, с возможностью расположения слоев схемы формирователя ниже и/или выше, а также в том же самом слое.

В дальнейшем приводится подробное описание вариантов осуществления изобретения со ссылками на чертежи, на которых:

фиг. 1 изображает вариант осуществления наращиваемого интегрированного устройства обработки данных, в котором может быть использовано настоящее изобретение.

Фиг. 2 - схему компоновки устройства ПЗУ емкостью 1 Гб согласно варианту осуществления настоящего изобретения.

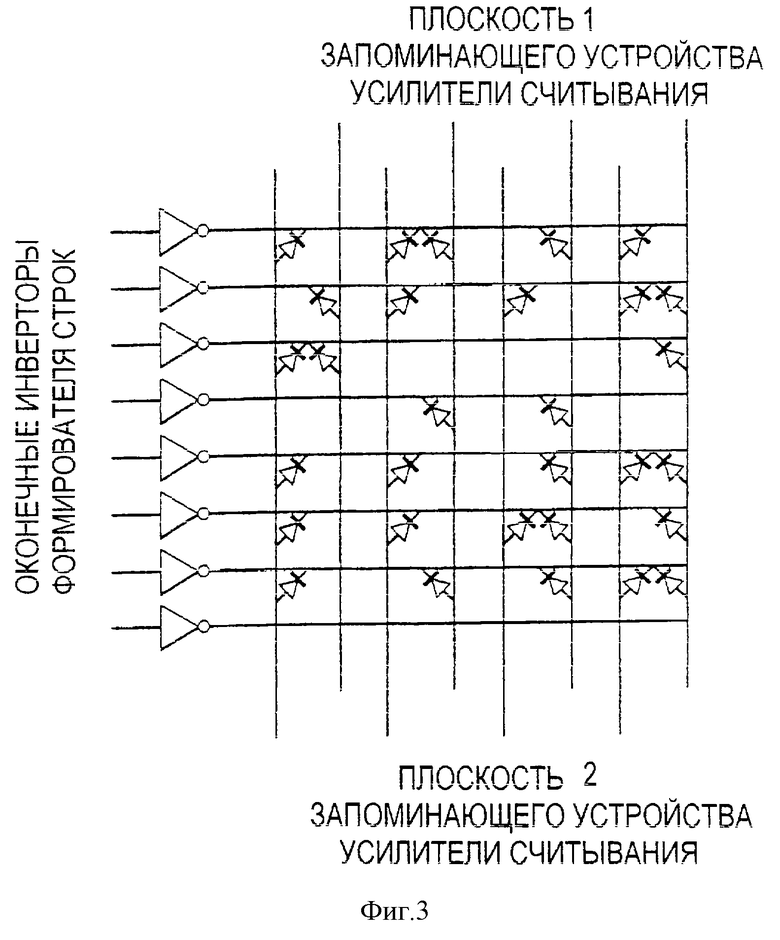

Фиг. 3 - схему расположения шин адресации строки/столбца двух матриц памяти для ПЗУ из фиг.2.

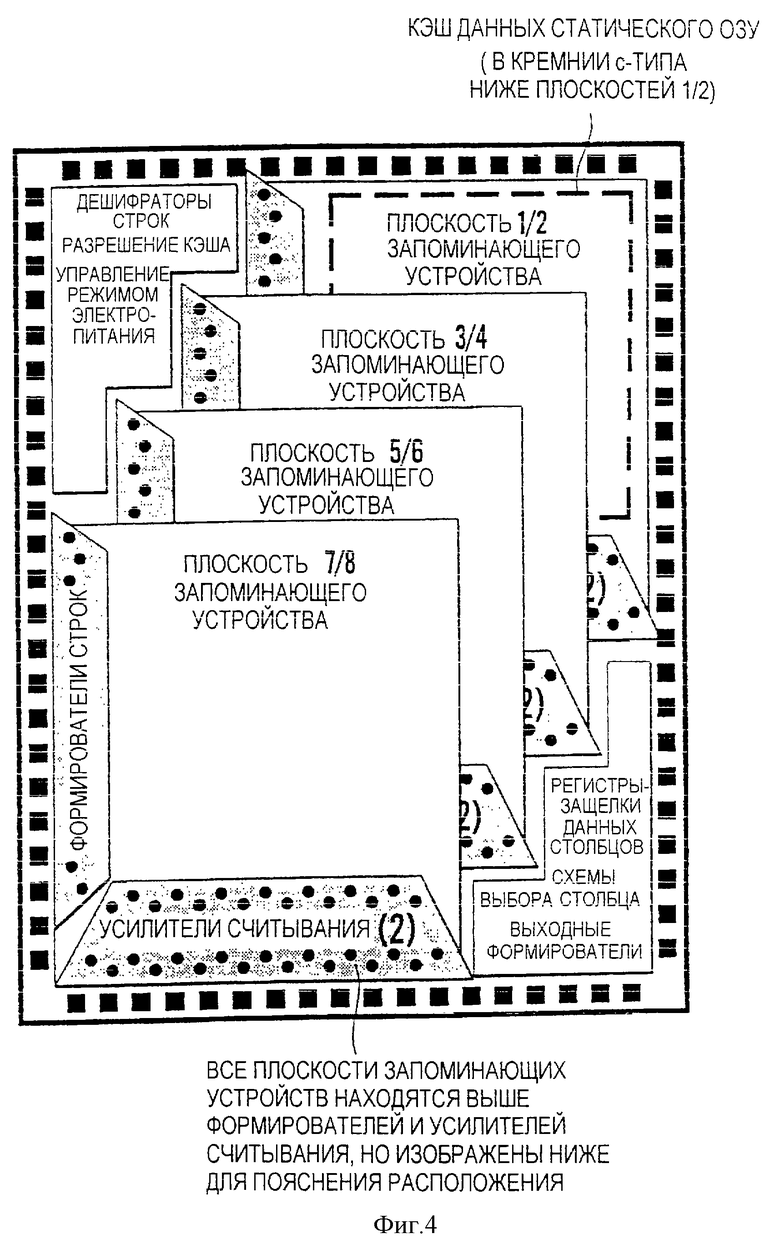

Фиг.4 - структуру многослойной укладки матриц памяти в шахматном порядке для ПЗУ из фиг.2.

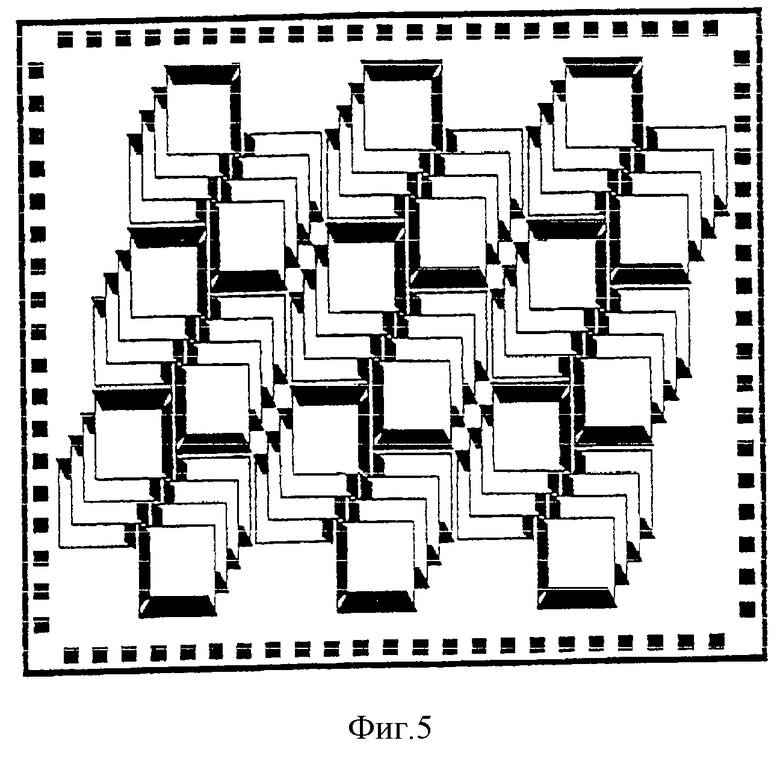

Фиг. 5 - совокупность нескольких структур многослойной укладки в шахматном порядке показанного на фиг.4 типа в виде многосегментной структуры многослойной укладки матриц памяти в шахматном порядке для ПЗУ из фиг.2.

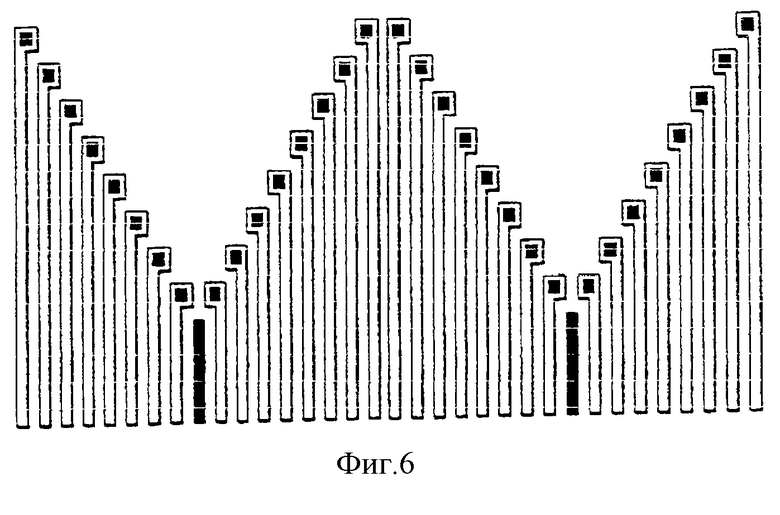

Фиг. 6 - расположенные в шахматном порядке вертикальные или горизонтальные сквозные перемычки для обеспечения соединений поперек или вдоль матриц памяти и соединения последних с нижележащими схемами.

Фиг.7 - график зависимости времени выборки от количества сегментов блока памяти.

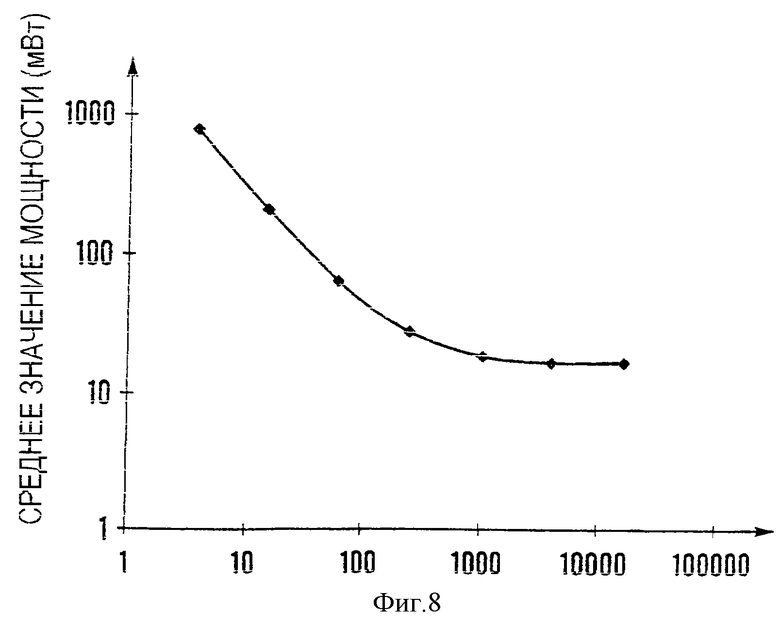

Фиг. 8 - график зависимости среднего значения потребляемой мощности для адресации от среднего размера адресуемого блока (считывание).

Фиг. 9 - вертикальные диоды во "включенном" и в "выключенном" элементе памяти ПЗУ.

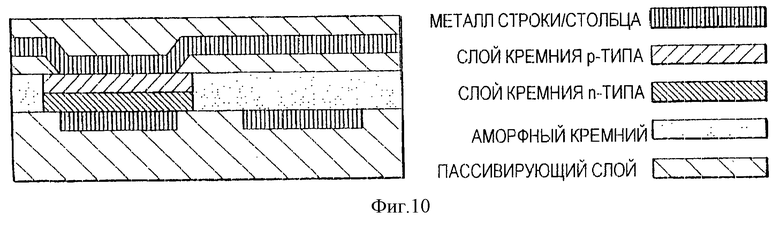

Фиг. 10 - те же вертикальные диоды, что и на фиг.9, но изготовленные посредством процесса самосовмещения и планаризации.

Предпочтительный вариант устройства согласно изобретению реализуют в виде многослойной структуры, построенной на монокристаллической кремниевой подложке, которая содержит все активные электронные схемы. Последние соединены с одним или с большим количеством вышележащих слоев запоминающих устройств посредством сквозных перемычек. Каждый слой запоминающих устройств содержит полученные способом низкотемпературной обработки матрицы диодных ПЗУ, и/или устройств ОЗМС, и/или ПЕРЕЗАПИСЫВАЕМЫХ устройств, в которых высокая плотность записи в битах на единицу площади достигнута посредством использования пассивной матричной адресации. Каждый слой запоминающих устройств представляет собой самостоятельный объект и не требует никакой высокотемпературной или химически агрессивной обработки, способной повредить нижележащие структуры при изготовлении. Таким образом, модули запоминающих устройств могут быть расположены поверх находящихся в подложке активных электронных схем при сохранении "недвижимости" подложки и путем создания коротких электронных магистралей между активными схемами и модулями запоминающего устройства. Кроме того, емкость запоминающего устройства может быть увеличена путем добавления большего количества слоев запоминающих устройств поверх первых, что приводит к наличию трехмерной многослойной структуры с очень высокой объемной плотностью записи в битах.

Описанные выше устройства хорошо поддаются постобработке модулей запоминающего устройства, при которой сначала осуществляют подготовку всех схем на монокристаллической кремниевой подложке с использованием традиционной обработки кремниевого литья. Последующее нанесение слоя (слоев) запоминающих устройств может быть выполнено на отдельных производственных мощностях, например, если при этой операции желательно использовать такие материалы и процессы, которые могут вызвать проблему загрязнения при обработке кремния.

Для минимизации затрат и достижения требуемых высоких скоростей передачи данных схемы формирования и считывания в предпочтительном варианте изготавливают на монокристаллической кремниевой подложке посредством стандартной КМОП-технологии (CMOS). Затем над последним слоем металлизации создают множество матриц ПЗУ/ОЗМС/ПЕРЕЗАПИСЫВАЕМЫХ устройств, соединенных с нижележащими формирователями посредством сквозных перемычек. Диоды могут быть неорганическими, например выполненными из аморфного, поликристаллического или микрокристаллического кремния, либо они могут быть выполнены из органического материала, например из сопряженного полимера или олигомера. Схема пассивной матричной адресации и трехмерная архитектура с использованием низкотемпературных диодов обеспечивают резкое увеличение емкости памяти для всех существующих конструкций ПЗУ/ОЗМС/ПЕРЕЗАПИСЫВАЕМЫХ устройств при предельно малом увеличении стоимости по сравнению с нижележащей КМОП-схемой.

Используемые в устройстве согласно изобретению вертикальные межкомпонентные соединения могут иметь различный вид: один из вариантов состоит в том, что проходящие внутрь проводники осуществляют в виде сквозных перемычек: в этом случае, как упомянуто выше, наличие коротких расстояний и больших площадей при использовании концепции многослойной структуры позволяет реализовать высокие скорости передачи данных, а также гибкую архитектуру при, например, шахматном порядке расположения сквозных перемычек, что будет более подробно описано ниже при рассмотрении предпочтительного варианта осуществления. Вертикальные межкомпонентные соединения могут также быть осуществлены посредством находящихся в каждом слое электрических проводников, идущих к краю рассматриваемого слоя, где они выходят наружу и где может быть выполнено их электрическое соединение с подобным же образом выведенными наружу проводниками других слоев. Эту задачу можно облегчить, например, посредством ступенчатого продления краев нижележащих слоев. Другой класс вертикальных межкомпонентных соединений основан на бесконтактной (негальванической) связи через слои. Возможность этого обусловлена наличием многослойной архитектуры, то есть возможностью емкостной, индуктивной или оптической связи между схемами в различных слоях.

Для ясности и конкретности последующее подробное описание изобретения будет приведено для предпочтительного варианта осуществления, основанного на массивах ПЗУ с диодами из поликристаллического кремния, полученными путем низкотемпературной обработки, в виде многослойной структуры с четырьмя двойными слоями. Такая конструкция может быть легко распространена на запоминающие устройства ОЗМС с использованием как индуцированной взрывной кристаллизации аморфных диодов, так и модуляции проводимости межслойных органических пленок, и на ПЕРЕЗАПИСЫВАЕМЫЕ запоминающие устройства путем включения в матрицы запоминающих устройств высокоэффективных запоминающих материалов (см. остальные принадлежащие настоящему заявителю заявки на патенты, на которые имеются ссылки в настоящем документе).

На фиг.2 изображена схема расположения слоев для устройства ПЗУ емкостью 1 гигабайт (Гб) согласно изобретению. Демультиплексоры и формирователи строк, усилители считывания и мультиплексоры столбцов реализованы в виде традиционной сверхбольшой монокристаллической КМОП-микросхемы (КМОП-СБИС) (VLSI CMOS), образующей основание структуры. Все слои диодов-ПЗУ изготавливают после завершения изготовления цепей СБИС поверх слоя нанесенного конечного диэлектрика и СМР-планаризации.

Подробности схемного решения КМОП-СБИС не будут приведены, за исключением того случая, когда это прямо относится к матрицам памяти. Формирователи и усилители считывания, по существу, идентичны тем, которые используют в обычных модулях динамического ОЗУ, а отслаивание устройств может быть осуществлено почти без повреждений. Для обеспечения согласования с высоким емкостным сопротивлением структуры диоды-ПЗУ необходимо изменить размеры инверторов формирователей строк, а также необходимо выполнить видоизменение усилителей считывания для обеспечения более медленной скорости зарядки.

Матрицы памяти укладывают послойно в виде многослойной структуры, а каждый слой ПЗУ состоит из простого пересечения шин строк/столбцов, которые могут быть соединены посредством вертикальной диодной структуры; причем двоичный 0 (или 1) указывают посредством наличия диода. Для получения модуля емкостью 1 гигабайт требуется всего восемь матриц памяти, каждая из которых содержит 109 бит. Для уменьшения общего количества уровней фотошаблона шины строк разделяют между двумя матрицами памяти, что уменьшает быстродействие, но упрощает весь процесс изготовления.

Принципиальная электрическая схема для каждой пары матриц памяти показана на фиг.3. При фиксированном адресе строки (строб адреса строки(RAS)) конечный инвертор замыкает одну из шин строк на землю. Ток, поступающий от шин столбцов (симметрично от обеих пар столбцов), протекает через диоды, а падение напряжения на шине столбцов считывают параллельно для всех шин столбцов. После считывания значение потенциала шины строк опять устанавливают равным VDD, а значения шин столбцов - их потенциалу в статическом состоянии (между "землей" и VDD - 0,7). Для запоминающего устройства, осуществленного посредством диодов, (по сравнению с МОП-структурой ИЛИ-НЕ), выигрыш от увеличения плотности, допустимой при схеме расположения строк/столбцов с частыми пересечениями металлизации, не компенсирует потери мощности и быстродействия. В устройстве с поблочной выборкой данных приведение в действие одного инвертора строк обеспечивает считывание данных для двух столбцов. Несмотря на то, что скорость каждой операции выборки строки может быть ограничена емкостным накоплением заряда, суммарная скорость передачи данных является "усиленной" в число раз, равное удвоенной длине столбца. Как будет показано ниже, время произвольной выборки данных может быть также скорректировано путем надлежащей сегментации памяти, что частично более подробно будет описано ниже со ссылкой на фиг.5.

При трехмерной многослойной конфигурации запоминающего устройства для обеспечения пространства для формирователей строк, усилителей считывания, и периферийных схем необходимо, чтобы многослойная укладка матриц памяти на кристалле кремния была осуществлена в шахматном порядке вне зависимости от сегментации. Такая структура многослойной укладки матриц памяти в шахматном порядке показана на фиг.4, где матрицы памяти обозначены светло-серым цветом, а блоки монокристаллического кремния обозначены темно-серым цветом. Для того, чтобы в "недвижимости" монокристаллического кремния предусмотреть место для формирователей строк (больших инверторов) и усилителей считывания, каждые пары матриц памяти смещают как по горизонтали, так и по вертикали. Сигнал ко всем формирователям строк подают от логических схем общего

дешифратора строк (с выполнением операции И-НЕ при выборе конечной пары плоскостей). Чертеж изображен не в масштабе; в частности, часть площади, требуемая для формирователей строки и усилителей считывания, уменьшается, приблизительно как квадратный корень емкости запоминающего устройства. Даже допуская то, что сегментация равна 4096х4096, усилители считывания займут лишь менее десяти процентов площади "недвижимости" кристалла. Для массивов емкостью 256 Мбит эта площадь составляет менее одного процента от общей площади кристалла.

При многослойной конфигурации, в которой матрицы памяти расположены над находящимися в монокристалле логическими схемами, существенная часть кристалла остается неиспользованной. Некоторая его часть необходима для размещения логических схем отображения дефектных ячеек и исправления ошибок, но остальную часть следует выполнить в виде кэша данных статического ОЗУ для уменьшения количества множественных обращений к матрицам памяти. Как будет показано ниже, основное рассеяние мощности происходит при обращениях к памяти, что уменьшает их количество, требуемое при выполнении запросов от кэш-памяти, и может значительно уменьшить полную мощность даже в режиме с произвольной выборкой. Для осуществления произвольной выборки из памяти необходимо, чтобы кэш-память дополнительно осуществляла бы нечто вроде упреждающего прогнозирующего считывания из запоминающего устройства для компенсации ограничения мощности и быстродействия при прямом доступе. В вариантах применения для памяти с высокой степенью поблочной выборки кэш-память становится менее необходимой, и вместо нее площадь можно использовать под алгоритмы исправления ошибок высшего порядка для повышения коэффициента выхода годных кристаллов и снижения затрат.

Вследствие емкостной нагрузки от диодных элементов оптимальная структура запоминающего устройства, имеющего 8 плоскостей по 1 гигабиту в каждой плоскости, не будет иметь вид матриц 32768х32768. При увеличении размеров матрицы линейно возрастают как электрическая емкость шины строк (обусловленная диэлектрическими и диодными элементами), так и электрическая емкость шины столбцов. Рассеиваемая мощность определяется зарядом строки и проходящим через диоды током; электрическая емкость столбца непосредственно определяет время накопления заряда, требуемое для усилителей считывания. Для увеличения быстродействия может быть осуществлена сегментация блоков памяти по 1 гигабиту так, как показано на фиг.5, где для объединения нескольких таких плоскостей используют структуру многослойной укладки из фиг.4 с чередованием направления многослойной укладки между отдельными блоками, за счет увеличения площади "недвижимости" электронных схем формирователя. Но поскольку в этой конструкции большие области кремниевой подложки остаются неиспользованными (оставшаяся часть, предназначенная для кэш-памяти), эти издержки несущественны. Оптимальная сегментация в сильной степени зависит от варианта применения, в частности от среднего размера блока памяти, к которому осуществляют доступ. В общем случае, при уменьшении размера блока необходимы сегменты меньшего размера, что обусловлено рассеиваемой мощностью. Минимальная скорость при произвольной выборке также может быть резко увеличена путем увеличения количества сегментов запоминающего устройства. (Обе эти проблемы рассмотрены ниже).

Также возможно осуществить блоки множества матриц посредством использования только одной пары усилителей считывания, используя для столбцов общие сквозные перемычки с диодной изоляцией между плоскостями. Однако такая конструкция сильно теряет в быстродействии вследствие того, что для включения разделительного диода для плоскостей необходимо некоторое время. В будущем, когда появятся работоспособные активные разделительные МОП-транзисторы для матриц памяти, в некоторых вариантах применения могут быть использованы схемы с одним усилителем считывания. Но выигрыш в размере кристалла будет минимальным, поскольку нижележащая подложка не имеет ограничений, обусловленных "недвижимостью".

Для того, чтобы достичь требуемых скоростей передачи данных, должна быть осуществлена фиксация всех усилителей считывания в течение строба данных, обеспечивающего поблочную пересылку к логическим схемам дешифратора столбца. Это естественным образом происходит в кэш-памяти статического ОЗУ, что обусловлено его конструкцией. Допуская возможность замены на CD-ROM (постоянное запоминающее устройство на компакт-диске), большее количество разрешений на доступ к данным будет поступать от кэша столбца на регистрах-защелках без дополнительных стробов данных для строк.

Также могли бы вызывать беспокойство ограничения, обусловленные высокой плотностью сквозных перемычек между уровнем устройств и верхними блоками памяти, но это не так, поскольку сквозные перемычки могут быть расположены в шахматном порядке, что удовлетворяет как нормам проектирования для присоединения обычных сквозных перемычек, так и реализации плотной трассировки металлизированных межсоединений для матриц памяти. Одним из возможных решений является расположение сквозных перемычек просто в шахматном порядке, как показано на фиг.6. Сквозные перемычки располагают в шахматном порядке в вертикальном (или в горизонтальном) направлении относительно кристалла так, чтобы были строго удовлетворены следующие условия: размер сквозной перемычки равен 2х2λ, размер области перекрытия металлизации со всех сторон сквозной перемычки равен 1λ, минимальное расстояние между сквозными перемычками равно 3λ, при этом внутри самой матрицы памяти целиком сохраняют плотную трассировку металлизированных межсоединений. Обычно сквозные перемычки отстоят одна от другой на большее расстояние, чем показано, чтобы фактически обеспечить требуемое пространство для усилителя считывания или формирователей строк. При этой схеме расположения одна из N шин оказывается утраченной. Для сохранения однородной плотности металлизации и оптимизации разработки технологического процесса (необходимой для введения шага металлизации помимо норм проектирования для произвольной логики) отсутствующую шину заменяют фиктивной металлической токопроводящей дорожкой (не имеющей соединений). Приведенные в описанном ниже анализе схемного решения результаты вычислений получены с учетом уменьшения плотности строк/столбцов в результате использования этого принципа расположения в шахматном порядке. Несмотря на то, что в качестве примера служила сквозная перемычка размером 2λ, очевидно, что для соединения матриц памяти со слоем металлизации Металл 1 или 2 может быть использована сквозная перемычка произвольного размера.

В дальнейшем с использованием описанной выше общей схемы расположения, может быть определен требуемый размер кристалла. Плотность матрицы памяти ограничена шагом металлизации при трассировке запоминающего устройства и определяет общую плотность записи в запоминающем устройстве. Для консервативной конструкции необходимый шаг металлизации обусловлен как минимальным перекрытием сквозных перемычек, так и расстоянием между металлизированными дорожками. Общий размер кристалла в этом случае будет приблизительно на 20% больше, чем сама матрица памяти (для схемы расположения в шахматном порядке и периферийных формирователей). Однако необходимость ограничивать металлизацию посредством ограничений, налагаемых на конструкции произвольной логики, отсутствует. При переходе к матрице с максимальной плотностью металлизации, имеющей одинаковые промежутки и плотность, ширина дорожки и промежуток между ними могут быть значительно уменьшены. При условии, что нерегулярная трассировка на матрицах памяти минимизирована, процессы литографии и травления могут быть определенным образом оптимизированы для обеспечения частого шага металлизации, что позволяет использовать дорожки различной ширины или шириной металл 1 даже в этих верхних слоях. Это не может быть применено к сквозным перемычкам, но, как показано выше, они могут быть успешно изготовлены в рамках ограничений, обусловленных нормами проектирования.

Кроме того, для ячейки памяти, имеющей простую конструкцию, не требуется наличия перекрытия металлизации сквозных перемычек внутри ячеек памяти; несовпадения при литографии могут уменьшить площадь контакта (по одной оси), но последующий межслойный диэлектрик осуществит пассивирование открытой части диода. Эти два видоизменения процесса позволяют обеспечить максимальный шаг металлизации, что в результате приводит к тому, что площади ячеек становятся равными 4λ2 (где λ приблизительно равна ширине металлизированной дорожки/промежутку между ними).

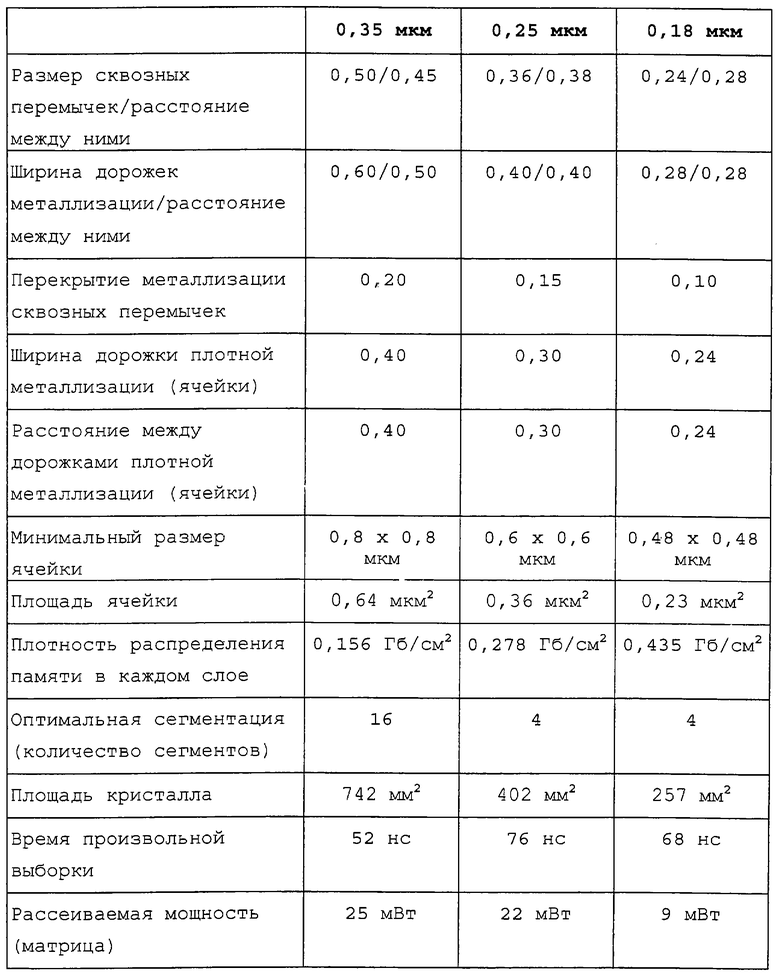

В табл. 1 приведено полное сравнение трех технологий, основанных на 0,35, 0,25 и 0,18 мкм литографии (нормы проектирования взяты из наращиваемых конструкций, полученных с использованием как тонкопленочных (TSMC), так и МОП-технологий (MOSIS)). В приведенной ниже таблице суммированы результаты для схем емкостью 1 гигабайт (Гб), в предположении, что средний размер поблочных пересылок равен 512 байт и что устройство должно обеспечивать общую скорость передачи данных 1000 Мб/с (мегабайт в секунду). Сегментация представляет собой рекомендованный размер для обеспечения соответствия времени выборки тому требованию, чтобы его максимальное значение было равным 100 нc.

Таким образом, посредством существующих 0,25-микронных технологий можно выполнить запоминающее устройство емкостью 1 Гб с размером кристалла в пределах приемлемых ограничений (<500 мм2). Согласно нормам проектирования размер кристалла однокристальной микросхемы, вероятно, слишком велик для его изготовления посредством 0,35-микронной технологии, но может быть изготовлена матрица емкостью 0,5 Гб. Единственное предостережение в отношении 0,35-микронной технологии состоит в том, что планаризация металла верхнего уровня должна быть осуществлена посредством СМР-процесса для обеспечения требуемой плоскостности для плотной металлизации в верхних слоях.

Далее будут рассмотрены быстродействие запоминающего устройства и рассеяние мощности в зависимости от конструкции и рабочих параметров.

Расчетные параметры. Для данного примера устройства были использованы следующие приближения.

Паразитные электрические емкости шин строк и столбцов считают равными частичной емкости.

Толщина межслойного диэлектрика эквивалентна толщине 300 нм двуокиси кремния (SiO2).

Удельная электропроводность металлизированных шин равна 0,07 Ом/см2.

Минимальное пороговое значение для усилителя считывания равно 10 мВ.

Крутизна характеристики диода равна 103 А/см2 для напряжения прямого смещения 1 В.

Диоды имеют односторонний переход с шириной обедненной зоны 400 нм при нулевом смещении (легирование 1017).

Скорость передачи данных. Требуемая долговременная скорость передачи данных 1 Гбит/с может быть легко достигнута при заполнении регистров-защелок столбцов. Даже при наличии 4096 сегментов каждое обращение к строке соответствует 8192 регистрам-защелкам, при этом требуется, чтобы время считывания строки равнялось всего 10 мкс, тогда как реальные времена выборки данных составляют менее 1 мкс. Однако это предполагает, что передача данных является в высокой степени коррелированной и используют все 8192 битов столбца. При нарушении этого условия возникают потери производительности.

Время выборки. Мгновенную скорость выборки данных (время от строба адреса строки (RAS) до доступа к данным в регистрах-защелках строба адреса столбца (CAS)) определяют по времени зарядки электрической емкости шины столбцов через диоды. Значение именно этого параметра наиболее сложно обеспечить в ячейке ПЗУ на основе диода. Время является комплексной функцией размера матрицы (сегментации), проводимости диода, электрической емкости диода (основное), сопротивления шины управления строкой и минимальной чувствительности по напряжению усилителя считывания.

Время выборки есть сумма времени зарядки строки (RстрокиСстроки) (RrowCrow), времени интеграции при считывании столбца до минимального заданного перепада напряжения (СстолбцаΔV/Iдиода) (CcolΔV/Idiode) и приближенного значения задержек произвольной логики при адресации строки/столбца.

Как показано на графике из фиг.7, скорость выборки лишь в незначительной степени зависит от нормативов, используемых в литографии, но сильно зависит от количества сегментов. При наличии в матрице более 16 сегментов ее прирост уменьшается.

Рассеяние мощности. Основным параметром конструкции, влияющим на рассеяние мощности является средний размер блока, передаваемого при каждом считывании. До тех пор, пока запрос на считывание может быть получен из кэша считывания строки, мощность, требуемая для усилителей зарядки и считывания, может быть усреднена по большому количеству циклов считывания. Но если выборка становится произвольной, что требует наличия цикла зарядки строк для каждой выборки, то потребляемая мощность существенно увеличивается. На графике из фиг.8 изображена функция зависимости оценочного значения потребляемой мощности от среднего размера блока считывания при долговременной скорости передачи данных, равной 1000 Гб/с. Для этого было использовано устройство, состоящее из четырех сегментов, которое было выполнено по 0,25-микронной технологии. Следует отметить, что масштаб является логарифмическим. До тех пор, пока средний размер блока остается большим, чем несколько сотен, рассеяние мощности обусловлено внутренними пересылками. Однако при уменьшении размера необходимы дополнительные операции считывания строк, и мощность увеличивается обратно пропорционально размеру блока.

Изготовление матрицы памяти. Для осуществления, например, памяти ПЗУ в виде множества плоскостей согласно настоящему изобретению необходимо, чтобы при обработке верхнего уровня было обеспечено сохранение плоских структур при минимальном наращивании микрорельефа (более 12-ти слоев металлизации). Обработка должна быть выполнена с учетом того, что металлизированные дорожки оказывают воздействие на сквозные перемычки строк/столбцов, что фактически ограничивает температуру обработки величиной <250oС. В предпочтительном варианте, изготовление диодов должно также быть осуществлено посредством самосовмещения со сквозными перемычками контактов для уменьшения количества фотошаблонов.

В дальнейшем будет приведено описание двух вариантов осуществления с использованием неорганических полупроводниковых материалов, в том числе селективного нанесения микрокристаллического кремния на слой металла/затравочного кремния через сквозные перемычки (либо нанесение сплошным слоем и СМР-травление) и взрывной кристаллизации сплошного слоя кремния а-типа, при которой для планаризации остается высо-корезистивный кремний а-типа, с использованием модуляции интенсивности лазерного излучения посредством межслойного диэлектрика.

В отличие от традиционной планарной компоновки, применяемой в используемой в настоящее время технологии, при плотности запоминающего устройства 4λ2, имеющего вертикальную компоновку, необходимо, чтобы была выполнена полная обработка разделительных диодов и обеспечен их контакт. Разделительные диоды как в ПЗУ, так и в ОЗУ с импедансным управлением изготавливают непосредственно на металлизированных дорожках строк/столбцов так, как показано на фиг. 9. Левая ячейка памяти, служащая для ПЗУ, находится во включенном состоянии, тогда как правая ячейка памяти остается в выключенном состоянии. При самой простой компоновке единственным различием между ячейками памяти является наличие или отсутствие выемки в межслойном диэлектрике, которую формируют над материалом диода. Будут описаны некоторые конкретные способы изготовления, начиная с наиболее сложного, в котором используют современные промышленные технологии, и кончая способами, которые включают в себя только менее известные процессы.

Ниже приводится описание способов изготовления вертикальных диодов посредством обработки с использованием направленной энергии со ссылкой на конкретные примеры обработки.

Пример А - изготовление диодов непосредственно на слое металлизации с полимерными/низкотемпературными подложками.

Для всех методик изготовления общим является формирование имеющего вертикальную ориентацию диода с р - n - переходом непосредственно на плотной матрице металлических токопроводящих дорожек, образующих шины строк или столбцов запоминающего устройства. Кратковременная термообработка, в частности импульсным лазерным излучением или ионным пучком, является предпочтительным способом изготовления, поскольку она пригодна и для других низкотемпературных материалов, применяемых для устройств ОЗМС/ОЗУ. Способ включает в себя следующие операции.

I. Нанесение металлической пленки для нижележащей матрицы строк/столбцов. Выбор нижележащего металла отчасти зависит от описанного ниже способа. Металлическая пленка может быть многослойной, состоящей из имеющего высокую проводимость нижнего слоя (алюминия - Аl) и барьера в пограничной области для обеспечения контакта с кремнием (например, из вольфрама).

II. Нанесение тонкого слоя аморфного кремния, легированного донором (n-типа), например, посредством напыления, электронно-лучевого напыления или плазмохимического осаждения из газовой фазы (PECVD).

III. Нанесение на этом же участке второго слоя из легированного акцептором (р-типа) кремния или германия.

IV. Кристаллизация аморфных пленок под действием лазерного излучения, образующих поликристаллические диоды с р - n переходом. Плотность энергии выбирают такой, чтобы достичь полного или почти полного плавления кремниевой пленки, что приводит к образованию центров кристаллизации от слоя металла. Следствием этого является образование высокозернистых (>50 нм) поликристаллических диодов, переходы которых находятся около исходной границы осаждения р - n примесей.

V. Маскирование и травление шин строк, расположенных на нижнем уровне, а после этого конформное нанесение межслойного диэлектрика (двуокиси кремния - SiO2).

VI. Нанесение шаблона уровня контактов, определяющего "включенные" и "выключенные" ячейки памяти.

VII. Нанесение металла столбца и травление шаблона.

Пример Б - вариант с использованием взрывной кристаллизации.

Интегральная плотность потока излучения, необходимая для кристаллизации, описанной выше как операция (IV), обусловлена толщиной пленки. В альтернативном варианте кристаллизация может быть осуществлена с использованием взрывной кристаллизации (М.О. Томпсон, журнал "Phys. Rev. Lett.", т.52, с. 2360, 1984г.) (М.О. Thompson, Phys. Rev. Lett. 52:2360, 1984], то есть способа, для которого требуется только образование минимальной области расплавленного вещества на поверхности. Разность энтальпий между аморфной и кристаллической фазами инициирует плавление сквозь пленку с минимальным результирующим термическим воздействием на нижний слой металла. Полученный в результате этого слой диодов имеет смешанную аморфную/поликристаллическую фазу, но сохраняет достаточную плотность тока (100 А/см2) для использования в качестве изолирующего слоя запоминающего устройства.

Пример В - вариант с использованием диодов Шотки.

Вместо нанесения пленок р- и n-типа для плоскостного диода процесс может быть видоизменен таким образом, чтобы непосредственно создавать диоды с барьером Шотки с использованием нижней металлической пленки. Этот вариант включает в себя нанесение пленки только n-типа, кристаллизацию и формирование барьера Шотки либо непосредственно с металлом (минимальное взаимодействие с жидкостью), либо с силицидной фазой, образованной посредством частичного расплавления металлического контакта. В этом варианте наиболее целесообразно использовать взрывную кристаллизацию для того, чтобы тепловая энергия, рассеиваемая в слое металла, была минимальной.

Пример Г - вариант с автолегированием от металлического контакта.

В металлическую пленку могут быть внедрены электрически активные легирующие примеси, что устраняет необходимость наличия отдельных пленок кремния n- и р-типа (вышеприведенные операции II и III). Нанесение на слой металлизации из вольфрама тонкого слоя мышьяка или бора, или сплава, содержащего бор или мышьяк, может обеспечить компенсирующее легирование при нанесении одиночной пленки. Частичное плавление и введение примесей от металла или металлического покрытия, сопровождаемое диффузией жидкой фазы и, возможно, сегрегацией при кристаллизации, также формируют р - n - переход. Положение границы раздела регулируют посредством динамики кристаллизации, но его также можно регулировать посредством изменения интегральной плотности потока излучения, в основном опять-таки в режиме взрывной кристаллизации.

Пример Д - вариант с использованием германия.

Все вышеуказанные способы работают одинаково хорошо и с германием вместо кремния. Несмотря на то, что поликристаллические германиевые диоды могут иметь более высокий ток утечки, это возмещается снижением всех температур жидкостного процесса на 450К. Хотя фаза расплавленного состояния является кратковременной, тем не менее она является в высшей степени активной химически.

Пример Е - выбор металла.

Помимо варианта, раскрытого выше как пример В, главным необходимым условием для металла является обеспечение минимального взаимодействия с расплавленным полупроводником при отвердевании. В таком случае перечень возможных металлов включает в себя тугоплавкие металлы, такие как тантал, вольфрам и платина, полупереходные металлы, включающие в себя палладий (Pd), молибден (Мо), никель (Ni), кобальт (Со) или хром (Сr), диффузионные токовые барьеры, такие как нитрид титана (TiN), и временные силицидные фазы типа NiSi2. Все природные металлы образуют устойчивые силицидные фазы, и ожидается наличие умеренной реакции с жидким кремнием или германием. Использование устойчивого силицида свело бы подобные реакции к минимуму; однако поскольку силициды к тому же являются неплохими проводниками, формирование тонкого слоя силицида обычно не вызывает проблем. Для осуществления варианта, приведенного как пример В, необходимо создать силицид, имеющий строго определенные границы.

Для самосовмещения и планаризации диодов может быть введена определенная обработка.

Описанный в вышеприведенном примере А процесс представляет собой традиционную обработку полупроводника, включающую в себя точное наложение контактного фотошаблона на нижележащую металлизированную структуру для строк. Кроме того, процессы травления создают увеличение неровностей топологии, которые необходимо сгладить для обеспечения многослойной трехмерной интеграции. Однако разность удельной электропроводности между поликристаллической и аморфной фазой, составляющая 103-105, может быть использована для создания шаблонов границ самосовмещенных диодов с одновременным решением проблем планаризации. Основное изменение для этого режима состоит в том, чтобы оставить материал, имеющий аморфную фазу, в областях между диодами и минимизировать высоту топологических элементов. В этом случае последовательность технологических операций была бы следующей.

I. Нанесение металла для шин строк и формирование их рисунка. Его полностью вытравливают и выравнивают посредством диэлектрика, расположенного между металлическими токопроводящими дорожками.

II. Нанесение сплошных аморфных пленок n- и р-типа (или одиночного слоя посредством описанных выше вариантов).

III. Нанесение контактного диэлектрика и тонкого слоя металлического отражателя (хрома или алюминия). Рисунок вытравливают, оставляя сквозные перемычки там, где должны быть сформированы диоды.

IV. Облучение лазерным излучением через структурированную пленку. Только в сквозных перемычках будет поглощена энергия, достаточная для того, чтобы инициировать кристаллизацию кремния (взрывное или полное плавление).

V. Нанесение металла для шин столбцов. (Пленку отражателя, если она выполнена из совместимого металла, не следует удалять до нанесения - она может быть вытравлена одновременно). Формирование рисунка шин столбцов и его вытравливание.

VI. Нанесение диэлектрика и планаризация.

В этом процессе требования к совмещению металла столбца с регулярно расположенными сквозными перемычками являются менее строгими. Неправильное совмещение не может привести к короткому замыканию между столбцом и строкой, так как нижележащий металл полностью покрыт аморфным кремнием. Необходимо сохранять достаточно низкую удельную электропроводность аморфного кремния, чтобы перекрестные помехи между шинами строк были несущественными. Этого легко достигнуть путем использования пленок очень слаболегированного кремния а-типа с диодом, сформированным посредством введения легирующих примесей от нижележащей металлизации (см. приведенный выше пример Г). Для полученной в результате этого диодной структуры может быть дана ссылка на фиг.10.

В другом варианте для инициализации кристаллизации вместо использования коротковолнового лазера (эксимерного лазеpa) в качестве источника излучения используют длинноволновый лазер. На длине волны 1,06 мкм (длина волны лазера на аллюмоиттриевом гранате с неодимом - Nd:YAG) аморфный кремний имеет достаточную прозрачность, так что энергия может проходить через аморфную пленку и быть поглощена только нижележащей металлической пленкой. Затем указанный металл инициирует взрывную кристаллизацию (или полное плавление). Преимущество данного режима состоит в том, что диоды формируют только в области металла шины строк.

Наконец, вместо использования рисунка, нанесенного на пластину, рисунок диодных матриц может быть сформирован посредством использования структурированного луча лазера (строящего изображение через фотошаблон). Этот вариант имеет ограничения, обусловленные большими размерами топологических элементов (1 мкм), но устраняет несколько фотолитографических операций.

Настоящее изобретение ни в коем случае не ограничено устройствами ПЗУ, а, как указано во введении, может быть осуществлено в виде запоминающих устройств и устройств обработки данных и модулей различных типов. Ниже будет приведено краткое описание альтернативных предпочтительных вариантов осуществления.

Описанные выше основные конфигурации могут также быть адаптированы для использования в качестве устройств ОЗМС. Это осуществляют на основе массивов пассивных матриц, в которых все точки пересечения изначально обладают свойствами выпрямительных диодов. Запись в заданную точку пересечения осуществляют путем создания разомкнутой цепи, то есть путем разрушения прямой проводимости диода.

В одной из категорий вариантов осуществления массив матриц изготавливают путем прослаивания сопряженного полимера между двумя наборами параллельных электродов, которые образуют пассивную матрицу, причем материал электрода и слоистый материал выбирают таким образом, чтобы выпрямительный диод в каждой точке пересечения был сформулирован самопроизвольно. Физика данного процесса была полностью исследована и описана в научной литературе. Запись в заданную точку пересечения осуществляют одним из нескольких способов. Наиболее простой, но не единственный способ, сводится к созданию в точке пересечения теплового дефекта посредством короткого, но сильного импульса тока через полимерный материал, сопровождаемому пространственно управляемым снижением проводимости, или разомкнутой цепи. Описания соответствующих материалов и конфигурации приведены в указанных ниже заявках на изобретение, владельцем которых является настоящий заявитель, в частности заявки на патент Норвегии 972803 и 973390 и производные от них заявки на изобретение.

При осуществлении считывания с малым смещением, что является близкой аналогией предпочтительному варианту осуществления, описанному выше в разделе 4 (IV), для записи необходимы более высокие значения токов и иной протокол подачи импульсов. Таким образом, чтобы получить в диодном переходе требуемую тепловую предысторию, необходимо осуществить тщательное управление совокупностью временных параметров рассеяния энергии в точке пересечения, а также ограничить область вызванного током изменения импеданса (например, теплового дефекта) точкой пересечения, в которую производят запись. Эти подходы подразумевают, что электронные схемы для запоминающего устройства ОЗМС являются более сложными по сравнению с ПЗУ, и учет этого вместе с необходимостью обеспечения более высоких значений тока при записи приводит к тому, что плотность расположения битов является несколько уменьшенной. С другой стороны, полностью электронный процесс записи подразумевает, что при изготовлении, например, ПЗУ с масочным программированием избегают операций обработки, основанных на кремниевом литье.

Для специалиста в данной области техники очевидно, что описанные выше основные конфигурации открывают возможности для объединения массивов ПЗУ, устройств ОЗМС и ПЕРЕЗАПИСЫВАЕМЫХ устройств в одном устройстве, либо в одном и том же слое или слоях, либо в виде отдельных слоев ПЗУ, устройств ОЗМС и ПЕРЕЗАПИСЫВАЕМЫХ устройств в одной многослойной структуре. Из многих вытекающих из этого возможностей следует в особенности отметить объединение этих типов запоминающих устройств.

Увеличение выхода годных изделий достигается посредством самодиагностики. Чтобы определить ошибки в запоминающем устройстве, в ПЗУ приводят в действие программу самодиагностики, которая является частью методики послепроизводственного контроля и проверки на соответствие техническим условиям. Результаты сохраняют в устройстве ОЗМС и обеспечивают их связь с командами, полученными из ПЗУ, что приводит к обходу или исправлению ошибок в устройстве запоминающего устройства. Указанную операцию осуществляют понятным для пользователя способом, кроме возможного времени ожидания. Таким образом может быть увеличен выход годных изделий при изготовлении.

Прямым расширением области применения вышеупомянутых устройств, которые могут объединять в себе различные типы запоминающих устройств, является включение вычислительных ресурсов в состав двух- и трехмерных структур. Таким образом, распределенные процессоры (содержащие в себе микропроцессоры, но не ограниченные ими), обладающие быстрым и прямым доступом к расположенным в физической близости специализированным запоминающим устройствам, должны обеспечить такое быстродействие и гибкость, которые не могут быть достигнуты посредством процессорных/микропроцессорных конфигураций, основанных на традиционной технологии изготовления кремниевых пластин. Для более исчерпывающего рассмотрения указанных и смежных аспектов, в частности, объединенных структур запоминающих обрабатывающих устройств с наращиваемой архитектурой, может быть приведена ссылка на заявку на патент Норвегии 982518, которая обеспечивает приоритет настоящей заявки и в которой, по существу, взят опубликованный материал по компьютерной тематике.

Очевидно, что настоящее изобретение позволяет расширить концепции и конкретные варианты осуществления, приведенные в вышеприведенном опубликованном материале, посредством новых конфигурационных решений, а также посредством использования материалов и процессов, которые способствуют осуществлению двух- и трехмерных структур высокой плотности.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕГНЕТОЭЛЕКТРИЧЕСКОЕ УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ | 1998 |

|

RU2184400C2 |

| МАСШТАБИРУЕМОЕ ИНТЕГРИРОВАННОЕ УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ | 1999 |

|

RU2201015C2 |

| ПОСТОЯННАЯ ПАМЯТЬ И ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1998 |

|

RU2212716C2 |

| ПОСТОЯННАЯ ПАМЯТЬ И ПОСТОЯННЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА | 1998 |

|

RU2216055C2 |

| ЭЛЕКТРИЧЕСКИ АДРЕСУЕМОЕ УСТРОЙСТВО, СПОСОБ ЭЛЕКТРИЧЕСКОЙ АДРЕСАЦИИ И ИСПОЛЬЗОВАНИЕ ЭТОГО УСТРОЙСТВА И ЭТОГО СПОСОБА | 1998 |

|

RU2182732C2 |

| МАСШТАБИРУЕМОЕ УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ | 1999 |

|

RU2201639C1 |

| ПРИБОР С МАТРИЧНОЙ АДРЕСАЦИЕЙ, СОДЕРЖАЩИЙ ОДНО ИЛИ НЕСКОЛЬКО ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2002 |

|

RU2261500C2 |

| ТРЕХМЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2002 |

|

RU2274913C2 |

| СПОСОБ ФОРМИРОВАНИЯ ЭЛЕКТРОПРОВОДЯЩИХ И/ИЛИ ПОЛУПРОВОДНИКОВЫХ ТРЕХМЕРНЫХ СТРУКТУР, СПОСОБ УНИЧТОЖЕНИЯ ЭТИХ СТРУКТУР И ГЕНЕРАТОР/МОДУЛЯТОР ЭЛЕКТРИЧЕСКОГО ПОЛЯ ДЛЯ ИСПОЛЬЗОВАНИЯ В СПОСОБЕ ФОРМИРОВАНИЯ | 1999 |

|

RU2210834C2 |

| ПОЛЕВОЙ ТРАНЗИСТОР | 1999 |

|

RU2189665C2 |

Изобретение относится к устройству хранения и обработки данных и способу его изготовления. Устройство содержит расположенные на подложке модули памяти ПЗУ и/или ОЗМС, и/или ПЕРЕЗАПИСЫВАЕМЫЕ, и/или модули обработки. Модули памяти и/или обработки создают в виде одного или множества основных слоев, расположенных поверх подложки. Устройство содержит в себе активные компоненты, обеспечивающие функционирование устройства. Согласно способу изготовления устройства модули памяти и/или модули обработки формируют на подложке путем операций последовательного нанесения слоев. Нанесение и обработку слоев производят в тепловом режиме, при котором уже нанесенный и обработанный нижележащий слой или слои не подвергают воздействию статических или динамических температур, превышающих заданные пределы устойчивости. В результате предложенной конфигурации плотные двумерные комбинации однобитовых ячеек могут быть объединены в трехмерные структуры памяти с уменьшенными затратами. Устройство также имеет короткие времена произвольной выборки, повышенную скорость передачи данных, уменьшенную потребляемую мощность при одновременном повышении плотности упаковки. При создании используются низкотемпературные процессы и пригодные для них материалы. 2 с. и 35 з.п.ф-лы, 10 ил.