Данное изобретение относится к электрически адресуемой энергонезависимой постоянной памяти, содержащей совокупность ячеек памяти, каждой из которых во время операции записи, как части процесса изготовления постоянной памяти, на постоянное время присваивают одно из двух или более логических состояний в соответствии с определенным протоколом, который в этой памяти определяет постоянно записанные или запомненные данные, и пассивную матрицу проводников для адресации, причем пассивная матрица проводников содержит первую и вторую электродные структуры в соответствующих взаимно отделенных интервалом и параллельных плоскостях с параллельными электродами в каждой плоскости и выполнена с возможностью формирования электродами по существу ортогональной х-, у-матрицы, при этом электроды в первой электродной структуре содержат вертикальные шины матрицы, или х-электроды, а электроды во второй электродной структуре содержат горизонтальные шины матрицы, или у-электроды, при этом, по меньшей мере, часть объема между пересечением х-электрода и у-электрода определяет ячейку памяти в постоянной памяти, причем каждая из перекрывающих друг друга частей х-электрода и у-электрода в ячейке памяти определяет контактную площадку в ячейке памяти, причем, по меньшей мере, один полупроводниковый материал обеспечивают между электродными структурами и он обладает выпрямляющими свойствами в отношении выбранного электропроводного электродного материала и электроизолирующего материала.

Причем полупроводниковый материал в электрическом контакте с электродом в ячейке памяти формирует диодный переход на границе между полупроводниковым материалом и электродным материалом, причем первое логическое состояние ячейки памяти в постоянной памяти формируют активной частью полупроводникового материала, покрывающего всю контактную площадку ячейки памяти, при этом диодный переход включает в себя всю контактную площадку ячейки памяти, при этом второе логическое состояние в выбранной ячейке памяти в постоянной памяти формируют, по меньшей мере, одной электродной структурой в ячейке памяти, покрываемой изолирующим материалом, и при этом логическое состояние в каждом случае создают значением полного сопротивления ячейки памяти, при этом указанное значение полного сопротивления по существу создают одним или более факторами из числа следующих: характеристики полного сопротивления полупроводникового материала, характеристики полного сопротивления изолирующего материала и характеристика полного сопротивления диодного перехода.

Данное изобретение также относится к постоянному запоминающему устройству, которое содержит одну или более постоянных памятей в соответствии с данным изобретением, и к постоянному запоминающему устройству, которое содержит две или более постоянных памятей в соответствии с данным изобретением.

Матричная адресация ячеек запоминающего устройства данных или разрядных ячеек на плоскости является простым и эффективным способом обеспечения большого числа доступных ячеек памяти с умеренным числом электрически адресуемых шин. В квадратной х, у-матрице с n-шин, соответственно, как в х-направлении, так и в у-направлении число ячеек памяти составляет n2. В той или иной форме этот основной принцип в настоящее время осуществляют во множестве разных осуществлений полупроводниковых средств памяти. В них ячейка памяти содержит простые электронные схемы, которые осуществляют внешнее сообщение через пересечение в матрице и элементе памяти и обычно являются устройством запоминания заряда. Несмотря на то, что эти средства были очень успешными с технической и коммерческой точек зрения, у них есть ряд недостатков, и в частности тот недостаток, что каждая ячейка памяти имеет сложную архитектуру, обусловливающую повышенную себестоимость и пониженную плотность размещения информации. В крупном подклассе так называемых энергозависимых запоминающих устройств схемы должны постоянно сохранять питание током, и этому сопутствует нагрев и потребление электроэнергии для сохранения запомненной информации. С другой стороны, энергонезависимые средства не имеют этой проблемы, но зато имеют пониженный доступ и большее время переключения, и также увеличенное энергопотребление и повышенную усложненность.

Из известного уровня техники известен ряд примеров постоянных памятей на базе полупроводников с электрической адресацией в пассивной матрице. Так, патент США 4099260 (Lynn et al.) раскрывает полупроводниковую постоянную память на базе полупроводников (ПЗУ), выполненную в виде устройства интегральной схемы с высокой степенью интеграции, в котором самоизолирующиеся зоны поверхности разрядной шины одного типа проводимости формируют в полупроводниковой подложке и непосредственно в объемной зоне подложки противоположного типа проводимости. В интервалах между зонами разрядных шин формируют каналоограничительные участки того же типа проводимости, что и в объемной зоне. Металлические числовые шины, находящиеся сверху зон разрядных шин и ортогональные по отношению к ним, формируют отдельно от них посредством изолирующего слоя. Ячейка памяти содержит один диод Шотки. Диод этого типа формируют или не формируют на каждом пересечении между числовой шиной и разрядной шиной в зависимости от следующего: формируют или не формируют отверстие в изолирующем слое во время изготовления, чтобы обеспечить для числовой шины возможность контактировать с немного легированной частью разрядной шины. Считается, что ПЗУ этого типа имеет небольшую площадь, высокую скорость, низкое рассеяние энергии и небольшую себестоимость.

Из патента США 4000713 (Bauge & Mollier) известно устройство с полупроводниковыми элементами, такими как диоды Шотки и транзисторы, выполненные интегрально в виде матрицы на кристаллах. Матрица может быть индивидуально изготовлена в целях обеспечения необходимой функции. Например, ее можно использовать в качестве матриц И или ИЛИ в программируемых логических матрицах или в качестве постоянных памятей, которые считаются имеющими лучшие свойства по плотности размещения информации и рассеянию энергии. Первую электродную структуру с параллельными металлическими электродами несколько отличающегося исполнения обеспечивают на полупроводниковой подложке, например, р-типа. Оксидный слой обеспечивают на полупроводниковой подложке, и отверстия формируют в оксидном слое для обеспечения анодных контактов и катодных контактов через металлические шины, которые образуют первый металлический уровень в электродной матрице. Две зоны п+ расположены под катодными контактами. Эти зоны проходят в находящиеся внизу коллекторные слои, в результате чего формируют диод Шотки. Над первым металлическим слоем или электродным уровнем обеспечивают изолирующий слой и над ним - второй металлический уровень, который содержит, например, ортогональную вторую электродную структуру. Отверстия в изолирующем слое обеспечивают контакт с катодным контактом в группе катодных контактов, которые содержатся в отдельном элементе в матрице.

Наконец, из патента США 5272370 (French) известно тонкопленочное ПЗУ на основе матрицы открытых и закрытых ячеек памяти, сформированных в стеке тонких пленок на стекле или другой подложке. Каждая закрытая ячейка памяти содержит тонкопленочный диод; и с помощью стеков полупроводниковых пленок, например, из гидрогенизированного аморфного кремния, в которых отдельные пленки имеют разные типы проводимости, можно получить диоды с разными характеристиками электропроводности. Тем самым можно увеличить информационное содержание в матрице ПЗУ. Каждый элемент памяти, который формируют с помощью диодной структуры, затем можно выполнить с разными логическими уровнями согласно некоторому протоколу изготовления. В тех случаях, когда элемент памяти не имеет диодной структуры или когда полупроводники покрыты изолирующим слоем, в результате чего электродный контакт не формируется, данный элемент памяти можно использовать для формирования определенного первого логического уровня, например логического "0".

Хотя во всех вышеупомянутых устройствах из известного уровня техники формируют электрическую адресацию в пассивной матрице известным образом путем обеспечения плоскостных диодов в закрытых электродных контактах, они - частично по причине применения разных типов полупроводников - имеют относительно высокий уровень усложненности. В устройстве ПЗУ, раскрываемом в последней упоминаемой публикации (патент США 5272370), возможно тем не менее запоминать более двух логических значений в матрице, но это предполагает использование разных типов диодов и поэтому нескольких слоев различным образом легированных полупроводников в разрядной ячейке с плоскостным диодом.

Поэтому первоочередной задачей данного изобретения является обеспечение постоянной памяти или ПЗУ, которое позволяет осуществление в пассивной матрице электрической адресации отдельной ячейки памяти в постоянной памяти и которое не нужно регенерировать для сохранения запомненных данных в ячейке памяти; и также простая и недорогая реализация постоянной памяти с помощью известных технологий и способов, применяемых в полупроводниковой и тонкопленочной технологии.

В частности, задача данного изобретения заключается в обеспечении энергонезависимой постоянной памяти на основе применения органических материалов, например полимеров, которую, при реализации в тонкопленочной технологии, можно использовать как в токопроводящих дорожках, так и в изоляторах и полупроводниковых материалах; и это, предположительно, даст более гибкие технические решения и, особенно, низкую себестоимость, относительно себестоимости при применении кристаллических неорганических полупроводников.

Еще одной задачей является обеспечение постоянной памяти, обеспечивающей многоуровневое кодирование заданных ячеек памяти или адресов ячейки памяти.

Наконец, задача данного изобретения заключается в обеспечении постоянной памяти, которую можно использовать для реализации объемного постоянного запоминающего устройства.

Эти задачи и преимущества достигают в соответствии с данным изобретением с использованием постоянной памяти, которая отличается тем, что одно или более дополнительных логических состояний в ячейке памяти постоянной памяти формируют активной частью полупроводникового материала, покрывающего только некоторую часть контактной площадки, и/или тем, что диодный переход включает в себя только некоторую часть контактной площадки, в результате чего данные, запомненные в этой памяти, могут быть представлены логическими состояниями в многозначном коде, и тем, что указанное одно или более дополнительных логических состояний создают значениями полного сопротивления, определяемого продолжением активной части полупроводникового материала и/или продолжением той части контактной площадки, которая формирует диодный переход.

Первое постоянное запоминающее устройство согласно данному изобретению отличается тем, что постоянную память обеспечивают на подложке полупроводникового материала или между подложками полупроводникового материала и посредством подложек соединяют с задающей схемой и управляющей схемой для приведения в действие и адресации, причем указанные задающая и управляющая схемы интегрированы в подложке или подложках и сформированы согласно полупроводниковой технологии, соответствующей материалу подложки, а второе постоянное запоминающее устройство согласно данному изобретению отличается тем, что постоянная память является стеком горизонтальных слоев в целях обеспечения объемного запоминающего устройства; тем, что объемное запоминающее устройство обеспечивают на подложке полупроводникового материала или между подложек полупроводникового материала и посредством подложки или подложек соединяют с задающей схемой и управляющей схемой для приведения в действие и адресации, причем указанные задающая и управляющая схемы интегрированы в подложке или подложках и сформированы согласно полупроводниковой технологии, соответствующей материалу подложки.

При этом постоянная память согласно данному изобретению образует память двоичной логики и целесообразно, чтобы первое логическое состояние, представляющее либо логический "0", либо логическую "1", создавалось сопротивлением по переменному току прямого смещения диода, сформированного в ячейке памяти, в которой полупроводниковый материал контактирует и с х-электродом, и с у-электродом, и при этом вторые или дополнительные логические состояния, которые соответственно представляют либо логическую "1", либо логический "0", создают выбранным значением сопротивления для изолирующего материала, обеспечиваемого в ячейке памяти, в которой полупроводниковый материал по большей части контактирует либо с х-электродом, либо с у-электродом, и при этом указанный изолирующий материал в ячейке памяти предпочтительно имеет бесконечное значение сопротивления.

Постоянную память согласно данному изобретению реализуют как многоуровневую логическую память с одним или более дополнительными логическими состояниями, при этом первое логическое состояние целесообразно создают сопротивлением по переменному току прямого смещения диода, сформированного в ячейке памяти, в которой полупроводниковый материал контактирует и с х-электродами, и с у-электродами, при этом дополнительные логические состояния создают заданными значениями сопротивления для изолирующего материала, обеспечиваемого в ячейке памяти, в которой полупроводниковый материал по большей части контактирует либо с х-электродом, либо с у-электродом, и выбранные определенные значения сопротивления в каждом случае находятся в пределах между сопротивлением по переменному току прямого смещения ячейки памяти, сформированной в диоде, и бесконечным значением.

В первом варианте реализации постоянной памяти согласно данному изобретению изолирующий материал в выбранных ячейках памяти обеспечивают между электродными структурами в виде отдельной слоеобразной изолирующей накладки, которая полностью или частично покрывает, по меньшей мере, один из электродов в ячейке памяти, при этом выбранная ячейка памяти, зависимая от активной части полупроводникового материала и/или части, представляющей собой диодный переход контактной площадки, в последнем случае получает логическое состояние, которое соответствует некоторому уровню многозначного кода.

Если в указанном первом варианте реализации изолирующая накладка полностью или частично покрывает только один из электродов, то полупроводниковый материал можно обеспечить между электродными структурами в слое по всему полю пластины и также на изолирующей накладке в выбранных ячейках памяти. Если изолирующая накладка полностью или частично покрывает оба электрода, то полупроводниковый материал можно предпочтительно обеспечить между электродными структурами и в прилегании к изолирующим накладкам в выбранных ячейках памяти, в результате чего полупроводниковый материал и изолирующие накладки выполняют взаимно заподлицо в общем сплошном слое.

Во втором варианте реализации постоянной памяти в соответствии с данным изобретением изолирующий слой обеспечивают между электродными структурами в виде по существу слоя по всему полю пластины, который покрывает, по меньшей мере, одну из электродных структур и имеет удаленные части в выбранных ячейках памяти, в результате чего удаленная часть полностью или частично экспонирует электроды в выбранной ячейке памяти, при этом ячейка памяти, зависимая от активной части полупроводникового материала и/или от части, представляющей собой диодный переход контактной площадки, в последнем случае получает логическое состояние, которое соответствует некоторому уровню многозначного кода.

Если изолирующий слой в указанном втором варианте реализации покрывает только одну из электродных структур, то полупроводниковый материал предпочтительно можно обеспечить между электродными структурами и на изолирующем слое в слое по всему полю пластины, и помимо этого он будет контактировать с электродными структурами в удаленных частях изолирующего слоя. Если изолирующий слой покрывает обе электродные структуры, то полупроводниковый материал можно предпочтительно обеспечить только между электродными структурами и в прилегании к изолирующему слою в выбранных ячейках памяти, в результате чего полупроводниковый материал и изолирующий слой выполняют взаимно заподлицо в общем сплошном слое. Наконец, согласно данному изобретению целесообразно, чтобы полупроводниковым материалом был аморфный кремний, поликристаллический кремний или органический полупроводник, причем органическим полупроводником предпочтительно является сопряженный полимер.

В соответствии с данным изобретением полупроводниковым материалом может быть анизотропный проводник. Полупроводниковый материал предпочтительно может содержать свыше одного полупроводника либо его можно добавить в или скомбинировать с электропроводным материалом.

Предпочтительно формировать полупроводниковый материал, изолирующий материал и электродные структуры в виде тонких пленок.

Предпосылки данного изобретения и различные примеры его осуществления далее излагаются более подробно со ссылкой на чертежи.

На фиг.1 представлено схематическое изображение общего осуществления запоминающего устройства, в котором пассивную электродную матрицу обеспечивают между объединительными платами или подложками.

На фиг.2 представлено схематическое изображение примеров контуров паразитного тока, которые могут возникать в матрице этого вида.

На фиг. 3а представлен вид первого осуществления постоянной памяти в соответствии с данным изобретением в горизонтальной проекции.

На фиг.3b представлено сечение вида постоянной памяти по фиг.3a по линии А-А в первом варианте этого осуществления.

На фиг.3с представлено сечение вида постоянной памяти по фиг.3а по линии А-А во втором варианте этого осуществления.

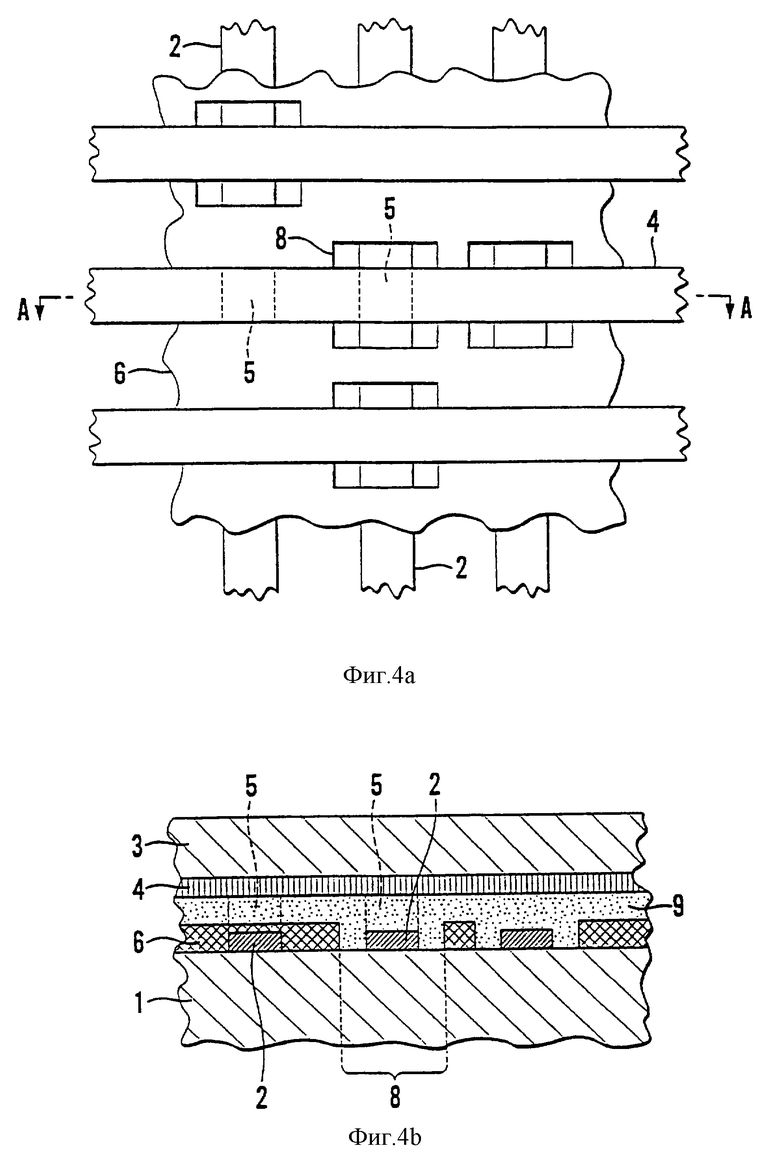

На фиг. 4а представлено второе осуществление постоянной памяти в соответствии с данным изобретением в горизонтальной проекции.

На фиг.4b представлено сечение вида постоянной памяти по фиг.4а по линии А-А в первом варианте этого осуществления.

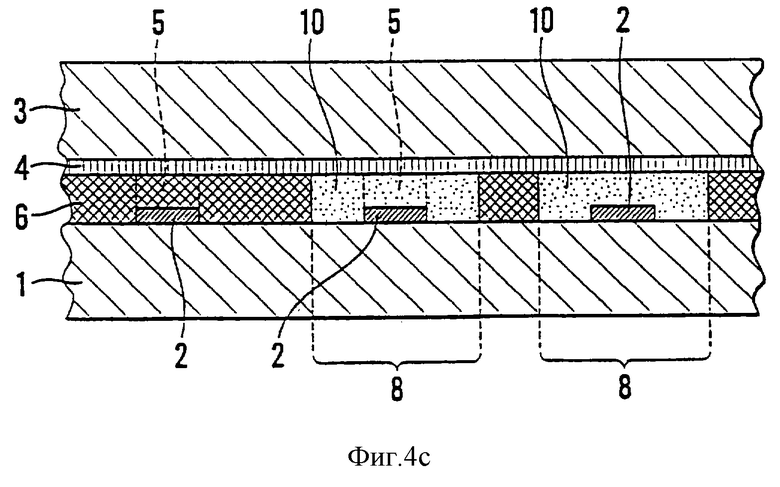

На фиг.4с представлено сечение вида постоянной памяти по фиг.4а по линии А-А во втором варианте этого осуществления.

На фиг.5а представлен пример многоуровневого кодирования ячейки памяти в осуществлении по фиг.3a.

На фиг.5b представлено сечение вида постоянной памяти по фиг.5а по линии В-В.

На фиг.6а представлен пример многоуровневого кодирования ячейки памяти в осуществлении по фиг.4а.

На фиг. 6b представлено сечение вида ячейки памяти по фиг.6а по линии В-В.

На фиг. 7 представлено сечение вида первого постоянного запоминающего устройства согласно данному изобретению.

На фиг. 8 представлено сечение вида второго постоянного запоминающего устройства согласно данному изобретению.

Далее следует более подробное описание предпосылок данного изобретения. Общая матричная система адресации изображена на фиг.1, где, например, электропроводные шины 2 взаимно отделены интервалами и проходят в х-направлении, и также, например, имеют n число налагающихся электрошин 4, которые проходят в у-направлении и соответственно формируют первую и вторую электродные структуры в ортогональной х-, у-электродной матрице. Х-электроды 2 и у-электроды 4 располагают достаточно близко друг к другу, в результате чего обеспечивают геометрически хорошо определенные перекрывающиеся зоны или пересечения между электродами. Объем вблизи и между каждым пересечением, приблизительно определяемый перекрывающейся зоной, созданной шириной пересекающихся х-электродов и у-электродов в этих пересечениях, определяет то, что далее обозначается как ячейка памяти 5 - см. фиг.2. Взаимно перекрывающиеся зоны соответственно х- и у-электродов 2, 4 в ячейке памяти 5 будут обозначаться как контактная площадка ячейки памяти. Согласно данному изобретению данные запоминают в каждой ячейке памяти как значения полного сопротивления, например значения сопротивления между х- и у-электродами в каждом пересечении. Логическое состояние в каждом пересечении или адрес ячейки памяти находят путем измерения полного сопротивления между х-электродом и у-электродом, которые пересекают друг друга в ячейке памяти.

В отличие от общеизвестных токоадресуемых и матричных систем памяти данное изобретение позволяет применение чисто пассивной электрической адресации, поскольку в ячейках памяти не имеется дискретных активных схемных элементов. Хорошо известно, что использование электронных запоминающих устройств с ячейками памяти в пассивной матрице затрудняется альтернативными токовыми цепями или цепями паразитных токов в электродной матрице. Эта проблема представлена на фиг.2, где альтернативные токовые цепи, формируемые адресацией ячейки памяти 5k1, созданной пересечением между электродами mk, n1, указаны более тонкими штрих-линиями, идущими в соседние ячейки памяти. С увеличением размера матрицы, т.е. произведения х на у, проблема паразитных токов тоже усугубляется. Если элементы памяти в каждом пересечении имеют чисто активное сопротивление, то это означает, что разница сопротивления в операции записи будет маскироваться токами, утечка которых происходит по альтернативным токовым цепям, согласно изображению на фиг.2. Если придать электрическому соединению в каждом пересечении высокую нелинейную вольт-амперную характеристику, то проблему паразитных токов можно уменьшить или вовсе устранить. Это довольно просто осуществляют уже хорошо известным из уровня техники способом, а именно за счет выпрямительного диода, подключенного последовательно в отношении полного сопротивления или сопротивления в каждом пересечении.

Основной целью данного изобретения является формирование сети диодов такого типа довольно простым, недорогим и надежным способом, который при этом также позволяет использование соответствующих структур памяти в виде регулируемых полных сопротивлений. Согласно данному изобретению х и у-электроды могут предпочтительно окружать слой полупроводникового материала, например, в тонкопленочной конфигурации. В частности, этот полупроводниковый материал может целесообразно быть сопряженным полимером теофенового или полифенилвинилового типа. Путем выбора соответствующего электродного материала для полупроводникового материала получают диодный переход на границе электрод - полупроводник, и диоду можно придать очень хорошие выпрямляющие свойства. Простой линейный анализ демонстрирует, что число электродных пересечений, т. е. ячеек памяти, которые можно адресовать без искажения или шума от паразитных токов, приблизительно равно отношению диодного выпрямления в каждом пересечении, т.е. взаимосвязи между прямотекущим и обратнотекущим токами в данном напряжении смещения.

Еще одна значительная проблема, связанная с запоминающими устройствами на пассивной матрице, изображаемыми на фиг.1, где слой сплошного материала с конечным значением сопротивления проходит в интервалы между пересечениями электродной матрицы, заключается в том, что токи даже при совершенном выпрямлении в каждом пересечении могут течь между электродными шинами 2, 4 в этих интервалах. Даже если длина токопроводящей дорожки в этих интервалах будет гораздо большей, чем длина в пересечениях, т.е. в ячейке памяти, и если слой между электродными структурами будет чрезвычайно тонким с высоким поверхностным сопротивлением, то комбинированный эффект многих этих токопроводящих дорожек будет вредить измеренному полному сопротивлению и поэтому, в конечном счете, установит верхний предел числу пересечений и также ячеек памяти, которые смогут быть реализованы в пассивной матрице.

Последний тип переходного затухания можно исключить за счет придания высокой анизотропии для активной проводимости пленки, т.е. за счет создания высокой активной проводимости в нужном направлении тока или низкой активной проводимости. В случае фиг. 1 это будет соответствовать высокой активной проводимости, перпендикулярной к плоскости матрицы, и низкой активной проводимости в плоскости матрицы. Полимерные составы со свойствами такого рода описаны в литературе, например в статье "White light emission from a polymer blend light emitting diode" of M. Granstrom и O. Inganas, Applied Physics Letters 68, 2:147-149 (1996), а электродные средства и устройства на их основе описаны в патентной заявке Норвегии 973390.

Начиная с известной принципиальной структуры в соответствии с фиг.1, согласно которой х- и у-электроды 2, 4 обеспечивают на каждой стороне анизотропной тонкой пленки с высоким отношением выпрямления в пересечениях электродов, данные можно кодировать с помощью управляемого осаждения электроизолирующего материала между диодами в выбранных пересечениях, и это более подробно будет изложено со ссылкой на фиг.3а. Если этим выбранным пересечениям придать бесконечное сопротивление, тогда можно будет выполнить двоичное кодирование каждого пересечения или каждой ячейки памяти, например, с помощью напряжения прямого смещения, которое дает либо логику "1", R=RF, где RF является сопротивлением по переменному току прямого смещения диода в этом пересечении, или логику "0" как R=∞, где бесконечное сопротивление намеренно введено в данное пересечение. Повышенная емкость запоминающего устройства будет получена с помощью более широкого диапазона значений сопротивления, который эквивалентен нескольким разрядам, запоминаемым в каждой ячейке памяти, например со значениями сопротивления R1,R2,R3,...,RF<R1<R2<R3<∞.

Первый вариант реализации постоянной памяти согласно данному изобретению далее излагается со ссылкой на фиг.3а-3с. В этом случае известную из уровня техники структуру формируют путем осаждения х-электродов на нижней подложке 1 или в объединительной плате, которую можно выполнить из полупроводникового материала 2 и которая содержит активные схемы для обработки сигнала, трассировки и управления логикой, интегрированные в х-электродах 2, которые здесь образуют первую электродную структуру в электродной матрице. Соответственно, верхний слой 3 может включать в себя схемы с у-электродами 4 таким же образом и для соответствующих целей. Подразумевается, что х-электроды 2 и у-электроды 4 могут использоваться для формирования, например, разрядных шин и числовых шин в постоянной памяти согласно данному изобретению. Обе подложки 1, 3 со схемами и электродами 2, 4 обрабатывают посредством стандартной полупроводниковой технологии, и они могут быть, например, кристаллической полупроводниковой пластиной, например из кремния, применяемой в качестве подложки. Альтернативно, кремний может иметь вид аморфного кремния либо могут использоваться полупроводниковые органические материалы на жестких или гибких опорах (объединительные платы). На следующем этапе любую из подложек 1, 3 или обе подложки 1, 3 можно кодировать таким образом, что получаемое таким образом постоянное запоминающее устройство воспримет нужное информационное содержание. Это целесообразно выполнить за счет обеспечения локализованных изолирующих пленок или пленок сопротивления 6 в виде накладок 7 на электродах 2, 4 на одной из подложек 1, 3, в результате чего они будут расположены в пересечении между х-электродом и у-электродом. Можно использовать обычные используемые в полупроводниковой технике материалы и также хорошо известную технологию осаждения и регулировки. Далее на изолирующих накладках 7 располагают полупроводниковый слой 9 по всему полю пластины согласно фиг. 3b (полупроводниковый слой 9 для ясности в фиг.3а не показан), который одновременно формирует диодный переход с электродным материалом в одной из электродных структур, например, в у-электродах 4. Выбранный полупроводниковый материал и выбранный материал в электродной структуре могут быть такими материалами, что при их использовании в тех местах, где экспонированные части электродных структур физически контактируют с полупроводниковым материалом, спонтанно формируются выпрямляющие переходы или диодные переходы.

Применяемый полупроводниковый материал должен обладать соответствующими выпрямляющими и проводящими свойствами и также желательно, чтобы он имел невысокую производственную себестоимость, простую обработку, чтобы он обладал длительным ресурсом и пр., и должен быть таким, чтобы можно было получить оптимальный контакт с материалом электродных структур. В качестве полупроводникового материала, например, можно использовать сопряженные полимеры, такие как тиофеновые или полифенилвиниловые полимеры. Альтернативно вместе с анизотропной проводящей тонкой пленкой из пластмассы можно применять аморфный кремний или поликристаллический кремний.

Основная процедура изготовления требует точной регулировки, когда изолирующие накладки 7 располагают на электродах 2, 4. Но этот этап можно легко выполнить путем непосредственного распространения процессов изготовления на активные схемы с электродными матрицами. Размещение полупроводниковой пленки 9 по всему полю пластины согласно фиг.3b можно осуществить без какой-либо прецизионной регулировки. Но у-электрод 4 должен быть обеспечен таким образом, чтобы изолирующие накладки 7 располагались в пересечениях между электродными структурами. Чем ближе друг к другу обеспечивают пересечения, тем более повышенная точность позиционирования требуется для этого. В этой связи применение прозрачной верхней подложки 3 с полупроводниковыми схемами на органических полупроводниках или на аморфном кремнии в сочетании с тонкой пленкой полупроводникового полимера может обеспечить такие возможности регулировки, которые нельзя достичь с помощью непрозрачных подложек из кристаллического кремния. В осуществлении согласно фиг.3а значения сопротивления изолирующих накладок 7 можно изменять с помощью различных изолирующих материалов, возможно путем изменения толщины или формы изолирующих накладок. Поэтому имеются хорошие возможности обеспечить многоуровневое кодирование, при котором, например, ячейка памяти 5 в том пересечении, где изолирующая накладка 7 не предусматривается, может представлять логический "0", и при этом прочие логические значения можно запоминать в ячейках памяти, в которых используются изолирующие накладки с изменяющейся геометрией или накладки, выполненные из материалов с разными значениями сопротивления. В чисто двоичном кодировании значения полного сопротивления всех изолирующих накладок будут, разумеется, одинаковыми. Поэтому их все можно выполнить как имеющие бесконечное значение сопротивления.

Особо предпочтительный способ получения двоичного кодирования в осуществлении согласно фиг.3а-с также будет обсуждаться ниже со ссылкой на фиг.5а и 5b. Если изолирующие накладки 7 имеют одинаковую толщину, то полупроводниковый слой 9 может быть, согласно фиг.3с, обеспечен между электродами 2, 4, в результате чего они будут выполнены заподлицо с поверхностью изолирующих накладок 7. Это может дать дополнительные преимущества по устранению и уменьшению паразитных токов и паразитных емкостей. В варианте осуществления согласно фиг. 3b паразитные емкости могут возникать и паразитные токи могут протекать в полупроводниковый сплошной материал 9. Но это явление можно устранить с помощью анизотропного полупроводника в качестве полупроводникового материала, направление электропроводности которого проходит между электродными структурами. Если полупроводниковый материал 9 выполнен заподлицо с изолирующей накладкой 7 согласно фиг.3с, что является целесообразным, когда изолирующие накладки имеют одинаковую толщину, то расстояние между электродными структурами можно сократить и сделать полупроводниковый слой в общем гораздо более тонким, в результате чего полупроводниковый материал не должен быть обязательно анизотропно проводящим, и при этом будут значительно уменьшены возможные объемные токи. Разумеется, при этом одновременно будет сохраняться диодный переход между полупроводниковым материалом и одной из электродных структур, и он понизит или устранит опасность появления паразитных токов от электродных структур.

Фиг. 4а и 4b соответственно изображают в горизонтальной проекции и сечении по линии А-А фиг.4а еще одно осуществление постоянной памяти согласно данному изобретению (полупроводниковый слой 9 на фиг.4а также не изображен). Электродные структуры, как и ранее, осаждают на соответствующих нижней и верхней подложках 1, 3, но изолирующий слой 6 в данном случае осаждают на электроды 2, 4 и между электродными структурами, и на одной из них по существу в качестве слоя по всему полю пластины, но с удаленными частями 8 в заданных пересечениях в целях формирования в них ячеек памяти 5, которые запоминают другие логические значения. Полупроводниковый материал 9, который теперь осаждают сверху изолирующего слоя 6, см. фиг.4b, будет контактировать только с обеими электродными структурами в удаленных частях 8 или "окнах" в изолирующем слое 6, в результате чего ячейки памяти 5 в этих удаленных частях, например, могут запоминать двоичное логическое значение "0", при этом ячейки памяти 5, в которых одна из электродных структур покрыта изолирующим слоем 6, запоминают двоичную логику "1". Аналогично осуществлению согласно фиг. 3а полупроводниковый материал 9 могут обеспечить таким образом, что он выполнен заподлицо с изолирующим слоем 6, т.е. он будет расположен только в удаленных частях 8 или окнах с указанными выше вытекающими преимуществами согласно описанию в соответствии с фиг.4с, где полупроводниковый материал изображен в виде "накладки" 10 на электроде 2.

Этап изготовления для осуществления в соответствии с фиг.4а-с можно вкратце резюмировать как состоящий из операции осаждения х-электродов на подложке 1, нанесения по существу по всему полю пластины изолирующего слоя 6, кодированного посредством удаленных частей 8 или окон, и нанесения на нем полупроводникового слоя 9 по всему полю пластины, причем у-электроды осаждают сверху подложки 3, после чего верхние подложки 1, 3 с осажденными электродами 2, 4, изолирующим слоем 6 и полупроводниковым слоем 9 соединяют в трехслойную структуру. Преимущество осуществления согласно фиг.4а и 4b заключается в том, что нет необходимости в том, чтобы полупроводник был анизотропным полупроводником, причем одновременно по существу полностью устраняются токи утечки и паразитные токи вне пересечений между электродами. Помимо этого уменьшают паразитные токи, проходящие через диодные переходы, так как ток будет протекать только там, где расположено окно в изолирующем слое. Ограничение по использованию двоичного кодирования делает возможным увеличение плотности размещения информации в запоминающем устройстве за счет уменьшения горизонтального расстояния между электродами в каждой электродной структуре, в результате чего повышается плотность размещения информации в ячейках памяти. Обычно при двоичном кодировании основа паразитного тока разделяется пополам на одну половину с нулями и одну половину с единицами, и это даст возможность удвоить число ячеек памяти или пересечений в электродной матрице при сохранении того же основного отношения сигнал/шум при адресации (считывании). Также в осуществлении согласно фиг.4а-с можно запоминать логические значения на основе многоуровневого кода, и это подробнее описывается ниже со ссылкой на фиг.6а и 6b.

Фиг.5а и 5b изображают в горизонтальной проекции и сечении ячейку памяти осуществления постоянной памяти согласно фиг.3а и 3с. Изолирующая накладка 7, которая кодирует ячейку памяти 5, здесь реализована таким образом, что она изолирует только часть контактной площадки в каждой ячейке памяти, в противоположность осуществлению согласно фиг.3а, где, например, изолирующая накладка 7 изолирует всю контактную площадку 11. Как и ранее, полупроводниковый материал 9 обеспечивают между электродами 2, 4 сверху изолирующей накладки 7 и, как ранее, диодный переход формируют между одним из электродов 2, 4 в ячейке памяти 5 и полупроводниковым материалом 9. Диодный переход может, например, в осуществлении согласно фиг.3b быть идентичен контактной площадке 11, но если используются полупроводниковые слои 9, выполненные заподлицо с изолирующими перемычками 7, как в фиг.3с, то площадь диодного перехода, разумеется, будет уменьшена на ту часть, которая не покрыта изолирующей накладкой 7. Эффективное поперечное сечение проводника и объемное полное сопротивление в полупроводниковом материале, в тонких полупроводниковых слоях или анизотропных полупроводниковых слоях будут зависеть от эффективной контактной площадки, которая на фиг.5а, 5b ограничена той частью электрода 2, 4, которая не покрыта изолирующей накладкой 7. Эта эффективная контактная площадка, которая может отличаться от площади диодного перехода, определяет активную часть полупроводника между электродами 2, 4. С помощью изолирующих накладок разного размера для кодирования ячеек памяти можно таким образом запоминать данные в многозначном коде.

Кодирование ячеек памяти 5 в осуществлении фиг.4а-4с происходит в соответствии с обратной аналогией способа согласно фиг.5а и 5b, т.к. в данном случае, согласно фиг. 5а, он является продолжением удаленных частей 7 или окон в изолирующем слое 6, который определяет эффективную контактную площадку в ячейке памяти 5; и если применяется вариант фиг.4с, то он также определяет ту часть контактной площадки, которую занимает диодный переход. Поэтому полупроводниковый материал 10, который обеспечивают на х-электроде 2, например, в ячейке памяти 5, имеет существенно пониженное объемное полное сопротивление в соответствии с сокращением эффективной контактной площадки; и посредством изменения таким образом размера окна 8 в изолирующем слое 6 и тем самым путем изменения эффективной контактной площадки данные можно запоминать в ячейках памяти с помощью многозначного кода.

Следует отметить, что кодирование данных с помощью многозначного кода предъявляет повышенные требования к различительной способности при считывании значения полного сопротивления в ячейке памяти; и если имеется опасность объемных или паразитных токов, маскирующих сигнал значения полного сопротивления, то тогда либо можно увеличить взаимное расстояние между электродами 2, 4 в каждой электродной структуре и таким образом увеличить ячейки памяти 5, либо можно применить многозначный код согласно вариантам осуществления, изображаемым соответственно на фиг.3с и фиг.4с, что даст удобную возможность разместить ячейки памяти с большей плотностью и с сохранением различительной способности, необходимой для обеспечения считывания данных, запомненных, например, в двоичном коде, т.е. с двумя уровнями между уровнем кода, созданным соответственно полным маскированием контактной площадки в ячейке памяти и полным экспонированием контактной площадки в ячейке памяти. Но предполагается, что будет возможно увеличить число уровней в коде, например, с помощью трех- или четырехразрядного кодирования. Последнее представлено шестнадцатью уровнями, и поэтому реализация будет вопросом габаритов и обеспечиваемого шага, если изготовление ячеек памяти происходит с применением обычных микрофотолитографических способов.

Может быть целесообразным формирование полупроводникового материала из нескольких полупроводников, например, в виде слоев согласно известному уровню техники в целях получения особых типов диодов также согласно известному уровню техники или в целях изменения характеристик полного сопротивления. В этих же целях полупроводниковый материал можно скомбинировать с электропроводным материалом или добавить его в электропроводный материал.

Целесообразно обеспечить одну или более постоянных памятей ПЗУ в соответствии с данным изобретением на полупроводниковой подложке 1, выполненной, например, из кремния. В этой подложке либо интегрально с ней согласно соответствующей полупроводниковой технологии можно обеспечить задающую и управляющую схемы 13 для постоянной памяти. Осуществление с четырьмя постоянными памятями ПЗУ, обеспеченными, например, на кремниевой подложке 1 с интегрированными задающей и управляющей схемами 13, изображено на фиг.7. Вместо обеспечения постоянных памятей в плоскостной конфигурации их также можно выполнить в виде стека вертикальных слоев согласно изображению на фиг.8. В этом случае также используют полупроводниковую подложку 1 из, например, кремния с интегрированными задающей и управляющей схемами 13. По боковым краям стекового запоминающего устройства этого типа могут обеспечивать адресующие и задающие шины 14 и для соединения электродов в соответствующей электродной структуре, т. е. электродной матрице, с задающей и управляющей схемами в кремниевых подложках согласно фиг.7, где изображено осуществление со стековыми постоянными памятями ПЗУ 151...15n, которые взаимно изолированы изолирующими слоями 161...l6n, выполненными, например, из керамики.

Постоянные памяти и постоянные запоминающие устройства согласно данному изобретению могут быть целесообразно реализованы в формате карты, совместимом со стандартными интерфейсами, обычно используемыми для персональных компьютеров. На практике постоянная память, реализуемая в постоянном запоминающем устройстве, может быть выполнена согласно известной тонкопленочной технологии, и постоянное запоминающее устройство будет интегрировано с кремниевой подложкой как гибридное устройство. На практике выявлено, что постоянные памяти согласно данному изобретению могут быть выполнены с толщиной электродных структур и ячеек памяти в большей мере в несколько микрон и, реально, по меньшей мере, с двумя ячейками памяти на квадратный микрон с использованием технологий из известного уровня техники. Постоянная память с одним слоем памяти и площадью 1 см2, таким образом, запомнит 25 Мбайт с двоичным кодированием. С помощью двух- или четырехразрядного кодирования, что более реально, плотность размещения информации можно, разумеется, повысить. Предполагается, что будет также реальным снижение размера ячеек памяти в еще большей степени с получением учетверенной плотности размещения информации. Поэтому будет возможным запоминание более сотни Мбайтов, но не менее 1 Гбайта в каждой постояннной памяти, и плотность размещения информации, разумеется, будет повышена пропорционально числу стековых слоев в постоянном запоминающем устройстве, объемно конфигурированном.

При выполнении со стандартными интерфейсами карт, используемыми в персональных компьютерах или в декодерных устройствах для оборудования воспроизведения аудио- и видеоматериала, постоянную память согласно данному изобретению можно будет применять в качестве носителя исходного материала, который обычно хранят на таких носителях, как CD-ROM.

Запись в постоянную память согласно данному изобретению, т.е. ввод и кодирование данных, осуществляют во время процесса изготовления и интегрируют ее с процессом изготовления. Постоянную память предпочтительно изготавливают с помощью хорошо известной тонкопленочной технологии и фотолитографическими способами. В основном все материалы можно обеспечить в слоях по всему полю пластины, а электродные структуры, накладки и удаленные части (окна) можно сформировать с помощью фотошаблонов и травлением. Затем производят "запись" данных путем "кодирования" фотошаблонов для накладок или окон с позиционированием и заданием размеров накладок, или окон маски согласно определенному протоколу, в результате чего каждая ячейка памяти правильно кодируется. Процессы такого рода нетрудно осуществить для изготовления крупных партий постоянных памятей с одинаковой исходной информацией, например с программным материалом для музыки или фильмов.

Изобретение относится к электрически адресуемой энергонезависимой постоянной памяти. Техническим результатом является обеспечение возможности многоуровнего кодирования заданных ячеек памяти или адресов ячеек памяти и возможность создания объемного запоминающего устройства. Электрически адресуемая энергонезависимая постоянная память содержит совокупность ячеек памяти, пассивную матрицу, которая содержит параллельные электроды, вертикальные и горизонтальные шины, полупроводниковый материал, изолирующий материал. Постоянная память содержит одну или более электрически адресуемых энергонезависимых постоянных памятей, задающую и управляющую схемы. 3 с. и 17 з. п.ф-лы, 8 ил.

| US 5272370 А, 21.12.1993 | |||

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| US 5170227 A, 08.12.1992 | |||

| US 5375085 A, 20.12.1994 | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| US 5464989 A, 07.09.1995 | |||

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1012704A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

Авторы

Даты

2003-09-20—Публикация

1998-08-28—Подача