Изобретение относится к микро-наноэлектронике и может быть использовано, в частности, при создании запоминающих устройств, двухмерных управляющих матриц для жидкокристаллических дисплеев, скоростных сканеров, сенсоров, линий задержки и т.д.

Известны аналоги, т.е. динамические последовательные функциональные устройства (ДПФУ), способные последовательно перемещать информационный заряд по цепочке из составляющих их элементов пиксел [1-3], например ДПФУ устройства, состоящие из последовательно включенных биполярных [1, 3] (см. фиг.1) или МОП-транзисторов [2, 3] (см. фиг.2), которые в литературе получили название «пожарные цепочки». Широкое применение в приемниках оптического изображения нашли ДПФУ на основе последовательно соединенных МОП-структур, получивших название «приборы с зарядовой связью» (ПЗС) [3] (см. фиг.3).

Однако перечисленные ДПФУ устройства обладают серьезным недостатком, заключающимся в том, что они не способны усиливать переносимый информационный заряд, что в конечном итоге приводит к его ослаблению или полному затуханию. Кроме этого пикселы этих устройств ДПФУ не способны управлять технологически совместимыми с ними другими электронными приборами - транзисторами, резисторами, светодиодами и т.д.

Вторым недостатком перечисленных ДПФУ является необходимость тактирования цепочки последовательно соединенных пиксел для обеспечения перемещения информационного заряда от пиксела к пикселу, что требует использование двух - трех тактовых шин, что значительно усложняет схему и конструкцию ДПФУ устройства.

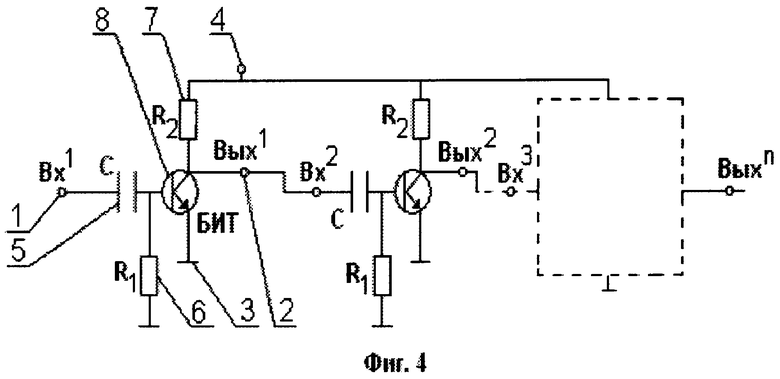

Этих недостатков частично лишено наиболее близкое по технологической сущности ДПФУ, описанное в патенте России [4] и заявке РСТ на патент [5], взятое за прототип. Данное ДПФУ (см. фиг.4) содержит цепочку последовательно соединенных пиксел, включающих входную и выходную шины (клеммы), общую шину и шину питания, при этом выходная шина (клемма) каждого пиксела, кроме последней, соединена с входной шиной (клеммой) последующего за ним пиксела. Каждый пиксел цепочки содержит биполярный транзистор, причем его коллектор подключен к выходной шине и через резистор к шине питания, эмиттер подключен к общей шине, а база подключена через другой резистор к общей шине и через конденсатор к входной шине, причем время хранения информации определяется временем рекомбинации неосновных носителей заряда, при котором

где tнас - время насыщения, τ0 - время жизни неосновных носителей, Iк и Iб - токи коллектора и базы соответственно, h21э - коэффициент усиления тока базы.

Данное устройство ДПФУ также не лишено недостатков, которые заключаются в невысоком быстродействии из-за использования режима «глубокого» насыщения биполярного транзистора, относительной сложности технологии изготовления биполярных транзисторных структур, а также относительно больших их размеров, что не позволяет достичь максимального уровня интеграции ДПФУ.

Техническим эффектом изобретения является повышение быстродействия, технологичности и интеграции ДПФУ.

Указанные эффекты достигаются тем, что каждый пиксел цепочки содержит не биполярный МОП-транзистор, конденсатор, первое сопротивление, второе сопротивление и третье сопротивление, причем затвор МОП-транзистора подключен через конденсатор к входной шине (клемме) и через первое - входное сопротивление к общей шине, его сток подключен через второе нагрузочное сопротивление к шине питания, его подзатворная область через третье дополнительное сопротивление подключена к общей шине, а исток также подключен к общей шине.

При этом время хранения информационного заряда, определяемое временем задержки выключения МОП-транзистора (tзад), которое должно превышать постоянную времени перезарядки (τп) конденсатора (С) через (первое) входное сопротивление - R1

tзад>C·R1,

а величина произведения емкости конденсатора С на величину входного напряжения Uвx должна превышать величину произведения емкости затвора - подзатворную область (Сзп), умноженную на величину порогового напряжения МОП-транзистора (UT)

Uвx·C>UТ·Сзп

С целью обеспечения синхронизации (что важно для некоторых применений) первые - входные сопротивления пиксел ДПФУ могут быть подключены к дополнительной шине синхронизации.

С целью обеспечения большей технологичности, конденсатор и (первое) входное и/или (третье) дополнительное сопротивления пиксел могут быть выполнены на основе диодов, причем анод диода, заменяющего конденсатор, подключается к затвору МОП-транзистора, а катод - к входной шине (клемме), анод диода заменяющего (первое) входное сопротивление подключен к общей шине, а катод - к затвору МОП-транзистора, анод диода заменяющего (третье) дополнительное сопротивление подключен к подзатворной области, а его катод - к общей шине.

С целью обеспечения большей надежности работы, подзатворная область МОП-транзистора подключена к базе дополнительного биполярного транзистора, коллектор которого подключен к области стока, а эмиттер - к области истока МОП-транзистора.

С целью упрощения конструкции схемы ДПФУ, подзатворная область может быть ни к чему не подсоединена, т.е. быть «плавающей», т.е. в этом случае (третье) дополнительное сопротивление равно бесконечности.

Описание электрических схем

На фиг.1 показана электрическая схема ДПФУ типа «пожарной» цепочки, выбранного в качестве аналога изобретения, содержащая пикселы, выходные шины 2 которых последовательно соединены с входными шинами 1 последующих пиксел, при этом электроды биполярных транзисторов 3 соединены соответственно: эмиттеры к входным шинам 1, коллекторы к выходным шинам 2, базы через соответствующие конденсаторы 4 подсоединены к коллекторам и нечетной 5 и четной 6 шинам соответственно.

На фиг.2 показана аналогичная электрическая схема, выбранная в качестве аналога ДПФУ типа «пожарной» цепочки на МОП-транзисторах. Обозначения в схеме идентичны.

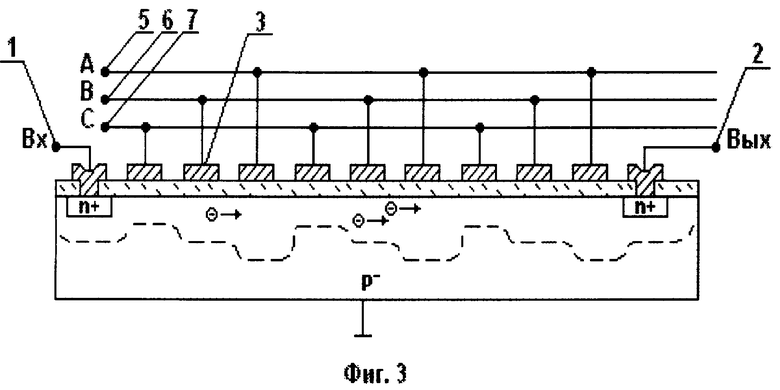

На фиг.3 показана конструкция еще одного аналога устройства, получившего название «ПЗС», прибора, содержащего последовательно расположенные МОП-структуры 3.

В ПЗС приборах также имеются тактовые шины 5, 6, 7, однако входная шина-клемма имеется только на первом пикселе, а выходная - на последнем.

На фиг.4 показана электрическая схема ДПФУ, взятого за прототип. Она содержит последовательно включенные пикселы, каждый из которых содержит входную 1 и выходную 2 шину (клемму), общую шину 3, шину питания 4, конденсатор 5, первый резистор R1 6, второй резистор R2 7, биполярный транзистор 8.

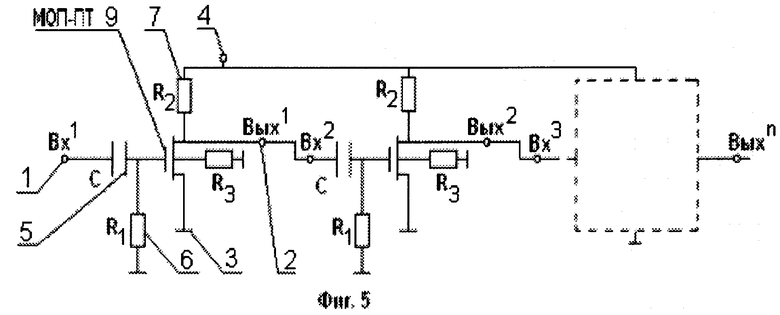

На фиг.5 показана электрическая схема ДПФУ, соответствующая первому пункту формулы изобретения. Электрическая схема содержит цепочку последовательно соединенных пиксел, каждый из которых имеет входную 1 и выходную 2 шины (клеммы), общую шину 3 и шину питания 4, конденсатор 5, (первое) входное сопротивление 6, (второе) нагрузочное сопротивление 7, (третье) дополнительное сопротивление 8, МОП-транзистор 9. При этом в схеме затвор МОП-транзистора 9 через конденсатор 5 подсоединен к входной клемме 1 и через (первое) входное сопротивление R1 6 подсоединен к общей шине 3, его сток соединен с выходной шиной 2 и через нагрузочное сопротивление R2 7 подключен к шине питания 4, подзатворная область МОП-транзистора 9 через (третье) дополнительное сопротивление 8 подсоединена к общей шине 3.

На фиг.6 показана электрическая схема ДПФУ, соответствующая п.2 формулы изобретения. Электрическая схема содержит цепочку последовательно включенных пиксел, каждый из которых имеет входную 1 и выходную 2 шины (клеммы), общую шину 3 и шину питания 4, конденсатор 5, первое сопротивление 6, второе сопротивление 7, третье сопротивление 8, МОП-транзистор 9, затвор которого через первое сопротивление R1 6 подсоединен к дополнительной тактовой шине 10, его сток соединен с выходной шиной 2 и через сопротивление R2 7 подсоединен к шине питания 4, подзатворная область МОП-транзистора 9 через третье сопротивление 8 подсоединена к общей шине 3.

На фиг.7 показана электрическая схема ДПФУ, соответствующая п.3 формулы изобретения. Электрическая схема содержит цепочку последовательно включенных пиксел, каждый из которых имеет входную 1 и выходную 2 шины (клеммы), общую шину 3 и шину питания 4, конденсатор 5, первое сопротивление 6, второе сопротивление 7, третье сопротивление 8, МОП-транзистор 9, при этом в схеме затвор МОП-транзистора 9 соединен с анодом диода 11, катод которого подключен к входной шине 1, и с анодом диода 12, катод которого соединен с общей шиной 3, его сток соединен с выходной шиной 2 и через сопротивление R2 7 подключен к шине питания 4, подзатворная область МОП-транзистора 9 через третье сопротивление подключена к общей шине.

На фиг.8 показана электрическая схема ДПФУ, соответствующая п.4 формулы изобретения. Электрическая схема содержит цепочку последовательно включенных пиксел, каждый из которых имеет входную 1 и выходную 2 шины (клеммы), общую шину 3 и шину питания 4, конденсатор 5, первое сопротивление 6, второе сопротивление 7 третье сопротивление 8, МОП-транзистор 9 и биполярный транзистор 13. При этом в схеме затвор МОП-транзистора 9 подключен через конденсатор 5 к входной шине 1 и через первое сопротивление - к общей шине 3, его исток соединен с общей шиной 3, его сток соединен с выходной шиной 2 и через сопротивление R2 7 подключен к шине питания 4, подзатворная область МОП-транзистора 9, подсоединена к базе биполярного транзистора 13, коллектор которого подсоединен к выходной шине 2, а эмиттер - к общей шине 3.

На фиг.9 показана электрическая схема ДПФУ, соответствующая пункту п.1 формулы изобретения. Электрическая схема содержит цепочку последовательно включенных пиксел, каждый из которых имеет входную 1 и выходную 2 шины (клеммы), общую шину 3 и шину питания 4, конденсатор 5, первое сопротивление 6, второе сопротивление 7, третье сопротивление 8, МОП-транзистор 9, затвор которого через конденсатор подключен к входной шине 1 и через первое сопротивление подключен к общей шине 3 и входной шине 1, и его сток соединен с выходной шиной 2 и через сопротивление R2 7 подключен к шине питания 4, подзатворная область МОП-транзистора 9 ни к чему не подсоединена (т.е. имеет «плавающий» потенциал).

ДПФУ устройство (см. фиг.5) работает следующим образом.

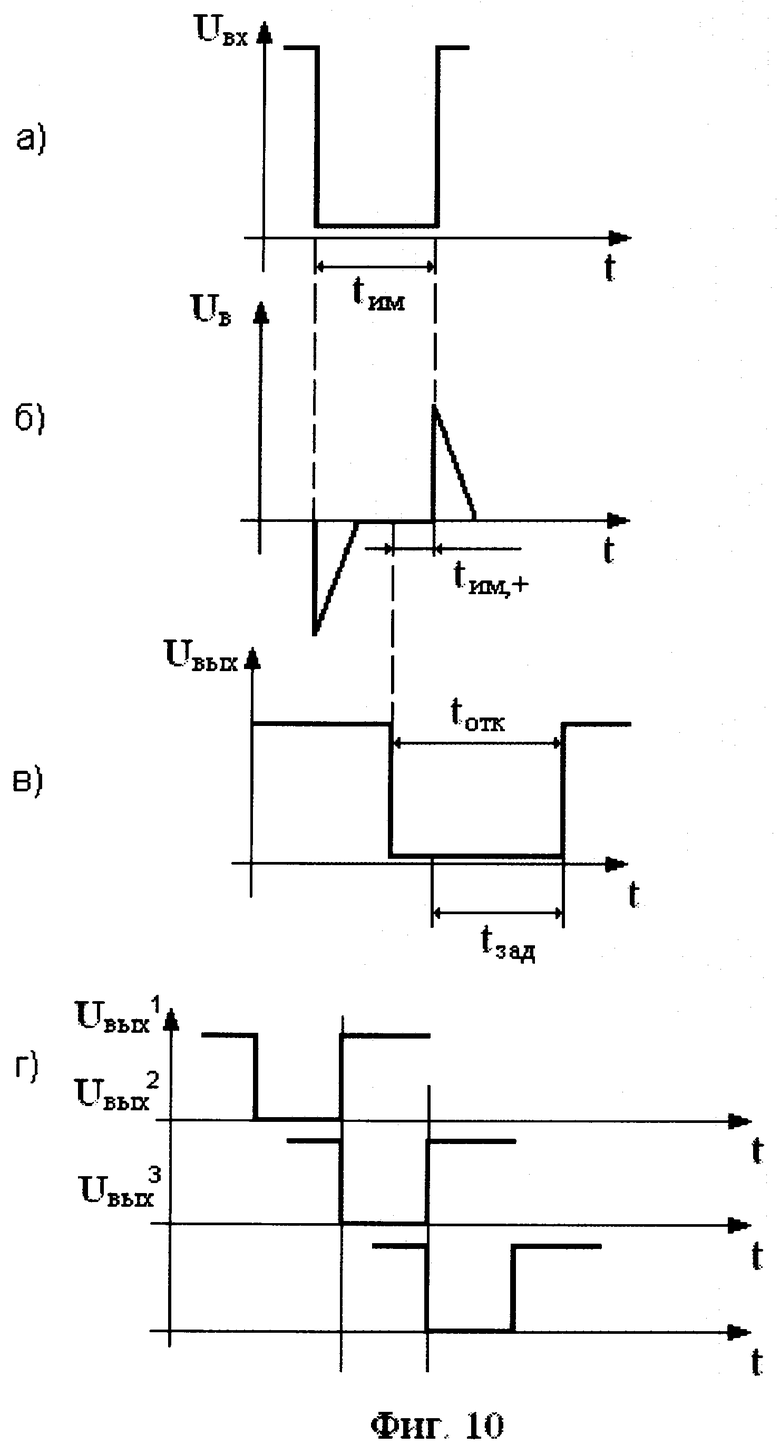

При поступлении «длинного» отрицательного входного импульса (Uвx) на входную клемму 1, как это показано на фиг.10а, происходит его дифференциация за счет R-C цепочки, образованной конденсатором С 5 и сопротивлением R1 6. В результате на затворе МОП-транзистора 9 образуются два «коротких» импульса: отрицательный и положительный соответственно (см. фиг.10б). При этом положительный импульс открывает МОП-транзистор 9, находящийся до этого момента в закрытом состоянии. Однако время открытого состояния транзистора (tотк) может значительно превышать время действия положительного «короткого» импульса (tимп,+) и время действия самого входного импульса (tимп), т.е. в реальных транзисторах всегда имеет место задержка времени выключения транзистора (tзад) по отношению ко времени окончания действия входного сигнала (см фиг.10в). Это явление в МОП-транзисторах обычно крайне нежелательно и обусловлено известными физическими эффектами, получившими в специальной литературе названия: - «kink-эффект», «bodi-эффект», эффект паразитного n-p-n транзистора. В предлагаемой электрической схеме ДПФУ эти паразитные эффекты используются для запоминания факта подачи импульса на вход пиксела на величину времени - (tзад). В этом случае ДПФУ используется как устройство динамической оперативной памяти, (tзад) является по существу временем хранения информационного заряда в пикселе - ячейке памяти.

Очевидно, что поступление выходного сигнала (Uвых) со стока МОП-транзистора первого пиксела на вход следующего пиксела ДПФУ, для которого он будет являться входным сигналом, приведет к аналогичному процессу. Таким образом, импульс, поданный на первую ячейку памяти, будет последовательно распространяться по всей цепочке пиксел за счет последовательного открывания МОП-транзисторов пиксел (см. фиг.10г). Поступление на вход ДПФУ нескольких разделенных по времени входных импульсов приводит к их последовательному перемещению информационных сигналов - зарядов по цепочке пиксел, аналогично «бегущей строке» световой рекламы.

Следует отметить, что устройство ДПФУ, так же как и ПЗС прибор, является функциональным устройством, поскольку технический результат достигается за счет одновременного использования оригинальной схемы и специфических «паразитных» эффектов, присущих МОП структуре, которые не могут быть адекватно описаны средствами схемотехники.

Важно отметить, что работоспособность цепочки пиксел ДПФУ, возможна только при выполнении указанных выше соотношений

tзад>C·Rl,

которое определяет условие приемлемой дифференциации входного импульса и условия

Uвх·С>VT·Cn,

определяющего необходимое условие для достаточного открывания МОП-транзистора. При этом обычно tзад коррелирует с величиной времени жизни неосновных носителей заряда в подзатворной области.

Работа ДПФУ в асинхронном режиме смоделирована с помощью известной компьютерной программы «SPACE». B качестве примера на фиг.11 показаны временные зависимости выходных напряжений для цепочки из 8 пиксел, на вход которой подан одиночный импульс.

Для некоторых применений ДПФУ важна его синхронная работа с другими электронными устройствами (например, в схемах развертки плоских телевизионных изображений), при этом для обеспечения режима синхронизации достаточно подачи синхронизирующих импульсов на всего одну тактовую шину 10, как это показано на фиг.6. Смоделированная с помощью SPACE программы временная диаграмма работы ДПФУ в асинхронном режиме показана на фиг.12.

Работа цепочки ДПФУ возможна в случае замены конденсатора С 5 и/или резистора R1 6 на диоды 11 и 12 соответственно (см. фиг.7). В этом случае барьерная емкость диода 11 выполняет функции конденсатора, а наличие обратного тока диода 12 обеспечивает наличие необходимого нулевого потенциала на затворе МОП-транзистора. Такая замена конденсатора и резисторов R1 и/или R3 обеспечивает большую технологичность изготовления ДПФУ и его меньшие размеры, т.е. большую интеграцию. Следует отметить, что в качестве резистора R2 7 может быть использован любой элемент - двухполюсник (светодиод, индуктивность и т.д.).

В случае использования «длинноканальных» МОП-транзисторов, в которых вышеупомянутые «паразитные» эффекты проявляются слабее, возможно использование комбинации в пикселы МОП и биполярных транзисторов, как это показано на фиг.8. В этом случае значительно понижается зависимость работоспособности ДПФУ от величины и разброса номиналов емкости и сопротивлений - резисторов схемы, а также от электрофизических параметров МОП и биполярных транзисторов. Это обстоятельство обеспечивает повышенную надежность работы схемы.

Схема ДПФУ, использующая МОП-транзисторы с «плавающей» подзатворной областью (см. фиг.8), отличается от предыдущих схем меньшим быстродействием, поскольку в ней наиболее сильно выражены «паразитные» эффекты. Однако она имеет наилучшую интеграцию, поскольку в ней отсутствует сопротивление в подзатворной области (R3) и контакт к ней. Такое ДПФУ может быть легко реализовано на основе технологии «кремний на изоляторе» - КНИ (см. фиг.14). Такая схема может быть использована в случае, когда быстродействие не является определяющим параметром.

Практическое использование

Опытные устройства (макеты) ДПФУ были изготовлены на базе стандартных технологий К-МОП СБИС на монокремниевой и на диэлектрической подложках. Топологии и конструкции таких устройств при минимальной топологической норме LT~1,5 мкм показаны соответственно на фиг.13 и 14. Номиналы резисторов, изготовленных на поликремнии n--типа, составляли соответственно R1=10 МОм, R2=100 кОм, величина емкости конденсатора С=10-13 Ф, длина и ширина затвора МОП-транзистора соответственно составляла Lк=1,5 мкм, Wк=10 мкм, емкость затворной системы Сзп=10-14 Ф, емкости стока - истока Сс=Си~5·10-14 Ф. Размер меза-структуры транзистора (длина и ширина) составляли соответственно Lм=20 мкм и Wм~10 мкм, толщина подзатворного оксида δ~300 Å. Напряжение порога (UT) МОП-транзисторов составляло UT~1,0 В, напряжение питания схемы +Uc=5 В. Изготовленный макет устройства ДПФУ показал его устойчивую работоспособность при широком изменении параметров элементов схемы в диапазоне ±200% и напряжения питания от +Uc=2,5 В до 10 В.

В заключение следует также отметить важные преимущества ДПФУ, которые состоят в следующем:

- исключительно низкое потребление энергии при его использовании в качестве сканирующего устройства, поскольку в этом случае энергопотребление происходит только в одном пикселе (см. фиг.15);

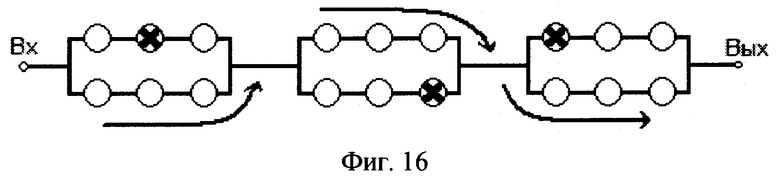

- исключительно высокая надежность работы, высокий процент выхода годных (и связанная с этим низкая стоимость) реализуются в случае организации работы ДПФУ по принципу «двойной спирали» (см. фиг.16), поскольку в этом случае отказ одного или многих пиксел не приводит к отказу всего устройства;

- для монтажа кристалла (чипа) ДПФУ требуется всего 2-3-выводной корпус.

Источники информации

1. Sangster F.L. J The Bucket Brigade Delay Line. A Shift Register for Analogue Signals, Philips Tech. Review, 31, 97-110 (1970).

2. Krause G. Analog Speicherketle: Fine Neuartige Schaltung Jum Speichern and Verzoegern von Signalen. Electronics Lett, 3, 544-546 (1967).

3. Carlo H. Sevuin and Michael F. Tompsett Charge Transfer Devices Academic Press, Inc. New York, San Francisco, London 1975 pp.10-15.

К.Секен, М.Томпсет. Приборы с переносом заряда. Из-во Мир. 1978 г. стр.12-14.

4. Мурашев В.Н. «Динамическая ячейка памяти». Патент на изобретение России №2147772, приоритет от 11.06.1997 г.

5. Мурашев В.Н., Саито Т. «Последовательное динамическое функциональное устройство». Заявка на патент №PCT/RU 02/00457 от 21 июля 2003 г.

6. Silicon-on-insulator Techology: Materials to VLSI, 2-nd Edition by Jean-Pierre Colinge, Universite catholigye de Louvajn, Belgium. Kluwer Academic Publishers Boston/Dordrecht/London TK7871 35 С.758, 1997. 651.38.152-dc21 97-35777cip.PP-126, 134, 163.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| ФУНКЦИОНАЛЬНО-ИНТЕГРИРОВАННАЯ ЯЧЕЙКА ФОТОЧУВСТВИТЕЛЬНОЙ МАТРИЦЫ | 2012 |

|

RU2517917C2 |

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1997 |

|

RU2147772C1 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" | 2011 |

|

RU2481701C2 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ-НЕ" | 2011 |

|

RU2468510C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

Изобретение относится к области микро-наноэлектроники и может быть использовано при создании динамических запоминающих устройств, двухмерных управляющих матриц для жидкокристаллических дисплеев, скоростных и высокоточных сканеров, двухмерных сенсоров, линий задержки и т.д. Изобретение позволяет повысить быстродействие функционального устройства, а также упростить технологию его изготовления, уменьшить его размеры и повысить интеграцию. В устройстве применяется цепочка последовательно соединенных активных функционально-интегрированных ячеек, которые способны управлять технологически совместимыми с ними электрическими приборами. Каждая ячейка цепочки представляет собой простейшую электрическую схему, состоящую из МОП-транзистора, резисторов и конденсатора. При этом используется задержка времени выключения МОП-транзистора по отношению ко времени окончания действия выходного сигнала. 16 ил.

Динамическое последовательное функциональное устройство, содержащее цепочку последовательно соединенных ячеек, включающих общую шину, шину питания, вход и выход, причем выход каждой ячейки соединен с входом последующей за ней ячейки, каждая ячейка содержит транзистор, конденсатор, первое входное сопротивление, второе нагрузочное сопротивление, отличающееся тем, что транзистор ячейки является МОП-транзистором, при этом затвор МОП-транзистора подключен через конденсатор ко входу ячейки и через первое, входное сопротивление к обшей шине, его сток подключен к выходу ячейки и через второе нагрузочное сопротивление к шине питания, его подзатворная область через третье дополнительное сопротивление подключена к общей шине, а исток также подключен к общей шине; при этом время задержки включения МОП-транзистора (tзад) превышает постоянную времени перезарядки конденсатора (С) через первое входное сопротивление (R1), т.е.

tзад>С·R1,

а величина произведения величины емкости конденсатора (С), умноженная на величину входного напряжения (Uвх), превышает величину произведения величины емкости, образуемой затвором и подложкой МОП транзистора (Сзп), на величину порогового напряжения МОП транзистора (UT)

Uвх·С>UT·Сзп.

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1997 |

|

RU2147772C1 |

| УСТРОЙСТВО для КОНТРОЛЯ и РЕГИСТРАЦИИ СТАБИЛЬНОСТИ ЗОН РАДИОМАЯКА | 0 |

|

SU186533A1 |

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

Авторы

Даты

2010-06-20—Публикация

2005-06-06—Подача