Изобретение относится к радиотехнике и радиоэлектронике, а именно к устройствам стабилизации режима работы дифференциальных усилителей как в гибридном, гибридно-интегральном, так и в интегральном исполнении.

Предшествующий уровень техники

Известен широкополосный усилитель высокой частоты [1], в котором использованы цепи отрицательной обратной связи для обеспечения в широких пределах глубины регулировки коэффициента усиления по напряжению и динамического диапазона входных сигналов.

Наиболее близким по технической сущности и решению поставленной технической задачи является устройство поддержания режима работы по постоянному току усилителя, являющегося первым блоком устройства и имеющего выводы, соединенные с общей шиной и питанием, первый и второй входы, первый и второй выходы, включающее блоки, соединенные выводами с общей шиной, содержащие резисторы, конденсатор, транзисторы [2] . Известное устройство состоит из первого блока - непосредственно из операционного усилителя, подсоединенного к общей шине и шине питания. Он имеет два входа, прямой (неинвертируемый) и инверсный (инвертируемый), и два выхода, один из которых соединен с блоками для поддержания режима работы по постоянному току упомянутого операционного усилителя, соединенными с общей шиной, питанием, усилителем и включающими резисторы, конденсатор, транзисторы.

Использование известного устройства [2] для стабилизации режима работы дифференциального усилителя в широком диапазоне изменения температуры среды не представляется возможным.

Раскрытие изобретения

В основу изобретения поставлена задача создания устройства поддержания режима работы по постоянному току дифференциального усилителя со значительным уменьшением зависимости усилителя от флуктуаций входного постоянного тока и обеспечением стабильности режима его работы при повышении стабилизации токов питания обеих плеч дифференциального каскада в расширенном диапазоне изменения температуры среды.

Поставленная техническая задача решается тем, что предложено устройство поддержания режима работы по постоянному току усилителя, являющегося первым блоком устройства и имеющего выводы, соединенные с общей шиной и питанием, первый и второй входы, первый и второй выходы, включающее блоки, соединенные выводами с общей шиной, содержащие резисторы, конденсатор, транзисторы, причем питание имеет выделенные шину питания положительной полярности и шину питания отрицательной полярности, устройство выполнено из четырех блоков, на первый вход первого блока при работе поступает входной импульсный сигнал, по выводу первого выхода первого блока при работе проходит выходной импульсный сигнал, второй выход первого блока соединен с входом второго блока, дополнительный третий выход первого блока соединен с выходом второго блока и со входом третьего блока, выход которого соединен со входом четвертого блока, выход которого соединен со вторым входом первого блока, второй блок соединен с шиной питания положительной полярности, четвертый блок соединен с шинами питания положительной и отрицательной полярностей, усилитель, первый блок, выбран дифференциальным, дифференциальный каскад которого выполнен из двух первого и второго транзисторов, управляемый вход первого транзистора является первым входом дифференциального усилителя, эмиттеры первого и второго транзисторов соединены через генератор стабилизированного тока с шиной питания отрицательной полярности, регулируемый вход второго транзистора является вторым входом первого блока - дифференциального усилителя, коллектор первого транзистора является первым выходом первого блока - дифференциального усилителя, коллекторы первого и второго транзисторов соединены, соответственно, с парами транзисторов, третьим и четвертым, пятым и шестым, образующими "зеркало тока", где коллекторы первого и второго транзисторов, соответственно, соединены с коллекторами третьего и пятого транзисторов, которые включены в диодном режиме, эмиттеры которых, соответственно, через первый и второй резисторы соединены с шиной питания положительной полярности, при этом коллектор и база третьего транзистора соединены с базой четвертого транзистора, коллектор которого соединен с общей шиной, а его эмиттер через третий, резистор соединен с шиной питания положительной полярности, коллектор и база пятого транзистора соединены с базой шестого транзистора, эмиттер которого через четвертый резистор соединен с шиной питания положительной полярности, кроме того, эмиттер четвертого транзистора является вторым выходом первого блока - дифференциального усилителя, а коллектор шестого транзистора является третьим выходом первого блока - дифференциального усилителя, второй выход дифференциального усилителя соединен с входом второго блока, включающем первый конденсатор, первый вывод которого является входом второго блока, а второй его вывод соединен с первым выводом пятого резистора, второй вывод которого соединен с шиной питания положительной полярности, второй вывод конденсатора также соединен с эмиттером седьмого транзистора, включенном в диодном режиме, коллектор и база которого соединены с первым выводом второй емкости, второй вывод которой соединен с шиной питания положительной полярности, также коллектор и база седьмого транзистора соединены с первым выводом шестого резистора, второй вывод которого соединен с общей шиной, а также коллектор и база седьмого транзистора соединены с первым выводом стабилизатора напряжения, второй вывод которого соединен с шиной питания положительной полярности, второй вывод первой емкости соединен с базой восьмого транзистора, эмиттер которого через седьмой резистор соединен с шиной питания положительной полярности, коллектор восьмого транзистора является выходом второго блока и соединен с третьим выходом первого блока - дифференциального усилителя и с входом третьего блока, выполненного из восьмого резистора и третьей емкости, соединенных параллельно, первые выводы которых соединены и являются входом и выходом третьего блока, а их вторые выводы соответственно соединены с общей шиной, выход третьего блока соединен с входом четвертого блока, выполненным на основе операционного усилителя с выходным эмиттерным повторителем, где при работе устройства сигнал поступает на инвертируемый вход операционного усилителя, неинвертируемый вход которого соединен с первым выводом стабилизатора опорного напряжения, второй вывод которого соединен с общей шиной, первый и второй выводы питания операционного усилителя, соответственно, соединены с шиной питания положительной полярности и с шиной питания отрицательной полярности, выход операционного усилителя соединен с базой девятого транзистора, эмиттер которого является выходом четвертого блока, соединенным со вторым регулируемым входом первого блока - дифференциального усилителя, а коллектор соединен с общей шиной, кроме того, шина питания отрицательной полярности соединена с первым выводом четвертой емкости, второй вывод которой соединен с общей шиной, а шина питания положительной полярности соединена с первым выводом пятой емкости, второй вывод которой соединен с общей шиной.

Существенным отличием предложенного устройства поддержания режима работы по постоянному току дифференциального усилителя является наличие созданных нами второго блока - блока фиксации уровня постоянного напряжения сигнала с дифференциального каскада, третьего блока - блока вычитания переменного импульсного сигнала и сложения постоянного сигнала, четвертого блока - блока сравнения и управления по режиму, что позволило осуществить поддержание стабильным режима работы дифференциального усилителя при усилении псевдослучайных импульсных сигналов в широком частотном и динамическом диапазонах.

Поставленная техническая задача решается также тем, что в предложенном устройстве во втором блоке коллектор и база седьмого транзистора соединены с первым выводом девятого резистора, второй вывод которого соединен с эмиттером десятого транзистора, коллектор которого соединен с первым выводом десятого резистора, второй вывод которого соединен с эмиттером восьмого транзистора, также коллектор и база седьмого транзистора соединены с первым выводом одиннадцатого резистора, второй вывод которого соединен с базой десятого транзистора и с первым выводом двенадцатого резистора, второй вывод которого соединен с шиной питания положительной полярности.

Это приводит к тому, что постоянный ток в цепи второго коллектора не меняется при изменении температуры среды.

Техническая реализация изобретения основана на известных базовых технологических процессах, которые к настоящему времени хорошо разработаны и широко применяются при изготовлении гибридных, гибридно-интегральных и интегральных схем.

Предложенное изобретение является новым, обладающим изобретательским уровнем и промышленно применимо. Предложенное устройство решает поставленную техническую задачу: значительное уменьшение зависимости усилителя от флуктуаций входного постоянного тока и обеспечение стабильности режима его работы при повышении стабилизации токов питания обеих плеч дифференциального каскада в расширенном диапазоне изменения температуры среды.

Краткое описание чертежей

Настоящее изобретение поясняется схемами, изображенными на фиг.1-3.

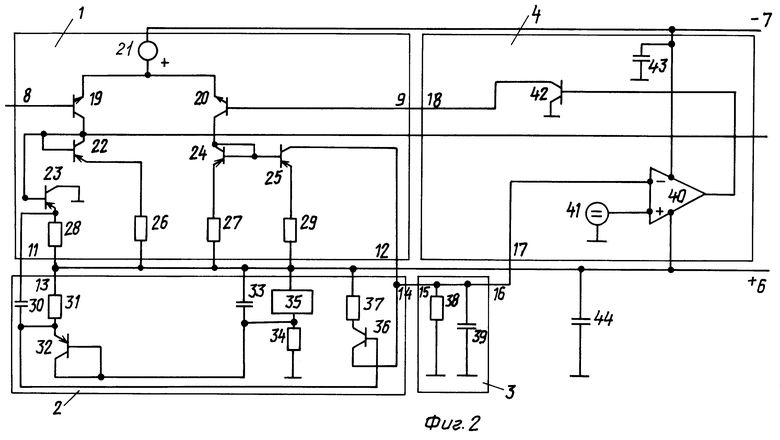

На фиг.1 изображена блок-схема предложенного устройства.

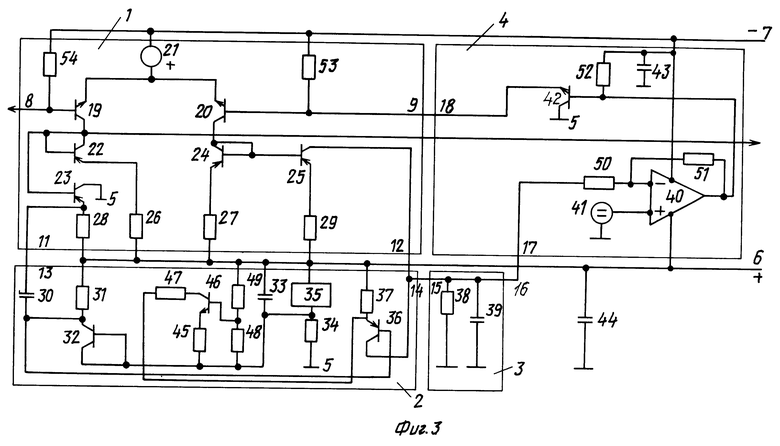

На фиг.2 изображена принципиальная схема устройства по примеру 1.

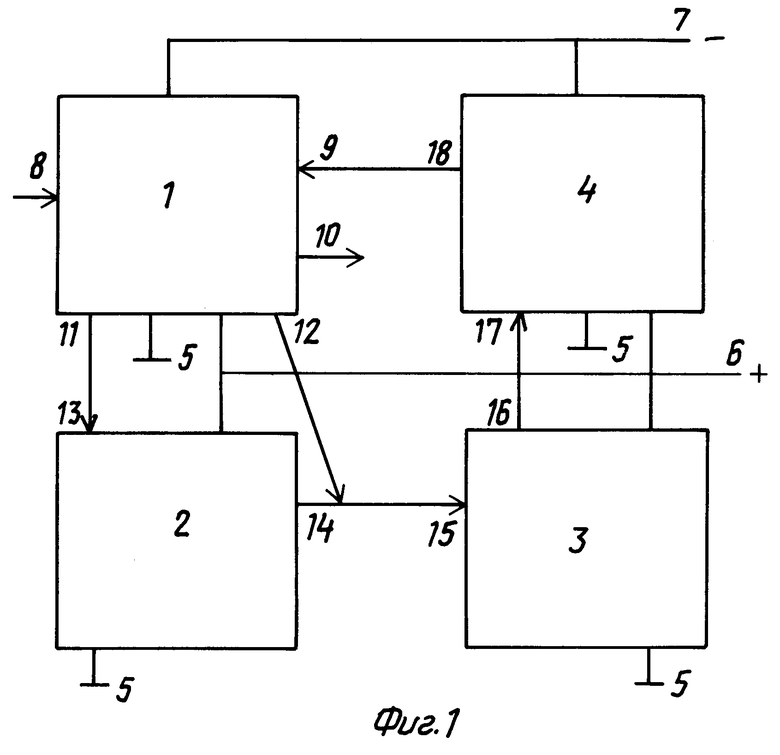

На фиг.3 изображена принципиальная схема устройства по примеру 2.

Варианты осуществления изобретения

Блок-схема и конструкция устройства поддержания режима работы по постоянному току усилителя изображены соответственно на фиг. 1 и 2. Блок-схема (см. фиг.1) состоит из первого блока - дифференциального усилителя 1 (далее - "ДУ") и других трех блоков устройства, а именно второго 2, названного блоком фиксации уровня постоянного напряжения сигнала с дифференциального каскада, третьего блока 3, названного блоком вычитания переменного импульсного сигнала и сложения постоянного сигнала, и четвертого блока 4, названного блоком сравнения и управления по режиму.

В предложенном устройстве имеются общая шина 5, шина питания положительной полярности 6, шина питания отрицательной полярности 7. ДУ 1 имеет первый вход 8, второй вход 9, первый выход 10, второй выход 11 и третий выход 12. Первый вход 8 является входом усилителя, а первый выход 10 является выходом усилителя. Второй выход 11 ДУ 1 соединен со входом 13 второго блока 2. Третий выход 12 ДУ 1 соединен с выходом 14 второго блока 2 и входом 15 третьего блока 3, выход 16 которого соединен с входом 17 четвертого блока 4. Выход 18 четвертого блока 4 соединен с входом 9 первого блока - ДУ 1.

Предложенная блок-схема позволяет обеспечить стабилизацию режима работы ДУ 1 при усилении псевдослучайных импульсных сигналов в широком частотном и динамическом диапазонах.

Первый пример конкретного исполнения

ДУ 1 выполнен на основе дифференциального каскада из двух, первого 19 и второго 20 транзисторов. Управляемый вход первого транзистора 19 является первым входом 8 ДУ 1. Эмиттеры первого 19 и второго 20 транзисторов соединены через генератор стабилизированного тока 21 с шиной питания отрицательной полярности 7. Регулируемый вход второго транзистора 20 является вторым входом 9 первого блока - ДУ 1 и соединен с выходом 18 четвертого блока 4. Коллектор первого транзистора 19 является первым выходом 10 первого блока - ДУ 1.

Коллекторы первого 19 и второго 20 транзисторов соединены соответственно с парами транзисторов, третьим 22 и четвертым 23, пятым 24 и шестым 25, образующими, так называемое "зеркало тока". Коллектор первого транзистора 19 соединен с коллектором третьего транзистора 22, который включен в диодном режиме. Коллектор второго транзистора 20 соединен с коллектором пятого транзистора 24, который включен в диодном режиме. Эмиттер третьего транзистора 22 через первый резистор 26 соединен с шиной питания положительной полярности 6. Эмиттер пятого транзистора 24 через второй резистор 27 соединен с шиной питания положительной полярности 6. Коллектор и база третьего транзистора 22 соединены с базой четвертого транзистора 23, коллектор которого соединен с общей шиной 5, а его эмиттер через третий резистор 28 соединен с шиной питания положительной полярности 6. Коллектор и база пятого транзистора 24 соединены с базой шестого транзистора 25, эмиттер которого через четвертый резистор 29 соединен с шиной питания положительной полярности 6.

Кроме того, эмиттер четвертого транзистора 23 является вторым выходом 11 первого блока - ДУ 1, а коллектор шестого транзистора 25 является третьим выходом 12 первого блока - ДУ 1.

Второй выход 11 ДУ 1 соединен с входом 13 второго блока 2, включающем первый конденсатор 30, первый вывод которого является входом 13, а второй его вывод соединен с первым выводом пятого резистора 31, второй вывод которого соединен с шиной питания положительной полярности 6. Второй вывод первого конденсатора 30 также соединен с эмиттером седьмого транзистора 32, включенном в диодном режиме. (Седьмой транзистор 32, включенный в диодном режиме, может быть заменен на диод 32.) Коллектор и база седьмого транзистора 32 соединены с первым выводом второй емкости 33, второй вывод которой соединен с шиной питания положительной полярности 6. Также коллектор и база седьмого транзистора 32 соединены с первым выводом шестого резистора 34, второй вывод которого соединен с общей шиной 5. Также коллектор и база седьмого транзистора 32 соединены с первым выводом стабилизатора напряжения 35, второй вывод которого соединен с шиной питания положительной полярности 6. Второй вывод первой емкости 30 соединен с базой восьмого транзистора 36, эмиттер которого через седьмой резистор 37 соединен с шиной питания положительной полярности 6. Коллектор восьмого транзистора 36 является выходом 14 второго блока и соединен с третьим выходом 12 ДУ 1 и с входом 15 третьего блока 3.

Третий блок 3 выполнен из восьмого резистора 38 и третьей емкости 39, соединенных параллельно, первые выводы которых соединены с входом 15 и выходом 16 третьего блока 3, а их вторые выводы соединены с общей шиной 5. Выход 16 третьего блока соединен с входом 17 четвертого блока 4.

Входом 17 четвертого блока 4 является инвертируемый вход операционного усилителя 40, неинвертируемый вход которого соединен с первым выводом стабилизатора опорного напряжения 41, второй вывод которого соединен с общей шиной 5. Первый и второй выводы питания операционного усилителя 40, соответственно, соединены с шиной питания положительной полярности 6 и с шиной питания отрицательной полярности 7. Выход операционного усилителя 40 соединен с базой девятого транзистора 42 - эмиттерного повторителя, эмиттер которого является выходом 18 четвертого блока 4, соединенным со вторым входом 9 ДУ 1. Коллектор девятого транзистора 42 соединен с общей шиной 5.

Кроме того, шина питания отрицательной полярности 7 соединена с первым выводом четвертой емкости 43, второй вывод которой соединен с общей шиной 5, а шина питания положительной полярности 6 соединена с первым выводом пятой емкости 44, второй вывод которой соединен с общей шиной 5.

Предложенное устройство работает следующим образом.

Входной импульсный сигнал подается на первый вход 8 ДУ 1 дифференциального каскада, его первое плечо - первый транзистор 19. С коллекторной нагрузки первого транзистора 19, через эмиттерный повторитель, включенный по схеме "зеркало тока", сигнал поступает на второй блок 2 - блок фиксации уровня или блок привязки к уровню постоянного напряжения сигнала с дифференциального каскада.

Коллекторной нагрузкой усилителя восьмого транзистора 36 являются параллельно включенные восьмой резистор 38 и третий конденсатор 39 в третьем блоке 3.

Выходной сигнал представляет собой фиксированный уровень постоянного напряжения, на который накладывается импульсный сигнал положительной полярности, и может быть определен формулой

U1=Uф+(Uимп1/Q), (1)

где U1 - первое напряжение на нагрузке, Uф - напряжение фиксированного уровня, Uимп1 - амплитуда импульсного напряжения положительной составляющей, Q - скважность импульсной последовательности, которая определяется как Q= Т/τ, где Т - период повторения импульсов, а τ - длительность импульсов тока в коллекторной цепи восьмого транзистора 36.

С коллекторной нагрузки второго транзистора 20 второго плеча дифференциального каскада через усилитель, включенный по схеме "зеркало тока", сигнал, пропорциональный синфазной и импульсной составляющей тока второго плеча, создает на коллекторной нагрузке (восьмой резистор 38 и третий конденсатор 39 в третьем блоке 3) напряжение, определяемое формулой

U2=Uс+(-Uимп2/Q), (2)

где U2 - второе напряжение на нагрузке, Uc - напряжение синфазной составляющей, -Uимп2 - амплитуда импульсного напряжения отрицательной составляющей, Q - скважность импульсной последовательности.

Коллекторная развязка между каскадами на восьмом транзисторе 36 и шестом транзисторе 25 позволяет определить суммарное напряжение Uобщ на нагрузке (третий блок 3 - восьмой резистор 38 и третий конденсатор 39, соединенные параллельно) по формуле

Uобщ=U1+U2=Uф+(Uимп1/Q)+Uc+(-Uимп2/Q). (3)

При расчете и настройке режима и коэффициента усиления усилителя на восьмом транзисторе 36 амплитуда импульсного сигнала |Uимп1| приравнивалась амплитуде |Uимп2|. Равенство амплитуд |Uимп1| и |Uимп2| является следствием равенства изменений токов плеч дифференциального каскада при стабильном токе генератора тока 21. При этом напряжение фиксированного уровня Uф может отличаться от напряжения синфазной составляющей Uc. При равенстве амплитуд |Uимп1| и |Uимп2| суммарное напряжение Uобщ равно сумме напряжения фиксированного уровня Uф и напряжения синфазной составляющей Uc. Сигнал с нагрузки (третий блок 3 - восьмой резистор 38 и третий конденсатор 39, соединенные параллельно) поступает на инвертируемый вход операционного усилителя 40, а его выход через эмиттерный повторитель (девятый транзистор) 42 поступает на регулируемый вход второго транзистора 20 ДУ 1. Опорное напряжение на неинвертированном входе операционного усилителя 40 устанавливается такой величины, чтобы синфазный ток второго плеча дифференциального каскада ДУ 1 был равен току первого плеча дифференциального каскада ДУ 1.

Проверка работоспособности устройства в условиях изменения температуры среды показала устойчивую работу и незначительные изменения режима дифференциального каскада ДУ 1.

Второй пример конкретного применения

Для поддержания неизменным фиксированного уровня постоянного напряжения при изменении температуры среды во второй блок 2 введен узел термокомпенсации (см. фиг.3). Упомянутый узел требуется для улучшения поддержания практически неизменным режима усиления восьмого транзистора 36. В остальном устройство не изменилось.

Во втором блоке 2 коллектор и база седьмого транзистора 32 (диод 32) дополнительно соединены с первым выводом девятого резистора 45. Второй вывод девятого резистора 45 соединен с эмиттером десятого транзистора 46. Коллектор десятого транзистора 46 соединен с первым выводом десятого резистора 47. Второй вывод десятого резистора 47 соединен с эмиттером восьмого транзистора 36. Также коллектор и база седьмого транзистора 32 соединены с первым выводом одиннадцатого резистора 48. Второй вывод одиннадцатого резистора 48 соединен с базой десятого транзистора 46 и с первым выходом двенадцатого резистора 49. Второй выход двенадцатого резистора 49 соединен с шиной питания положительной полярности 6.

Кроме того, для более стабильной работы устройства в него следует ввести следующие элементы. В четвертом блоке 4 входом 17 является первый вывод тринадцатого резистора 50, второй вывод которого соединен с инвертируемым входом операционного усилителя 40. Кроме того, инвертируемый вход операционного усилителя 40 через четырнадцатый резистор 51 соединен с выходом операционного усилителя 40. Также введен пятнадцатый резистор 52, соединяющий базу девятого транзистора 42 с первым выводом четвертой емкости 43, с выводом питания операционного усилителя 40 и шиной питания отрицательной полярности 7. Далее в четвертый блок 4 и ДУ 1 введен шестнадцатый резистор 53, соединяющий вход ДУ 1 и выход четвертого блока 4 с шиной питания отрицательной полярности 7. Кроме того, в ДУ 1 введен семнадцатый резистор 54, соединяющий первый вход ДУ 1 с шиной питания отрицательной полярности 7.

Предложенное устройство с узлом термокомпенсации работает следующим образом.

При стабильном напряжении на контуре анод-катод диода 32 - седьмой транзистор 32 в диодном включении, база - эмиттер восьмого транзистора 36 и седьмого резистора 37 ток в этой цепи равен

I=(Uстаб-U3-U4)/R7, (4)

где Uстаб - напряжение стабилизатора 35, U3 - напряжение на диоде - седьмом транзисторе 32, включенном в диодном режиме, U4 - напряжение база - эмиттер восьмого транзистора 36, R7 - номинал седьмого резистора 37.

При изменении температуры среды величины U3 и U4 изменяются. Изменение напряжения в цепи: седьмой транзистор (диод) 32 - "эмиттер - база" восьмого транзистора 36, приводит к изменению тока в цепи седьмого резистора 37 и, как следствие, к изменению коллекторного тока восьмого транзистора 36. В термокомпенсационном каскаде на десятом транзисторе 46, питаемого от стабилизатора напряжения 35, напряжение на "база - эмиттер" изменяется и меняется ток в цепи девятого резистора 45. При подключении коллектора десятого транзистора 46 к эмиттеру восьмого транзистора 36 изменения в цепи коллектора десятого транзистора 46 компенсируют изменения тока коллектора восьмого транзистора 36. Выбором режима десятого транзистора 46 - потенциала базы и номинала одиннадцатого резистора 48 можно добиться изменения тока коллектора десятого транзистора 46, компенсирующего изменения коллекторного тока восьмого транзистора 36 и в определенном расширенном диапазоне изменения температуры среды сделать его стабильным.

Введенные элементы устройства позволили нам получить стабильный широкополосный импульсный усилитель, режим которого не зависит от изменения составляющей сигнала на входе, что позволяет его использовать при реализации в качестве промежуточного каскада высокочувствительных широкополосных с большим динамическим диапазоном усилителей импульсных сигналов.

Промышленная применимость

Предложенное устройство может быть использовано при построении быстродействующих передающих и принимающих устройств, для волоконнооптических линий связи.

Источники информации

1. Патент RU 2074507, Научно-исследовательский институт измерительных систем (RU), 1992, Н 03 F 1/42, 1/30.

2. Патент RU 2080737, Попель А.С. (UA), 1992, Н 03 F 1/32, 3/343.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРЕДАТЧИК МУЛЬТИПЛЕКСНОЙ МАНЧЕСТЕРСКОЙ ЛИНИИ СВЯЗИ | 2002 |

|

RU2229769C2 |

| ПРЕДВАРИТЕЛЬНЫЙ УСИЛИТЕЛЬ ПРОМЕЖУТОЧНОЙ ЧАСТОТЫ | 2006 |

|

RU2316890C1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| ИНТЕГРАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2010 |

|

RU2436224C1 |

| ИНТЕГРАЛЬНЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2005 |

|

RU2289199C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ПРИ ПОПАДАНИИ В НИХ ТЯЖЕЛЫХ ЗАРЯЖЕННЫХ ЧАСТИЦ | 2005 |

|

RU2305894C2 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ | 2002 |

|

RU2231213C2 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОТ ВОЗДЕЙСТВИЯ РАДИАЦИИ | 2006 |

|

RU2322757C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ПЕРЕГРУЗКИ ПО ТОКУ ПРЕОБРАЗОВАТЕЛЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 2008 |

|

RU2370884C1 |

Использование: при построении быстродействующих передающих и принимающих устройств, для волоконно-оптических линий связи. Устройство поддержания режима работы по постоянному току дифференциального усилителя (ДУ) (1), являющегося первым блоком устройства, который имеет выводы, соединенные с общей шиной и питанием, три входа, на первый вход которого при работе поступает входной импульсный сигнал, два выхода, по выводу первого выхода которого при работе проходит выходной импульсный сигнал. Устройство включает еще три блока: второй блок (2) - блок фиксации уровня постоянного напряжения сигнала с дифференциального каскада, третий блок (3) - блок вычитания переменного импульсного сигнала и сложения постоянного сигнала, четвертый блок (4) - блок сравнения и управления по режиму. Технический результат - поддержание стабильного режима работы дифференциального усилителя при усилении псевдослучайных импульсных сигналов в широком частотном и динамическом диапазонах. 1 з. п.ф-лы, 3 ил.

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 1992 |

|

RU2080737C1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ ВЫСОКОЙ ЧАСТОТЫ | 1992 |

|

RU2074507C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ РЕЖИМА ТРАНЗИСТОРА | 1996 |

|

RU2116693C1 |

| US 5124663 А, 23.06.1992 | |||

| УСТРОЙСТВО ДЛЯ СКАНИРОВАНИЯ ХРОМАТОГРАММ В ТОНКОМ СЛОЕ СОРБЕНТА | 0 |

|

SU296992A1 |

Авторы

Даты

2003-06-27—Публикация

2001-08-07—Подача