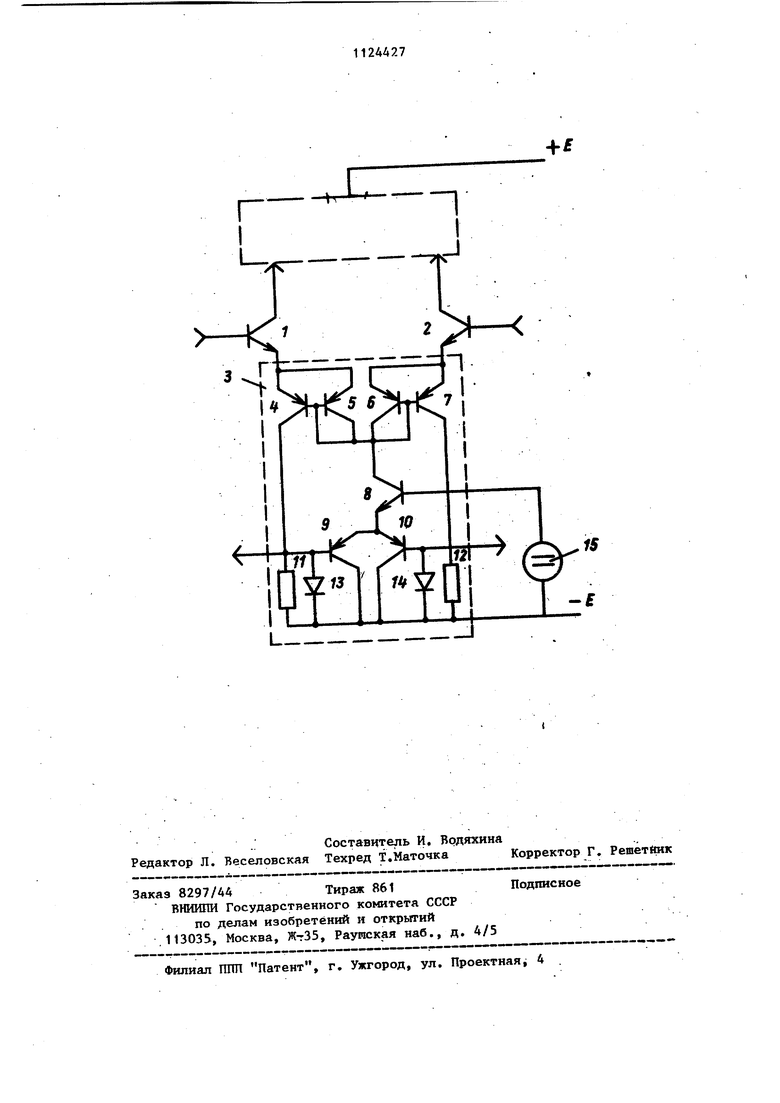

Изобретение относится к радиоэлек ронике и может быть использовано в качестве входного каскада в быстро действующих операционных усилителях. Известен дифференциальный усили тель, содержащий первый и второй входные транзисторы одной структуры, эмиттеры которых подключены соответственно к первому и второму выходам блока токового смещения l . Однако быстродействие в известно дифференциальном усилителе ограничено значительной паразитной емкость обусловленной параллельным соединением двз переходов коллекторбаза транзисторов в блоке токового смещения. Наиболее близким к предлагаемому по технической сущности является дифференциальный усилитель, содержащий первый и второй транзисторы, баз которых являются соответствующими входами дифференциального усилителя, а эмиттеры подключены соответственно к объединенным эмиттерам третьего и четвертого транзисторов и к объе- диненным эмиттерам пятого и шестого транзисторов, базы которых объединены и подключены к коллекторам четвер того, пятого и седьмого транзисторов база седьмого транзистора через источник напряжения смещения подключен к соответствующей щине источника пит ния, к которой также подключены первые вьтоды первого и второго токо задающих элементов, коллектор третье го транзистора соединен с базой вось мого транзистора, а также девятый транзистор, причем структура первого, второго и седьмого транзисторов противоположна структуре третьего четвертого, пятого и шестого транзисторов . . Однако известное устройство обладает сравнительно малым быстродейстЦель изобретения - увеличение быстродействия. Поставленнаяцель достигается тем, что в дшЬференциальном усилите ле, содержащем первый и второй транзисторы, базы которых являются соответствующими входами дифференхщального усилителя, а эмиттеры подключены соответственно к объединенным эмиттерам третьего и четв.ертого транзисторов и к объединенным эмитте рам пятого и гаестого транзисторов. базы которых объединены и подключены к коллекторам четвертого, пятого и седьмого транзисторов, база седьмого транзистора через источник напряжения смещения подключена к соответствующей шине источника питания,к которой также подключены первые выводы первого и второго токозадающих элементов, коллектор третьего транзистора соединен с базой восьмого транзистора, а также девятый транзистор, причем структура, первого, второго и седьмого транзисторов противоположна структуре третьего, четвертого, пятого и щестого транзисторов, восьмой и девятьй транзисторы включены по схеме с общим коллектором, их эмиттеры объединены и пбдключены к эмиттеру седьмого транзистора, а базы подключены к вторым выводам соответственно первого и второго токозадающих элементов параллельно которым включены введенные в усилитель первый и второй пряМосмещенные диоды соответственно, коллектор щестого транзистора соединен с базой девятого транзистора, при этом восьмой и девятьй транзисторы имеют структуру, одинаковую со структурой третьего, четвертого, пятого и щестого транзисторов а .коллекторы первого и второго транзисторов являются выходами дифференциального усилителя. На чертеже представлена принципиальная электрическая схема дифференциального усилителя. Дифференциальный усилитель содержит первый 1 и второй 2 транзисторы, активный источник-тока 3, состоящий из третьего 1, девятого транзисторов , первого 11 и второго 12 токозадающик элементов, первого 13 и второго 14 прямосмещенных диодов и источник 15 напряжения смещения. Дифференциальный усилитель работает следующим образом. При подключении коллекторов первого 1 и второго 2 транзисторов к элементам нагрузки и подаче питания в коллекторных цепях всех транзисторов начинает протекать ток. При условии, что первый 1 и второй 2 транзисторы, третий- шестой транзисторы 4-7 и восьмой 9 и девятый 10 транзисторы взаимно согласованы, первый 11 и второй 12 токозадающие элементы одинаковы, а сдвиг на базах первого 1 и второго 2 тран зисторов отсутствует, с учетом глубокой обратной отрицательной связи по току в схеме источника тока 3 можно записать 1,. + U 21 V э68- э6) где,. iJg, . эмиттерные то1си перво го 1 и второго 2 трав зйсторов соответствен коллекторные токи соот IM iT ветствующих транзисто ров. напряжение источника 15 напряжения смещения;U ggjUgg,- прямое смещение базо эмиттерных переходов соответствующих транзисторов J R - сопротивление первого 11 и второго 12 токозадающих элементов, Численные коэффициенты в выражения соответствуют равенству эмиттерных площадей третьего, шестого транзисто ров 4-7. Наличие глубокой отрицательной обратной связи по току позволяет обеспечить высокое выходное сопроти ление источника тока 3 относительно первого и второго его выходов, кото рое примерно равно выходному сопротивлению транзистора с общей базой при равном выходном токе и равном падении на резисторах обратной связ при этом обеспечивается хорошее подавление синфазного сигнала, поданного на входы ДУ. Кроме этого, наличие обратной отрицательной связи и используемая конфигурация источника тока 3 способствует снижению дрейфа, обусловл ного нестабильностью токовогр-питания, даже при значительной асимметрии в схеме. В режиме малого сигнала частотно усилительные характеристики предлагаемого ДУ соответствуют характерис тикам известных схем при равных. эмиттерных токах усилительных транзисторов. В режиме большого сигнала запира ние одного из усилительных транзист ров, например 1, приводит к выключе нию третьего транзистора 4 и уменьшению падения напряжения на первом токозадающем элементе 11. При этом коллекторные токи седьмого 8 и восьмого 9 транзисторов возрастают до значения, которое ограничивается лишь крэффициентом усиления тока восьмого транзистора 9. Увеличение коллекторного тока седьмого транзистора 8 отражается схемой токового зеркала, выполненной на пятом 6 и шестом 7 транэисто pax при этом коллекторный ток пестого транзистора 7 пропорционально возрастает, а падение напряжения на втором токозадающем элементе 12 увеличивается до тех пор, пока основная часть коллекторного тока щестого транзистора 7 не начнет отводиться через второй прямосмещенный диод на шину питания. Поскольку общая точка схемы токового зеркала является одним из . выходов источника тока 3 и подключена к эмиттеру второго транзистора 2, то его кол,лекторный ток значительно возрастает, при этом функция передачи предлагаемого ДУ примерно соответствует прототипу, однако крутизна передачи в режиме болыпого сигнала для предлагаемого устройства имеет большее значение. На больших перепадах входного синфазного сигнала запирающей полярности, когда наличие емкостей коллектор-база третьего 4,.шестого 7 и седьмого В транзисторов способ- , ствует одновременному снижению эмиттерных токов первого 1 и второго 2 транзисторов в равной степени уменьшаются коллекторные токи третьего 4 и шестого 7 транзисторовА; уменьшается падение напряокения на первом 11 и втором 12 токозадающих элементах и увеличиваются коллектор ные токи седьмого 8, восьмого 9 и девятого 10 транзисторрв. Увелитчение этих токов способствует ускорению заряда паразитных емкостей, причем наличие емкостей коллекторбаза третьего 4 и шестого 7 транзисторов способствует возникновению положительной обратной связи. в структуре источника тока 3 и дополнительному увеличению тока, заряжающего паразитные емкости. При этом в отлимие от прототипа,. быстродействие которого в режиме большого синфазного сигнала ограничено скоростью перезаряда выходных

емкостей первого и второго блоков токового сгмещения, быстродействие предлагаемого ДУ ограничивается лиш частотными свойствами применяемых транзисторов, постоянной .времени базовых цепей восьмого 9 и девятого 10 транзисторов с учетом возникающей при запиракяцих входных сигналах положительной обратной связи и при перепадах напряжения на первом 11 и втором 12 токозадающих элементах не превьшающих сотен милливольт, является принципиально более высоким.

При использовании предлагаемого ДУ в операционном усилителе i симметричным промежуточным каскадом высокое быстродействие обеспечивает ся без изменений операционного усилителя, если только достигнутая скорость нарастания не ограничивается другими его каскадами. Однако симметричная структ а промежуточного каскада предполагает наличие двух параллельных токовых ветвей, что при основном токопотреблении в этом каскаде, необходимом для улучшения частотных свойств операционного усилителя, делает его недостаточно эконот шчным.

Поэтому в предлагаемом ДУ предусмотрена возможность осуществления симметричного усиления тока .в операционных усилителях содержащих несимметричные промежуточные каскады, при этом несимметричный промежуточный каскад приобретает свойства двухтактного усилителя. Для этого в источнике тока 3 предусмотрены дополнительные выходы, к которым могут подключаться входы усилителей тока, используемых в качестве динамческой нагрузки промежуточного, кас,када, устанавливаемых, вместо традиционньк пассивных токостабилизаторов или вместе с ними. При этом необходимая токовая симметрия в каскадах операционного усилителя в

уравновешенном режиме и в режиме большого сигнала легко обеспечивается обычными методами интегральной схемотехники.

Двухтактная структура промежуточного каскада, образованная при использовании предлагаемого ДУ, позволяет обеспечить высокое быстродействие операционного усилителя, симметрию предельных скоростей нарастания

и высокую нагрузочную способность без снижения экономичности.

Следует отметить, что источник тока 3 является устойчивым, не увеличивает числа полюсов малосигнапьной амшшту{ но-частотной характеристики операционного усилителя и не требует дополнительных цепей коррекции.

Применение резисторов в качестве первого и второго токозадаюнщх элементов является предпочтительным ввиду меньшей их собственной емкости и возможности ограничения выходноfo тока ДУ на допустимом уровне, однако .при необходимости первый и второй резисторы могут быть заменены токостабилизаторами, при этом суммарньй ток смещения первого

и второго транзисторов в уравновешенном режим,е равен удвоенной сумме их выходных токов.

Применение предлагаемого ДУ целесообразно в операционных усилителях любого типа, при этом улучшение их быстродействия не сопровождается ухудшением других параметров, в том числе экономичности и точности по входу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель | 1983 |

|

SU1160530A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421885C1 |

| Усилитель | 1988 |

|

SU1720146A1 |

| Операционный усилитель | 1983 |

|

SU1193773A1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349024C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

| Дифференциальный усилитель | 1981 |

|

SU1083341A2 |

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| Множительное устройство | 1982 |

|

SU1119037A1 |

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ содержащий первый и второй транзисторы, базы которых являются соответствующими входами дифференциального усилителя, а эмиттеры подключены соответственно к объединенным эмиттерам третьего и четвертого транзисторов и к объединенным эмиттерам пятого и шестого транзисторов, базы . которых объединены и подключены к коллекторам четвертого, пятого и седьмого транзисторов, база седьмого транзистора через источник напряжения смещения подключена к соответствующей шине источника питания, к которой также подключенн первые выводы первого и второго токозадающих элементов, коллектор третьего транзистора соединен с базой восьмого транзистора, а также девятый транзистор, причем структура первого, второго и седьмого транзисторов противоположна структуре третьего, четвертого, пятого и шестого транзисторов, отличающийс я тем, что, с целью увеличения быстродействия восьмой и девятый транзисторы включены по схеме с общим коллектором, их эмиттеры объединены и подключены к эмиттеру седьмого транзистора, а базы подключены к вторым выводам соответственно первого и второго, токозадакидих элементов, параллельно которым включены § введенные в усилитель первый и второй прямосмещенные диоды соответстU венно, коллектор шестого транзистора соединен с базой девятого транзистора, при этом восьмой и девятый транзисND 4 { hO Ч торы имеют структуру, одинаковую со структурой третьего, четвертого пятого и шестого транзисторов, а коллекторы первого и второго транзисторов являются выходами дифференциального усилителя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналоговые интегральные схемы.Под ред | |||

| Дж.Коннели | |||

| М., Мир, 1977, С.105 фиг.3.26а | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| КУРИТЕЛЬНОЕ ИЗДЕЛИЕ | 2013 |

|

RU2633952C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-29—Подача