Изобретение относится к электронике, а именно к повторителям напряжения для усиления тока и преобразования импеданса в цепях электронных устройств, выполненным по интегральной технологии. Изобретение может использоваться во входных каскадах операционных усилителей и в качестве буферного усилителя для работы на низкоомные и емкостные нагрузки в электрических схемах для видеотехники, радиолокации, измерительной техники, связи и в других областях.

Известна схема повторителя напряжения, содержащая первый n-p-n-транзистор, база которого соединена с базой первого p-n-p-транзистора и со входом устройства, эмиттер - с эмиттером второго p-n-p-транзистора, а коллектор - с шиной питания положительной полярности и с первым зажимом первого источника тока. Эмиттер первого p-n-p-транзистора подключен к эмиттеру второго n-p-n-транзистора, а коллектор - к шине питания отрицательной полярности. База второго n-p-n-транзистора соединена с его коллектором, а также со вторым зажимом первого источника тока и с базой третьего n-p-n-транзистора, коллектор которого подключен к шине питания положительной полярности, а эмиттер - к эмиттеру третьего p-n-p-транзистора, база которого соединена с коллектором третьего p-n-p-транзистора, с выходом устройства и с коллектором и базой четвертого n-p-n-транзистора, эмиттер которого подключен к эмиттеру четвертого p-n-p-транзистора, коллектор которого соединен с шиной питания отрицательной полярности, а база - с коллектором и базой второго p-n-p-транзистора и первым зажимом второго источника тока, второй зажим которого подключен к шине питания отрицательной полярности [1]. Схема обладает недостаточными динамическим диапазоном передаваемого сигнала, быстродействием и точностью вследствие применения в тракте передачи напряжения транзисторов в диодном включении.

Известна другая схема повторителя напряжения, содержащая первый n-p-n-транзистор, эмиттер которого соединен со входом устройства и с эмиттером первого p-n-p-транзистора, база - с базой второго n-p-n-транзистора, эмиттером третьего n-p-n-транзистора и первым зажимом первого источника тока, а коллектор - с базой третьего n-p-n-транзистора, коллектор которого подключен к шине питания положительной полярности и первому зажиму второго источника тока, второй зажим которого соединен с коллектором первого n-p-n-транзистора. Эмиттер второго n-p-n-транзистора подключен к эмиттеру второго p-n-p-транзистора и выходу устройства, а коллектор - к шине питания положительной полярности и первому зажиму третьего источника тока, второй зажим которого соединен с базами первого и второго p-n-p-транзисторов и эмиттером третьего p-n-p-транзистора, база которого подключена к коллектору первого p-n-p-транзистора и первому зажиму четвертого источника тока, а коллектор - к шине питания отрицательной полярности, коллектору второго p-n-p-транзистора и вторым зажимам первого и четвертого источников тока [2].

Описанная выше структурная схема наиболее близка к предлагаемому варианту и принята за прототип. Повторители, отвечающие данной структуре, имеют неудовлетворительную совокупность параметров: напряжение смещения и быстродействие вследствие применения дополнительных каскадов с общим коллектором, которые не позволяют задать одинаковые режимы для входных и выходных транзисторов и наличия значительных емкостей, ограничивающих скорость нарастания.

Целью данного изобретения является повышение быстродействия и точности.

Для достижения поставленной цели в схему интегрального повторителя напряжения, содержащую первый n-p-n-транзистор, эмиттер которого соединен с эмиттером первого p-n-p-транзистора и входом устройства, а база - с базой второго n-p-n-транзистора, эмиттер которого подключен к эмиттеру второго p-n-p-транзистора и к выходу буферного усилителя, база второго p-n-p-транзистора соединена с базой первого p-n-p-транзистора, шину питания положительной полярности, шину питания отрицательной полярности, дополнительно введены: первый резистор, первый вывод которого подключен к базе первого n-p-n-транзистора, а второй вывод - к базе первого p-n-p-транзистора, третий p-n-p-транзистор, коллектор которого соединен с базой первого n-p-n-транзистора, эмиттер - с коллектором первого n-p-n-транзистора, второй резистор, первый вывод которого подключен к коллектору первого n-p-n-транзистора, а второй вывод - к шине питания положительной полярности, третий n-p-n-транзистор, коллектор которого соединен с базой первого p-n-p-транзистора, а эмиттер - с коллектором первого p-n-p-транзистора, третий резистор, первый вывод которого подключен к коллектору первого p-n-p-транзистора, а второй вывод - к шине питания отрицательной полярности, первая коллекторная нагрузка, первый вывод которой соединен с шиной питания положительной полярности, а второй вывод - с коллектором второго n-p-n-транзистора, вторая коллекторная нагрузка, первый вывод которой подключен к коллектору второго p-n-p-транзистора, а второй вывод - к шине питания отрицательной полярности, цепь задания режимного тока, первый вывод которой соединен с шиной питания положительной полярности, второй вывод - с базой третьего p-n-p-транзистора, третий вывод - с базой третьего n-p-n-транзистора и четвертый вывод - с шиной питания отрицательной полярности.

Признаками, отличающими предлагаемую схему интегрального повторителя напряжения от прототипа, являются наличие третьего p-n-p-транзистора, коллектор которого соединен с базой первого n-p-n-транзистора, эмиттер - с коллектором первого n-p-n-транзистора, первого резистора, первый вывод которого подключен к базе первого n-p-n-транзистора, а второй вывод - к базе первого p-n-p-транзистора, третьего n-p-n-транзистора, коллектор которого соединен с базой первого p-n-p-транзистора, а эмиттер - с коллектором первого p-n-p-транзистора, второго резистора, первый вывод которого подключен к коллектору первого n-p-n-транзистора, а второй - к шине питания положительной полярности, третьего резистора, первый вывод которого соединен с коллектором первого p-n-p-транзистора, а второй вывод - с шиной питания отрицательной полярности, первой коллекторной нагрузки, первый вывод которой подключен к шине питания положительной полярности, а второй вывод - к коллектору второго n-p-n-транзистора, второй коллекторной нагрузки, первый вывод которой соединен с коллектором второго p-n-p-транзистора, а второй вывод - с шиной питания отрицательной полярности, цепи задания режимного тока, первый вывод которой подключен к шине питания положительной полярности, второй вывод - к базе третьего p-n-p-транзистора, третий вывод - к базе третьего n-p-n-транзистора и четвертый вывод - к шине питания отрицательной полярности.

Таким образом, заявленное схемное решение соответствует критерию "новизна".

Повышение быстродействия обусловлено увеличением скорости нарастания за счет уменьшения постоянных времени цепей заряда паразитных емкостей благодаря введению в схему третьего p-n-p-транзистора и третьего n-p-n-транзистора, включенных по схеме с общей базой и обеспечивающих их режим по постоянному току, первого, второго и третьего резисторов.

Повышение точности обусловлено уменьшением напряжения смещения вследствие выравнивания напряжений коллектор-эмиттер входных и выходных транзисторов благодаря введению в схему третьего p-n-p-транзистора и третьего n-p-n-транзистора, первого, второго и третьего резисторов, первой и второй коллекторных нагрузок, а также цепи задания режимного тока.

Таким образом, повышение быстродействия и точности интегрального повторителя напряжения обусловлено введением в схему интегрального повторителя напряжения третьего p-n-p-транзистора и третьего n-p-n-транзистора, первого, второго, третьего резисторов, первой и второй коллекторных нагрузок, а также цепи задания режимного тока.

Следовательно, заявленное схемотехническое решение соответствует критерию "изобретательский уровень".

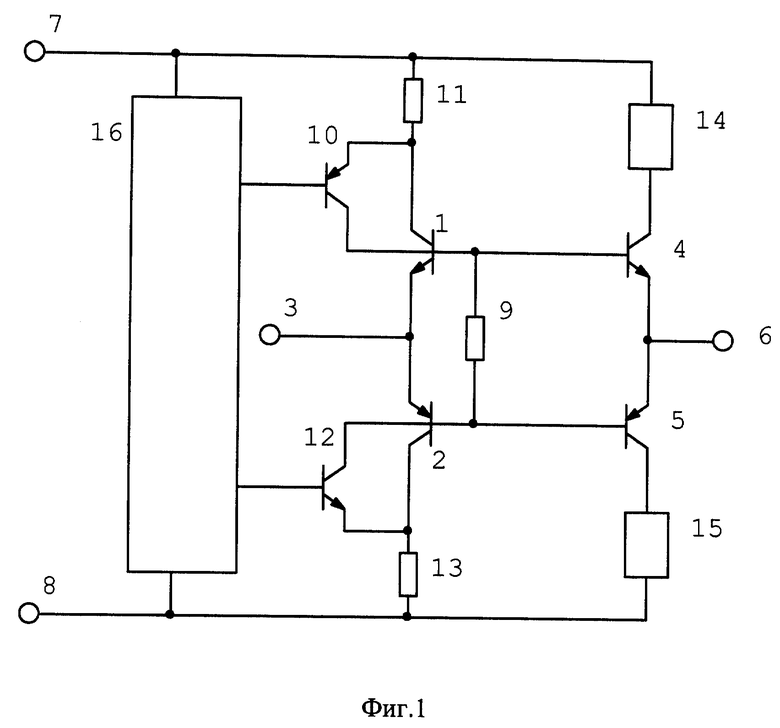

Примером реализации интегрального повторителя напряжения является электрическая схема, изображенная на фиг.1.

Интегральный повторитель напряжения содержит первый n-p-n-транзистор 1, эмиттер которого соединен с эмиттером первого p-n-p-транзистора 2 и входом устройства 3, а база - с базой второго n-p-n-транзистора 4, эмиттер которого подключен к эмиттеру второго p-n-p-транзистора 5 и к выходу буферного усилителя 6, база второго p-n-p-транзистора 5 соединена с базой первого p-n-p-транзистора 2, шину питания положительной полярности 7, шину питания отрицательной полярности 8, первый резистор 9, первый вывод которого подключен к базе первого n-p-n-транзистора 1, а второй вывод - к базе первого p-n-p-транзистора 2, третий p-n-p-транзистор 10, коллектор которого соединен с базой первого n-p-n-транзистора 1, эмиттер - с коллектором первого n-p-n-транзистора 1, второй резистор 11, первый вывод которого подключен к коллектору первого n-p-n-транзистора 1, а второй вывод - к шине питания положительной полярности 7, третий n-p-n-транзистор 12, коллектор которого соединен с базой первого p-n-p-транзистора 2, а эмиттер - с коллектором первого p-n-p-транзистора 2, третий резистор 13, первый вывод которого подключен к коллектору первого p-n-p-транзистора 2, а второй вывод - к шине питания отрицательной полярности 8, первую коллекторную нагрузку 14, первый вывод которой соединен с шиной питания положительной полярности 7, а второй вывод - с коллектором второго n-p-n-транзистора 4, вторую коллекторную нагрузку 15, первый вывод которой подключен к коллектору второго p-n-p-транзистора 5, а второй вывод - к шине питания отрицательной полярности 8, цепь задания режимного тока 16, первый вывод которой соединен с шиной питания положительной полярности 7, второй вывод - с базой третьего p-n-p-транзистора 10, третий вывод - с базой третьего n-p-n-транзистора 12 и четвертый вывод - с шиной питания отрицательной полярности 8.

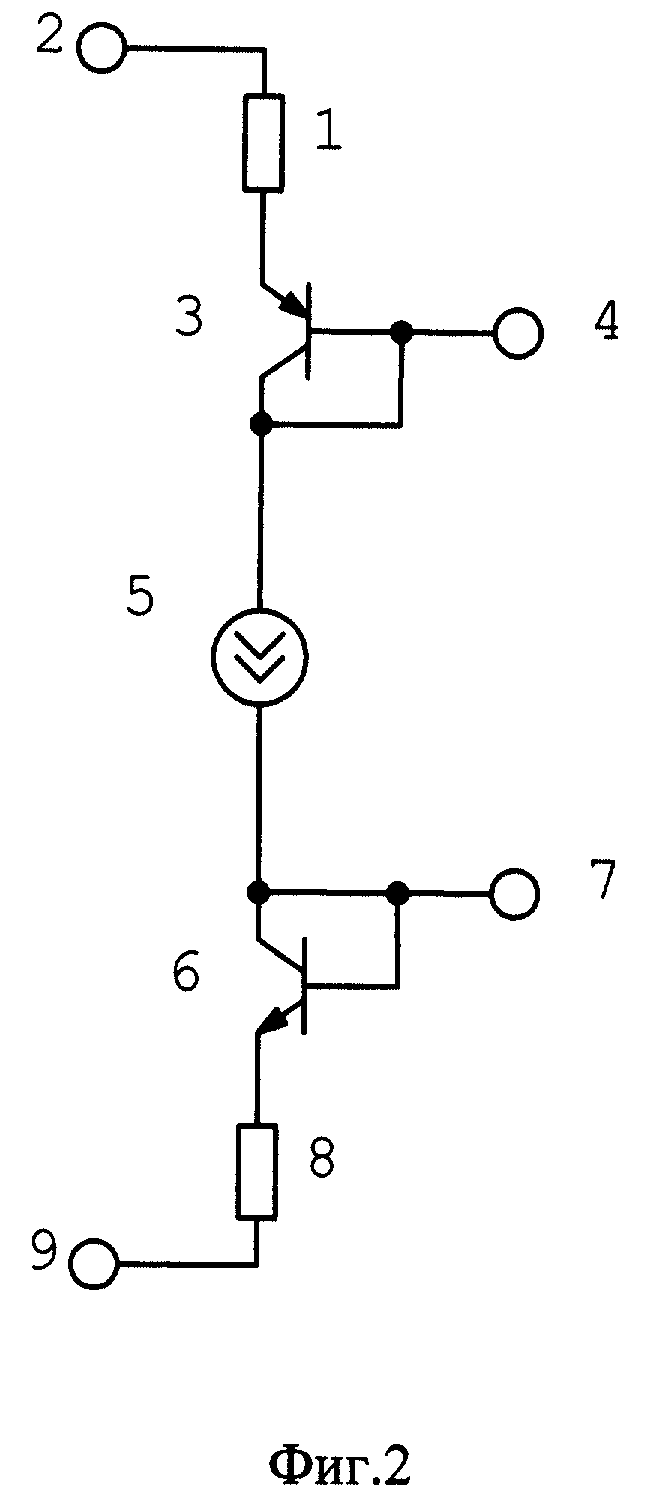

На фиг.2 приведен пример реализации цепи задания режимного тока. Схема содержит первый резистор 1, первый вывод которого является первым выводом устройства 2, а второй вывод подключен к эмиттеру p-n-p-транзистора 3, база которого соединена с его коллектором и является вторым выводом устройства 4, а коллектор подключен к первому зажиму источника тока 5, второй вывод которого соединен с коллектором и базой n-p-n-транзистора 6 и является третьим выводом устройства 7, эмиттер n-p-n-транзистора 6 подключен к первому выводу второго резистора 8, второй вывод которого является четвертым выводом устройства 9.

В качестве первой и второй коллекторных нагрузок могут быть использованы резисторы.

Предложенная схема интегрального повторителя напряжения позволяет повысить быстродействие в 1,47 раза по сравнению с прототипом. Также предложенная схема по сравнению со схемой прототипа позволяет увеличить точность за счет уменьшения напряжения смещения по сравнению с прототипом с 1,13 до 0,11 мВ. Отмеченные выше свойства схемы являются техническим результатом.

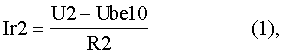

Схема работает следующим образом. С помощью цепи задания режимного тока задается ток через резистор 11 (R2) для верхнего плеча повторителя:

где U2 - разность напряжений между 1 и 2 выводами цепи задания режимного тока, Ube10 - напряжение база-эмиттер третьего p-n-p-транзистора 10, R2 - номинал второго резистора 11. Ток коллектора третьего p-n-p-транзистора 10:

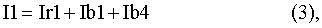

где α - коэффициент передачи эмиттерного тока в коллектор третьего p-n-p-транзистора 10, Iq1 - ток коллектора первого n-p-n-транзистора 1. Ток I1 разветвляется на три составляющих:

где Ir1 - ток через первый резистор 9, Ib1 - ток базы первого n-p-n-транзистора 1, Ib4 - второго n-p-n-транзистора 4.

Аналогично задается коллекторный ток третьего n-p-n-транзистора 12 для нижнего плеча повторителя.

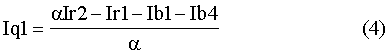

Решая систему уравнений (2) и (3), можно найти режимный ток первого n-p-n-транзистора 1:

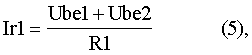

Аналогично находится ток коллектора первого p-n-p-транзистора 2. Ток через первый резистор 9 можно найти как:

где Ube1 - напряжение база-эмиттер первого n-p-n-транзистора 1, Ube2 - напряжение база-эмиттер первого p-n-p-транзистора 2, R1 - номинал первого резистора 9.

Транзисторы 1 и 4, 2 и 5 попарно идентичны, т.к. выполнены на одном кристалле, и их коллекторные токи одинаковы. Тогда, если выбрать номинал резистора R4, используемого в качестве коллекторной нагрузки:

то падения напряжений на R2 и R4 будут одинаковы и, следовательно, напряжения коллектор-эмиттер n-p-n-транзисторов 1 и 4 будут равны. Аналогично задается равенство напряжений коллектор-эмиттер для p-n-p-транзисторов 2 и 5.

Таким образом, входной и выходной n-p-n-транзисторы и входной и выходной p-n-p-транзисторы имеют одинаковые напряжения коллектор-эмиттер и одинаковые токи коллекторов, следовательно, их напряжения Ube также будут одинаковы, что практически сводит к нулю напряжение смещения повторителя. Это условие не выполняется в схеме прототипа, т.к. напряжения коллектор-база (Ukb) входных транзисторов в ней равны Ube транзисторов, подключенных своими базами к их коллекторам, а Ukb выходных транзисторов равно напряжению питания за вычетом Ube и могут отличаться в 19 раз (при напряжении питания ±15 В). Если учесть, что при Ukb=Ube транзистор (особенно СВЧ-типа) попадает в область квазинасыщения или близок к ней, то его Ube будет заметно отличаться от Ube, идентичного по типу транзистора при Ukb, во много раз большем Ube. Моделирование показывает, что при напряжении питания ±15 В и режимных токах транзисторов 1 мА напряжение смещения прототипа 1,13 мВ, а заявляемого устройства - 0,11 мВ.

При действии на входе устройства быстро изменяющегося напряжения, например импульса положительной полярности, эмиттер транзистора 1 смещается в положительном направлении и транзистор практически обесточивается. При этом ток коллектора транзистора 10 становится равным:

Заряд суммарной паразитной емкости Cs в точке соединения баз транзисторов 1 и 4, которая формирует доминирующий полюс устройства при положительной полярности импульса, осуществляется током:

Нетрудно заметить, что при условии задания через входные транзисторы заявляемого устройства и прототипа одинаковых режимных токов Iq в заявляемом устройстве и прототипе будут одинаковы (речь идет о заряде суммарной паразитной емкости, действующей на коллекторе входного транзистора для схемы прототипа).

где Cbk1 - емкость база-коллектор транзистора 1, Cbk4 - емкость база-коллектор транзистора 4, Cbk10 - емкость база-коллектор транзистора 10, Cks1 - емкость коллектор-подложка транзистора 10. Аналогичное выражение для прототипа при условии, что аналогичные транзисторы в схемах одинаковы, выглядит так:

Здесь принято, что источник тока, соединенный с коллектором входного транзистора, выполнен на транзисторе, аналогичном транзистору 10. Cbkt - емкость коллектор-база транзистора VT5, базоэмиттерный переход которого включен между коллектором и базой входного транзистора. Cks1 - емкость коллектор-подложка входного транзистора. Как видно из (9) и (10), в составе Csp по сравнению с Cs вместо Cbk4 входит Cbkt и дополнительная емкость Cks1. Если даже учесть, что площадь эмиттера VT5 меньше, чем у транзистора 4, к примеру, в 3 раза Cks1 дает существенно больший вклад в суммарную паразитную емкость, т.к. емкость коллектор-подложка для интегральных транзисторов с изоляцией p-n-переходом почти на порядок больше, чем их емкость коллектор-база. Для большей определенности приведем типичные значения паразитных емкостей и получаемые при этом численные значения Cs и Csp для комплементарной биполярной микросхемы. Cbk1=Cbk4=0,26 пФ, Cbkt=0,138 пФ, Cbk10=0,25 пФ, Cks10=2,3 пФ, Cks1=1,12 пФ. Тогда Cs=3,07 пФ, Csp=4,068 пФ.

Аналогично рассмотренному работает нижняя половина схемы. Для заявляемого устройства суммарная паразитная емкость в точке доминирующего полюса для отрицательной полярности входного сигнала Cs-=1,824 пФ. Для прототипа - Csp-=4,511 пФ. Различие в величинах емкостей для верхней и нижней половин схем объясняется тем, что емкости p-n-p-транзисторов больше, чем у n-p-n-транзисторов, что связано с технологическими особенностями изготовления интегральных микросхем с изоляцией p-n-переходами.

Скорость нарастания выходного напряжения устройства определяется как:

где С - суммарная паразитная емкость в точке, определяющей доминирующий полюс устройства. Т.к. Vu.вых устройства определяется по наихудшей полярности, то при расчете следует брать Cs - для заявляемого устройства и Csp - для прототипа. Следовательно, скорости нарастания выходного напряжения заявляемого устройства и прототипа будут отличаться как Csp-/Cs, т.е. в 1,47 раза.

При сравнительном моделировании заявляемого устройства и прототипа получены следующие результаты (при одинаковых режимных токах и параметрах транзисторов).

Напряжение смещения заявляемого устройства по сравнению с прототипом уменьшилось с 1,13 до 0,11 мВ.

Скорость нарастания выходного напряжения заявляемого устройства по сравнению с прототипом увеличилась в 2,2 раза (с 1270 до 2827 В/мкс).

При расчете применены параметры моделей, созданных для быстродействующих микросхем, выполняемых по комплементарной биполярной технологии с изоляцией p-n-переходом.

Список литературы

1. U.S. Patent №4639685, 330/263; 330/267, Jan. 27, 1987.

2. U.S. Patent №5218321, 330/263; 330/267, Jun. 8, 1993 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1993 |

|

RU2057392C1 |

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 2001 |

|

RU2207712C2 |

| Интегральный усилитель воспроизведения для стереофонических магнитофонов | 1979 |

|

SU1003139A1 |

| Усилитель | 1988 |

|

SU1656669A1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2004 |

|

RU2274947C2 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Формирователь импульсов управления | 1987 |

|

SU1522387A2 |

| ИНТЕГРАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2010 |

|

RU2436224C1 |

| Согласующее устройство для ультразвукового пьезопреобразователя | 1989 |

|

SU1647384A1 |

| Генератор импульсов | 1981 |

|

SU1018195A1 |

Изобретение относится к электронике, а именно к повторителям напряжения для усиления тока и преобразования импеданса в цепях электронных устройств, выполненным по интегральной технологии. Технический результат заключается в повышении быстродействия и точности. Устройство содержит первый-третий n-p-n транзисторы (Т) (1,4,12), первый-третий p-n-p Т (2,5,10), резисторы (Р) (9,11,13), коллекторные нагрузки (14,15). Повышение быстродействия обусловлено увеличением скорости нарастания за счет уменьшения постоянных времени цепей заряда паразитных емкостей благодаря введению Т (10) и Т (12), включенных по схеме с общей базой и обеспечивающих их режим по постоянному току Р (9,11,13). Повышение точности обусловлено уменьшением напряжения смещения вследствие выравнивания напряжений коллектор-эмиттер входных Т (1,2) и выходных Т (4,5) благодаря введению Т (10,12), Р (9,11,13), коллекторных нагрузок (14,15), а также цепи задания режимного тока (16). 2 ил.

Интегральный повторитель напряжения, содержащий первый n-p-n-транзистор, эмиттер которого соединен с эмиттером первого p-n-p-транзистора и входом устройства, а база - с базой второго n-p-n-транзистора, эмиттер которого подключен к эмиттеру второго p-n-p-транзистора и к выходу буферного усилителя, база второго p-n-p-транзистора соединена с базой первого p-n-p-транзистора, шину питания положительной полярности, шину питания отрицательной полярности, отличающийся тем, что, с целью повышения быстродействия и точности, в него введены: первый резистор, первый вывод которого подключен к базе первого n-p-n-транзистора, а второй вывод - к базе первого p-n-p-транзистора, третий p-n-p-транзистор, коллектор которого соединен с базой первого n-p-n-транзистора, эмиттер - с коллектором первого n-p-n-транзистора, второй резистор, первый вывод которого подключен к коллектору первого n-p-n-транзистора, а второй вывод - к шине питания положительной полярности, третий n-p-n-транзистор, коллектор которого соединен с базой первого p-n-p-транзистора, а эмиттер - с коллектором первого p-n-p-транзистора, третий резистор, первый вывод которого подключен к коллектору первого p-n-p-транзистора, а второй вывод - к шине питания отрицательной полярности, первая коллекторная нагрузка, первый вывод которой соединен с шиной питания положительной полярности, а второй вывод - с коллектором второго n-p-n-транзистора, вторая коллекторная нагрузка, первый вывод которой подключен к коллектору второго p-n-p-транзистора, а второй вывод - к шине питания отрицательной полярности, цепь задания режимного тока, первый вывод которой соединен с шиной питания положительной полярности, второй вывод - с базой третьего p-n-p-транзистора, третий вывод - с базой третьего n-p-n-транзистора и четвертый вывод - с шиной питания отрицательной полярности.

| US 5218321 А, 08.06.1993 | |||

| Широкополосный усилитель | 1987 |

|

SU1584075A1 |

| US 5323122 A, 21.06.1994 | |||

| US 4639685, 27.01.1987 | |||

| СПОСОБ ХИМИЧЕСКОЙ СТЕРИЛИЗАЦИИ ЭНДОСКОПИЧЕСКОЙ АППАРАТУРЫ | 2002 |

|

RU2232030C1 |

Авторы

Даты

2006-12-10—Публикация

2005-05-04—Подача