Изобретение относится к области электронной техники и может быть использовано при построении высоконадежных резервированных устройств и систем для выбора среднего по напряжению из трех сигналов.

Известен аналоговый мажоритар для выбора цепей, описание которого приведено в [1], он предназначен для выбора среднего из трех сигналов, поступающих на его входы. Устройство содержит первый, второй и третий усилители с релейной характеристикой, охваченные общей отрицательной обратной связью и соединенные с соответствующими входами устройства.

Однако максимально возможный выходной сигнал этого устройства Uвых.mах не может превышать значения Uн/3, где Uн - напряжение насыщения усилителя (максимально возможный выходной сигнал), что накладывает значительные ограничения на параметры системы.

Известно устройства выбора среднего сигнала - прототип, описание которого приведено в [2], оно предназначен для выбора среднего по напряжению из трех сигналов, поступающих на его входы. Устройство содержит схему управления, реализованную на компараторах, для сравнения входных сигналов друг с другом, и электронные ключи для соединения входов устройства с его выходом.

Недостаток известного устройства состоит в том, что оно имеет один выход, в результате чего обладает низкой надежностью, т. к. отказ выхода приводит к выходу из строя всего канала обработки информации.

Задача изобретения - повышение надежности.

Эта задача достигается тем, что в устройство выбора сигналов, содержащее первый, второй и третий входы, первый, второй и третий компараторы, неинвертирующие входы которых соединены с инвертирующими входами, соответственно, третьего, первого и второго компараторов, дополнительно введены первый, второй и третий усилитель, шифратор, первый, второй, третий, четвертый и пятый мультиплексоры, первое и второе пороговое устройство, первый и второй интеграторы, при этом первый, второй и третий входы устройства через первый, второй и третий усилители соединены, соответственно, с неинвертирующими входами первого, второго и третьего компараторов, первым, вторым и третьим выходами устройства и первым, вторым и третьим входами второго, третьего и четвертого мультиплексоров, выходы компараторов соединены с соответствующими входами шифратора, а его первая выходная шина соединена с входами адресов первого и второго мультиплексоров, вторая выходная шина соединена с входами адресов третьего и третья выходная шина - с входами адресов четвертого и пятого мультиплексоров, входы смещения первого, второго и третьего усилителей соединены, соответственно, с первыми, вторыми и третьими выходами первого и пятого мультиплексоров, выход второго мультиплексора соединен с первым входом первого порогового устройства, второй вход которого соединен с выходом третьего мультиплексора и первым входом второго порогового устройства, второй вход которого соединен с выходом четвертого мультиплексора, причем выходы первого и второго пороговых устройств соединены через первый и второй интеграторы с входами, соответственно, первого и пятого мультиплексоров.

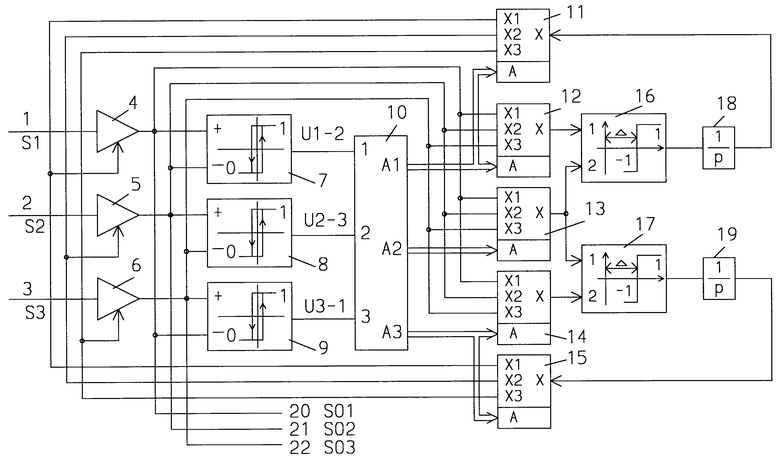

На чертеже приведена блок-схема устройства выбора сигналов.

На чертеже 1, 2, 3 - первый, второй и третий входы устройства, 4, 5, 6 - первый, второй и третий усилители, 7, 8, 9 - первый, второй и третий компараторы, 10 - шифратор, 11, 12, 13, 14, 15 - первый, второй, третий, четвертый и пятый мультиплексоры, 16, 17 - первое и второе пороговое устройство, 18, 19 - первый и второй интеграторы, 20, 21, 22 - первый, второй и третий выход устройства.

Первый вход 1 устройства через первый усилитель 4, второй вход 2 устройства через второй усилитель 5 и третий вход 3 устройства через третий усилитель 6 соединены, соответственно, с первым 20, вторым 21 и третьим 22 выходами устройства и с неинвертирующими входами первого 7, второго 8 и третьего 9 компараторов. Выходы первого 18 и второго 19 интеграторов соединены с входами первого 11 и пятого 15 мультиплексоров, соответственно. Инвертирующие входы первого 7, второго 8 и третьего 9 компараторов подключены к выходам второго 5, третьего 6 и первого 4 усилителей, при этом выходы компараторов соединены с соответствующими входами шифратора 10, а его первая, вторая и третья выходные шины соединены с входами адресов, соответственно, первого 11 и второго 12, третьего 13, четвертого 14 и пятого 15 мультиплексоров. Выход первого усилителя 4 соединен с первыми входами второго 12, третьего 13 и четвертого 14 мультиплексоров, вторые и третьи входы которых соединены с выходами второго 5 и третьего 6 усилителей, соответственно. Входы смещения первого 4, второго 5 и третьего 6 усилителей соединены, соответственно, с первыми, вторыми и третьими выходами первого 11 и пятого 15 мультиплексоров. Выход второго мультиплексора 12 соединен с первым входом первого порогового устройства 16, второй вход которого соединен с выходом третьего мультиплексора 13 и первым входом второго порогового устройства 17, второй вход которого соединен с выходом четвертого мультиплексора 14. Выходы первого 16 и второго 17 пороговых устройств соединены с входами, соответственно, первого 21 и второго 22 интеграторов.

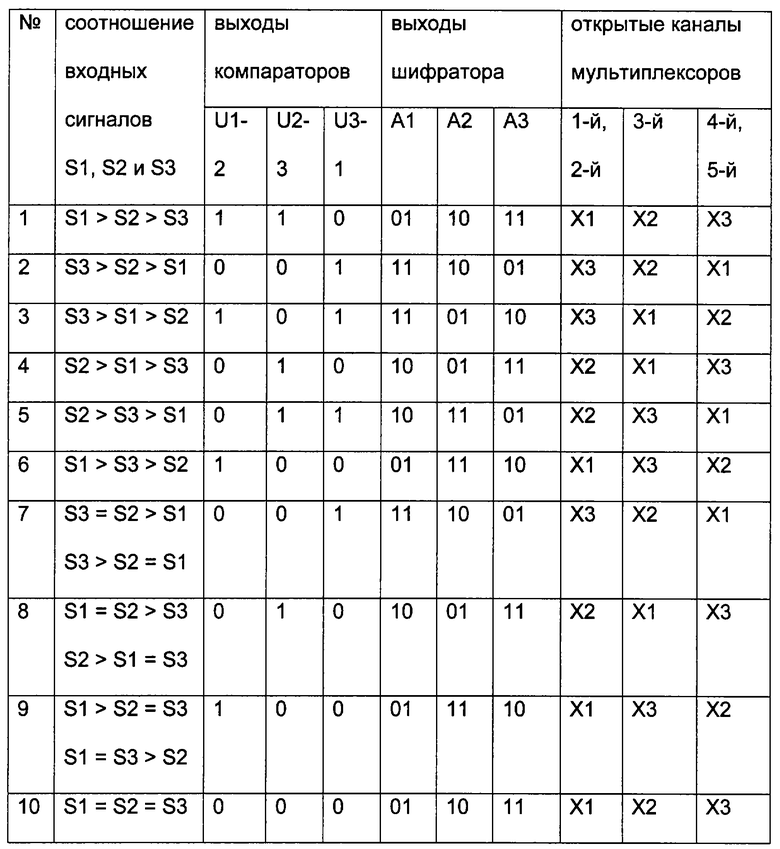

Устройство выбора сигналов работает следующим образом. Входные сигналы S1, S2 и S3, поступающие на входы 1, 2 и 3 устройства, проходят через первый 4, второй 5 и третий 6 усилители соответственно. В результате чего сигнал S1 поступает на неинвертирующий вход первого компаратора 7 и инвертирующий вход третьего компаратора 9, сигнал S2 поступает на неинвертирующий вход второго компаратора 8 и инвертирующий вход первого компаратора 7, сигнал S3 поступает на неинвертирующий вход третьего компаратора 9 и инвертирующий вход второго компаратора 8. Выходные сигналы первого 7, второго 8 и третьего 9 компараторов U1-2, U2-3 и U3-1, соответственно, в зависимости от значений входных сигналов S1, S2 и S3, будут определяться согласно таблице. В этой таблице для каждого соотношения входных сигналов S1, S2 и S3 приведено состояние выходных шин шифратора 10 и указаны открытые каналы мультиплексоров 11-15. При этом низкий уровень сигнала соответствует значению "0", а высокий уровень сигнала - значению "1".

Пусть входные сигналы S1, S2 и S3 соответствуют комбинации 1 таблицы (S1>S2>S3). В этом случае, в соответствии со схемой чертежа, на выходе первого компаратора 7 будет логическая единица (S1>S2, считаем, что |S1-S2|>δ, где δ - гистерезис компаратора 7). На выходе второго компаратора 8 будет логическая единица (S2>S3, считаем, что |S2-S3|>δ, где δ - гистерезис компаратора 8), на выходе третьего компаратора 9 логический ноль (S1>S3), т.е. U1-2= 1, U2-3=1, U3-1=0. Тогда в соответствии со схемой чертежа и таблицей с выхода А1 шифратора 10 на входы адресов первого 11 и второго 12 мультиплексоров будет поступать кодовая комбинация 01, которая откроет каналы Х1-Х данных мультиплексоров, в результате на первом входе первого порогового устройства 16 будет сигнал с выхода первого усилителя 4 (S1). С выхода А2 шифратора 10 на входы адресов третьего 13 мультиплексора будет поступать кодовая комбинация 10, которая откроет канал Х2-Х данного мультиплексора, в результате на выход устройства 23 поступит сигнал с выхода второго усилителя 5 (S2), т. е. средний из сигналов S1, S2 и S3 поступит на второй вход первого порогового устройства 16 и на первый вход второго порогового устройства 17. С выхода A3 шифратора 10 на входы адресов четвертого 14 и пятого 15 мультиплексоров будет поступать кодовая комбинация 11, которая откроет каналы Х3-Х данных мультиплексоров, в результате на втором входе второго порогового устройства 17 будет сигнал с выхода третьего усилителя 6 (S3).

Таким образом, на выходе второго мультиплексора 12 всегда будет сигнал с датчика, имеющего наибольшее значение, на выходе третьего мультиплексора 13 сигнал с датчика, имеющего среднее значение, а на выходе четвертого мультиплексора 14 сигнал с датчика, имеющего наименьшее значение. А значит, на первом входе первого порогового устройства 16 будет наибольший сигнал, на втором входе - средний сигнал, на первом входе второго порогового устройства 17 - средний сигнал, на втором входе - наименьший сигнал. В случае отличия между сигналами большего, чем величина порога, на выходе порогового устройства появится положительное напряжение, в исходном состоянии - отрицательное. В исходном состоянии (входные сигналы S1, S2 и S3 отличаются друг от друга на величину меньшую, чем пороговая) первый 18 и второй 19 интеграторы находятся в насыщении - на их выходах нулевое напряжение. При наличии положительного напряжения на входе первого интегратора 18 на его выходе появится и начнет расти положительное напряжение. Оно через первый мультиплексор 11 поступит на вход смещения усилителя, имеющего наибольший входной сигнал. При наличии положительного напряжения на входе второго интегратора 19 на его выходе появится и начнет расти (по модулю) отрицательное напряжение. Оно через пятый мультиплексор 15 поступит на вход смещения усилителя, имеющего наименьший входной сигнал. Нарастающее (по модулю) напряжение с выходов интеграторов 18, 19 будет поступать на входы смещения усилителей, вызывая "снижение" передаточной характеристики вдоль оси Y первого усилителя 4 и вызывая "подъем" передаточной характеристики вдоль оси Y у третьего усилителя 6. Изменение сигнала на их выходах будет проходить до тех пор, пока разница между сигналами достигнет пороговой величины пороговых устройств 16, 17. В результате передаточные характеристики датчиков, сигналы которых поступают на входы компараторов 7-9, будут сближены. Аналогично работает устройство выбора сигналов и при других комбинациях входных сигналов S1, S2 и S3 (пункты 1-6 таблицы).

Усилители 4-6 должны обладать единичным коэффициентом усиления. А скорость изменения напряжения на выходах интеграторов (их быстродействие) должна быть выше, чем скорость изменения входных сигналов S1, S2 и S3.

В случае совпадения входных сигналов (выполняется одно из неравенств |S1-S2|<δ, |S1-S3|<δ, |S2-S3|<δ) на входах шифратора 10 возможны следующие комбинации - см. пункты 7-9 таблицы. Видно, что в этих случаях на выход третьего мультиплексора 13 будет поступать один из двух равных сигналов. В случае, когда входные сигналы равны S1 = S2 = S3(|S1-S2|<δ,|S1-S3|<δ, |S2-S3|<δ), на входах шифратора 10 будет нулевая комбинация. При этом не имеет существенного значения, какой из входных сигналов S1, S2 или S3 подается на выход мультиплексора 13 и выбирается в качестве среднего. Для определенности можно подавать S2, что и записано в строке 10 таблицы.

При исправной работе источников информации (расхождение между входными сигналами S1, S2 и S3 невелико) на выход устройства информация от всех трех датчиков поступает без изменения, а в случае выхода из строя какого либо источника информации его сигнал корректируется за счет приближения к среднему. При этом выходной сигнал того канала устройства, в котором отказал датчик (источник информации), будет определяться следующим образом. Пусть S1, S2, S3 - входные сигналы устройства. Тогда в случае отказа одного из источников информации возможно всего три варианта соотношений между входными сигналами. Для определенности будем считать, что входные сигналы Si и Sj достоверны, а сигнал Sk неверен, где i, j, k принимают значения из множества {1, 2, 3}, при этом i≠j, j≠k, i≠k. Вариант 1: отказавший датчик имеет наименьшее значение Si>Sj>Sk и Sj-Sk>П. В этом случае на k-ом выходе SOk будет сигнал Sj-П. Вариант 2: отказавший датчик имеет наибольшее значение Sk>Si>Sj и Sk-Si>П. В этом случае на k-ом выходе SOk будет сигнал Si+П. Вариант 3: отказавший датчик имеет среднее значение Si>Sk>Sj. В этом случае на k-ом выходе SOk будет сигнал Sk. При этом величина порога П определяется передаточными характеристиками источников сигналов в его рабочей зоне. Пусть сигнал в исправных каналах Si определяется уравнением вида Si=Ai•X+Ci, где i - номер исправного канала {1, 2}, X - измеряемый параметр (независимый аргумент). А сигнал отказавшего канала Sk = A•sin(ω•X+ϕ), где А, ω, ϕ - переменные величины. В этом случае порог П будет определяться как максимальное значение функции  на рабочем интервале независимого аргумента X. Т. е. сигнал с исправных датчиков проходит через устройство без изменений, а сигнал с отказавшего датчика, в случае его расхождения больше, чем на пороговую величину, "привязывается" к среднему сигналу. Такой выбор порога П необходим для того, чтобы избежать возможного смещения по оси У передаточных характеристик исправных датчиков. Больше данного значения увеличивать порог нет смысла, т.к. этим будет уменьшаться точность восстанавливаемого сигнала.

на рабочем интервале независимого аргумента X. Т. е. сигнал с исправных датчиков проходит через устройство без изменений, а сигнал с отказавшего датчика, в случае его расхождения больше, чем на пороговую величину, "привязывается" к среднему сигналу. Такой выбор порога П необходим для того, чтобы избежать возможного смещения по оси У передаточных характеристик исправных датчиков. Больше данного значения увеличивать порог нет смысла, т.к. этим будет уменьшаться точность восстанавливаемого сигнала.

Учитывая, что у устройства выбора сигналов могут "смещаться" только 2 экстремальные передаточные характеристики, а одна остается неизменной (на вход смещения усилителя не подается сигнал) в устройстве невозможен "уход" по оси У всех характеристик, например, при длительной работе.

Эффект от использования предлагаемого устройства выбора сигналов в том, что оно обладает большей надежностью по сравнению с устройством-прототипом, т. к. имеет три канала передачи сигнала - три входа, три усилителя и три выхода. Оценим надежность известного и предлагаемого решения. При практической реализации оба устройства могут иметь интегральное исполнение. Учитывая статистику отказов аналоговых интегральных устройств, видим, что наиболее часто бывают повреждаемы входные и выходные устройства микросхем. Внутренние логические части микросхем наиболее защищены. Т.е. хотя в предлагаемом решении логическая часть содержит большее количество функциональных элементов, его надежность, практически, равна надежности известного устройства. Поэтому при оценке надежности устройств в составе всей системы обработки информации для известного решения всю систему можно представить как: три источника информации, три входные части, одна логическая часть, один выходная часть и три потребителя информации (система троирована). А для предлагаемого устройства: три источника информации, три входные части, одна логическая часть, три выходных части и три потребителя информации. Считаем, что вероятность безотказной работы источника информации P1, входной части P2, логической части Р3, выходной части Р4, потребителя информации P5. Учитывая, что источников информации, входных частей и логических частей у обоих устройств одинаковое количество, не будем их рассматривать, т.к. они внесут одинаковую ненадежность в оценку. Оставшаяся часть у известного устройства может быть представлена как

Рпрототипа= Р4•[P5 3+3•P5 2•(1-P5)] , где второй сомножитель учитывает вероятность безотказной работы потребителя информации по схеме "два из трех" (т. е. отказ одного не приводит к отказу системы). А у предлагаемого устройства Р=(P4•P5)+3•(P4•P5)2(1-P4•P5), т.е. вероятность выходных устройств и потребителей информации учитывается по схеме "два из трех". Предположим, что P4= 0,95, P5=0,9, тогда, подставляя в приведенные выражения данные значения, получим Рпрототипа=0,923, Р=0,943, т.е. предлагаемое устройство более надежно.

Кроме того, в случае, когда источники сигнала имеют вероятностный характер, например сигнал содержит постоянную составляющую, изменяющуюся от включения к включению, и нет возможности проводить ее предварительную компенсацию, устройство позволяет проводить нормализацию сигналов, приближая их к среднему сигналу, имеющему наиболее вероятное значение. В данном случае наименьшая величина порога пороговых устройств определяется величиной гистерезиса компараторов 7-9. В реальных схемах она будет определяться нелинейной погрешностью передаточных характеристик датчиков.

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства можно использовать операционные усилители, электронные ключи, логические элементы цифровых микросхем любых серий.

Литература

1. Патент США 3706044, кл. G 06 F 11/18, от 29 сентября 1970 г. Analog majority voting circuit.

2. Заявка на изобретение РФ 99113292/09, кл. G 06 G 7/52, от 17.06.1999 г. Устройство выбора среднего сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫБОРА СИГНАЛА | 2001 |

|

RU2208245C2 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО (ВАРИАНТЫ) | 2000 |

|

RU2174703C1 |

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2002 |

|

RU2208796C1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2194999C1 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2000 |

|

RU2173876C1 |

| СПОСОБ ЧАСТОТНО-ИМПУЛЬСНОГО ПРЕОБРАЗОВАНИЯ НЕПРЕРЫВНОГО СИГНАЛА И ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2001 |

|

RU2199757C1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1999 |

|

RU2179320C2 |

| УСТРОЙСТВО ВЫБОРА СРЕДНЕГО СИГНАЛА | 1999 |

|

RU2173878C2 |

| СПОСОБ ЧАСТОТНО-ИМПУЛЬСНОГО ПРЕОБРАЗОВАНИЯ НЕПРЕРЫВНОГО СИГНАЛА И ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2001 |

|

RU2199758C1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2240569C1 |

Предлагаемое изобретение относится к электронной технике и может быть использовано при построении высоконадежных резервированных устройств и систем. Техническим результатом является повышение надежности устройства. Для этого устройство включает три усилителя, три компаратора, шифратор, пять мультиплексоров, два пороговых устройства и два интегратора. 1 табл., 1 ил.

Устройство выбора сигналов, содержащее первый, второй и третий входы, первый, второй и третий компараторы, неинвертирующие входы которых соединены с инвертирующими входами, соответственно, третьего, первого и второго компараторов, отличающееся тем, что в него дополнительно введены первый, второй и третий усилители, шифратор, первый, второй, третий, четвертый и пятый мультиплексоры, первое и второе пороговые устройства, первый и второй интеграторы, при этом первый, второй и третий входы устройства через первый, второй и третий усилители соединены, соответственно, с неинвертирующими входами первого, второго и третьего компараторов, первым, вторым и третьим выходами устройства и первым, вторым и третьим входами второго, третьего и четвертого мультиплексоров, выходы компараторов соединены с соответствующими входами шифратора, а его первая выходная шина соединена с входами адресов первого и второго мультиплексоров, вторая выходная шина соединена с входами адресов третьего и третья выходная шина с входами адресов четвертого и пятого мультиплексоров, входы смещения первого, второго и третьего усилителей соединены, соответственно, с первыми, вторыми и третьими выходами первого и пятого мультиплексоров, выход второго мультиплексора соединен с первым входом первого порогового устройства, второй вход которого соединен с выходом третьего мультиплексора и первым входом второго порогового устройства, второй вход которого соединен с выходом четвертого мультиплексора, причем выходы первого и второго пороговых устройств соединены через первый и второй интеграторы с входами, соответственно, первого и пятого мультиплексоров.

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 1998 |

|

RU2141130C1 |

| RU 95111064 A1, 10.06.1997 | |||

| Устройство для определения средних значений сигналов | 1976 |

|

SU591876A1 |

| Устройство для определения среднего значения | 1982 |

|

SU1140134A2 |

| US 3706044 A, 12.12.1972 | |||

| US 4276648 A, 30.06.1981 | |||

| US 5140594 A, 18.04.1990. | |||

Авторы

Даты

2003-07-10—Публикация

2001-08-07—Подача