Изобретение относится к области электронной техники и может быть использовано для преобразования непрерывного сигнала в частоту в устройствах с высокими требованиями к точности преобразования.

Известен способ частотно-импульсного преобразования непрерывного сигнала, реализованный в [1], основанный на формировании дополнительного сигнала путем интегрирования входного сигнала, компенсации дополнительного сигнала путем интегрирования калиброванного по уровню эталонного сигнала в течение времени от момента достижения дополнительным сигналом заданного значения до момента достижения им нуля.

Недостаток этого способа состоит в низкой точности преобразования и в нелинейной зависимости выходной частоты от входного сигнала.

Известен преобразователь напряжения в частоту, описание которого приведено в [1], содержащий последовательно соединенные интегратор, компаратор, генератор тока, охваченные отрицательной обратной связью на вход интегратора.

Недостаток известного устройства состоит в низкой точности преобразования и в нелинейной зависимости выходной частоты от входного сигнала.

Наиболее близким техническим решением к предлагаемому способу частотно-импульсного преобразования непрерывного сигнала является способ, реализованный в [2], включающий формирование дополнительного сигнала путем интегрирования входного сигнала, компенсацию дополнительного сигнала путем интегрирования калиброванного по уровню и длительности эталонного сигнала.

Недостаток этого способа состоит в том, что при больших значениях входного сигнала не обеспечивается заданная высокая точность.

Известен интегральный преобразователь - прототип, описание которого приведено в [2], содержащий последовательно соединенные интегратор и релейный элемент с гистерезисом, первый и второй управляемые стабилизаторы тока, включенные в цепи отрицательной обратной связи соответственно на первый и второй входы интегратора, третий вход которого соединен со входом интегрального преобразователя.

Недостаток известного устройства состоит в том, что при больших значениях входного сигнала оно не обеспечивает заданной высокой точности.

Задача изобретения - повышение точности частотно-импульсного преобразования непрерывного сигнала за счет формирования эталонного импульсного сигнала разной длительности, зависящей от величины входного сигнала.

Эта задача достигается тем, что способ частотно-импульсного преобразования непрерывного сигнала, включающий формирование дополнительного сигнала путем интегрирования входного сигнала, компенсацию дополнительного сигнала путем интегрирования калиброванного по уровню и длительности эталонного сигнала, отличается тем, что компенсацию дополнительного сигнала осуществляют непрерывно эталонным сигналом, кратным по времени фиксированному интервалу Т0, от момента достижения дополнительным сигналом заданного значения до момента достижения им такого же значения противоположного знака, причем, в эти же моменты изменяют знак эталонного сигнала, а выходной сигнал формируют в виде отношения алгебраической суммы числа интервалов Т0 эталонного сигнала с учетом его знака за промежуток времени между двумя соседними достижениями дополнительным сигналом заданного значения одного и того же знака к этому промежутку времени.

Интегральный преобразователь, содержащий последовательно соединенные интегратор и релейный элемент с гистерезисом, первый и второй управляемые стабилизаторы тока, включенные в цепи отрицательной обратной связи соответственно на первый и второй входы интегратора, третий вход которого соединен со входом интегрального преобразователя, дополнительно содержит первый и второй D-триггеры, первый и второй элементы И, первый и второй элементы НЕ, генератор и блок формирования частотно-импульсного сигнала, первый и второй выходы которого соединены с выходными шинами положительного и отрицательного сигнала соответственно, а первый вход соединен с выходом второго элемента НЕ и первыми входами первого и второго элементов И, второй вход блока формирования частотно-импульсного сигнала соединен с выходом первого элемента И, третий вход соединен с выходом второго элемента И, четвертый вход соединен с выходом первого D-триггера, входом первого управляемого стабилизатора тока и вторым входом второго элемента И, при этом выход релейного элемента с гистерезисом соединен с D-входом второго D-триггера и входом первого элемента НЕ, выход которого соединен с D-входом первого D-триггера, С-вход которого соединен с выходом генератора, С-входом второго D-триггера и входом второго элемента НЕ, выход второго D-триггера подключен ко входу второго управляемого стабилизатора тока и второму входу первого элемента И.

Блок формирования частотно-импульсного сигнала содержит первый и второй реверсивные счетчики, цифровой компаратор, третий и четвертый элементы НЕ, третий и четвертый элементы И, одновибратор и элемент задержки, выход которого соединен с R-входом первого реверсивного счетчика, суммирующий вход которого соединен со вторым входом, а вычитающий вход соединен с третьим входом блока формирования частотно-импульсного сигнала, четвертый вход которого подключен ко входу одновибратора, а первый вход подключен ко вторым входам третьего и четвертого элементов И, первые входы которых соединены с выходом третьего элемента НЕ, соединенного своим входом с выходом А = В цифрового компаратора, входная шина В которого соединена с выходной шиной Q второго реверсивного счетчика, входная шина А подключена к выходу старшего разряда второго реверсивного счетчика, к входу четвертого элемента НЕ и к третьему входу второго элемента И, суммирующий вход второго реверсивного счетчика соединен с выходом четвертого элемента И и вторым выходом блока формирования частотно-импульсного сигнала, вычитающий вход подключен к выходу третьего элемента И и к первому выходу блока формирования частотно-импульсного сигнала, вход РЕ второго реверсивного счетчика соединен с выходом одновибратора и входом элемента задержки, a D-входы соединены с Q выходами первого реверсивного счетчика, выход четвертого элемента НЕ соединен с третьим входом третьего элемента И.

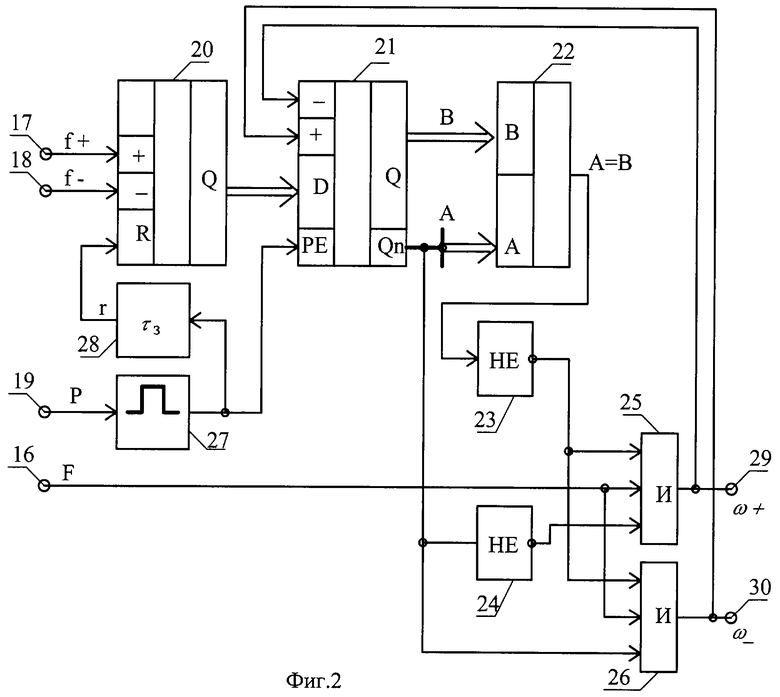

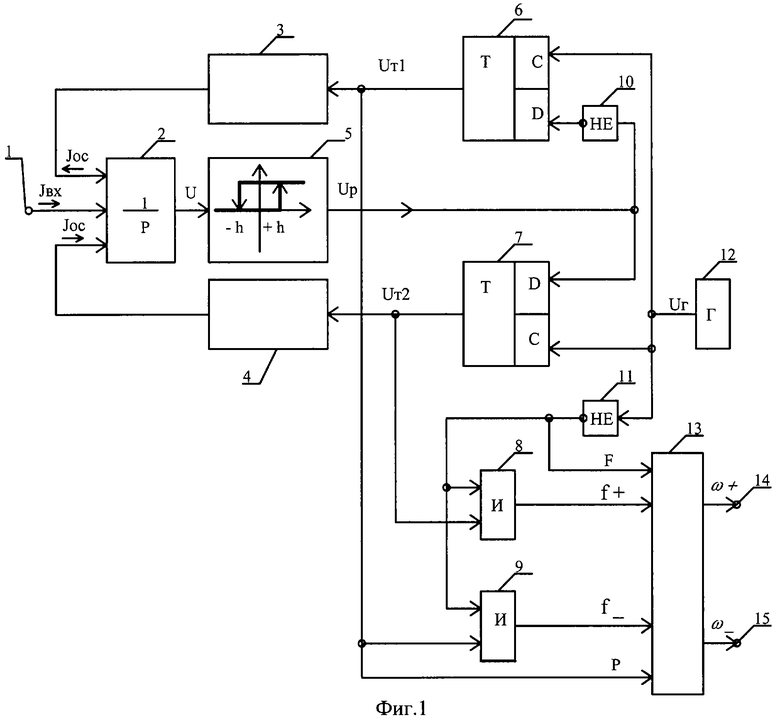

На фиг.1. приведена блок-схема интегрального преобразователя, реализующего предлагаемый способ, на фиг.2. приведена структурная схема блока формирования частотно-импульсного сигнала.

На фиг. 1: 1 - вход интегрального преобразователя, 2 - интегратор, 3 - первый управляемый стабилизатор тока, 4 - второй управляемый стабилизатор тока, 5 - релейный элемент с гистерезисом, 6 - первый D-триггер, 7 - второй D-триггер, 8 - первый элемент И, 9 - второй элемент И, 10 - первый элемент НЕ, 11 - второй элемент НЕ, 12 - генератор, 13 - блок формирования частотно-импульсного сигнала, 14 - выходная шина положительного сигнала, 15 - выходная шина отрицательного сигнала.

На фиг. 2: 16 - первый вход, 17 - второй вход, 18 - третий вход, 19 - четвертый вход, 20 - первый реверсивный счетчик, 21 - второй реверсивный счетчик, 22 - цифровой компаратор, 23 - третий элемент НЕ, 24 - четвертый элемент НЕ, 25 - третий элемент И, 26 - четвертый элемент И, 27 - одновибратор, 28 - элемент задержки, 29 - первый выход, 30 - второй выход.

В интегральном преобразователе вход 1 соединен с третьим входом интегратора 2, первый и второй входы которого соединены с выходом первого 3 и второго 4 управляемых стабилизаторов тока соответственно, выход интегратора 2 соединен со входом релейного элемента с гистерезисом 5, выход которого соединен со входом первого элемента НЕ 10 и D-входом D-триггера 7, С-вход которого соединен с выходом генератора 12, С-входом первого D-триггера 6 и входом второго элемента НЕ 11. Первый вход блока формирования частотно-импульсного сигнала 13 соединен с выходом второго элемента НЕ 11 и первыми входами первого 8 и второго 9 элементов И, второй и третий входы блока формирования частотно-импульсного сигнала 13 соединены с выходами первого 8 и второго 9 элементов И соответственно, четвертый вход соединен с выходом первого D-триггера 6, входом первого управляемого стабилизатора тока 3 и вторым входом второго элемента И 9. Выход второго D-триггера 7 соединен со входом второго управляемого стабилизатора тока 4 и вторым входом первого элемента И 8. Выход первого элемента НЕ 10 соединен с D-входом первого D-триггера 6, первый и второй выходы блока формирования частотно-импульсного сигнала 13 соединены с выходными шинами положительного 14 и отрицательного 15 сигналов.

В блоке формирования частотно-импульсного сигнала 13 первый вход 16 соединен со вторыми входами третьего 25 и четвертого 26 элементов И, второй вход 17 и третий вход 18 соединены с суммирующим и вычитающим входами первого реверсивного счетчика 20 соответственно, четвертый вход 19 соединен со входом одновибратора 27, выход которого соединен со входом элемента задержки 28 и РЕ-входом второго реверсивного счетчика 21, D-входы которого соединены с Q-выходами первого реверсивного счетчика 20, суммирующий вход соединен с выходом четвертого элемента И 26 и вторым выходом 30, вычитающий вход соединен с выходом третьего элемента И 25 и первым выходом 29, выходная шина Q второго реверсивного счетчика 21 соединена со входной шиной В цифрового компаратора 22, входная шина А которого подключена к выходу старшего разряда второго реверсивного счетчика 21, ко входу четвертого элемента НЕ 24 и третьему входу четвертого элемента И 26. Выход А = В цифрового компаратора 22 соединен со входом третьего элемента НЕ 23, выход которого соединен с первыми входами третьего 25 и четвертого 26 элементов И. Выход четвертого элемента НЕ 24 соединен с третьим входом третьего элемента И 25, выход элемента задержки 28 соединен с R-входом первого реверсивного счетчика 20.

Интегральный преобразователь работает следующим образом. Пусть непрерывный сигнал (входной ток) IВХ увеличивается от нуля. В этом случае выходной сигнал U (дополнительный сигнал) интегратора 2 начнет увеличиваться, при U=h срабатывает релейный элемент с гистерезисом 5 и его выходной сигнал UР = 1 поступает на D-вход второго D-триггера 7. Импульсом с генератора 12 второй D-триггер 7 переводится в единичное состояние, его выходной сигнал UТ2=1 включает второй управляемый стабилизатор тока 4, который подключает ток обратной связи IОС (эталонный сигнал) ко второму входу интегратора 2. Ток IОС компенсирует дополнительный сигнал U и выбирается из условия IОС > IBX.MAX, где IBX.MAX - максимально возможное значение входного тока. Так как IOC > IBX, то выходной сигнал U интегратора 2 начнет уменьшаться до значения U = -h. В течение всего этого времени второй D-триггер 7 находится в единичном состоянии и его выходной сигнал, поступая на второй вход первого элемента И 9, открывает его для прохождения импульсов генератора 12 с выхода второго элемента НЕ 11, подключенного своим выходом к первому входу первого элемента И 8, выходные импульсы f+ которого поступают на второй вход блока формирования частотно-импульсного сигнала 13. Формирование выходных сигналов ω+ с первого выхода и сигналов ω- со второго выхода блока формирования частотно-импульсного сигнала 13 будет рассмотрено ниже.

При U = -h переключается релейный элемент 5 и его выходной сигнал Up = 0 поступает на вход первого элемента НЕ 10, единичный выход которого подается на D-вход первого D-триггера 6. Импульсом с генератора 12 первый D-триггер 6 переводится в единичное состояние, его выходной сигнал UТ1 = 1 включает первый управляемый стабилизатор тока 3, который подключает ток обратной связи IОС к первому входу интегратора 2, после чего его выходной сигнал U начинает увеличиваться до значения U = h. В течение всего этого времени первый D-триггер 6 находится в единичном состоянии и его выходной сигнал, поступая на второй вход второго элемента И 9, открывает его для прохождения импульсов генератора 12 с выхода второго элемента НЕ 11, подключенного своим выходом к первому входу второго элемента И 9, выходные импульсы f_ которого поступают на третий вход блока формирования частотно-импульсного сигнала 13. Так как IBX > 0, то время Т1 включенного состояния первого D-триггера 6 больше времени Т2 включенного состояния второго D-триггера 7, причем, Т1 и Т2 связаны соотношением

Если Т0 - период следования импульсов генератора 12, то Т1=n1Т0, Т2= n2Т0, где n1 и n2 - число импульсов генератора 12 соответственно за время T1 и Т2. Считаем, что за время (Т1+Т2) входной сигнал IBX остается неизменным, тогда из (1)

IBX=IOC (T1-T2)/(T1+T2) (2)

Иначе говоря, входной сигнал за время (T1+T2) определяется временем (T1-T2) или числом импульсов (n1-n2). Рассмотрим формирование выходного сигнала блоком формирования частотно-импульсного сигнала 13.

Блок формирования частотно-импульсного сигнала 13 (фиг. 2) работает следующим образом. На вход блока 13 поступают сигналы: на первый вход 16 - сигнал с выхода второго элемента НЕ, инвертирующего сигналы генератора 12 (фиг. 1) и обеспечивающего формирование импульса обнуления первого реверсивного счетчика 20 и импульса записи РЕ во второй реверсивный счетчик 21 в моменты отсутствия импульсов f+ и f_ на суммирующем и вычитающем входах первого реверсивного счетчика 20, на второй вход 17 - сигналы f+ с выхода первого элемента И 8, определяющие длительность Т2 (или число импульсов n2), на третий вход 18 - сигналы f_ с выхода второго элемента И 9, определяющие длительность Т1 (или число импульсов n1), на четвертый вход 19 - сигнал с выхода первого D-триггера 6, характеризующий начало периода (T1+T2). Сигналы f+ и f_ поступают на суммирующий и вычитающий входы первого реверсивного счетчика 20 и суммируются в нем до момента поступления на его R-вход импульса обнуления r с выхода элемента задержки 28. При переходе первого D-триггера 6 в единичное состояние (фиг.1) его выходной сигнал UT1 = 1 поступает на вход 19 (фиг.2) и одновибратор 27 формирует импульс, который поступает на вход РЕ второго реверсивного счетчика 21, осуществляя запись выходных сигналов Q первого реверсивного счетчика 20 по входам D во второй реверсивный счетчик 21, после чего элемент задержки 28 формирует сигнал сброса r на вход R первого реверсивного счетчика 20. Сигнал сброса r формируется один раз по началу периода (T1+T2), следовательно, в момент формирования импульса записи РЕ в первом реверсивном счетчике 20 содержится информация (n1-n2), характеризующая входной сигнал IВХ. С этого момента времени сигнал В с выходов Q второго реверсивного счетчика 21 не равен нулю (В≠0), а сигнал Qn с выхода старшего разряда второго реверсивного счетчика 21 равен нулю (А=0), иначе, на входных шинах цифрового компаратора 22 образуется состояние, соответствующее условию А≠В. В этом случае выходной сигнал цифрового компаратора А=В равен нулю и выходной сигнал третьего элемента НЕ 23 имеет высокий уровень. Так как сигнал Qn=0, то выходной сигнал четвертого элемента НЕ 24 имеет высокий уровень. На первом входе третьего элемента И 25 высокий уровень, на третьем входе также высокий уровень и импульсы F, поступающие на второй вход третьего элемента И 25, появляются на выходе ω+ этого элемента и поступают на первый выход 29 и вычитающий вход второго реверсивного счетчика 21. Такое состояние будет сохраняться до тех пор, пока на шине В цифрового компаратора 22 не образуется сигнал В=0 (второй реверсивный счетчик 21 произведет вычитание (n1-n2) импульсов). В результате на входе цифрового компаратора 22 образуется состояние А=В и на выходе А=В этого компаратора образуется высокий уровень, а на выходе третьего элемента НЕ 23 низкий уровень, который блокирует прохождение сигналов F на выход третьего элемента И 25 и счет импульсов вторым реверсивным счетчиком 21 прекращается.

Таким образом, на первом выходе 29 формируется (n1-n2) импульсов, соответствующих положительному значению входного сигнала IBX. Выходной сигнал ω+ интегрального преобразователя определяется выражением

ω+=(n1-n2)/(Т1+Т2). (3)

Процесс формирования выходных сигналов ω+ и ω- будет продолжен после поступления очередного сигнала Р = 1 на четвертый вход 19. В случае отрицательного входного сигнала IВХ < 0 выходной код Q первого реверсивного счетчика 20 отрицателен (Qn=1) и в этом случае по уже описанной схеме четвертый элемент И 26 будет формировать выходные сигналы ω- на втором выходе 30, соответствующие отрицательному значению входного сигнала IВХ.

Эффект от использования предлагаемого изобретения состоит в повышении точности. Оценим точность предлагаемого изобретения. Как следует из (2), точность преобразования зависит от точности задания двух параметров: тока обратной связи IОС и точности формирования интервалов Т1 и Т2 (от стабильности генератора 12). Однако в случае высокой частоты переключения тока обратной связи IОС существенным моментом, влияющим на точность преобразования, является быстродействие элементов, участвующих в формировании тока IОС в течение интервалов Т1 и Т2. В устройстве-прототипе эти интервалы всегда равны Т0. Пусть, например, входному току IMAX=10 мА соответствует частота 100 кГц. В этом случае в устройстве-прототипе интервал Т0≤10 мкс. Если, например, по каким-либо причинам (например от температуры) произойдет изменение фронта в формировании интервала Т0 на ΔТ=10 нc, то относительная погрешность δ1 преобразования будет равна ΔТ/Т0=0,001, что соответствует 0,1%. В предлагаемом изобретении относительная погрешность преобразования δ2 оценивается в виде

δ2 = 2ΔT/(T1-T2), (4)

так как за время (Т1+Т2) формируются два импульса тока IОС длительностью Т1 и Т2.

Выберем в предлагаемом изобретении h=5 IОС Т0. При входном токе IBX=6 мА и IОС= 12 мА Т1=20 Т0, Т2=6 Т0. Погрешность преобразования δ2 предлагаемого изобретения будет равна 2 ΔТ/(Т1-Т2)= 0,00014, что соответствует 0,014%. Таким образом, точность предлагаемого изобретения значительно выше точности известного решения. Следует также отметить, что в предлагаемом изобретении с увеличением входного сигнала относительная погрешность δ2 уменьшается, что непосредственно следует из (3) и имеет существенное положительное значение.

Предлагаемая совокупность признаков в рассмотренных автором решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства могут быть использованы логические элементы И, НЕ, триггеры, реверсивные счетчики, цифровой компаратор, одновибраторы, элементы задержки любых серий, например, серии 564, стандартные интеграторы, стабилизаторы тока, кварцевые генераторы.

Литература

1. Авторское свидетельство СССР 921080, кл. Н 03 К 13/20 от 24.07.81. Преобразователь напряжения в частоту.

2. Патент Российской Федерации 2138826, кл. G 01 R 19/252 от 29.09.99. Интегральный преобразователь.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2194999C1 |

| СПОСОБ ЧАСТОТНО-ИМПУЛЬСНОГО ПРЕОБРАЗОВАНИЯ НЕПРЕРЫВНОГО СИГНАЛА И ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2001 |

|

RU2199758C1 |

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2001 |

|

RU2194997C1 |

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2001 |

|

RU2208797C1 |

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2002 |

|

RU2208796C1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2240568C1 |

| СПОСОБ ЦИФРОВОЙ ФИЛЬТРАЦИИ СИГНАЛОВ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2000 |

|

RU2187883C2 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2240569C1 |

| ИНТЕГРАЛЬНЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2325664C2 |

| УСТРОЙСТВО ВЫБОРА СИГНАЛОВ | 2001 |

|

RU2208246C2 |

Использование: для преобразования непрерывного сигнала в частоту с высокими требованиями к точности преобразования. Технический результат заключается в повышении точности преобразования входного сигнала и уменьшении относительной погрешности при его возрастании. Способ частотно-импульсного преобразования непрерывного сигнала основан на формировании дополнительного сигнала путем интегрирования непрерывного сигнала и непрерывной компенсации дополнительного сигнала путем интегрирования калиброванного по уровню и длительности эталонного сигнала от момента достижения дополнительным сигналом заданного значения до момента достижения им такого же значения противоположного знака и формировании выходного частотно-импульсного сигнала по результату вычитания соседних интервалов между указанными достижениями заданных значений. Интегральный преобразователь, реализующий предлагаемый способ, содержит интегратор, релейный элемент с гистерезисом, управляемые стабилизаторы тока, генератор, D-триггеры, блок формирования частотно-импульсного сигнала, который преобразует результат сравнения времени нахождения в единичном состоянии D-триггеров в выходной частотно-импульсный сигнал. 2 c. и 1 з.п. ф-лы, 2 ил.

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2138826C1 |

| Преобразователь напряжения в частоту | 1980 |

|

SU921080A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-ЧАСТОТА | 0 |

|

SU394938A1 |

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1999 |

|

RU2160960C1 |

| ЭЛЕКТРОНАСОСНЫЙ АГРЕГАТ ВЕРТИКАЛЬНОГО ТИПА (ВАРИАНТЫ) | 2013 |

|

RU2506463C1 |

| US 4931921 A, 05.06.1990. | |||

Авторы

Даты

2003-02-27—Публикация

2001-07-12—Подача