Область техники, к которой относится изобретение

Изобретение относится к асинхронному устройству обработки данных и более конкретно - к технике, позволяющей асинхронному устройству обработки данных работать с улучшенным энергетическим кпд.

Уровень техники

Устройство обработки данных, такое как микропроцессор, обычно реализуют с использованием синхронной архитектуры, поскольку общепринято считать, что она более простая относительно асинхронной архитектуры. Синхронные микропроцессоры работают под управлением направляемого извне сигнала синхронизации, в то время как асинхронные микропроцессоры должны быть самосинхронизирующимися и работать без направляемого извне синхросигнала. Отсутствие направляемого извне синхросигнала усложняет проектирование микропроцессора. Например, проектировщик должен учитывать, как надо управлять потоком данных в отсутствие опорного генератора синхросигналов, а задержки элементов обработки должны измеряться самой схемой вместо того, чтобы их просто моделировать по периоду синхросигнала.

Но микропроцессоры синхронных архитектур не обладают надлежащим энергетическим кпд. Синхросигнал в синхронной схеме генерируется постоянно, в результате чего в схеме происходят переходы, рассеивающие электроэнергию. Частоту синхросигнала надо задавать такой величины, чтобы процессор смог справляться с пиковой нагрузкой, и, несмотря на то, что частоту синхросигналов можно регулировать под управлением средств программного обеспечения сообразно с изменяющимися требованиями, это можно осуществлять только относительно грубо и с низкой глубиной детализации. Поэтому синхросигнал большей частью имеет более высокую частоту, чем требуется для обеспечения текущей рабочей нагрузки, и в результате этого происходит потеря мощности.

Поэтому требуется микропроцессор с улучшенным энергетическим кпд.

Сущность изобретения

Соответственно, данное изобретение обеспечивает устройство для обработки данных, содержащее множество асинхронных схем управления, причем каждая асинхронная схема управления использует цикл управления запросом-подтверждением для управления потоком данных в этой асинхронной схеме управления, при этом она выполнена с возможностью обмена сигналами данных по меньшей мере с одной другой схемой из указанного множества асинхронных схем управления; при этом первая из указанных асинхронных схем управления содержит остановочную схему для блокирования сигнала управления в цикле управления первой асинхронной схемы управления, тем самым предотвращая обмен сигналами данных с указанной по меньшей мере одной другой схемой из указанного множества асинхронных схем управления, чтобы обусловить блокирование циклов управления указанного множества асинхронных схем управления.

Данное изобретение обеспечивает устройство, основанное на асинхронной архитектуре. Асинхронная архитектура обусловливает переходы в схеме только при реагировании на запрос о выполнении полезной работы. Она может мгновенно включаться между нулевым рассеянием электроэнергии и максимальными рабочими характеристиками по требованию. Поскольку многие встроенные прикладные задачи имеют быстроизменяющуюся рабочую нагрузку, обнаружено, что асинхронный процессор дает возможность значительно экономить энергию.

Большинство микропроцессоров проектируют как схему КМОП-структуры, и КМОП-схемы обычно потребляют очень незначительное количество энергии, если дезактивированы все функции. Поскольку большинство микропроцессоров известного уровня техники - асинхронные и поэтому используют свободно идущие синхросигналы, они не могут без труда управлять своими действиями; и когда программа не имеет больше подлежащей выполнению полезной работы, средства программного обеспечения обычно переходят в непрерывный цикл, при этом либо не выполняя какой-либо работы, либо опрашивая периферийное устройство, пока не поступит входной сигнал. Оба этих решения представляют собой непрерывное действие в схеме и рассеивают значительное количество энергии, при этом не выполняя какой-либо полезной работы или выполняя ее в очень малом объеме, пока не возникнет прерывание или пока периферийное устройство не получит входной сигнал. Асинхронный процессор, который выполняет ту же программу, также будет тратить энергию, не выполняя какой-либо работы.

Данное изобретение решает эту проблему за счет введения "остановочной" схемы, которая обусловливает прекращение всех действий процессора, пока не произойдет прерывание. Эта схема работает путем перехвата сигнала управления в асинхронных схемах управления устройства обработки данных и путем эффективного размыкания единого цикла управления запросом-подтверждением. Поскольку схемы управления взаимосвязаны, блокировка сигнала управления в одном цикле (но не сразу) останавливает все другие циклы управления в устройстве, и поэтому остановка, в конечном счете, распространяется на все устройство целиком, прекращая всякие действия. Предпочтительно, чтобы прерывание использовалось для отмены остановки в первоначальном цикле управления и чтобы затем действия распространялись от этой точки по всей системе.

Поэтому данное изобретение применяет нечувствительный к задержке характер асинхронных схем управления в устройстве обработки данных в целях осуществления остановки на одной точке управления в цикле управления одной из схем управления с последующим распространением остановки по всей системе.

Предпочтительно выполнение остановочной схемы с возможностью блокирования сигнала запроса, формируемого циклом управления запросом-подтверждением, но специалистам данной области будет очевидно, что остановочную схему можно также вместо этого выполнить с возможностью блокирования сигнала подтверждения вместо сигнала запроса.

В предпочтительных вариантах реализации первую асинхронную схему управления выполняют с возможностью исполнения команд, и устройство также содержит схему сравнения для сравнения исполняемых команд с заранее определенной командой, указывающей, что цикл управления первой асинхронной схемы управления надо блокировать. Схему сравнения предпочтительно включают в декодер команд устройства обработки данных, но ее можно поместить и в другом месте в устройстве. В предпочтительных осуществлениях заранее заданной командой является команда ветвления для ветвления в текущую команду. Но специалистам данной области будет очевидно, что для блокировки и разблокировки циклов управления асинхронных схем управления можно применить другие решения и что использование таковой команды ветвления не имеет существенного значения.

Предпочтительно, чтобы остановочная схема содержала первую логическую схему, имеющую входы для приема одного или более сигнала прерывания и остановочного сигнала, формируемого схемой сравнения и указывающего, что исполняемая команда согласуется заранее определенной командой. При этом первая логическая схема может иметь вход для приема сигнала исполнения, который используют для подтверждения того, что сигнал управления в цикле управления первой асинхронной схемы управления надо блокировать. Сигнал исполнения используют в предпочтительных вариантах реализации по той причине, что, например, остановка цикла управления может зависеть от результата предыдущей исполненной команды. В этом случае сигнал исполнения будут направлять в том случае, если результат предыдущей команды показал, что цикл управления нужно остановить. Помимо этого, предыдущая команда может быть командой ветвления, и в этом случае остановочную команду не следует исполнять, а сигнал исполнения соответственно устанавливают на "недействующий".

Первую логическую схему можно выполнить любым соответствующим образом, но в предпочтительных осуществлениях первая логическая схема является вентилем И-НЕ для выведения логического значения 0, когда все входные сигналы имеют значение логической 1; один или более сигналов прерывания имеют логическую 1 в недействующем состоянии, а остальные входные сигналы имеют значение логической 1 в действующем состоянии.

Остановочная схема предпочтительно также содержит вторую логическую схему, имеющую входы для приема сигнала запроса цикла управления запроса-подтверждения и выходного сигнала первой логической схемы, причем выход второй логической схемы подключают к независимому получателю для сигнала запроса. В предпочтительных осуществлениях второй логической схемой является вентиль И и поэтому его выполняют с возможностью не выводить сигнал запроса, если выходной сигнал первой логической схемы имеет значение логического 0. Специалистам данной области будет очевидно, что для выполнения логических схем остановочной схемы можно использовать любое другое соответствующее выполнение логических вентилей.

В предпочтительных вариантах реализации данного изобретения сигнал прерывания используют для разблокировки сигнала управления, блокированного остановочной схемой, тем самым обеспечивая возможность обмена сигналами данных между схемами управления и таким образом обусловливая разблокировку циклов управления.

При этом в предпочтительных вариантах реализации циклы управления запросом-подтверждением используют протокол связи уровневого сигнализирования.

В соответствии с предпочтительными осуществлениями множество асинхронных схем управления включают в себя совокупность взаимодействующих асинхронных конвейеризованных схем.

Устройство обработки данных согласно данному изобретению может иметь любую надлежащую форму, но в предпочтительных осуществлениях это устройство является микропроцессором.

С другой стороны, данное изобретение обеспечивает способ обработки данных в устройстве обработки данных, включающий в себя следующие этапы: обеспечение множества асинхронных схем управления для обработки данных, причем каждая асинхронная схема управления использует цикл управления запросом-подтверждением для управления потоком данных в этой асинхронной схеме управления и выполнена с возможностью обмена сигналами данных по меньшей мере с одной другой схемой из указанного множества асинхронных схем управления; при реагировании на соблюдение заранее определенного условия - блокирования сигнала управления в цикле управления первой схемы из числа указанных асинхронных схем управления, тем самым предотвращая обмен сигналами данных с указанной по меньшей мере одной другой схемой из указанного множества асинхронных схем управления, чтобы осуществилась блокировка циклов управления указанного множества асинхронных схем управления.

Краткое описание чертежей

Реализация данного изобретения излагается только в качестве примера со ссылкой на чертежи, на которых аналогичные ссылочные обозначения используют для аналогичных признаков и в которых:

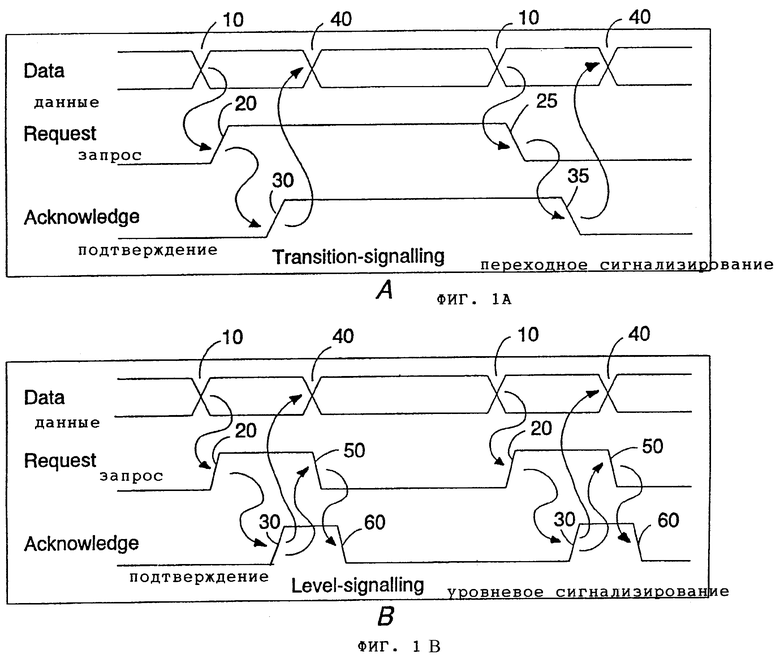

фиг. 1А и 1В - схемы двух разных протоколов связи, которые можно применить для управления потоком данных в асинхронном микропроцессоре;

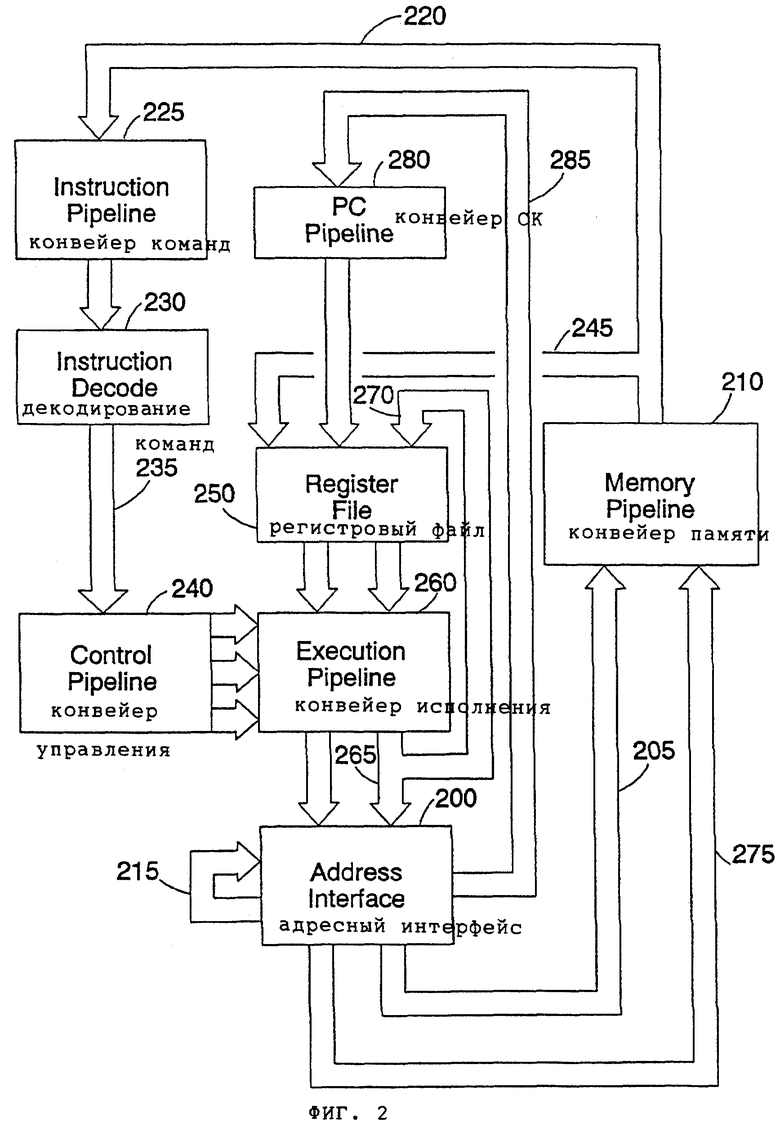

фиг. 2 - блок-схема структуры оперативной памяти процессора в соответствии с предпочтительным вариантом реализации данного изобретения;

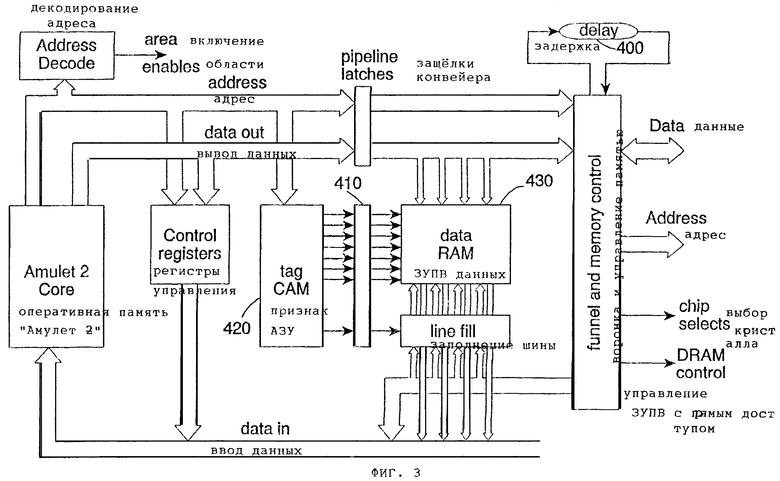

фиг. 3 - схема внутренней организации кристалла, содержащего оперативную память процессора предпочтительного варианта реализации в дополнение к части памяти;

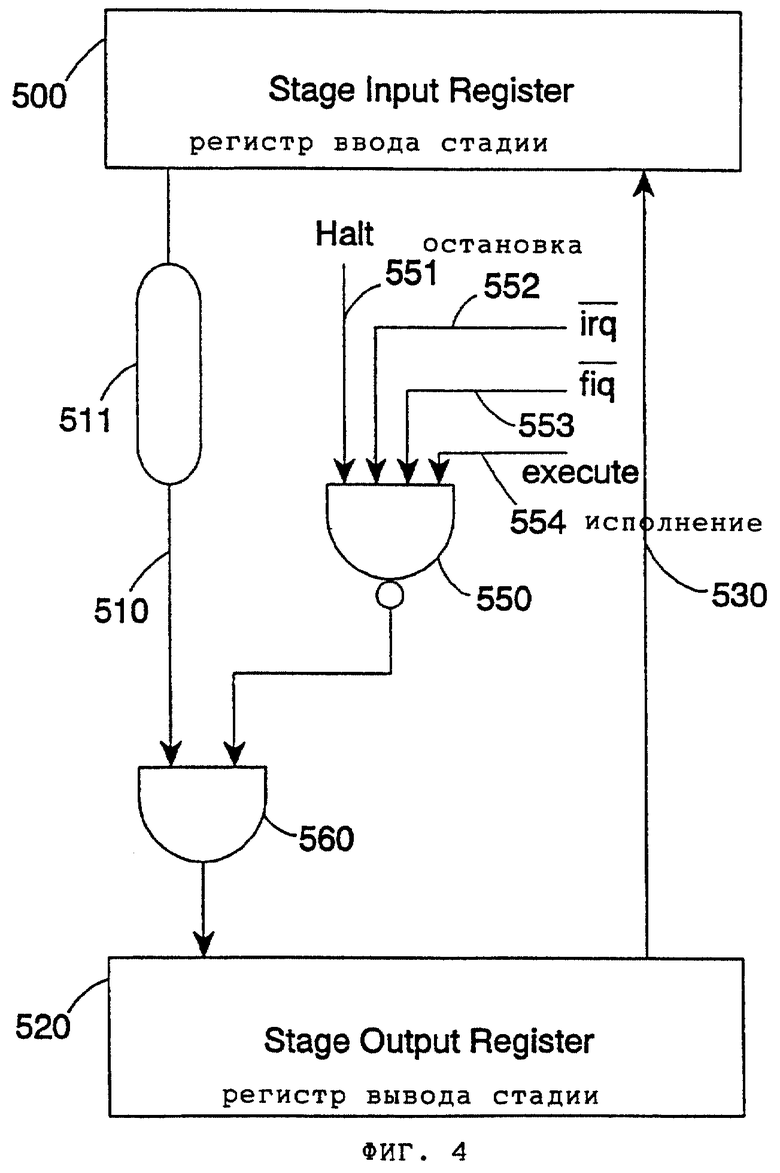

фиг. 4 - принципиальная схема логических компонентов, используемых для блокирования и разблокирования цикла запроса-подтверждения в асинхронной схеме управления в соответствии с предпочтительным вариантом реализации данного изобретения.

Описание предпочтительного варианта реализации изобретения

Перед подробным описанием структуры микропроцессора в соответствии с предпочтительным осуществлением далее будут изложены некоторые основные сведения об асинхронном конструировании.

Асинхронное проектирование является комплексной и многогранной дисциплиной, имеющей много разных подходов к решению ее задач. Необходимо обеспечить методику для управления потоком данных в отсутствие какого-либо опорного синхросигнала. Процессор в соответствии с предпочтительным вариантом реализации для управления потоком данных использует формы квитирования установления связи типа "запрос-подтверждение". Последовательность действий, содержащая сообщение данных от отправителя к получателю, следующая:

1) отправитель помещает на шину действительное значение данных;

2) отправитель затем направляет событие "Запрос";

3) получатель принимает данные, когда он готов к этому;

4) получатель направляет событие "Подтверждение" отправителю; и

5) отправитель затем может убрать данные с шины и начать следующее сообщение, когда он будет готов к этому.

Данные направляют по шине с помощью обычного двоичного кодирования, но "Запросом" и "Подтверждением" можно обмениваться несколькими способами. Одно из решений заключается в использовании "переходного сигнализирования", в котором изменение в уровне сигнала (либо с высокого на низкий, или наоборот) является событием. Фиг. 1А изображает протокол связи с помощью переходного сигнализирования. В соответствии с фиг.1А: после того, как отправитель поместил действительное значение данных на шину (указано переходом 10), он затем направляет событие запроса, указываемое переходом с низкого на высокий 20. Получатель затем считывает данные с шины и направляет событие подтверждения к отправителю - указано переходом 30 на фиг.1А. После того, как отправитель получил это событие подтверждения, он может затем убрать данные с шины - указано переходом 40. В соответствии с изображением в правой стороне фиг.1А эта последовательность этапов затем повторяется для последующих значений данных. Согласно фиг.1А изменение в уровне с высокого на низкий 25, 35 также указывает направление запроса и событие подтверждения.

Другое решение для сигнализирования событий запроса и подтверждения заключается в использовании протокола связи уровневого сигнализирования согласно фиг. 1В, в котором фронт сигнализирует событие, а фаза возвращения к нулю должна произойти до того, как можно будет просигнализировать следующее сообщение. Когда действительное значение данных помещают согласно фиг.1В на шину (переход 10), событие запроса направляется отправителем при переходе 20, и по получении значения данных получатель направляет событие подтверждения при переходе 30. Как и в протоколе связи переходного сигнализирования, отправитель тогда может убрать значение данных с шины при переходе 40. Но кроме этого, по получении события подтверждения отправитель убирает событие запроса - указано переходом с высокого на низкий 50; и тогда получатель убирает событие подтверждения - указано переходом с высокого на низкий 60. Эта последовательность событий затем повторяется для следующего значения данных, помещенного на шину.

Согласно фиг.1А и 1В переходное сигнализирование является концептуально более ясным, так как каждый переход играет свою роль, и поэтому его синхронизация определяется функцией схемы. Это сигнализирование также использует минимальное число переходов и поэтому должно быть эффективным с точки зрения энергетического кпд. Но используемые для управления переходом КМПОП-структуры - относительно медленные и неэффективные, и поэтому в предпочтительном варианте реализации данного изобретения процессор использует протокол связи уровневого сигнализирования, который использует более быстродействующие и энергосберегающие схемы, несмотря на удвоенное число переходов, но оставляет в некоторой степени произвольные решения, принимаемые в отношении синхронизации фаз восстановления (возвращения к нулю) в протоколе.

С помощью указанной методики самосинхронизации возможно спроектировать блок асинхронной конвейеризованной обработки данных для учета задержки обработки данных на каждой стадии и одном из указанных протоколов, чтобы отослать результат на следующую стадию. Соответствующее проектирование может учесть разнообразные задержки в обработке данных и произвольные внешние задержки; главное заключается в местном упорядочении событий, хотя, разумеется, длительные задержки будут иметь своим результатом низкие рабочие характеристики.

В противоположность синхронному конвейеру, используемому в синхронном процессоре, когда весь конвейер нужно всегда синхронизировать на скорости, определяемой самой медленной стадией в наихудших условиях окружающей среды (напряжение и температура), и исходя из данных наихудшего случая - асинхронный конвейер будет работать с изменяющейся скоростью, определяемой текущими условиями. Можно допустить редко случающиеся условия наихудшего случая, чтобы блок обработки данных срабатывал немного медленнее. В этих случаях при таких условиях возникнет некоторая потеря в рабочих характеристиках, но поскольку такие случаи достаточно редки, то их влияние на общие рабочие характеристики будут незначительными.

После приведенного выше изложения методики самосинхронизации для управления асинхронным конвейеризованным блоком обработки данных далее следует подробное изложение оперативной памяти процессора (оперативная память представляет собой часть процессора, которую используют для выполнения общих функций обработки данных) в соответствии с предпочтительным вариантом реализации данного изобретения и со ссылкой на фиг.2, которая является блок-схемой структуры оперативной памяти процессора. Его структура основана на совокупности взаимодействующих асинхронных конвейеров, каждый из которых работает в своем собственном временном режиме с присущей ему скоростью. Эти конвейеры могут вносить в процессор недопустимо длительные задержки, но в противоположность синхронным конвейерам асинхронный конвейер может иметь очень небольшую задержку, так как конвейер не зависит от циклов синхросигнала и поэтому может работать в своем присущем ему темпе.

Работа процессора начинается с адресного интерфейса 200, который выдает запросы выборки команды в память 210 по тракту 205. Адресный интерфейс 200 имеет независимое устройство приращения адреса, которое дает ему возможность производить предварительную выборку команд настолько заблаговременно, насколько это позволяют емкости различных конвейерных буферов. Это логическое устройство приращения для определения следующего адреса изображено трактом-ветвью 215. После того, как конвейер памяти сделал выборку команды, команду направляют по тракту 220 в конвейер команд 225. Здесь команды запоминают в конвейерном порядке для направления их в логическую схему декодирования команд 230. После декодирования команд декодером 230 их направляют по тракту 235 в конвейер управления 240.

Кроме выдачи запросов на выборку команд, адресный интерфейс также направляет запросы данных в память 210. После выборки данных значения данных считывают в регистровый файл 250 через тракт 245. Затем исполнительная схема конвейера 260 считывает команды из конвейера управления 240 и исполняет эти команды, исходя из значений данных, считанных из регистрового файла 250. Результаты исполнения направляют в адресный интерфейс 200 по тракту 265 и их также можно вернуть в регистровый файл 250 по тракту 270. По получении результатов из конвейера исполнения адресный интерфейс 200 направляет результаты в конвейер памяти 210 по тракту 275 для запоминания в памяти.

Когда адресный интерфейс 200 направляет запросы на выборку команд в память 210, он направляет значения счетчика команд (СК), запрошенных по тракту 285, в конвейер СК 280. Оттуда значения СК можно считать в регистр СК, содержащийся в регистровом файле 250, где их можно использовать в качестве операндов посредством исполняемых ими команд. Конвейер СК нужен для запоминания значений СК, соответствующих значениям в конвейере памяти, чтобы каждая команда была бы соотнесена с правильным значением СК в соответствии с тем, как это определено структурой системы команд.

Адресный интерфейс 200 можно выполнить с возможностью предварительной выборки команд последовательно из текущего значения СК, и тогда все отклонения от последовательного исполнения будут направляться в качестве корректировок от конвейера исполнения в адресный интерфейс.

В предпочтительных вариантах реализации данного изобретения оперативную память процессора можно совместить с частью памяти, например 4 килобайтами памяти; при этом эту часть можно сконфигурировать либо как кэш-память, либо как фиксированную зону ЗУПВ и гибкий интерфейс памяти ("воронка"), что даст возможность непосредственно подключать 8-, 16- или 32-разрядные внешние устройства, включая памяти, выделенные из ЗУПВ с прямым доступом. Внутренняя организация кристалла, включающего в себя оперативную память процессора в соответствии с предпочтительным вариантом реализации данного изобретения и 4 килобайта памяти, изображены на фиг.3.

По причине отсутствия опорного синхросигнала в асинхронной системе обработки данных вопрос синхронизированной выборки из памяти имеет особое значение. В соответствии с предпочтительным вариантом реализации соответствующее предусматриваемое в кристалле процессора решение заключается в использовании единой внешней опорной задержки 400, подключаемой непосредственно к кристаллу и регистрам конфигурации и загружаемой во время пуска и определяющей характеристики организации и синхронизации в каждой области памяти. Опорная задержка обычно отражает время доступа внешней СЗУПВ, и поэтому ЗУПВ будет конфигурировано таким образом, чтобы принимать одну опорную задержку. ПЗУ, которое обычно работает гораздо медленнее, можно конфигурировать с принятием нескольких опорных задержек. Нужно отметить, что опорную задержку используют только для синхронизации вне кристалла, а все задержки на кристалле являются самосинхронизирующимися.

4 килобайта памяти предпочтительно конфигурировать в виде кэш-памяти, содержащей четыре блока по 1 килобайту; при этом каждый из этих блоков является полностью ассоциативным запоминающим устройством произвольной замены на числовую шину кварцевой линии задержки и размер блока. Конвейеризованный регистр 410 между секциями АЗУ 420 и ЗУПВ 430 дает возможность следующей выборке начать свой поиск АЗУ в то время, когда в ЗУПВ завершается предшествующая выборка. Тем самым используют возможность оперативной памяти процессора выдавать несколько запросов памяти до возвращения данных от первого запроса. Последовательные запросы детектируют, и они обходят просмотр АЗУ, тем самым экономя энергию и улучшая рабочие характеристики.

После изложенного выше описания общей структуры асинхронного микропроцессора согласно предпочтительным вариантам реализации данного изобретения далее следует описание схемы, которую используют для блокирования и разблокирования откликов в цикле управления одной из асинхронных схем управления.

Как указывалось выше, микропроцессор содержит некоторое число взаимосвязанных асинхронных схем управления, каждая из которых применяет цикл управления запросом-подтверждением для управления потоком данных. Путем блокировки отклика в одном из этих циклов управления блок, в конечном счете, будет распространяться по всему микропроцессору, прекращая всякие действия.

В предпочтительном варианте реализации данного изобретения предусмотрена схема, которая обеспечивает блокировку и последующую разблокировку цикла запроса-подтверждения на конечной стадии конвейера исполнения 260. Специалистам данной области будет очевидно, что точное местоположение этой схемы не представляет особого значения, поскольку все асинхронные схемы управления взаимосвязаны, и поэтому блокированные любого цикла управления запросом-подтверждением будет в конечном счете иметь такое же следствие.

Схема, используемая в предпочтительном варианте реализации для блокировки и разблокировки цикла управления запросом-подтверждением на последней стадии исполнительного конвейера 260, далее излагается со ссылкой на фиг.4 - принципиальную схему необходимых логических компонентов. Всякий раз, когда команду направляют от конвейера команд 225 к декодеру команд 230, эту команду сравнивают с 'В.' -командой в декоре команд 230. 'В.' -команда является командой ветвления, а 'В'. -команда является командой ветвления, которая ветвится к текущей команде (т. е. к себе). Поэтому в этой точке программа повторно зацикливается, не выполняя при этом полезной функции, до тех пор, пока прерывание не возбудит цикл. 'В.' -команду обычно используют для того, чтобы микропроцессор находился в состоянии готовности до момента получения прерывания, которое указывает, что еще есть предстоящая полезная работа. В предпочтительном варианте реализации данного изобретения именно 'В.' -команда используется для прекращения всех действий в процессоре.

При детектировании 'В. ' -команды декодером команд 230 он формирует "остановочный" сигнал, который направляют по тракту 235 в конвейер управления 240, и оттуда направляют в конвейер исполнения 260, наряду с многими другими сигналами управления, которые используют для управления другими аспектами функциональности конвейера исполнения, например сигналы управления, которые сообщают арифметико-логическому устройству (АЛУ) в конвейере исполнения о том, какую операцию АЛУ должен выполнить.

Последняя стадия конвейера исполнения 260 имеет входной регистр 500 и выходной регистр 520, которые запоминают соответственно операнды входных и выходных данных. Цикл управления формируют сигналом запроса 510, который должен быть подвергнут задержке 511, чтобы имелось время для функций обработки данных на этой стадии, и сигналом подтверждения 530; эти сигналы связывают с регистрами 500 и 520 для формирования полного цикла управления. Цикл управления может быть прерван вентилем И 560, который, если выходным сигналом вентиля И-НЕ 550 является логический 0, не даст возможности пройти сигналу запроса.

Вентиль И-НЕ 550 принимает четыре входных сигнала, а именно: "остановочный" сигнал 551, сформированный декодером команд 230, сигнал запроса прерывания (irq) 552, сигнал запроса быстрого прерывания (fiq) 553 и сигнал исполнения 554, который сформирован конвейером исполнения и подтверждает, что команду 'В. ' действительно нужно исполнить. Сигнал исполнения используют в предпочтительных вариантах реализации по той причине, что, например, исполнение 'В.' -команды может зависеть от результата предшествующей команды. В этом случае сигнал исполнения будет выдан конвейером исполнения, если результат предшествующей команды, указанной как 'В.' -команда, нужно подвергнуть обработке. Либо предшествующая команда может быть командой ветвления, и в этом случае "остановочную" команду исполнять не надо, а сигнал исполнения будет соответственно установлен на "недействующий".

Вентиль И-НЕ 550 будет иметь выходной сигнал логического О, когда не будут действовать два источника прерывания 'irq' 552 и 'fiq' 553 (при логической единице, поскольку они являются "низкоактивными" сигналами), остановочный сигнал 551 будет действующим (при логической 1), и сигнал исполнения 554 будет местоположением, в котором следует выполнить остановочную схему предпочтительного варианта реализации данного изобретения.

Специалистам данной области будет очевидно, что синхронизация входных сигналов 551, 552, 553 и 554 в вентиль И-НЕ 550 имеет существенное значение для правильного функционирования схемы. Сигнал исполнения 554 надежен, поскольку его формируют на месте, и его правильную синхронизацию обеспечивают задержкой 511. Задержка 511 задерживает линию запроса, чтобы иметь время для определения из результатов предшествующей команды следующего: должен ли сигнал исполнения быть действующим, или нет; и для формирования соответствующего сигнала исполнения. Остановочный сигнал 551 формируют в декодере команд 230, и его правильную синхронизацию обеспечивают его передачей по конвейеру управления 240, который использует известную методику синхронизации для надежного направления значений в конвейер исполнения 260. Но входные сигналы прерывания 552 и 553 нельзя обрабатывать таким же образом, потому что они должны быть в состоянии разблокировать схему управления даже тогда, когда все схемы управления в системе блокированы вследствие исполнения команды 'В. '. Поэтому источники прерывания должны быть непосредственно подключены к шинам 552 и 553. Для этого сигналы прерывания никогда не должны делать переход с действующего (значение логического 0) на недействующий уровень (значение логической 1), когда остановочный сигнал 551 все еще является действующим, чтобы избежать неправильного поведения схемы. Но устройства, которые формируют прерывания, обычно выполняют таким образом, чтобы они не вызывали прерываний до тех пор, пока процессор не даст им на это команду; причем таковое устранение сигнала прерывания находится под управлением средств программного обеспечения. Поэтому указанные выше ограничения можно соблюдать простым образом за счет соответствующих методов программирования.

Путем применения изложенного выше технического решения останавливают конвейер исполнения 260. Тогда конвейер исполнения последующие команды не исполняет и таким образом конвейер управления заполняется. После того, как конвейер управления 240 заполнится, декодер 230 останавливается, так как он больше не может направлять декодированные команды в конвейер управления, и соответственно конвейер исполнения 225 будет заполняться командами, выбранными из памяти 210.

Одновременно с этим адресный интерфейс 200 может производить выборку команд только до этого времени, поскольку конвейер исполнения 225 или конвейер СК 280 являются заполненными. Как указывалось выше, конвейер исполнения 225 будет заполнен по той причине, что декодер команд 230 больше не будет считывать команды с конвейера 225. Поэтому очевидно, что остановка конвейера исполнения 260, в конечном счете, обусловит прекращение работы всего микропроцессора.

С помощью 'В'. -команды, которая уже имеется в большинстве наборов команд микропроцессора, отсутствует необходимость в новой команде и можно обеспечить совместимость средств программного обеспечения с большей частью имеющихся кодов. Специалистам данной области будет очевидно, что для блокирования и деблокирования циклов управления асинхронных схем управления можно применить и другие решения, а использование 'В'. -команды не является существенно важным.

Выше был изложен конкретный вариант реализации изобретения, но следует понимать, что данное изобретение им не ограничивается, и диапазон раскрытия данного изобретения охватывает также и многие изменения и дополнения к нему.

Изобретение касается обработки данных. Техническим результатом является расширение функциональных возможностей. Устройство содержит множество асинхронных схем управления, остановочную схему для блокирования сигнала управления в цикле управления первой асинхронной схемы управления. Остановочная схема предотвращает обмен сигналами данных первой из асинхронных схем управления с другими асинхронными схемами управления. Способ описывает работу указанного устройства. 3 с. и 12 з.п. ф-лы, 4 ил.

| Устройство для измерения давления | 1977 |

|

SU638858A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ АСИНХРОННЫХ РАЗНОСКОРОСТНЫХ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2014737C1 |

| US 5313621 А, 17.05.1994 | |||

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| УСТРОЙСТВО ДЛЯ ЭЛЕКТРОДИНАМИЧЕСКОГО | 0 |

|

SU334625A1 |

Авторы

Даты

2002-05-10—Публикация

1997-09-30—Подача