Настоящее изобретение относится к устройству и способу преобразования потока носителей заряда в частотный сигнал.

Подобного рода устройство, известное также под названием преобразователя заряд - частота, представляет собой электронную схему, служащую для измерения потока электрических зарядов.

Известна электронная схема преобразователя заряд - частота с последовательно включенными интегратором и компаратором. На вход схемы подается электрический заряд, который затем интегрируется интегратором. Последний подает к усилителю сигнал напряжения, соответствующий интегралу подаваемого заряда. В компараторе интегрированный сигнал напряжения сравнивается с заданной опорной величиной заряда. По достижении сигналом опорной величины компаратор выдает импульс на выход схемы. Затем интегратор возвращается в исходное состояние и цикл интегрирования и сравнения повторяется. Таким образом на выходе схемы возникает серия импульсов во времени, мгновенная частота которых является мерой подаваемого в единицу времени количества электрических зарядов, т.е. потока носителей заряда.

Недостаток известной схемы состоит в том, что интегратор в течение процесса возврата в исходное состояние не может работать, т.е. возникает "мертвое время", в течение которого нельзя измерить поток носителей заряда. Из этого следует, что в таких критичных относительно времени процессах измерения, при которых подаваемое количество носителей заряда быстро меняется и требует быстрого обнаружения, вследствие возврата интегратора в исходное состояние теряется много времени. Это в свою очередь может привести к неточным результатам измерения, которые недопустимы, в частности, тогда, когда требуется высокая степень надежности измерения, как, например, при лечении ионным излучением больных.

Итак, задачей настоящего изобретения является создание устройства и способа преобразования потока носителей заряда в частотный сигнал, обеспечивающих точное, быстрое и надежное измерение заряда. Эта задача решается с помощью устройства, имеющего признаки в соответствии с пп.1 и 14, и способа, имеющего признаки в соответствии с пп.8 и 21 формулы изобретения. Предпочтительные варианты выполнения настоящего изобретения определены в дополнительных пунктах формулы изобретения.

Предлагаемые устройство и способ имеют ряд преимуществ.

Наличие двух параллельно включенных схемных ветвей позволяет продолжить процесс измерения потока носителей заряда во второй ветви, когда в первой ветви поток носителей заряда достигнет заданного порогового значения и возникнет необходимость возврата интегратора этой ветви в исходное состояние, и наоборот. Благодаря этому в ходе измерения потока носителей заряда не возникает "мертвого времени", вызываемого возвратом интегратора в исходное состояние.

Предусматривая разные значения порогового напряжения для каждого из компараторов в отдельности, получают схему с расширенным диапазоном измерения. Если переключение с одной ветви на другую производится реже, удается свести к минимуму периоды времени, уходящие на переключение, и "мертвые времена".

Далее, подключением второй ветви в момент, когда в первой ветви еще осуществляется измерение потока носителей заряда, можно исключить время переключения, оставшееся в момент перехода с одной ветви на другую. В результате получают устройство и способ, позволяющие вести измерение потока носителей заряда непрерывно, т.е. без "мертвых времен".

Кроме того, схема построена из доступных в торговле компонентов, т.е. ее можно изготовить экономически выгодным образом, и ее проектные свойства удается воспроизвести надежным образом в масштабах крупносерийного производства.

Настоящее изобретение иллюстрируется чертежами:

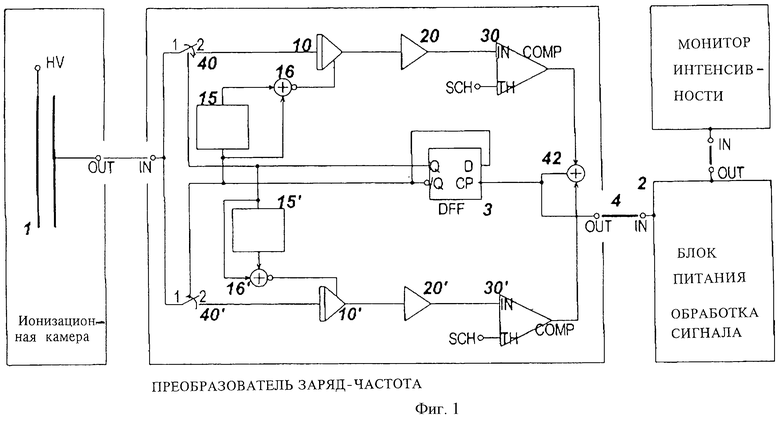

Фиг. 1 - блок-схема преобразователя заряд - частота согласно первому варианту выполнения изобретения,

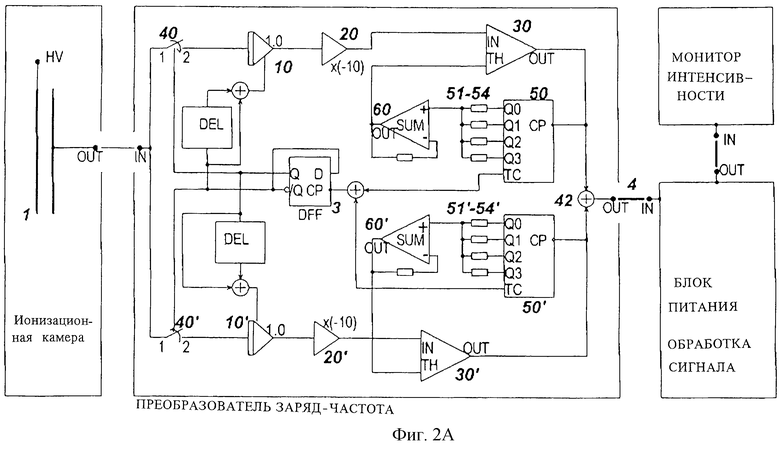

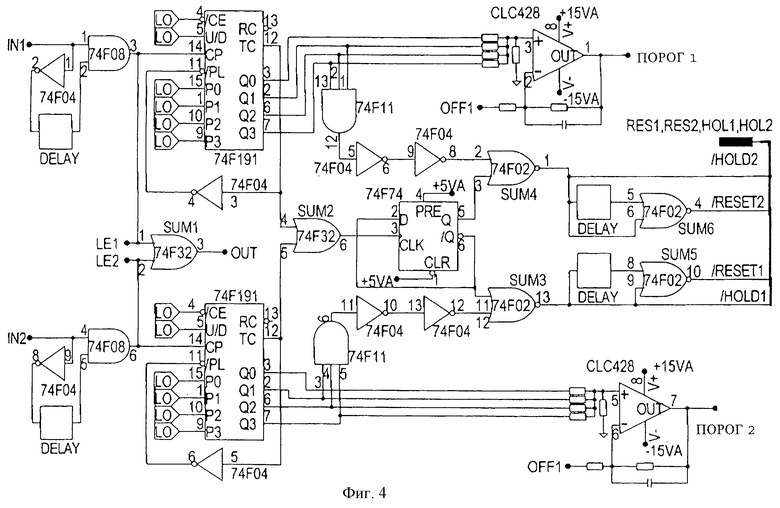

Фиг. 2А, Б - блок-схема преобразователя заряд - частота согласно второму варианту выполнения изобретения,

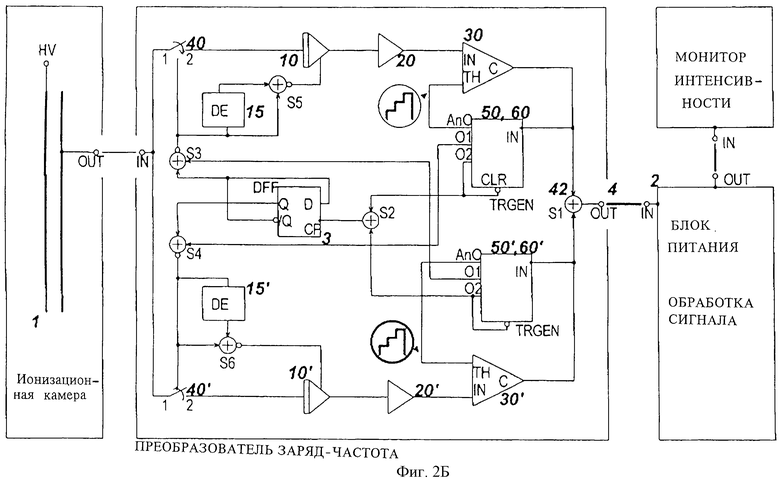

Фиг. 3 - схема аналоговой части преобразователя заряд - частота согласно второму варианту выполнения изобретения,

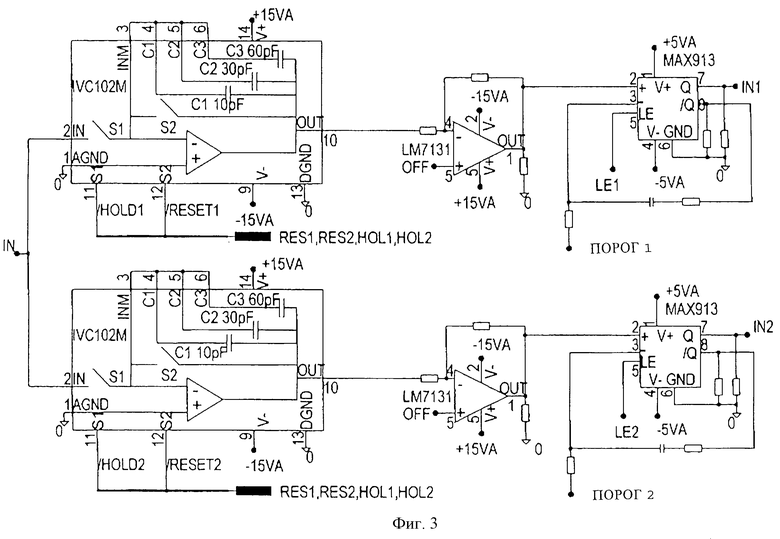

Фиг. 4 - схема цифровой части и генератора пороговых напряжений преобразователя заряд - частота согласно второму варианту выполнения изобретения,

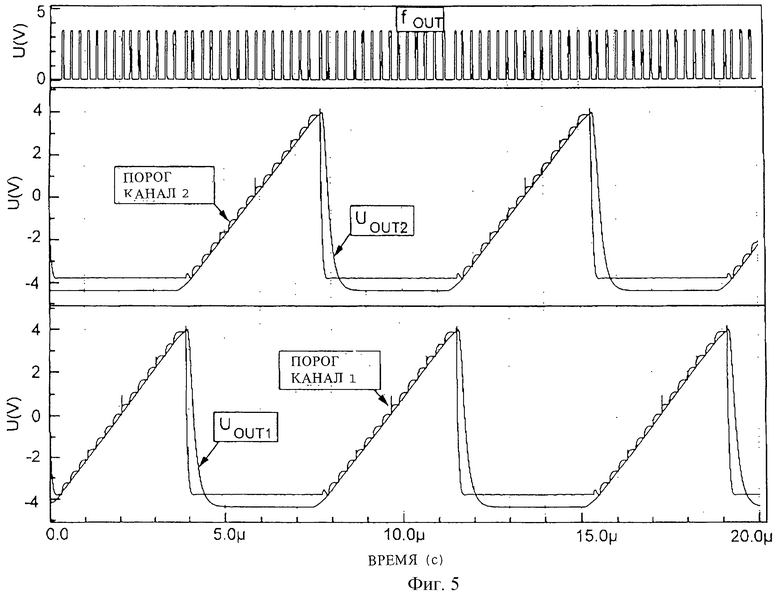

Фиг. 5 - диаграмма характеристики преобразователя заряд - частота согласно второму варианту выполнения изобретения,

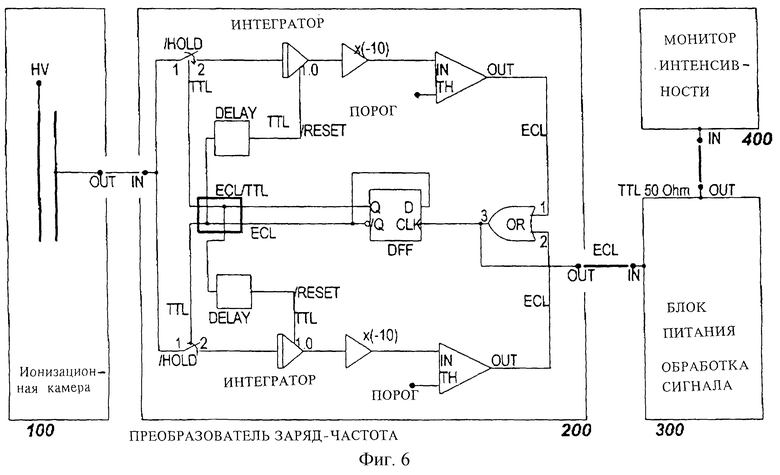

Фиг. 6 - блок-схема конкретного назначения предлагаемого преобразователя заряд - частота.

На Фиг. 1 показана блок-схема преобразователя заряд - частота согласно первому варианту выполнения изобретения, иллюстрирующая компоновку преобразователя. Преобразователь в основном состоит из двух параллельно включенных схемных ветвей Z и Z' (называемых также группами единичных импульсов), имеющих одинаковую структуру. Ветви Z и Z' в двухтактном режиме соединяются со входом 1 или отключаются от него переключательными элементами 40 и 40' соответственно. Каждая ветвь включает интегратор 10, 10', служащий для интегрирования потока носителей заряда, подаваемого через замкнутый в данный момент переключательный элемент 40 или 40', и для выделения соответствующего интегралу сигнала напряжения. Выход интегратора связан с усилителем 20, 20'. Сигнал напряжения подается к компаратору 30, 30'. Ко второму входу компаратора 30, 30' приложен сигнал порогового напряжения, служащий в качестве сравнительного сигнала. Сигнал порогового напряжения представляет собой сигнал постоянного напряжения, величина которого устанавливается делителем напряжения.

Выходы двух компараторов 30, 30' через сумматор 4 связаны с D-триггером 3, с помощью которого интегратор 10 или 10' через звено задержки 15, 15' возвращается в исходное состояние и запускаются переключательные элементы 40, 40'. Каждый из двух инверсных выходов Q,  D-триггера 3 связан с одним из двух переключательных элементов 40, 40'. В результате оба переключательных элемента работают в двухтактном режиме. Вслед за сумматором 4 предусмотрен элемент 42 для съема выходного сигнала.

D-триггера 3 связан с одним из двух переключательных элементов 40, 40'. В результате оба переключательных элемента работают в двухтактном режиме. Вслед за сумматором 4 предусмотрен элемент 42 для съема выходного сигнала.

Итак, обе ветви Z, Z' работают попеременно, т.е. в то время, когда в рабочей ветви интегрируется и усиливается сигнал потока носителей заряда и сравнивается с пороговым напряжением, запертая ветвь не работает, так что остается достаточно времени для возврата интегратора этой ветви в нулевое состояние.

Интегратор 10, 10' в рабочей ветви интегрирует сигнал потока носителей заряда, поступающий со входа схемы, и преобразовывает полученный интегрированный сигнал потока носителей заряда в сигнал напряжения. Сигнал напряжения усиливается в усилителе 20, 20', а затем подается на один из входов компаратора 30, 30'. Компаратор 30, 30' сравнивает величину этого сигнала с пороговым напряжением, приложенным к его другому входу. Когда интегрированный сигнал потока носителей заряда достигает порогового напряжения, компаратор на выходе выделяет импульс. Через сумматор 4 этот импульс подается к D-триггеру 3. Тогда D-триггер 3 меняет свое состояние, т.е. происходит инверсия сигналов на его выходах Q и  соответственно. В результате разомкнутый до сих пор переключательный элемент замыкается, а замкнутый до сих пор переключательный элемент размыкается и соответствующий интегратор возвращается в исходное состояние. Возврат в исходное состояние происходит мгновенно; снятие возврата в исходное состояние осуществляется только через некоторое время (обычно через 50 нс) после замыкания соответствующей ветви. Для этого предусмотрены элементы задержки 15, 15', препятствующие тому, чтобы возникающий при замыкании соответствующей ветви импульс тока не интегрировался интегратором 10, 10' и тем самым искажал результаты измерения.

соответственно. В результате разомкнутый до сих пор переключательный элемент замыкается, а замкнутый до сих пор переключательный элемент размыкается и соответствующий интегратор возвращается в исходное состояние. Возврат в исходное состояние происходит мгновенно; снятие возврата в исходное состояние осуществляется только через некоторое время (обычно через 50 нс) после замыкания соответствующей ветви. Для этого предусмотрены элементы задержки 15, 15', препятствующие тому, чтобы возникающий при замыкании соответствующей ветви импульс тока не интегрировался интегратором 10, 10' и тем самым искажал результаты измерения.

Затем вышеописанный цикл повторяется во второй ветви, в то время как первая ветвь не работает.

Итак, обе ветви поочередно подают импульсы к сумматору 4, в результате чего в элементе для съема сигналов 42 образуется временная последовательность импульсов, частота которых представляет собой поток носителей заряда в единицу времени на входе схемы.

Разрешение данной схемы составляет около 10 пКл/импульс, а поток носителей заряда - около 25 мкКл/с. С помощью этой схемы можно вырабатывать выходные сигналы частотой до 1 МГц для излучения интенсивностью 106-108 частиц в секунду. При этом частота ошибок составляет менее 3%.

Частоту ошибок можно еще понизить, уменьшая число переключений двух ветвей. Это можно осуществить с помощью схемы согласно Фиг.2А, Б. На Фиг.2А показана структура преобразователя заряд - частота в виде блок-схемы в соответствии со вторым вариантом выполнения изобретения. По сравнению со схемой по фиг. 1 данная схема включает еще дополнительные компоненты 50, 60 и 50', 60' соответственно для выработки пороговых напряжений различной величины. Пороговые напряжения вырабатываются подключением разных сопротивлений 51-54 и 51'-54' соответственно к входу операционных усилителей 60, 60'. Подача порогового напряжения данной величины осуществляется с помощью элементов двоичного счетчика 50, 50', которые запускаются импульсами сигнала, выделяемого компаратором 30, 30'. С помощью четырех сопротивлений 51-54 и 51'-54' соответственно можно вырабатывать по 16 разных пороговых напряжений (т.е. ступенчатые напряжения). Итак, при соотношении сопротивлений двух смежных сопротивлений 2:1 удается расширить диапазон измерения в 15 раз. И в этом примере выполнения изобретения обе ветви Z, Z' имеют идентичные схемотехнические параметры.

Измеряемый сигнал потока носителей заряда, как и в случае первого примера выполнения изобретения, подается к одной из двух ветвей тактированием работы переключательных элементов 40, 40'. Но в отличие от первого примера выполнения изобретения обе ветви в данном случае замыкаются не совсем точно по такту, а с некоторым временным перекрытием, т.е. времена замыкания обоих переключательных элементов перекрываются в начале и конце каждого такта.

Допустим, что ветвь Z представляет собой активную ветвь. В начале такта активной ветви интегратор 10 находится в нулевом состоянии, а к компаратору 30 приложено пороговое напряжение минимальной величины. Когда величина выделяемого усилителем 20 интегрированного сигнала потока носителей заряда достигает первого значения порогового напряжения, на выход, как и в первом примере выполнения изобретения, подается импульс. Но в отличие от преобразователя согласно первому примеру выполнения изобретения интегратор не возвращается в исходное состояние и ни один из переключательных элементов не переключается, т. е. ветвь Z продолжает быть активной. Затем запускается двоичный счетчик 50, который в свою очередь последовательным подсоединением другой комбинации сопротивлений 51-54 вырабатывает следующее по величине пороговое напряжение и подает его на вход компаратора 30. Процесс интегрирования продолжается до тех пор, пока величина интегрированного сигнала потока носителей заряда не достигнет актуального значения порогового напряжения. Тогда вновь выделяется импульс и цикл заново начинается. Этот цикл повторяется до достижения сигналом последнего из 16 значений порогового напряжения и только тогда отключается активная ветвь Z и интегратор 10 возвращается в исходное состояние.

С другой стороны, ветвь Z' замыкается не при достижении сигналом последнего значения порогового напряжения ветви Z, a уже при достижении предпоследнего, так что во время последней фазы измерения обе ветви Z и Z' оказываются активными. Благодаря этому удается исключить погрешность измерения, возникающую вследствие задержки при замыкании переключательного элемента в начале такта данной ветви.

Затем вышеописанный цикл повторяется и для ветви Z'.

На Фиг.3 изображена блок-схема аналоговой части преобразователя заряд - частота, которая является общей для обоих вариантов выполнения изобретения. Интегратор 10, 10' выполнен в виде операционного усилителя (ОРАМР) со схемой емкостной обратной связи 15, 15' и подаваемый поток носителей заряда с помощью переключательных элементов 40, 40' направляется к инвертирующему входу. Усилители 20, 20' и компараторы 30, 30' выполнены посредством дополнительных операционных усилителей с соответствующими схемами.

На Фиг. 4 изображены блок-схема цифровой части преобразователя заряд - частота и генераторы пороговых напряжений согласно второму примеру выполнения изобретения.

Генератор пороговых напряжений по существу может иметь разную структуру. Важно лишь то, чтобы он при каждом импульсе (вплоть до такой малой величины, как около 10 нс) надежно генерировал новый импульс напряжения менее чем за 100 нс. Конечно, возможно и другое распределение по ступеням пороговых напряжений. В таком случае в генератор пороговых напряжений будут входить большее или меньшее число сопротивлений и счетчик с соответствующим числом разрядов.

Вместо двоичного счетчика можно использовать и другую схему, с помощью которой можно последовательно выбирать ступенчато изменяющиеся напряжения.

Вместо генерации напряжения разной величины за счет подключения сопротивлений разных значений к выходу операционного усилителя 60, 60' генератор пороговых напряжений 50, 50' и 60, 60' можно выполнить и с помощью цифроаналогового преобразователя, преобразовывающего двоичное число в напряжение определенной величины. На Фиг.2Б изображена соответствующая модификация примера выполнения изобретения по Фиг.2А.

С помощью схемы согласно второму варианту выполнения изобретения с применением указанных на Фиг.3 и 4 компонентов удается измерить потоки носителей заряда от 10-14 до 10-4 Кл/с.

На Фиг.5 показана диаграмма характеристики преобразователя заряд - частота согласно второму примеру выполнения изобретения. В нижней диаграмме над горизонтальной временной осью изображены кривые напряжений на обоих входах компаратора 30 в ветви Z, в средней диаграмме - кривые напряжений на обоих входах компаратора 30' в ветви Z' и над этой диаграммой - выходной сигнал, подаваемый на выход 4. Пороговые напряжения ступенчато расположены на одинаковых расстояниях в пределах от -4 В до 4 В. Подаваемый к компараторам интегрированный сигнал напряжения Uout1 и Uout2 соответственно представляет здесь постоянный во времени поток носителей заряда на входе 1. Каждой точке соприкосновения Uout1 или Uout2 соответственно с данным значением порогового напряжения соответствует данный импульс напряжения в выходном сигнале. Из перекрывающихся тактов работы двух переключательных элементов 40, 40' следует, что заряд, подаваемый за время перекрытия, распределяется по обеим ветвям Z1, Z2. Из этого вытекает временное перекрытие конца каждого фронта нарастания Uout1 и Uout2 соответственно с началом каждого следующего фронта нарастания Uout2 и Uout1 соответственно в другой ветви. Поэтому пороговое напряжение следующей величины достигается немного позже, вследствие чего в выходном сигнале появляется некоторый разрыв.

Когда полное исключение "мертвых времен", вызываемых переключением переключательных элементов 40, 40', не необходимо, принцип расширения диапазона измерения с помощью схемных компонентов 50, 60 и 50', 60' соответственно согласно второму примеру выполнения изобретения можно комбинировать непосредственно с преобразователем заряд - частота согласно первому примеру выполнения изобретения.

Предлагаемый преобразователь заряд - частота и предлагаемый способ могут найти разностороннее применение. На Фиг.6 изображена блок-схема предлагаемого преобразователя, используемого для измерения интенсивности излучения пучка тяжелых ионов в лечении больных облучением. Детектором ионного излучения служит ионизационная камера 100, которая помещена в пучок ионного излучения. Проходящие через камеру ионные лучи генерируют заряд. Величина заряда пропорциональна количеству ионов, проходящих через ионизационную камеру. Заряд подается к преобразователю заряд - частота 200. Выделяемый преобразователем сигнал подается к блоку первичной обработки сигнала 300 и затем к монитору 400, отображающему интенсивность излучения; здесь производится оценка измеряемого сигнала в целях контроля облучения или отключения пучка. Быстрое, надежное и точное измерение интенсивности облучения, обеспечиваемое предлагаемым устройством, имеет величайшее значение именно в этой области его применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ перемножения аналоговых сигналов (его варианты) | 1982 |

|

SU1116437A1 |

| ДЕТЕКТОР ИЗЛУЧЕНИЯ И СИСТЕМА РЕНТГЕНОВСКОЙ ВИЗУАЛИЗАЦИИ | 2017 |

|

RU2683961C1 |

| Зарядно-пусковое устройство | 1988 |

|

SU1647768A1 |

| Преобразователь напряжения в частоту и способ его калибровки | 2020 |

|

RU2755017C1 |

| Устройство для передачи и приема многопозиционных широкополосных сигналов | 1986 |

|

SU1345361A1 |

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| БЛОК УПРАВЛЕНИЯ И СПОСОБ ДЛЯ ПРИВЕДЕНИЯ В ДЕЙСТВИЕ СРЕДСТВ БЕЗОПАСНОСТИ ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 2008 |

|

RU2518200C2 |

| СБОР ДАННЫХ | 2010 |

|

RU2541133C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО ТОКА С ОГРАНИЧЕНИЕМ ТОКА | 1991 |

|

RU2107380C1 |

Использование: для преобразования потока заряда в сигнал частоты. Технический результат заключается в обеспечении точного, быстрого и надежного измерения заряда. Устройство включает две параллельно включенные схемные ветви (Z, Z'), которые поочередно загружаются потоком носителей заряда и в каждой из которых последовательно включены переключательный элемент (40, 40'), интегратор (10, 10') и компаратор (30, 30'), причем переключательные элементы (40, 40') служат для подачи потока носителей заряда к одной из двух схемных ветвей (Z, Z'). Интегратор (10, 10') в схемной ветви (Z, Z'), к которой подается поток носителей заряда, служит для интегрирования потока носителей заряда и выполнен с возможностью возврата в исходное состояние, а компаратор (30, 30') рассчитан на выдачу сигнала в случае совпадения интегрированного значения потока носителей заряда с заданным пороговым значением. 4 с. и 22 з.п.ф-лы, 6 ил.

| WO 9740392 A, 19.05.1998 | |||

| RU 2070723 C1, 10.12.1996 | |||

| ИНДИКАТОР ИНТЕНСИВНОСТИ ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ | 1995 |

|

RU2098837C1 |

| УСТРОЙСТВО ДЛЯ ШЕЛУШЕНИЯ ЗЕРНА | 2010 |

|

RU2436632C1 |

Авторы

Даты

2004-01-20—Публикация

1999-09-10—Подача