Изобретение относится к многоканальным системам радиосвязи и предназначено для использования в многолучевых линиях тропосферной,ионосферной и др. связей при передаче дискретных сообщений.

Цель изобретения - повьшшние помехоустойчивости .

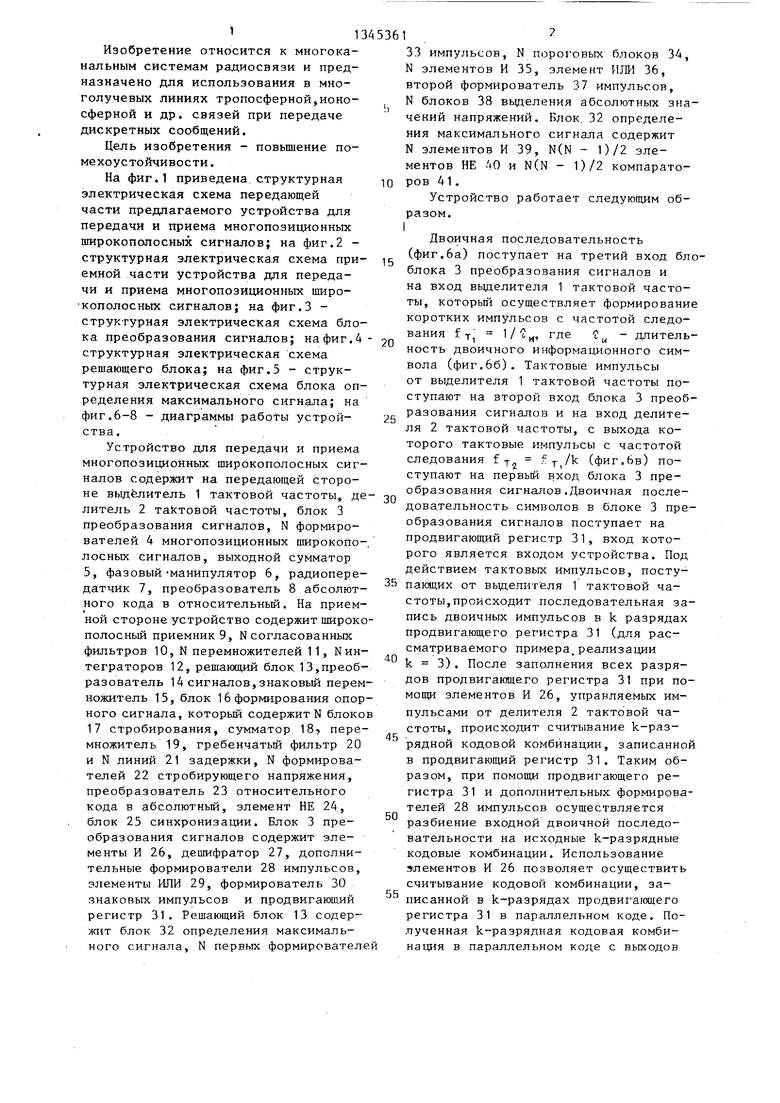

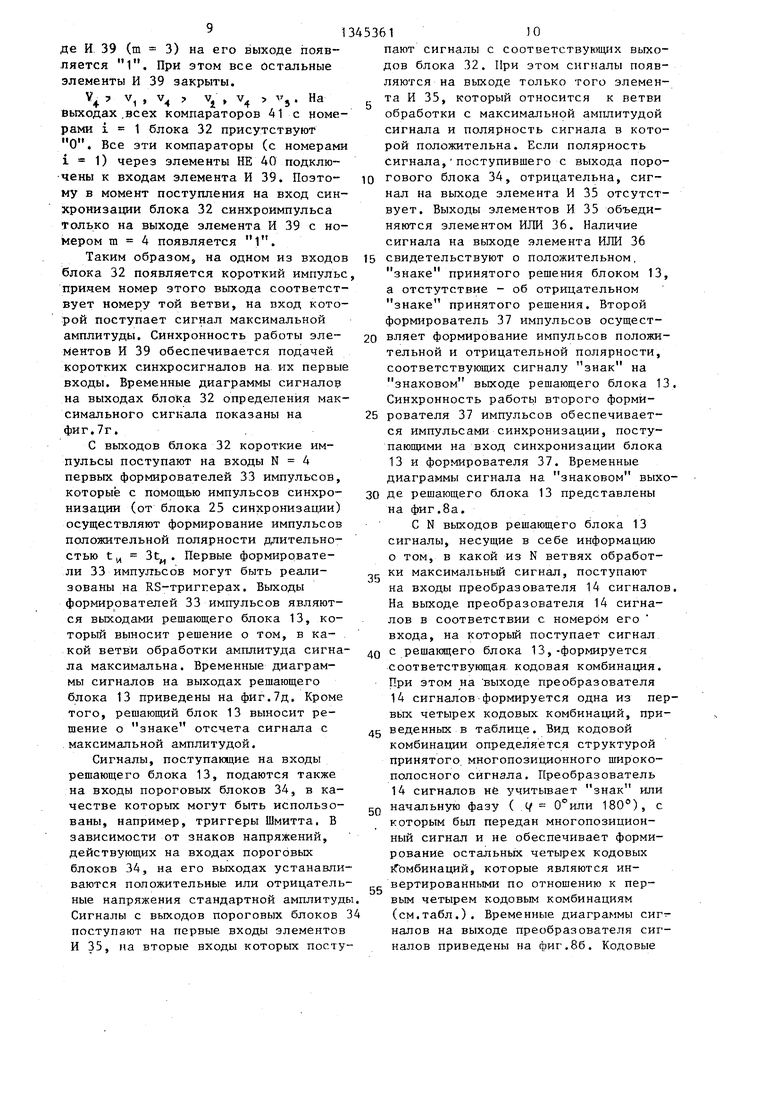

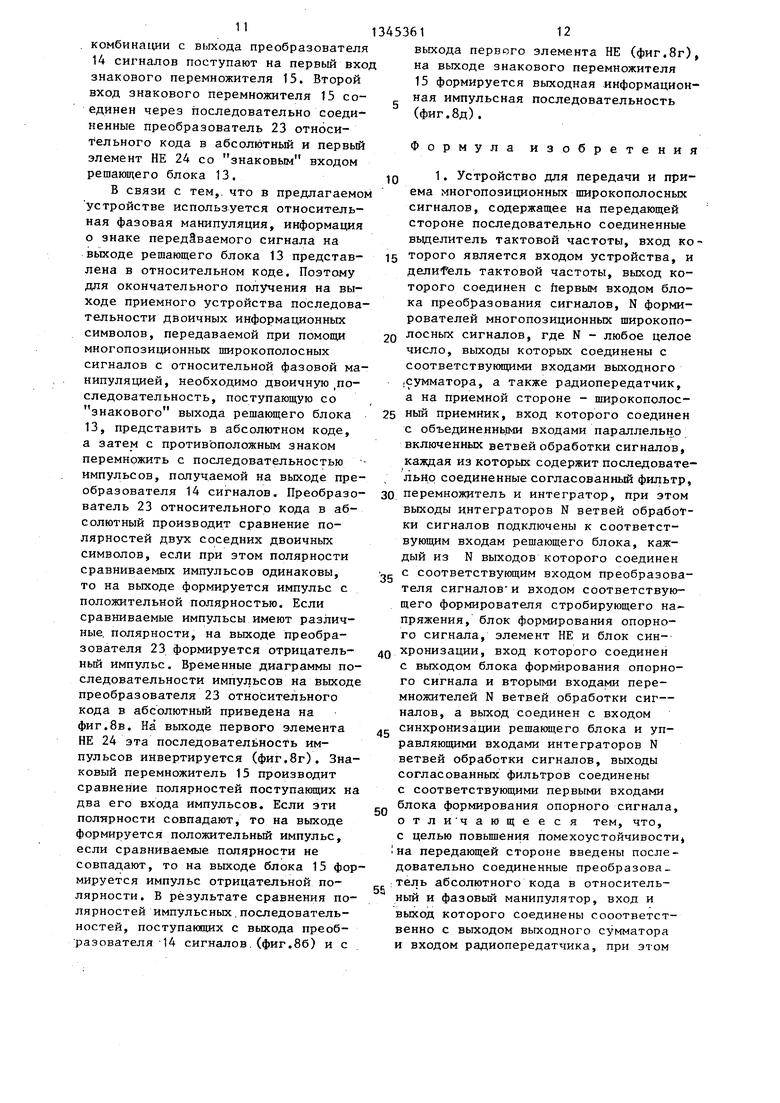

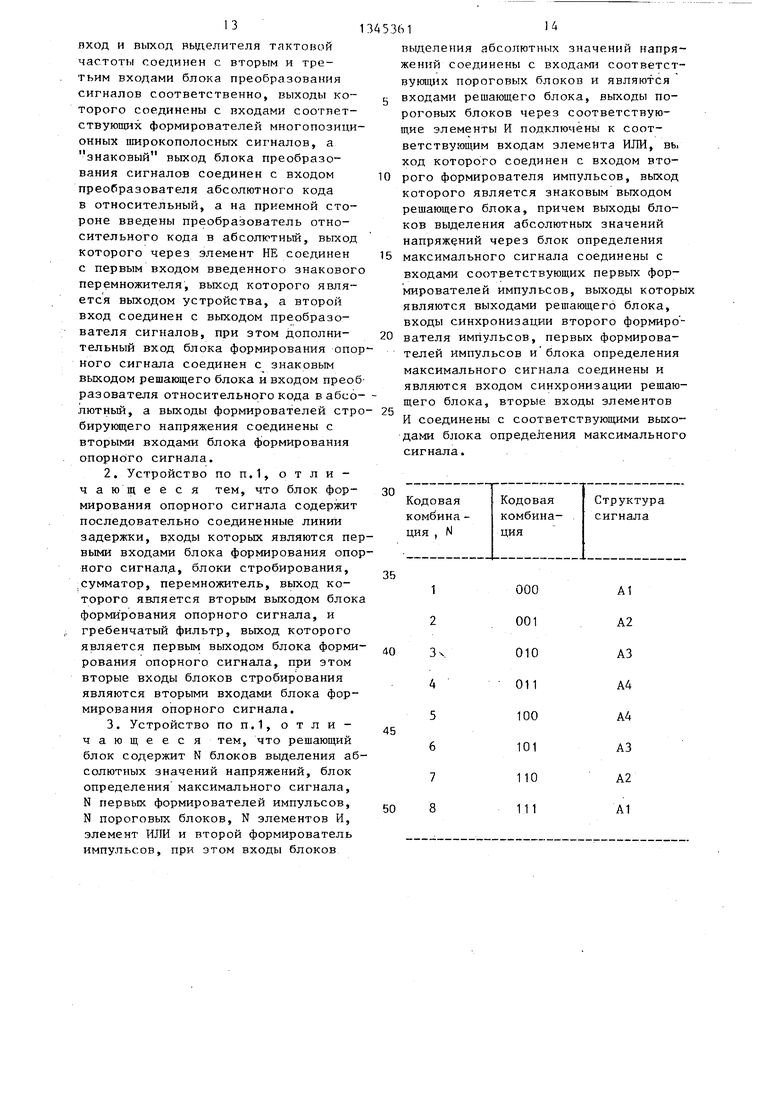

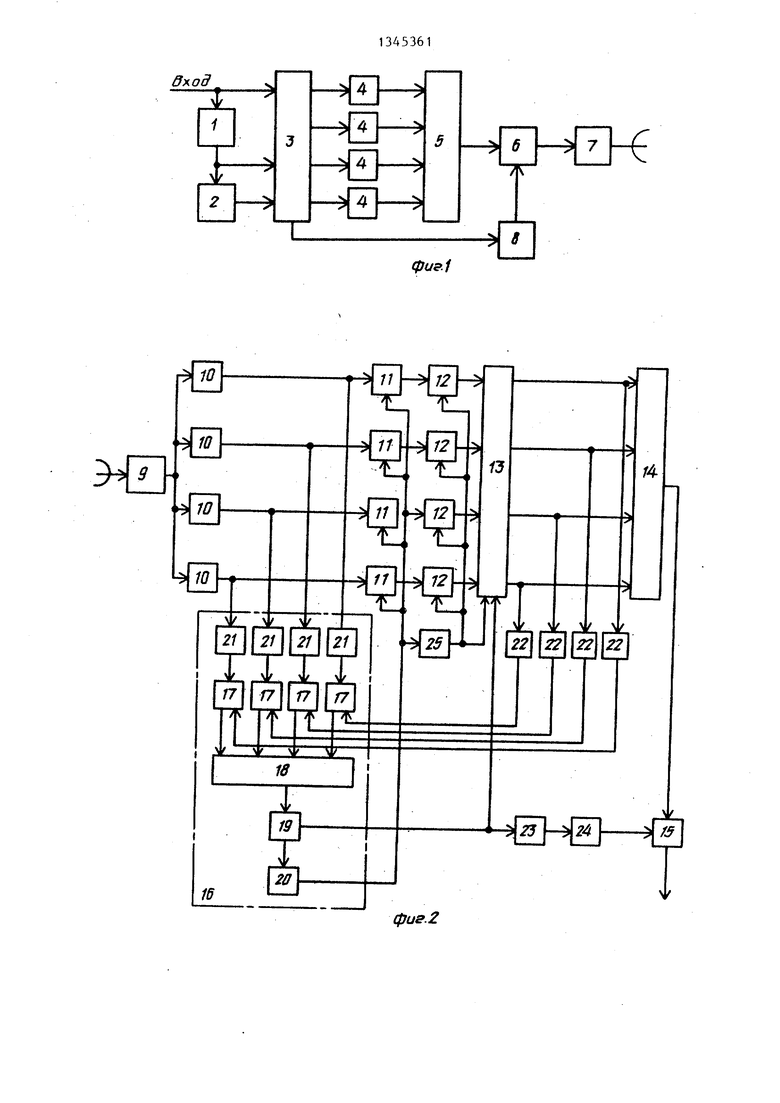

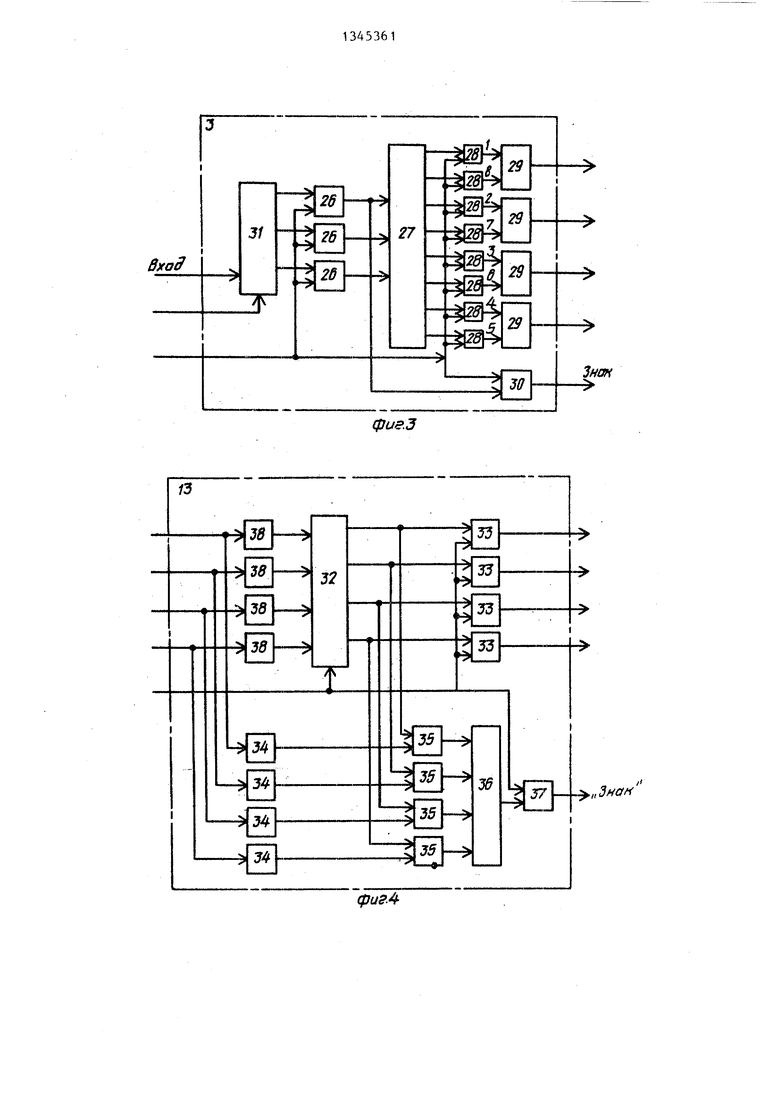

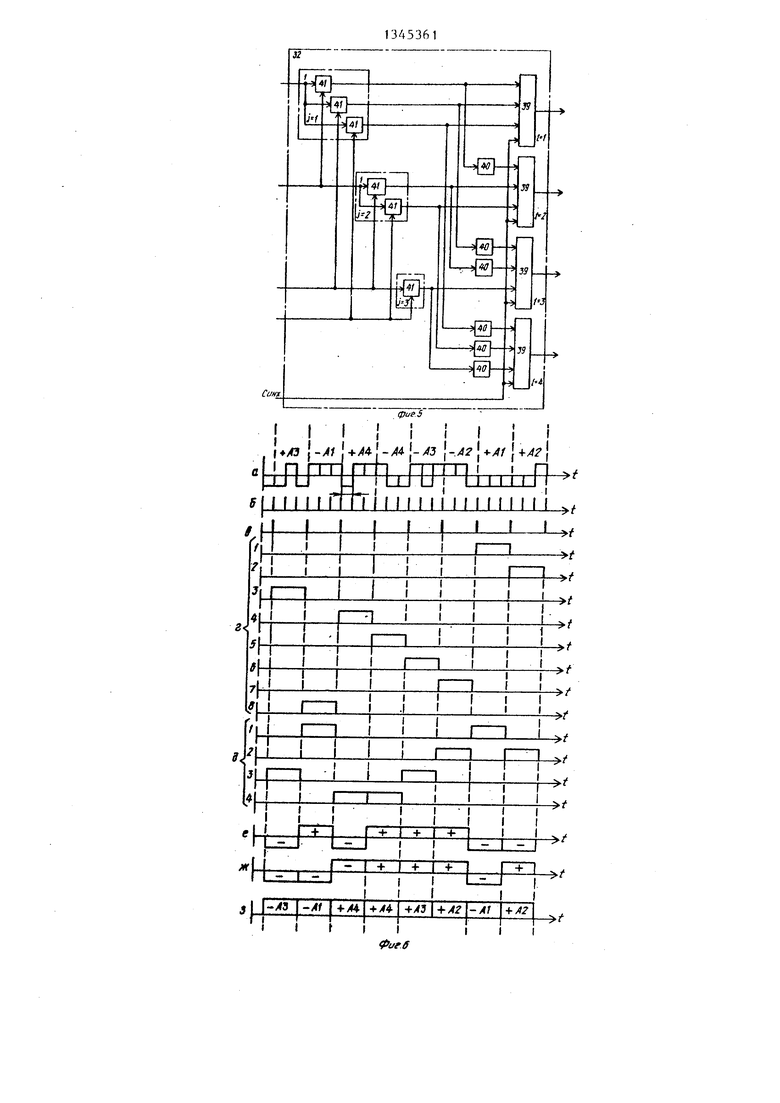

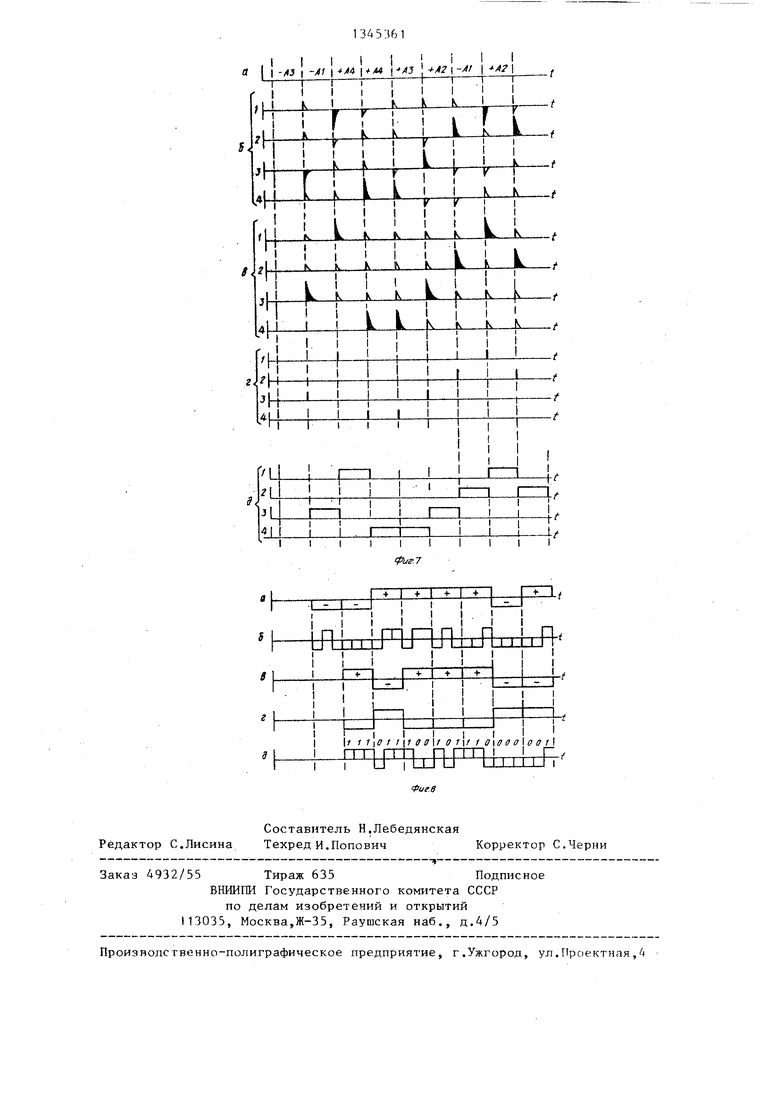

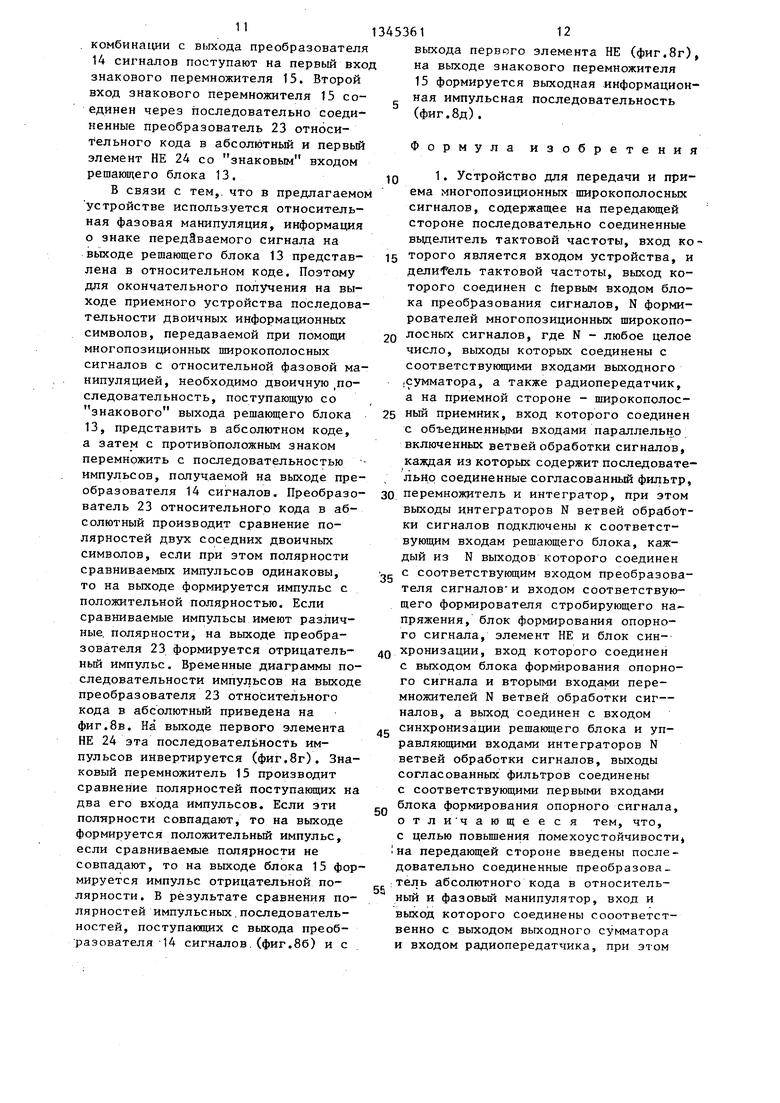

На фиг.1 приведена, структурная электрическая схема передающей части предлагаемого устройства для передачи и приема многопозиционных широкополосных сигналов; на фиг.2 - структурная электрическая схема приемной части устройства для передачи и приема многопозиционных широ- кополосных сигналов; на фиг.З - структурная электрическая схема блока преобразования сигналов; на фиг.4 структурная электрическая схема решающего блока; на фиг.З - структурная электрическая схема блока определения максимального сигнала; на фиг.6-8 - диаграммы работы устройства.

Устройство для передачи и приема многопозиционных широкополосных сигналов содержит на передающей стороне выделитель 1 тактовой частоты, де литель 2 тактовой частоты, блок 3 преобразования сигналов, N формирователей 4 многопозиционных широкополосных сигналов, выходной сумматор 5, фазовый-манипулятор 6, радиопередатчик 7, преобразователь 8 абсолютного кода в относительный. На приемной стороне устройство содержит широкополосный приемник 9, N согласованных фильтров 10, N перемножителей 11, N интеграторов 12, решающий блок. 13,преобразователь 14 сигналов, знаковый перемножитель 15, блок 16 формирования опорного сигнала, который содержит N блоко 17 стробирования, сумматор 18, перемножитель 19, гребенчатый фильтр 20 и N линий 21 задержки, N формирователей 22 стробирующего напряжения, преобразователь 23 относительного кода в абсолютный, злемент НЕ 24, блок 25 синхронизации. Блок 3 преобразования сигналов содержит элементы И 26, дешифратор 27, дополнительные формирователи 28 импульсов, элементы ИЛИ 29, формирователь 30 знаковых импульсов и продвигающий регистр 31. Решающий блок 13 содержит блок 32 определения максимального сигнала, N первых формировател

33 импульсов, N пороговых блоков 34, N элементов И 35, элемент ИЛИ 36, второй формирователь 37 импульсов, N блоков 38 выделения абсолютных значений напряжений. Блок. 32 определения максимального сигнала содержит N элементов И 39, N(N - 1)/2 элементов НЕ 40 и N(N - 1)/2 компараторов 4 1.

Устройство работает следующем образом.

5

0

5

о

5

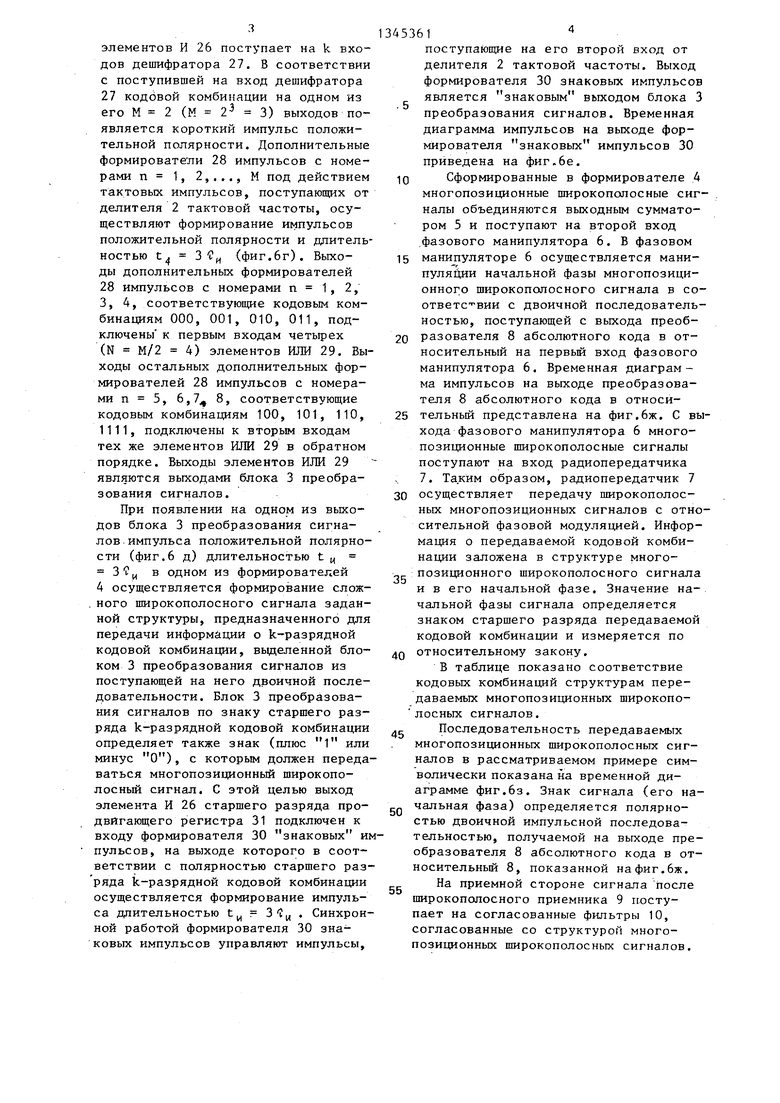

Двоичная последовательность (фиг.ба) поступает на третий вход бло- блока 3 преобразования сигналов и на вход выделителя 1 тактовой частоты, которьй осуществляет формирование коротких импульсов с частотой следования f т, длительность двоичного информационного символа (фиг.бб). Тактовые импульсы от выделителя 1 тактовой частоты поступают на второй вход блока 3 преобразования сигналов и на вход делителя 2 тактовой частоты, с выхода которого тактовые импульсы с частотой следования f f.. (фиг.бв) поступают на первый вход блока 3 преобразования сигналов .Двоич ая последовательность символов в блоке 3 преобразования сигналов поступает на продвигающий регистр 31, вход которого является входом устройства. Под действием тактовьпс импульсов, поступающих от выделителя 1 тактовой частоты, происходит последовательная запись двоичных импульсов в k разрядах продвигающего регистра 31 (для рассматриваемого примера.реализации k 3). После заполнения всех разрядов продвигающего регистра 31 при помощи элементов И 26, управляемых импульсами от делителя 2 тактовой частоты, происходит считывание k-раз- рядной кодовой комбинации, записанной в продвигающий регистр 31. Таким образом, при помощи продвигающего регистра 31 и дополнительных формирователей 28 импульсов осуществляется разбиение входной двоичной последовательности на исходные k-разрядные кодовые комбинации. Использование элементов И 26 позволяет осуществить считывание кодовой комбинации, за- писанной в k-разрядах продвигающего регистра 31 в параллельном коде. Полученная k-разрядная кодовая комбинация в параллельном коде с выходов

0

45

50

3

элементов И 26 поступает на k входов дешифратора 27. В соответствии с поступившей на вход дешифратора

27кодбвой комбинации на одном из его М 2 (М 2 3) выходов появляется короткий импульс положительной полярности. Дополнительные формирователи 28 импульсов с номерами п 1, 2,.,., М под действием тактовых импульсов, поступающих от делителя 2 тактовой частоты, осуществляют формирование импульсов положительной полярности и дпитель- ностью t, 31 (фиг.бг). Выходы дополнительных формирователей

28импульсов с номерами п 1, 2, 3, 4, соответствующие кодовым комбинациям 000, 001, 010, 011, подключены к первым входам четьфех

(N М/2 4) элементов ИЛИ 29. Выходы остальных дополнительных формирователей 28 импульсов с номерами п 5, 6,7 8, соответствующие кодовым комбинациям 100, 101, 110, 1111, подключены к вторым входам тех же элементов ИЛИ 29 в обратном порядке. Выходы элементов ИЛИ 29 являются выходами блока 3 преобразования сигналов.

При появлении на одном из выходов блока 3 преобразования сигналов импульса положительной полярности (фиг.6 д) длительностью t З в одном из формирователей 4 осуществляется формирование сложного широкополосного сигнала заданной структуры, предназначенного для передачи информации о k-разрядной кодовой комбинации, вьщеленной блоком 3 преобразования сигналов из поступающей на него двоичной последовательности. Блок 3 преобразования сигналов по знаку старщего разряда k-разрядной кодовой комбинации определяет также знак (плюс 1 или минус О), с которым должен передаваться многопозиционный широкопоосный сигнал. С этой целью выход элемента И 26 старшего разряда провигающего регистра 31 подключен к входу формирователя 30 знаковых имульсов, на выходе которого в соотетствии с полярностью старшего разяда k-разрядной кодовой комбинации существляется формирование импульа длительностью t 2 , Синхроной работой формирователя 30 знаовых импульсов управляют импульсы.

.5

45361

поступающие на его второй вход от делителя 2 тактовой частоты. Выход формирователя 30 знаковых импульсов является знаковым выходом блока 3 преобразования сигналов. Временная диаграмма импульсов на выходе формирователя знаковых импульсов 30 приведена на фиг.бе.

10 Сформированные в формирователе 4 многопозиционные широкополосные сигналы объединяются выходным сумматором 5 и поступают на второй вход .фазового манипулятора 6. В фазовом 15 манипуляторе 6 осуществляется мани- пуляй;ии начальной фазы многопозиционного широкополосного сигнала в со- ответс- вии с двоичной последовательностью, поступающей с выхода преоб- 20 разователя 8 абсолютного кода в относительный на первьй вход фазового манипулятора 6. Временная диаграмма импульсов на выходе преобразователя 8 абсолютного кода в относи- 25 тельный представлена на фиг.бж. С выхода фазового манипулятора 6 многопозиционные широкополосные сигналы поступают на вход радиопередатчика 7. Таким образом, радиопередатчик 7 30 осуществляет передачу широкополосных многопозиционных сигналов с относительной фазовой модуляцией. Информация о передаваемой кодовой комбинации заложена в структуре многопозиционного широкополосного сигнала и в его начальной фазе. Значение начальной фазы сигнала определяется знаком старшего разряда передаваемой кодовой комбинации и измеряется по 40 относительному закону.

В таблице показано соответствие кодовых комбинаций структурам передаваемых многопозиционных широкопо- лосных сигналов.

g Последовательность передаваемых многопозиционных широкополосных сигналов в рассматриваемом примере символически показана на временной диаграмме фиг.бз. Знак сигнала (его на- Q чальная фаза) определяется полярностью двоичной импульсной последовательностью, получаемой на выходе преобразователя 8 абсолютного кода в от- носительньй 8, показанной на фиг.бж. На приемной стороне сигнала после широкополосного приемника 9 ггосту- пает на согласованные фильтры 10, согласованные со структурой многопозиционных широкополосных сигналов.

35

13453616

При этом количество согласованных Пределы интегрирования устанавли- фильтров 10 равно N М/2 --Аи оп- ваются блоком 25 синхронизации, соединенным по входу с гребенчатым фильтром 20, а по выходу - с управляющими входами интеграторов 12 и последующими устройствами обработки

ределяетсл числом используемых структур многопозициоиных широкополосных сигналов. В результате на выходах согласованных фильтров 10 появляются отклики (короткие радиоимпульсы), начальная фаза которых может принимать значения О и 180- в зависимости от передаваемого сигнала. Изменение начальной фазы в последовательностях принимаемых сигналов осуществляется по относительному закону. В приемной части устройства осуществляется когерентный оптимальный прием сигналов, для чего выделяется опорное когеретное колебание путем суммирования откликов согласованных фильтров 10 в сумматоре 18 и очищения этой суммы от шумов с помощью гребенчатого фильтра 20. Для повьшения эффективности работы гребенчатого фильтра 20 применяется обратная связь по решению со съемом манипуляции с помощью линий 21 задержки на длительность сигнала (Т k ), и блоков 17, перемножителя 19, связанных с знаковым выходом решающего блока ТЗ,

На выходе сумматора 18 появляются колебания с переменной фазой,что делает невозможной работу гребенчатого фильтра 20, осуществляющего когерентное накопление сигналов за много тактов передачи. С целью устранения фазовой манипуляции на второй вход перемножителя 19 поступают управляющие импульсы положительной или отрицательной полярности с знакового выхода решающего бхюка 13. Таким образом осуществляется съем манипуляции.

Очищенное от шумов опорное когеретное колебание с выхода гребенчатого фильтра 20 поступает на вторые входы перемножителей 11, первые входы которых соединены с выходами согласованных фильтров 10. Этим осуществляется синхронное когерентное детектирование принятых сигналов. Для борьбы с замираниями, которые проявляются в рассыпании откликов на выходе согласованных фильтров 10 (многолучевая картина), сигналы с выходов перемножителей 11 поступают на интеграторы 12, в которых осуществляется когерентное накопление лучей.

10

15

25

30

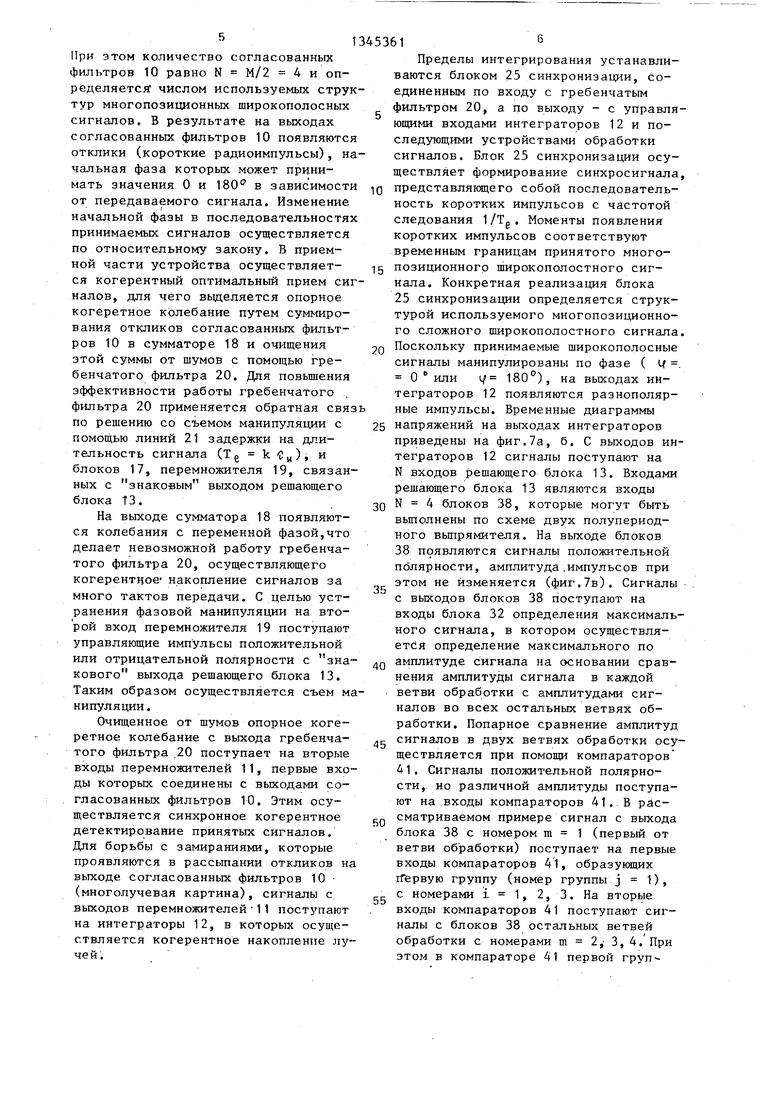

сигналов. Блок 25 синхронизации осуществляет формирование синхросигнала, представлякяцего собой последовательность коротких импульсов с частотой следования 1/Tg. Моменты появления коротких импульсов соответствуют временным границам принятого многопозиционного широкополостного сигнала. Конкретная реализация блока 25 синхронизации определяется структурой используемого многопозиционного сложного широкополостного сигнала. 20 Поскольку принимаемые широкополосные сигналы манипулированы по фазе ( Ц . О или ( 180°), на выходах интеграторов 12 появляются разнополяр- ные импульсы. Временные диаграммы напряжений на выходах интеграторов приведены на фиг.7а, б. С выходов интеграторов 12 сигналы поступают на N входов решающего блока 13. Входами решающего блока 13 являются входы N 4 блоков 38, которые могут быть выполнены по схеме двух полупериод- ного вьшрямителя. На выходе блоков 38 появляются сигналы положительной полярности, амплитуда.импульсов при этом не изменяется (фиг.7в). Сигналы с выходов блоков 38 поступают на входы блока 32 определения максимального сигнала, в котором осуществляется определение максимального по амплитуде сигнала на основании сравнения амплитуды сигнала в каждой ветви обработки с амплитудами сигналов во всех остальных ветвях обработки. Попарное сравнение амплитуд сигналов в двух ветвях обработки осуществляется при помощи компараторов 41. Сигналы положительной полярности, но различной амплитуды поступают на входы компараторов 41.. В рассматриваемом примере сигнал с выхода блока 38 с номером m 1 (первый от ветви обработки) поступает на первые входы компараторов 41, образующих хГервую группу (номер группы j 1), с номерами i 1, 2, 3. На вторые входы компараторов 41 поступают сигналы с блоков 38 остальных ветвей обработки с номерами m 2, 3,4. При этом в компараторе 41 первой груп35

40

45

50

55

5

5

0

сигналов. Блок 25 синхронизации осуществляет формирование синхросигнала, представлякяцего собой последовательность коротких импульсов с частотой следования 1/Tg. Моменты появления коротких импульсов соответствуют временным границам принятого многопозиционного широкополостного сигнала. Конкретная реализация блока 25 синхронизации определяется структурой используемого многопозиционного сложного широкополостного сигнала. 0 Поскольку принимаемые широкополосные сигналы манипулированы по фазе ( Ц . О или ( 180°), на выходах интеграторов 12 появляются разнополяр- ные импульсы. Временные диаграммы напряжений на выходах интеграторов приведены на фиг.7а, б. С выходов интеграторов 12 сигналы поступают на N входов решающего блока 13. Входами решающего блока 13 являются входы N 4 блоков 38, которые могут быть выполнены по схеме двух полупериод- ного вьшрямителя. На выходе блоков 38 появляются сигналы положительной полярности, амплитуда.импульсов при этом не изменяется (фиг.7в). Сигналы с выходов блоков 38 поступают на входы блока 32 определения максимального сигнала, в котором осуществляется определение максимального по амплитуде сигнала на основании сравнения амплитуды сигнала в каждой ветви обработки с амплитудами сигналов во всех остальных ветвях обработки. Попарное сравнение амплитуд сигналов в двух ветвях обработки осуществляется при помощи компараторов 41. Сигналы положительной полярности, но различной амплитуды поступают на входы компараторов 41.. В рассматриваемом примере сигнал с выхода блока 38 с номером m 1 (первый от ветви обработки) поступает на первые входы компараторов 41, образующих хГервую группу (номер группы j 1), с номерами i 1, 2, 3. На вторые входы компараторов 41 поступают сигналы с блоков 38 остальных ветвей обработки с номерами m 2, 3,4. При этом в компараторе 41 первой груп5

0

45

50

55

7

пы с номером i 1 осуществляется сравнение амплитуд первой и четвертой ветвей обработки, в компараторе 41 с номером первой и третьей ветвей, с номером первой и второй. Для реализации такого сравнения амплитуд сигнала на первой ветви обработки с сигналами в остальных в-етвях обработки необходимо иметь три компаратора, т.е. N - 1 - компа- ратор 41. Для сравнения амплитуды сигнала второй ветви с амплитудами сигналов остальных ветвей обработки

13

используются компараторы 41, образу ющие вторую группу с номером j 2. При этом сигнал с блока 38 с номеро m 2 поступает на первые входы компараторов 41 второй группы (j 2). На вторые входы Компараторов 41 поступают сигналы от остальных блоков 38 с номерами m 3, 4. Однако сравнение сигналов в первой и второй ветвях обработки уже было произведено в компараторе 41 первой группы с номером . Следовательно, нет необходимости осуществлять сравнение сигналов этих ветвей обработки во второй группе компараторов 41, поэтому их количество в этой группе оказывается на один меньше и равно двум. В третьей группе компараторов 41 сравнение сиг- налов третьей ветви обработки с сигналами остальных ветвей осуществляется аналогичным образом. Количество компараторов 41 в этой группе . на один меньше чем во второй и, следовательно, на два меньше чем в первой, поскольку сравнение сигналов третьей ветви с сигналами первой ивто- рой ветвями обработки бьшо произведено в предьщущих первой и второй группах соответственно. При этом количество компараторов 41 в каждой группе, используемых для сравнения данной конкретной ветви обработки с остальными, на один меньше чем в предьщу- щей и в общем случае определяется по формуле k N - j, где N - количество ветвей обработки; j - номер группы, совпадающий с номером анализируемой ветви обработки. ,

На вькоде компараторов 41 появляется стандартный импульс, соответст- вукяций 1 в том случае, если амплитуда сигнала, поступакяцего на его первьй вход, больше амплитуды сигнала, поступающего на его второй

5

3453618

вход, в противном случае на выходе компаратора 41 имеет место О.

Сигналы с выходов компараторов 41 каждой j-ой группы поступают на вхо- ды элементов И 39 с номерами 1 j. Каждый из элементов И 39 имеет N 4 входов и один выход. Первые входы всех элементов И 39 подключены к вы- Q ходу блока 25 синхронизации. Поэтому на элементы И 39 поступают разрешающие короткие импульсы в моменты времени, кратные Tj . Рассмотрим принцип работы блока 32 применительно к четырем частным случаям.

Отсчет сигнала на (т 1) первом входе блока 32 максимален (т.е.

v).

На

2 1 3 1

выходе компараторов 41 первой (j 1)

группы устанавливаются логические сигналы 1, а на выходе элемента И 39 с номером 1 1 (в момент поступления синхроимпульса на его первый вход) появляется 1. При этом на всех остальных элементах И 39 с номерами 1 2, 3, 4 уста- 0.

навливается

так как к каждому

из них подключены выходы компараторов j 1 группы через элементы НЕ 40.

Отсчет сигнала на (т 2) втором входе блока 32 максимален (т.е.

V,

Vj, v v) . На вы

ходах компараторов 41 ВТОРОЙ группы (j 2) устанавливаются 1. На вы-- ходе компаратора 41 с номером первой группы (j 1) при этом О (так как Vj v). Вследствие того, что выход этого компаратора подключен к элементу И 39 .(1 2) через элемент НЕ 40, на выходе элемента И 39 (в момент поступления синхроимпульса на первый его вход) появляется 1. При этом все остальные элементы И 39 (с .номерами 1 1,3 и 4) закрыты.

Отсчет сигнала на (т 3) третьем входе блока 32 максимален (т.е. Vj V,, Vj Vj, Vj7 V,). К входам элемента И 39 с номером компаратор 41, осуществляющий сравнение третьей и четвертой ветвей обработки (т 3 и 4), подключен непосредственно, а компараторы 41, осуществляюп1ие сравнение ветвей обработки первой (т 1) с третьей (ш 3) и второй (т 2) с третьей (т 3), - через элементы НЕ 40. Поэтому в момент появления синхроимпульса на первом вхо-де И 39 (m 3) на его выходе появляется 1. При этом все остальные элементы И 39 закрыты.

+ 4 4 4 з выходах .всех компараторов 41 с номерами блока 32 присутствуют

О . Все эти компараторы (с номерами ) через элементы НЕ 40 подключены к входам элемента И 39. Поэтому в момент поступления на вход синхронизации блока 32 синхроимпульса только на выходе элемента И 39 с но- JMepoM m 4 появляется 1.

Таким образом, на одном из входов блока 32 появляется короткий импульс придем номер этого выхода соответствует номеру той ветви, на вход которой поступает сигнал максимальной амплитуды. Синхронность работы элементов И 39 обеспечивается подачей коротких синхросигналов на их первые входы. Временные диаграммы сигналов на выходах блока 32 определения максимального сигнала показаны на фиг.7г.

С выходов блока 32 короткие импульсы поступают на входы N 4 первых формирователей 33 импульсов, которые с помощью импульсов синхронизации (от блока 25 синхронизации) осуществляют формирование импульсов положительной полярности ддхительно- стью 11д 3t . Первые формирователи 33 импульсов могут быть реализованы на RS-триггерах. Выходы формирователей 33 импульсов являются выходами решающего блока 13, который выносит решение о том, в какой ветви обработки амплитуда сигнала максимальна. Временные диаграммы сигналов на выходах решающего блока 13 приведены на фиг.7д. Кроме того, решающий блок 13 выносит решение о знаке отсчета сигнала с максимальной амплитудой.

Сигналы, поступающие на входы решающего блока 13, подаются также на входы пороговых блоков 34, в качестве которых могут быть использованы, например, триггеры Шмитта. В зависимости от знаков напряжений, действующих на входах пороговых блоков 34, на его выходах устанавливаются положительные или отрицательные напряжения стандартной амплитуды Сигналы с выходов пороговых блоков поступают на первые входы элементов И 35, на вторые входы которых поступают сигналы с соответствующих выходов блока 32. При этом сигналы появляются на выходе только того элемента И 35, который относится к ветви обработки с максимальной амплитудой сигнала и полярность сигнала в которой положительна. Если полярность сигнала,поступившего с выхода порогового блока 34, отрицательна, сигнал на выходе элемента И 35 отсутствует. Выходы элементов И 35 объединяются элементом ИЛИ 36. Наличие сигнала на вьпсоде элемента ИЛИ 36

5 свидетельствуют о положительном.

знаке принятого решения блоком 13, а отстутствие - об отрицательном знаке принятого решения. Второй формирователь 37 импульсов осущест0 вляет формирование импульсов положительной и отрицательной полярности, соответствуюш 1х сигналу знак на знаковом выходе решающего блока 13. Синхронность работы второго форми5 рователя 37 импульсов обеспечивается импульсами синхронизации, посту- паюпщми на вход синхронизации блока

13и формирователя 37. Временные диаграммы сигнала на. знаковом выхо0 де решающего блока 13 представлены на фиг.8а.

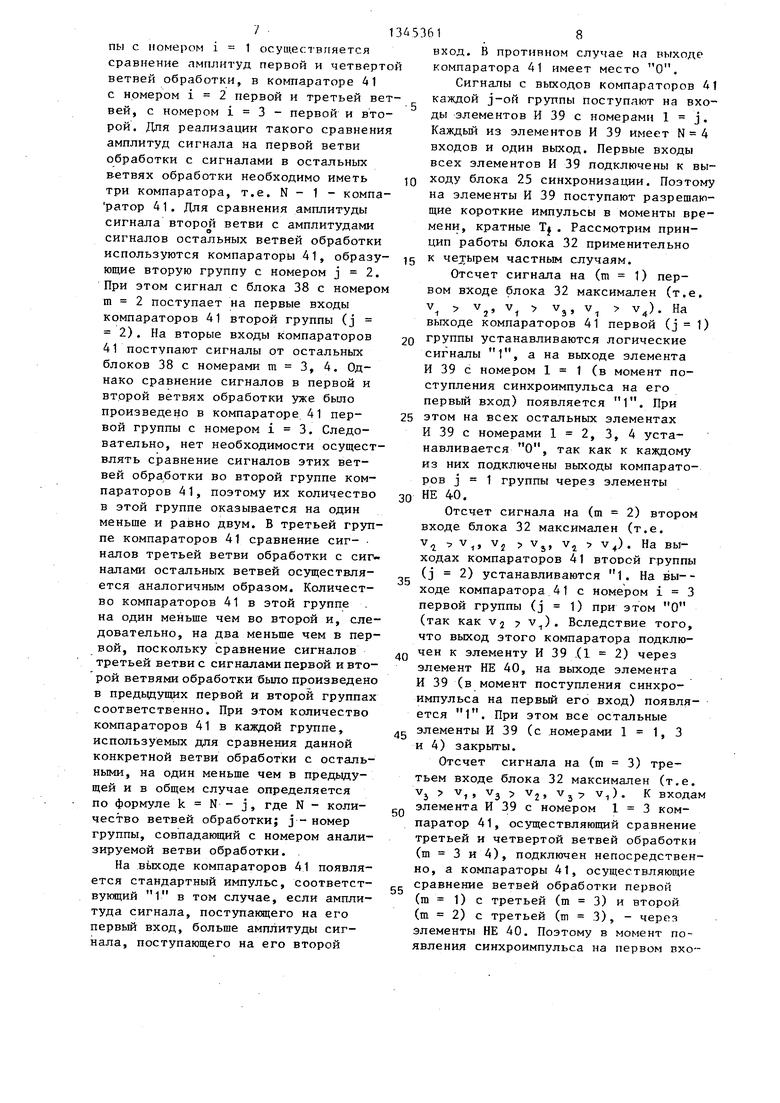

С N выходов решающего блока 13 сигналы, несущие в себе информацию о том, в какой из N ветвях обработки максимальный сигнал, поступают на входы преобразователя 14 сигналов. На выходе преобразователя 14 сигналов в соответствии с номером его входа, на который поступает сигнал с рещаклцего блока 13,-формируется соответствующая кодовая комбинация. При этом на выходе преобразователя

14сигналов формируется одна из первых четырех кодовых комбинаций, веденных в таблице. Вид кодовой комбинации определяется структурой принятого многопозиндонного широкополосного сигнала. Преобразователь 14 сигналов н6 учитывает знак или начальную фазу ( (/ 180°), с которым бьт передан многопозиционный сигнал и не обеспечивает формирование остальных четырех кодовых 1Гомбинаций, которые являются инвертированными по отношению к пер- вьш четырем кодовым комбинациям (см.табл.). Временные диаграммы сигналов на выходе преобразователя сигналов приведены на фиг.86. Кодовые

5

0

0

55

, комбинации с выхода преобразователя 14 сигналов поступают на первый вхо знакового перемножителя 15. Второй вход знакового перемножителя 15 соединен через последовательно соединенные преобразователь 23 относительного кода в абсолютный и первый элемент НЕ 24 со знаковым входом решающего блока 13.

В связи с тем,, что в предлагаемо устройстве используется относительная фазовая манипуляция, информация о знаке передЭваемого сигнала на выходе решающего блока 13 представлена в относительном коде. Поэтому для окончательного получения на выходе приемного устройства последовательности двоичных информационных символов, передаваемой при помощи многопозиционных широкополосных сигналов с относительной фазовой манипуляцией, необходимо двоичную последовательность, поступающую со знакового выхода решающего блока 13, представить в абсолютном коде, а затем с противоположным знаком перемножить с последовательностью импульсов, получаемой на выходе преобразователя 14 сигналов. Преобразователь 23 относительного кода в абсолютный производит сравнение полярностей двух соседних двоичных символов, если при этом полярности сравниваемых импульсов одинаковы, то на выходе формируется импульс с положительной полярностью. Если сравниваемые импульсы имеют различные, полярности, на выходе преобразователя 23 формируется отрицательный импульс. Временные диаграммы последовательности импульсов на выходе преобразователя 23 относительного кода в абсолютньш приведена на фиг.8в. На выходе первого элемента НЕ 24 эта последовательность импульсов инвертируется (фиг.Зг). Знаковый перемножитель 15 производит сравнение полярностей поступающих на два его входа импульсов. Если эти полярности совпадают то на выходе формируется положительный импульс, если сравниваемые полярности не совпадают, то на выходе блока 15 формируется импульс отрицательной полярности. В результате сравнения полярностей импульсных.последовательностей, поступаюпшх с выхода преобразователя 14 сигналов.(фиг.86) и с

0

15

0

выхода первого элемента НЕ (фиг.8г), на выходе знакового перемножителя 15 формируется выходная информационная импульсная последовательность (фиг.8д).

Формула изобретения

1. Устройство для передачи и приема многопозиционных широкополосных сигналов, содержащее на передающей стороне последовательно соединенные выделитель тактовой частоты, вход которого является входом устройства, и дели Гель тактовой частоты, выход которого соединен с йервым входом блока преобразования сигналов, N формирователей многопозиционных широкополосных сигналов, где N - любое целое число, выходы которых соединены с соответствующими входами выходного сумматора, а также радиопередатчик, а на приемной стороне - широкополос- 5 ный приемник, вход которого соединен с объединеннь1ми входами параллельно включенных ветвей обработки сигналов, каждая из которых содержит последовательно соединенные согласованный фильтр, перемножитель и интегратор, при этом выходы интеграторов N ветвей обработки сигналов подключены к соответствующим входам решающего блока, каждый из N выходов которого соединен с соответствующим входом преобразователя сигналов и входом соответствующего формирователя стробирующего на-- пряжения, блок формирования опорного сигнала, элемент НЕ и блок синхронизации, вход которого соединен с выходом блока формирования опорного сигнала и вторыми входами перемножителей N ветвей обработки сиг- налов, а выход соединен с входом синхронизации решающего блока и управляющими входами интеграторов N ветвей обработки сигналов, выходы согласованных фильтров соединены с соответствующими первыми входами блока формирования опорного сигнала, отли чающееся тем, что, с целью повышения помехоустойчивости на передающей стороне введены последовательно соединенные преобразователь абсолютного кода в относительный и фазовый манипулятор, вход и выход которого соединены сооответст- венно с выходом выходного сумматора и входом радиопередатчика, при этом

0

5

0

5

0

6

вход и выход выделителя тактовой частоты соединен с вторым и третьим входами блока преобразования сигналов соответственно, выходы которого соединены с входами соответствующих формирователей многопозиционных широкополосных сигналов, а знаковый выход блока преобразования сигналов соединен с входом преобразователя абсолютного кода в относительный, а на приемной сто

роне введены преобразователь относительного кода в абсолютный, выход которого через элемент НЕ соединен с первым входом введенного знакового перемножителя, выход которого является выходом устройства, а второй вход соединен с выходом преобразователя сигналов, при этом дополнительный вход блока формирования опор ного сигнала соединен с знаковьм выходом решающего блока и входом преобразователя относительного кода в абсо- лютный, а выходы формирователей стро бирующего напряжения соединены с вторыми входами блока формирования опорного сигнала.

2. Устройство ПОП.1, отличающееся тем, что блок формирования опорного сигнала содержит последовательно соединенные линии задержки, входы которых являются первыми входами блока формирования опорного сигнал.а, блоки стробирования, :сумматор, перемножитель, выход которого является вторым выходом блока формирования опорного сигнала, и гребенча:тый фильтр, выход которого является первым выходом блока формирования опорного сигнала, при этом вторые входы блоков стробирования являются вторыми входами блока формирования опорного сигнала.

3. Устройство ПОП.1, отличающееся тем, что решающий блок содержит N блоков вьщеления абсолютных значений напряжений, блок определения максимального сигнала, N первых формирователей импульсов, N пороговых блоков, N элементов И, элемент ИЛИ и второй формирователь импульсов, при этом входы блоков

5

10

15

20

- -- 25

3453611

выделения абсолютных значений напряжений соединены с входам соответствующих пороговых блоков и являются входами решающего блока, выходы пороговых блоков через соответствующие элементы И подключены к соответствующим входам элемента ИЛИ, вы ход которого соединен с входом второго формирователя импульсов, выход которого является знаковым выходом рещающего блока, причем выходы блоков выделения абсолютных значений напряжений через блок определения максимального сигнала соединены с входами соответствующих первых формирователей импульсов, выходы которых являются выходами решающего блока, входы синхронизации второго формиро - вателя импульсов, первых формирователей импульсов и блока определения максимального сигнала соединены и являются входом синхронизации решающего блока, вторые; входы элементов И соединены с соответствуюш;ими выходами блока определения максимального сигнала.

фиг. 2

фиг.З

„Знан

фиЗЛ

Сини

II

. м I л I . .(yl «A I

j-/

ttftF

I и и г

+/44

-ХД

Тип

«A I

ХД -XJ

-/«г- Ai

+/

Г4

TT

Тип 11

II KM П I

/

I Ч-ХЗ I -b xtf I- Xf I + I

II

Фиеб

1 1 1 11 J J 1 а ИМ О

гпгтиги

Редактор С.Лисина

Составитель Н.Лебедянская

Техред И.ПоповичКорректор С.Черни

Заказ 4932/55 Тираж 635Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,Ж-35, Раушская наб., д.4/5

Произвопственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

I

I

Изобретение м.б. использовано в многолучевых линиях тропосферной, ионосферной и др. связей при передаче дискретных сообщений. С целью повьшения помехоустойчивости на передающей стороне введены последовательно соединенные преобразователь абсолютного кода в относительный и фазовый манипулятор, а на приемной стороне - преобразователь относительного кода в абсолютный. В пп.2 и 3 ф-лы соответственно дано устр- во блока формирования опорного сигнала и решающего блока. 2 з.п. ф-лы, 1 табл., 8 ил. СП ОС О5

| УСТРОЙСТВО для ПЕРЕДАЧИ-ПРИЕЛ1А СОСТАВНЫХ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1971 |

|

SU428564A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-10-15—Публикация

1986-03-24—Подача