Изобретение относится к области электрорадиоизмерений и может быть использовано при построении быстродействующих вольтметров переменного напряжения, амплитудных демодуляторов, амплитудных анализаторов и др.

Известен измеритель, содержащий аналоговое запоминающее устройство, дифференциатор, блок управления и цифровой вольтметр постоянного тока, вход которого соединен с выходом аналогового запоминающего устройства, вход которого является входом измерителя, выходом которого служит выход цифрового вольтметра постоянного тока, управляющий вход которого соединен с выходом блока управления, вход которого соединен с выходом дифференциатора, вход которого объединен со входом аналогового запоминающего устройства, управляющий вход которого подключен к выходу блока управления [1].

Измеритель работает по принципу преобразования переменного напряжения в постоянное и далее измерения непосредственно постоянного напряжения, значение которого предполагается равным амплитуде исследуемого переменного (гармонического) напряжения.

При этом точность измерения в значительной степени зависит от точности выделения аналоговым запоминающим устройством амплитудного значения процесса и от способности сохранять его неизменным в течение цикла измерений, что следует отнести к недостатку измерителя. Другим недостатком измерителя является необходимость использования в его структуре автономного вольтметра постоянного тока, который, собственно, и измеряет напряжение и вносит дополнительные погрешности, величина которых определяется совершенством его конструкции. В целом, в структурном отношении измеритель получается достаточно сложным и содержит ответственные аналоговые узлы, в значительной степени влияющие на результат измерений. Кроме того, принцип действия измерителя не предусматривает вычисление средних и среднеквадратических значений исследуемых процессов.

Наиболее близким по технической сущности и достигаемому эффекту к заявляемому изобретению является измеритель, содержащий аналоговый коммутатор, два аналогово-цифровых преобразователя (АЦП), арифметический блок, блок управления, делитель напряжения, мультиплексор, элемент ИЛИ-НЕ и элемент 2И, причем вход аналогового коммутатора соединен с первым входом блока управления и является информационным входом измерителя, первый выход аналогового коммутатора подключен ко входу первого АЦП, выходы блока управления подключены к соответствующим управляющим входам первого АЦП, арифметического блока и к первому управляющему входу аналогового коммутатора, который соединен со входом делителя напряжения, вход управления второго АЦП подключен ко входу управления первого АЦП, первый и второй входы мультиплексора соединены соответственно с выходами первого и второго АЦП, а выход мультиплексора подключен ко входу арифметического блока, выход которого является выходом измерителя, выход элемента ИЛИ-НЕ соединен с адресным входом мультиплексора и первым входом элемента 2И, выход которого подключен ко второму управляющему входу аналогового коммутатора, а второй вход - к соответствующему выходу блока управления [2].

Измеритель позволяет вычислять, по измеренным в течение периода отсчетам, среднее и среднеквадратическое значения исследуемого гармонического процесса. Однако, учитывая, что указанные величины и амплитуда гармонического процесса связаны между собой через постоянный коэффициент пропорциональности, то измеритель-прототип может быть использован и для вычисления амплитудных значений.

К недостатку прототипа следует отнести сложность как в структурном, так и в функциональном отношении. В частности, требуется применение АЦП, параметры которых являются определяющими для результирующих характеристик измерителя. Кроме того, в устройстве применены достаточно сложные блок управления и арифметический блок, причем последний призван возводить в квадрат, суммировать с запоминанием промежуточных результатов и извлекать квадратный корень.

Технический результат, достигаемый при использовании настоящего изобретения, заключается в упрощении измерителя.

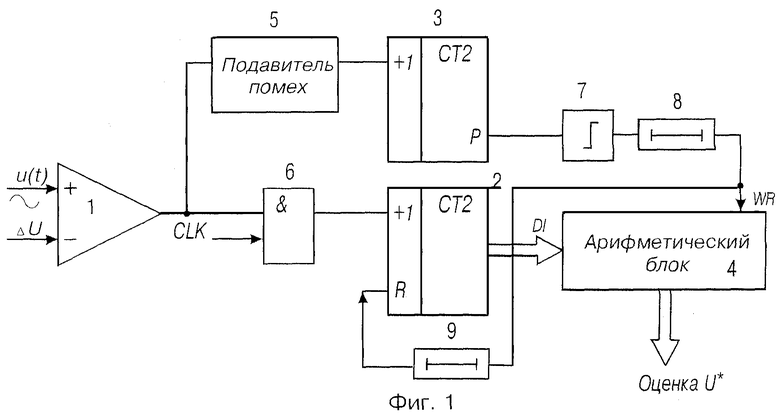

Технический результат достигается тем, что в известный измеритель амплитуды гармонических процессов, содержащий арифметический блок и элемент 2И, причем выход арифметического блока является выходом измерителя, согласно изобретению введены компаратор, два счетчика, подавитель помех, одновибратор, два элемента задержки, сигнальный вход компаратора является информационным входом измерителя, вход опорного напряжения компаратора является входом порогового уровня измерителя, выход компаратора соединен со входом подавителя помех и с первым входом элемента 2И, выход которого соединен с суммирующим входом первого счетчика, выход подавителя помех соединен с суммирующим входом второго счетчика, выход переполнения которого соединен с запускающим входом одновибратора, выход которого через последовательно включенные первый и второй элементы задержки соединен с обнуляющим входом первого счетчика, разрядные выходы которого подключены к соответствующим разрядным информационным входам арифметического блока, вход записи которого соединен с выходом первого элемента задержки, тактовым входом измерителя служит второй вход элемента 2И.

Кроме того, для повышения быстродействия измерителя в него может быть добавлен двухполупериодный выпрямитель, положительный выход которого соединен с сигнальным входом компаратора, а вход является информационным входом измерителя.

Сущность изобретения поясняется функциональными схемами и временными диаграммами.

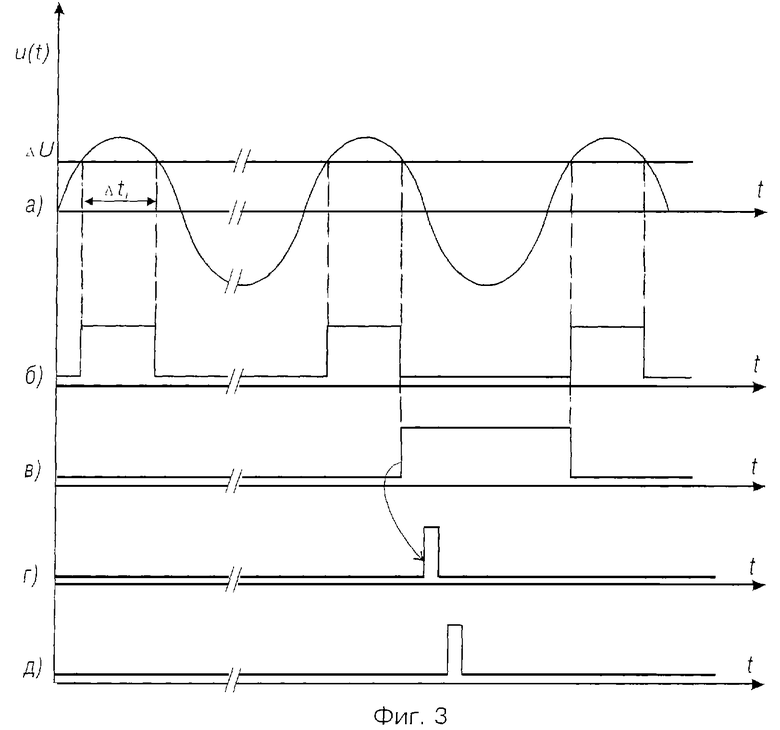

На фиг.1 приведена функциональная схема измерителя; на фиг.2 - функциональная схема арифметического блока (пример исполнения); на фиг.3 - временные диаграммы, иллюстрирующие работу устройства.

Измеритель (фиг. 1) содержит компаратор 1, первый и второй счетчики 2 и 3, арифметический блок 4, подавитель 5 помех, элемент 2И 6, одновибратор 7, элементы 8 и 9 задержки. Сигнальный вход "+" компаратора 1 является информационным входом u(t) измерителя, вход "-" опорного напряжения компаратора 1 является входом порогового уровня ΔU измерителя, выход компаратора 1 соединен со входом подавителя 5 помех и с первым входом элемента 2И 6, выход которого соединен с суммирующим входом счетчика 2, выход подавителя 5 помех соединен с суммирующим входом счетчика 3, выход переполнения которого соединен с запускающим входом одновибратора 7, выход которого через последовательно соединенные элементы 8 и 9 задержки соединен с обнуляющим входом счетчика 2, разрядные выходы которого подключены к соответствующим разрядным входам DI арифметического блока 4, вход записи WR которого соединен с выходом элемента 8 задержки, таковым входом CLK измерителя служит второй вход элемента 2И 6, а выходом измерителя является выход арифметического блока 4.

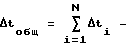

Арифметический блок 4 (фиг.2) содержит буферный регистр 10 и перепрграммируемое постоянное запоминающее устройство (ППЗУ) 11, разрядные адресные входы которого соединены с соответствующими разрядными выходами регистра 10, многоразрядный вход DI параллельной загрузки которого является информационным входом DI блока 4, выходом которого является многоразрядный информационный выход DO ППЗУ 11, а входом WR записи блока 4 служит тактовый вход регистра 10.

Временные диаграммы (фиг.3) содержат: измеряемый синусоидальный сигнал u(t)= U sin ωt, где U - амплитуда; ω - циклическая частота; t - текущее время, и пороговый уровень ΔU (фиг.3а); импульсы (фиг.3б) на выходе компаратора 1; импульс (фиг.3в) переполнения на выходе переполнения Р счетчика 3; импульс (фиг. 3г) на выходе элемента 8 задержки; импульс (фиг.3д) на выходе элемента 9 задержки.

Измеритель (фиг.1) работает следующим образом.

На вход u(t) подается сигнал u(t)=U sinωt, амплитуда U которого подлежит измерению, а на вход ΔU, который является входом опорного напряжения компаратора 1, пороговый уровень ΔU (фиг.3а). Причем ΔU<U и ω- const. Формируемые на выходе компаратора 1 прямоугольные импульсы (фиг.3б) имеют длительность Δt, равную времени пребывания сигнала u(t) над уровнем ΔU и зависящую от амплитуды U. Полученные таким образом информационные импульсы разрешают прохождение счетных (тактовых) импульсов со входа CLK на суммирующий вход счетчика 2, который подсчитывает количество счетных импульсов за время, равное времени действия N информационных импульсов с выхода компаратора 1. По окончании N-го импульса (фиг.3в) на разрядных выходах счетчика 2 будет зафиксирован код, соответствующий суммарной длительности N импульсов, формируемых компаратором 1.

Подсчет количества прошедших информационных импульсов ведется счетчиком 3, коэффициент пересчета которого выбирается таким образом, что по истечении последнего, N-го, импульса появляется признак переноса (переполнения) на его соответствующем выходе (фиг. 3в). Возникший импульс переполнения ограничивается одновибратором - формирователем передних фронтов и после дополнительного сдвига во времени (фиг.3г) элементом 8 задержки поступает на записывающий вход WR арифметического блока 4, разрешая запись кода с разрядных выходов счетчика 2 по входу DI в блок 4. По истечении времени, необходимого для записи информации в арифметический блок 4, счетчик 2 обнуляется укороченным импульсом переполнения (фиг. 3д), поступающим через элемент 5 9 задержки. Разумеется, время задержки элемента 9 не должно быть меньше времени, необходимого для завершения всех переходных процессов в блоке 4, связанных с записью информации со входа DI.

После обнуления счетчика 2 измеритель переходит в режим ожидания очередного, нового цикла измерений, который начинается с появлением очередного информационного импульса на выходе компаратора (фиг.3б), который и завершает формирование импульса переполнения (фиг. 3в) счетчика 3 (задний фронт импульса переполнения счетчика 3 совпадает с передним фронтом первого после формирования импульса переполнения импульса на входе компаратора).

В устройстве реализован принцип измерения амплитуды гармонического сигнала, суть которого состоит в том, что измерение амплитуды U при постоянной частоте ω сводится к измерению некоторого интервала времени Δt, ширина которого определяется временем пребывания сигнала u(t) над порогом ΔU и находится в строгой функциональной зависимости от искомой амплитуды U:

U = ΔUcos-1(ωΔt/2). (1)

Вычислять указанную функцию U=f(Δt) и призван арифметический блок 4, за тем исключением, что вместо значения интервала Δt в вычислении участвует оценка Δt*- усредненное значение

- длительность i-го измеренного интервала). Необходимость усреднения главным образом вызвана влиянием помех, неизбежных в реальных условиях и приводящих к смещению во времени моментов срабатывания компаратора 1, что в результате приводит как к искажениям длительностей информационных импульсов, так и к появлению коротких паразитных импульсов, сосредоточенных в окрестностях пересечения процессом U(t) порога ΔU. Учитывая, что длительности паразитных импульсов, возникающих в указанные интервалы времени, как правило, достаточно малы по сравнению с длительностью информационных импульсов, то к существенным искажениям длительности Δti они привести не могут. Однако количество паразитных импульсов может быть подсчитано счетчиком 3 одновременно с количеством и информационных импульсов, в результате чего относительная ошибка измерения количества периодов u(t), необходимых для определения границ интервала накопления-усреднения, может быть весьма существенной (на каждый информационный импульс может приходиться по несколько паразитных импульсов в случае перехода границы ΔU при dU(t)/dt>0 и при переходе границы при dU(t)/dt<0). Именно по этой причине в состав измерителя и введен подавитель 5 помех, который должен воспрепятствовать прохождению помеховых импульсов на суммирующий вход счетчика 3. Такие подавители достаточно известны, одним из простых примеров может служить фильтрующая высокочастотные составляющие замедляющая RC-цепъ [Хоровиц П., Хилл У. Искусство схемотехники. - М.: Мир, 1984, т.2, с. 47-48].

Как было показано выше, арифметический блок 4 вычисляет функцию от усредненного значения Δt*, средней длительности временных интервалов за время, равное N интервалам (периодам сигнала u(t)). Следовательно, зависимость между информационным входом DI арифметического блока 4 и выходом оценки U* будет иметь вид

где  суммарная длительность N временных интервалов, закодированная на разрядных выходах счетчика 2.

суммарная длительность N временных интервалов, закодированная на разрядных выходах счетчика 2.

Вычисление функции (2) относительно просто реализуется аппаратно-табличным методом путем записи, например, в ППЗУ набора возможных результатов U* при заданном объеме значений Δtобщ, исходя из дискрета вычислений указанной длительности. При k разрядах счетчика 2 в ППЗУ записывают предварительно вычисленные 2k значений искомой функции (2) по адресам, двоичный код которых является кодом аргумента этой функции. Таким образом, структура арифметического блока 4 сводится к буферному регистру 10 с параллельным вводом и выводом данных и запоминающему устройству 11 (фиг.2).

При реализации измерителя в качестве счетчика 3 могут быть использованы счетчики типа 555ИЕ7 при подключении дополнительно к выходу переноса (выв. 12) инвертора, так как выход переполнения у данного счетчика является инверсным. Одновибратор 7 реализуется на микросхемах типа 555АГЗ или 555АГ4. Элемент 8 задержки необходим для сдвига во времени импульса записи WR на время, необходимое для завершения переходных процессов в счетчике 2, при переходе его в последнее состояние под действием последнего счетного импульса.

Быстродействие измерителя может быть повышено за счет обработки не только положительных, но и отрицательных полуволн. Для этого на вход измерителя следует подавать измеряемое напряжение после двухполупериодного выпрямителя, выделяющего модуль процесса: |Usinωt|. Особенностью такого способа подачи входного сигнал является дополнительное падение измеряемого входного напряжения на диодах выпрямителя, что необходимо учитывать при измерениях. Кроме того, при выборе суммарного времени задержки в элементах 8 и 9 следует исходить из минимальной возможной паузы между импульсами на выходе компаратора 1, скважность которых при двухполупериодной обработке резко сокращается.

Среднее и среднеквадратическое значения исследуемого переменного напряжения вычисляют исходя из известной для гармонических процессов взаимосвязи между амплитудой и указанными величинами путем умножения найденного значения амплитуды на соответствующий постоянный коэффициент, например путем его задания в арифметическом блоке.

Источники, принятые во внимание

1. Куликовский К.Л., Купер В.Я. Методы и средства измерений. - М.: Энергоатомиздат, 1986, с. 217-218, рис.5.14.

2. А.с. СССР 1647425, G 01 R 19/00. Опубл. в БИ 17, 1991г. (прототип).

Использование: при построении быстродействующих вольтметров переменного напряжения, амплитудных демодуляторов, амплитудных анализаторов и др. Технический результат заключается в упрощении измерителя, включая сокращение аналоговых узлов. Измеритель содержит входной компаратор, два счетчика, арифметический блок, подаватель помех, элемент 2И, одновибратор и два элемента задержки. Принцип действия измерителя заключается в формировании из измеряемого синусоидального напряжения прямоугольных импульсов, длительности которых определяются моментами пересечения исследуемым сигналом порогового уровня в пределах одной полуволны. Длительность полученных указанным образом импульсов находится в строгой функциональной зависимости от амплитуды процесса. 1 з.п.ф-лы, 3 ил.

| Цифровой вольтметр переменного напряжения | 1988 |

|

SU1647425A1 |

| RU 94038816 A1, 27.05.1997 | |||

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2176088C1 |

| Устройство для бесконтактного измерения амплитуды импульсных сигналов | 1986 |

|

SU1396072A1 |

| Способ извлечения гумусовых веществ из почвы | 1982 |

|

SU1076829A1 |

Авторы

Даты

2004-02-20—Публикация

2002-09-10—Подача