Изобретение относится к контрольно-измерительной технике, в частности к цифровым измерителям параметров движения с первичным преобразователем перемещения, и может быть использовано для создания высокоточных систем автоматического управления электроприводами станков с ЧПУ и промышленных роботов.

Известен способ получения информации о скорости вращения вала, заключающийся в формировании гармонических сигналов, пропорциональных синусу и косинусу угла поворота вала, определении значений производных функций сформированных гармонических сигналов, выделении и суммировании модулей полученных сигналов, формировании суммы модулей гармонических сигналов и формировании модуля сигнала скорости за счет деления суммы модулей производных функций гармонических сигналов на сумму модулей гармонических сигналов. Устройство, реализующее указанный способ, содержит преобразователь угла поворота вала, выполненный в виде СКВТ, аналоговые дифференциаторы сигналов СКВТ, схемы выделения модулей сигналов дифференциаторов и СКВТ, два блока суммирования и блок деления, выходной сигнал которого пропорционален модулю сигнала скорости [1].

Недостатком этого способа является необходимость операции дифференцирования, которая при выполнении на аналоговых элементах имеет ограниченную точность. Кроме того, при работе с СКВТ пульсации напряжения питания усиливаются блоком дифференцирования, что приводит к снижению точности устройства и ограничивает нижний диапазон измеряемых скоростей.

Известны способ и устройство для его реализации, заключающиеся в преобразовании угла поворота вала в сигналы, пропорциональные синусу и косинусу угла поворота, преобразовании этих сигналов в многофазную систему гармонических сигналов, преобразовании полученной системы сигналов в пилообразный сигнал и определении скорости его изменения за счет преобразования крутизны пилообразного сигнала в частоту импульсов, определения числа этих импульсов за фиксированный интервал времени, и использовании этого числа в качестве скорости и формировании сигнала знака скорости за счет определения очередности следования фаз в многофазной системе гармонических сигналов.

Устройство, реализующее указанный способ, содержит первичный преобразователь угловых перемещений (СКВТ, преобразователь числа фаз, подключенный к выходам СКВТ, формирователь пилообразного напряжения с входами, подключенными к выходам преобразователя числа фаз, аналоговым выходам пилообразного сигнала и кодовым выходам номера участка пилообразного сигнала, цифровой вычислитель скорости с входом, подключенным к формирователю пилообразного напряжения, и выходом параллельного двоичного кода, преобразователь "цифра-аналог" с цифровым входом, подключенным к выходу цифрового вычислителя, и входом управления знаком выходного сигнала, и определитель очередности следования фаз с входом, подключенным к выходу кодового сигнала формирователя пилообразного напряжения, и выходом, подключенным к входу управления знаком выходного сигнала преобразователя "цифра-аналог" [2].

Недостатком известных устройства и способа является ограничение верхнего диапазона измеряемых скоростей, вызванное ограниченной полосой рабочих частот элементов устройства. Для обеспечения необходимой точности измерения в нижнем диапазоне скоростей в устройстве используется "электрический редуктор" с большим коэффициентом передачи, поэтому при низкой скорости вращения вала частота счетных импульсов достигает верхней границы рабочей частоты цифрового вычислителя скорости. В силу этого указанное устройство может быть использовано только в системах регулирования скорости "тихоходных" электроприводов. Кроме того, устройство содержит большое число аналоговых элементов, к которым предъявляются повышенные требования по точности и стабильности, что затрудняет его техническую реализацию с высокими метрологическими параметрами.

Цель изобретения - повышение точности и расширение диапазона измеряемых скоростей вращения вала.

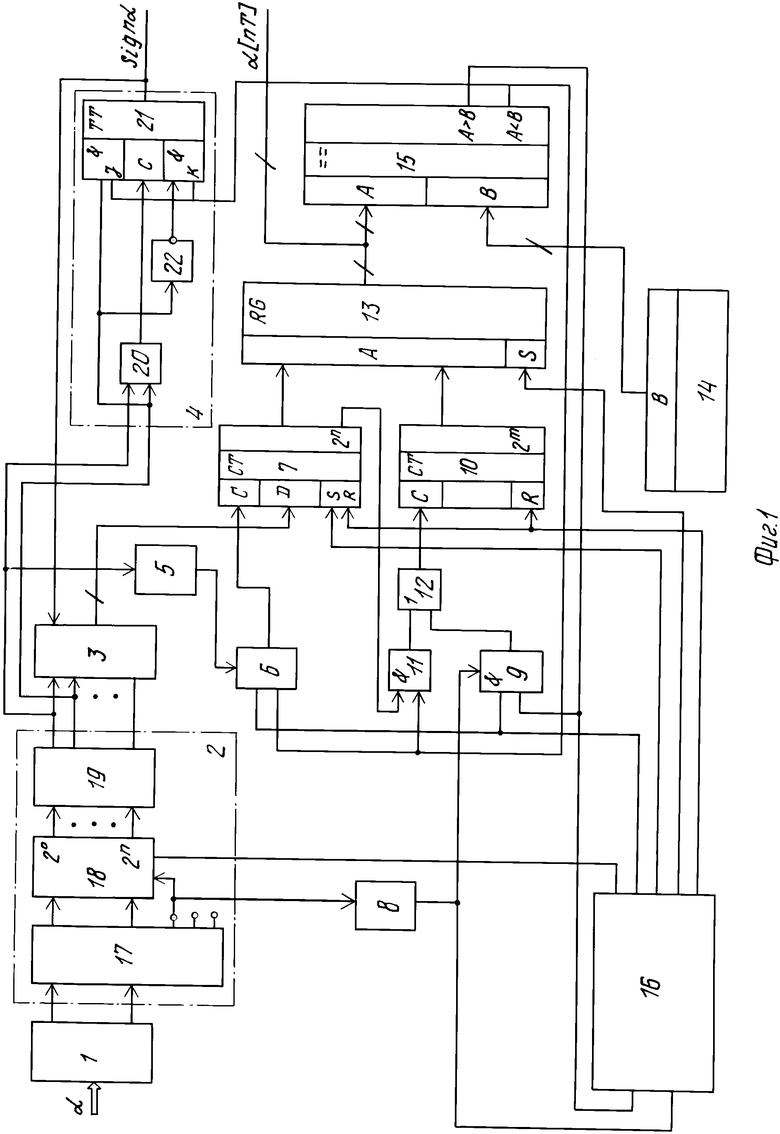

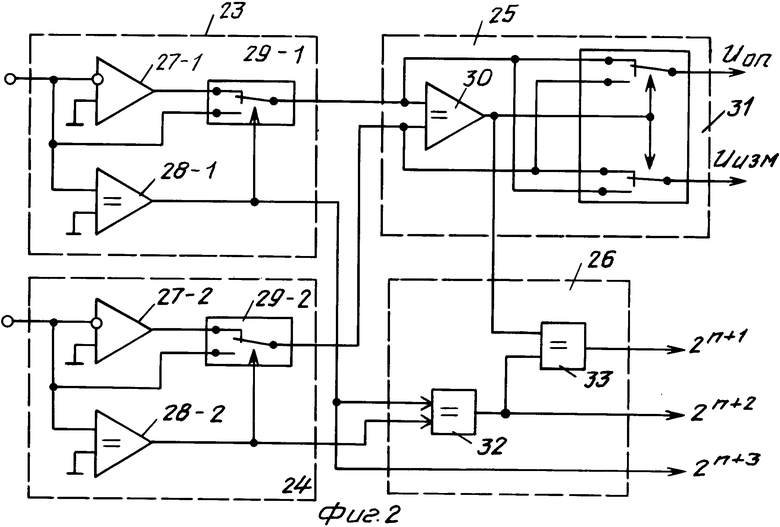

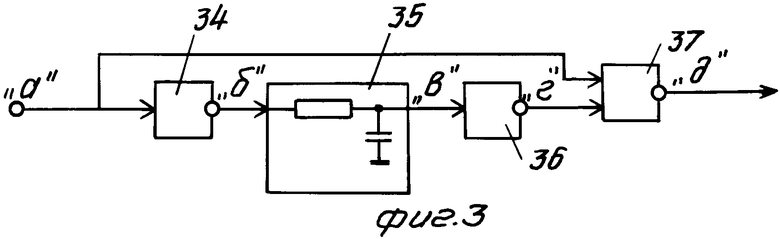

На фиг.1 приведена функциональная схема устройства для измерения скорости вращения вала; на фиг.2 - функциональная схема аналогового коммутатора; на фиг.3 - функциональная схема формирователя счетных импульсов; на фиг.4 - временные диаграммы входных и выходных сигналов элементов формирователя счетных импульсов; на фиг. 5 - функциональная схема блока управления; на фиг.6 представлены временные диаграммы входных и выходных сигналов элементов блока управления.

На функциональных схемах линии связи между элементами, осуществляющие передачу параллельного кодового сигнала, отмечены знаком Х.

Введены следующие обозначения:

α - угол поворота рабочего вала;

θ - текущее значение сигналов СКДУ;

Np - коэффициент "электрической редукции", связывающий угол с сигналом θ;

Np=2 π/Тр,

где Тр - угловой шаг измерительного растра СКДУ;

β - текущее значение угла θ СКДУ, приведенное в первый октант.

Измерение скорости вращения вала по предлагаемому способу производится в следующей последовательности.

Преобразуют угол поворота вала в двухфазную систему гармонических сигналов с помощью растрового синусно-косинусного датчика угла.

Формируют цифровой эквивалент угла θ в пределах периода гармонических сигналов следующим образом.

Преобразуют гармонические сигналы в формат первого октанта, сравнивая эти сигналы между собой и с нулевым уровнем, и одновременно определяют номер октанта (три старших разряда кода угла), соответствующий текущим значениям гармонических сигналов, при этом за первый октант (цифровой код 000) принимают октант, в котором sin θ>0, cosθ>0 и sinθ < cosθ , и считают, что возрастание номеров октантов происходит против часовой стрелки.

Преобразуют гармонические сигналы, приведенные в первый октант, в код тангенса угла путем линейного аналого-цифрового преобразования, используя в качестве опорного сигнала больший из приведенных сигналов, а в качестве измерительного - меньший из сигналов.

Используют в качестве цифрового эквивалента значения тангенса угла в нечетных октантах, когда младший разряд кода октантов равен нулю, прямой код тангенса угла, а в четных октантах, когда младший разряд кода октантов равен единице, формируют инверсный код тангенса угла.

Определяют младшие разряды кода угла, осуществляя функциональное арктангенсное преобразование кода тангенса угла в код угла, при этом нулевому входному коду тангенса угла соответствует нулевой код угла, а максимальному значению кода тангенса угла соответствует код угла: = 2n-1, где n - разрядность АЦП.

= 2n-1, где n - разрядность АЦП.

Формируют первую и вторую последовательности счетных импульсов, совпадающих с моментами изменения состояния младших разрядов кода угла и кода номера октантов.

Определяют число счетных импульсов первой последовательности за фиксированный интервал времени и используют это число в качестве значения скорости вращения вала в нижней части диапазона скоростей.

Одновременно определяют очередность следования фаз преобразователя перемещения путем определения фазового сдвига между сигналом второго младшего разряда кода угла и опорным сигналом, полученным в виде логической суммы сигналов двух младших разрядов кода угла, и формируют сигнал направления вращения вала.

При превышении измеряемой скоростью фиксированного значения определяют старшие разряды кода скорости по числу счетных импульсов второй последовательности за тот же самый интервал времени, причем отсчет интервала времени начинают в момент появления счетного импульса, и добавляют к старшим разрядам кода скорости младшие разряды, в качестве которых используют младшие разряды кода угла, сформированные в момент окончания интервала времени, при этом при вращении вала в сторону, соответствующую нарастанию кода угла θ в первом октанте, используют прямой код угла, а при вращении в противоположную сторону - обратный код угла.

В качестве сигнала направления вращения вала в верхней части диапазона скоростей используют сигнал направления вращения вала, полученный в нижней части диапазона скоростей.

Устройство для измерения скорости вращения вала, функциональная схема которого представлена на фиг.1, содержит растровый синусно-косинусный датчик 1 (СКДУ) угла с двумя выходами, преобразователь 2 "угол-код" с двумя информационными входами, подключенными к выходам СКДУ 1, входом синхронизации, трехразрядным выходом кода номера октантов и выходом n-разрядного кода угла, преобразователь 3 кода с цифровым входом, подключенным к выходу n-разрядного кода угла преобразователя 2 "угол-код", входом управления и выходом n-разрядного кода, блок 4 определения направления вращения вала с двумя информационными входами, соединенными с выходами двух младших разрядов кода угла преобразователя 2, управляющим входом и выходом, соединенным с входом управления преобразователя 3 кода и являющимся выходом сигнала направления вращения вала устройства, первый формирователь 5 счетных импульсов с информационным входом, подключенным к выходу младшего разряда кода угла преобразователя 2, первый ключ 6 с информационным входом, подключенным к выходу первого формирователя 4, двумя управляющими входами и выходом информационного сигнала, первый счетчик 7 импульсов со счетным входом (вход С), подключенным к выходу первого ключа 6, входом параллельной записи (вход D), соединенным с выходом преобразователя 3 кода, входом разрешения записи (вход S), входом установки в нулевое состояние (вход R) счетчика и выходом n-разрядного кода (выходом младших разрядов кода) скорости, второй формирователь 8 счетных импульсов с входом, соединенным с выходом младшего разряда кода номера октантов преобразователя 2, второй ключ 9 с информационным входом, подключенным к выходу второго формирователя 8, и двумя управляющими входами, второй счетчик 10 импульсов со счетным входом (вход С), входом установки

в нулевое состояние (вход R) и выходом параллельного двоичного кода (выходом старших разрядов кода скорости), логический элемент И 11 с двумя входами, первый из которых подключен к выходу старшего разряда первого счетчика 7, логический элемент ИЛИ 12 с двумя входами, подключенными к выходу второго ключа 9 и выходу логического элемента И 11, и выходом, соединенным со счетным входом второго счетчика 10, регистр 13 хранения кода (РХК) с цифровым входом, младшие разряды которого соединены с выходом n-разрядного кода первого счетчика 7, а старшие разряды регистра подключены к выходу параллельного двоичного кода второго счетчика 10, входом разрешения записи (вход S) и выходом m-разрядного кода скорости вращения вала, являющимся цифровым выходом устройства, задатчик 14 скорости переключения с выходом m-разрядного кодового сигнала, цифровой компаратор 15 с двумя входами, первый из которых (вход А) соединен с выходом регистра 13 хранения кода, а второй (вход В) подключен к выходу задатчика 14 и двумя выходами, первый из которых (выход А ≅ В) соединен с вторым управляющим входом первого ключа 6, вторым входом логического элемента И 11 и управляющим входом блока 4 определения направления вращения вала, а второй выход цифрового компаратора (выход А>B) соединен с вторым управляющим входом второго ключа 9, и блок 16 управления с двумя входами, первый из которых соединен с вторым выходом цифрового компаратора 15, а второй вход подключен к выходу второго формирователя 8 счетных импульсов, и пятью выходами, первый из которых соединен с входом синхронизации преобразователя 2, второй выход блока соединен с первыми управляющими входами первого и второго ключей, третий выход блока 16 соединен с входом разрешения записи первого счетчика 7 импульсов, четвертый выход блока 16 управления соединен с входом разрешения записи регистра 13 хранения кода, а пятый выход блока 16 управления соединен с входом установки в нулевое состояние счетчиков 7 и 10.

Преобразователь 2 "угол-код", возможный вариант реализации которого представлен на фиг. 1, содержит аналоговый коммутатор 17 с двумя входами, являющимися информационными входами преобразователя 2, выходами опорного и измерительного сигналов и выходом кода номера октантов, аналого-цифровой преобразователь 18 (АЦП) с входами опорного и измерительного сигналов, подключенными к соответствующим выходам аналогового коммутатора 17, входом управления выходным кодом АЦП 18, подключенным к выходу младшего разряда цифрового выхода кода номера октанта аналогового коммутатора 17, входом синхронизации, являющимся входом синхронизации преобразователя 2 и n-разрядным цифровым выходом, и функциональный арктангенсный преобразователь 19, выполненный в виде постоянного запоминающего устройства (ПЗУ) с адресным входом, подключенным к цифровому выходу АЦП 18. Выход кода номера октантов аналогового коммутатора 17 и цифровой выход АЦП 18 образуют цифровой выход преобразователя 2 "угол-код".

Блок 4 определения направления вращения вала, возможный вариант реализации которого представлен на фиг.1, содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20 с двумя входами, IK-триггер 21 с логическими элементами И на входах I и К, с синхронизирующим входом (вход С), подключенным к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, двумя информационными входами (входы I1 и K1) и управляющим входом, образованным соединенными друг с другом вторыми входами I2 и К2 триггера и являющийся управляющим входом блока 4, и инвертор 22 с выходом, подключенным к информационному К1-входу триггера 21.

Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 является первым входом блока 4 определения направления вращения вала, вторым входом которого является соединенные друг с другом второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, вход инвертора 22 и информационный I1-вход триггера 21. Выходом блока 4 определения направления вращения вала является выход IK-триггера 21.

Аналоговый коммутатор 17, возможный вариант реализации которого представлен на фиг.2, содержит первый блок 23 перемены знака с входом, являющимся первым входом аналогового коммутатора, и выходами аналогового и логического сигналов, второй блок 24 перемены знака с входом, являющимся вторым входом аналогового коммутатора, и выходами аналогового и логического сигналов, блок 25 перемены функций с двумя входами, подключенными к выходам аналогового сигнала первого и второго блоков перемены знака, двумя выходами аналоговых сигналов, являющимися выходами опорного и измерительного сигналов аналогового коммутатора, и выходом логического сигнала, и определитель 26 октантов с тремя входами, первый из которых подключен к выходу логического сигнала блока 25 перемены функций, а второй и третий входы определителя соединены соответственно с логическим выходом первого и второго блоков перемены знака, и выходом кода номера октантов, являющимся одноименным выходом аналогового коммутатора 17.

Блок 23 (24) перемены знака, возможный вариант реализации которого представлен на фиг.2, содержит усилитель-инвертор 27, неинвертирующий вход которого соединен с общей шиной, компаратор 28 с информационным входом, входом опорного сигнала, соединенным с общей шиной, и выходом, являющимся выходом логического сигнала блока 23 (24) перемены знака, и аналоговый переключатель 29 на одно направление с двумя информационными входами, первый из которых (нормально-закрытый контакт переключателя) соединен с выходом усилителя-инвертора 27, управляющим входом, подключенным к первому выходу компаратора 28, и выходом (общий контакт переключателя), являющимся выходом блока 23 (24) перемены знака. Соединенные друг с другом инвертирующий вход усилителя-инвертора 27, информационный вход компаратора 28 и второй (нормально-открытый контакт переключателя) информационный вход аналогового переключателя 29 является входом блока 23 (24) перемены знака. Выход логического сигнала блока 23 перемены знака является выходом старшего разряда кода номера октантов преобразователя 2 "угол-код".

Блок 25 перемены функций, возможный вариант реализации которого представлен на фиг. 2, содержит компаратор 30 с информационным входом, входом опорного сигнала и выходом, являющимся выходом логического сигнала блока 25 перемены функций, и аналоговый переключатель 31 на два направления с четырьмя информационными входами, управляющим входом, соединенным с выходом компаратора 30, выходом опорного сигнала (общий контакт первого направления переключателя), являющимся первым выходом блока 25 перемены функций, и выходом измерительного сигнала (общий контакт второго направления переключателя), являющимся вторым выходом блока 25 перемены функций. Соединенные друг с другом информационный вход компаратора 30, первый информационный вход переключателя 31 (нормально-закрытый контакт первого направления) и четвертый информационный вход переключателя (нормально-открытый контакт второго направления) являются первым информационным входом блока 25 перемены функций, а соединенные друг с другом вход опорного сигнала компаратора 30, второй информационный вход переключателя 31 (нормально-открытый контакт первого направления) и третий информационный вход переключателя 31 (нормально-закрытый контакт второго направления) являются вторым информационным входом блока 25 перемены функций.

Определитель 26 октантов, возможный вариант реализации которого представлен на фиг. 2, содержит первый логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 32 с двумя входами, являющимися вторым и третьим входом определителя 26 октантов, и второй логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33 с двумя входами, первый из которых является первым входом определителя 26 октантов, а второй вход подключен к выходу первого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 32. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 32 И 33 являются выходами второго и третьего разрядов кода номера октантов определителя 26.

Формирователь 5 (8) счетных импульсов, возможный вариант реализации которого представлен на фиг.3, содержит последовательно соединенные инвертор 34, элемент 35 задержки и развязывающий элемент 36 и логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 37 с двумя входами, второй из которых подключен к выходу развязывающего элемента 36, и выходом, являющимся выходом формирователя 5 (8) счетных импульсов. Соединенные между собой вход инвертора 34 и первый вход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 37 являются входом формирователя 5 (8).

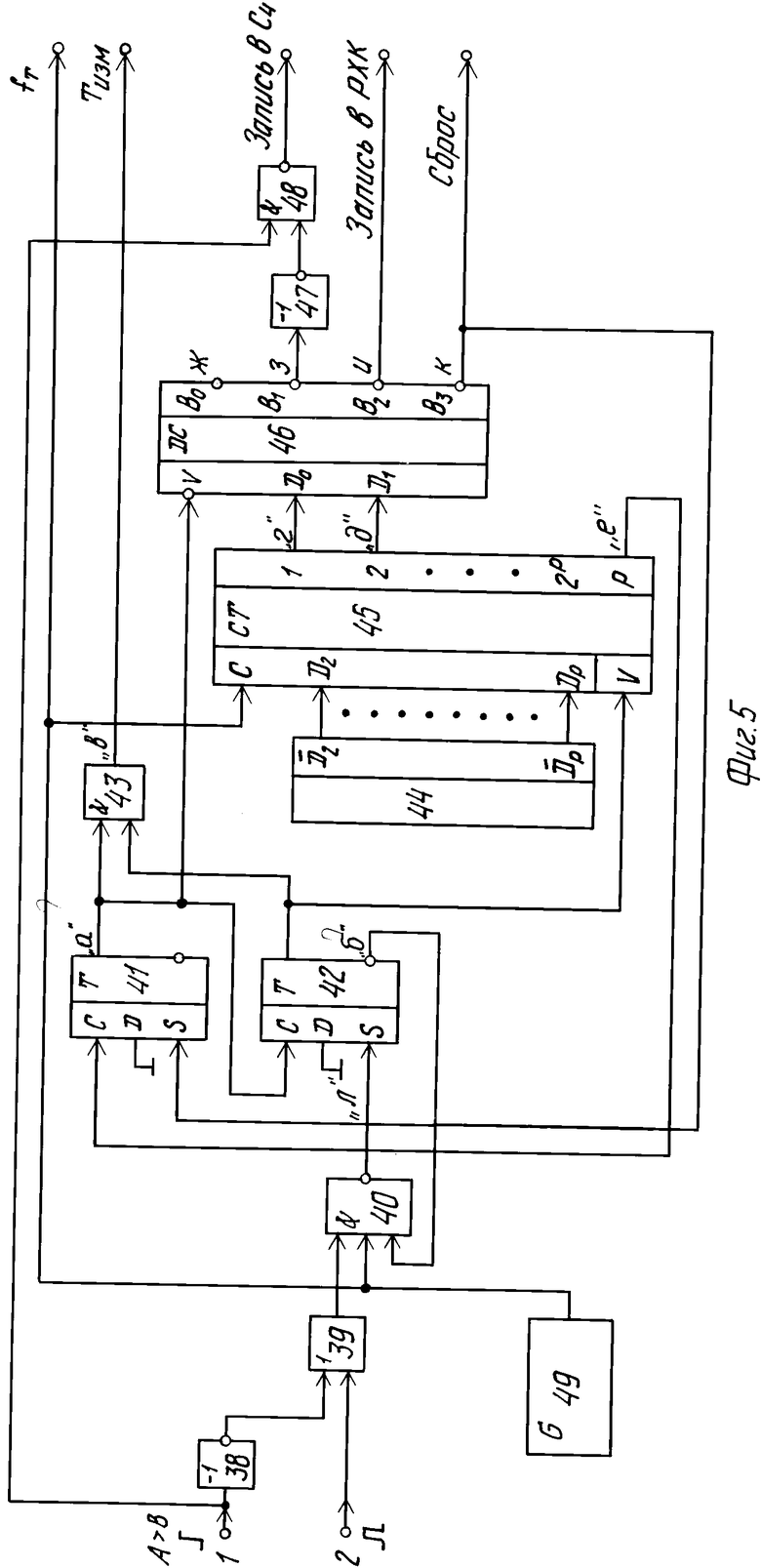

Блок 16 управления, возможный вариант реализации которого представлен на фиг. 5, содержит первый инвертор 38, логический элемент ИЛИ 39 с двумя входами, первый из которых соединен с выходом первого инвертора 38, логический элемент И-НЕ 40 с тремя входами, первый из которых соединен с выходом элемента ИЛИ 39, первый D-триггер 41 с синхронизирующим входом (вход С) и информационным входом (вход D), соединенным с общей шиной, установочным входом (вход S), второй D-триггер 42 с синхронизирующим входом, подключенным к прямому выходу первого D-триггера 41, информационным входом, соединенным с общей шиной, установочным входом, подключенным к выходу элемента ИЛИ-НЕ 40 и прямым и инверсным выходами, второй из которых подключен к третьему входу логического элемента И-НЕ 40, логический элемент И 43 с двумя входами, первый из которых подключен к прямому выходу первого D-триггера 41, а второй вход соединен с прямым выходом второго D-триггера 42, задатчик 44 фиксированного интервала времени с выходом p-разрядного параллельного кода, счетчик 45 с входом синхронизации (вход С), входом параллельной записи (вход D), соединенным с выходом задатчика 44, входом разрешения записи (вход V), соединенным с прямым выходом второго D-триггера 42, выходом двух младших разрядов и выходом переполнения (выход Р), соединенным с синхронизирующим входом первого D-триггера 41, дешифратора 46 состояния счетчика с двумя информационными входами, подключенными к первому и второму младшим разрядам счетчика 45 импульсов, управляющим входом (вход V), соединенным с прямым выходом первого D-триггера 41, и четырьмя выходами, четвертый из которых соединен с установочным входом первого D-триггера 41, второй инвертор 47 с входом, подключенным к второму выходу дешифратора 46, логический элемент И-НЕ 48 с двумя входами, второй из которых подключен к выходу второго инвертора 47, и генератора 49 импульсов с выходом, соединенным с входом тактовой частоты счетчика 45 импульсов и вторым входом логического элемента И-НЕ 40.

Соединенные друг с другом вход первого инвертора 38 и первый вход логического элемента И-НЕ 48 являются первым входом блока 16 управления, а второй вход логического элемента ИЛИ 39 является вторым входом блока 16 управления.

Выход генератора 49 является первым выходом блока 16 управления, выход первого логического элемента И-НЕ 43 - вторым выходом блока 16 управления, выход логического элемента И-НЕ 48 - третьим выходом блока 16 управления, а третий и четвертый выходы дешифратора 46 являются соответственно четвертым и пятым выходами блока 16 управления.

Устройство работает следующим образом.

Растровый СКДУ преобразует угол поворота рабочего вала в двухфазную систему гармонических сигналов. Принцип действия СКДУ основан на модуляции потока излучения, осуществляемого двумя сопряженными растрами (измерительным, связанным с рабочим валом, и анализирующим неподвижным растром). Растры имеют окна, расположенные с некоторым шагом, т.е. переменную от угла прозрачность. При мелком шаге растров сигналы фотоприемников имеют квазигармоническую форму. Фазовый сдвиг между световыми потоками осуществляется за счет выполнения анализирующего растра в виде групп штрихов, смещенных друг относительно друга по углу на четверть шага измерительного растра (плюс целое число шагов). Для получения двух квадратурных гармонических сигналов в СКДУ используется четырехфазная считывающая система, с фотоприемников которой снимаются сигналы, смещенные по фазе друг относительно друга на четверть периода. Четырехфазная система сигналов преобразуется в двухфазную, т.е. в синусный и косинусный сигналы, которые формируются за счет включения по балансной схеме фотоприемников, сигналы которых смещены по фазе друг относительно друга на половину периода. При этом устраняются постоянные составляющие и другие четные гармоники сигналов фотоприемников. При перемещении измерительного растра в одном направлении сигнал на первом выходе СКДУ отстает по фазе на четверть периода от изменения сигнала на его втором выходе, а при перемещении измерительного растра в противоположном направлении - опережает на четверть периода. Поэтому знак фазового сдвига между квадратурными сигналами СКДУ характеризует направление вращения рабочего вала. Текущее значение квадратурных гармонических сигналов, сформированных растровым СКДУ, зависящее от угла поворота θ, преобразуется преобразователем 2 "угол-код" в цифровой код угла θ. Преобразователь 2 работает в амплитудном режиме и осуществляет преобразование гармонических сигналов СКДУ в формат первого октанта с одновременным формированием трех старших разрядов кода (кода номера октанта) и затем определяет младшие разряды кода угла через код тангенса этого угла, при этом код тангенса угла формирует на АЦП 18 отношения сигналов, на опорный и информационные входы которого поступают соответственно больший и меньший из сигналов СКДУ, приведенных в первый октант.

Преобразование угла θ поворота СКДУ 1 в цифровой код в пределах одного шага измерительного растра осуществляется следующим образом.

Сигналы с выхода СКДУ 1, пропорциональные синусу (Us) и косинусу (Uc) угла θ поворота вала, поступают на входы блоков 23 и 24 перемены знака аналогового коммутатора 17. Напряжения Us=Usin θ и Uc=Ucos θ сравниваются на компараторах 28-1 и 28-2 с нулевым уровнем напряжения. В результате на выходах блоков 23 и 24 перемены знака формируются логические сигналы:

Us1=signsin θ и Uc1=sign cos θ .

Эти сигналы соответствуют знакам напряжений Us и Uc. Нулевой уровень логических сигналов Us1 и Uc1 соответствует положительному значению напряжений Us и Uc. Аналоговые переключатели 29-1 и 29-2 управляются по выявленным на компараторах 28-1 и 28-2 знакам функций Usи Uc. При нулевом уровне Us1 и Uс1 обеспечивается прямая, а при единичном - инверсная передача напряжений Us и Uc на выходы блоков 23 и 24 перемены знака через инверторы 27-1 и 27-2 соответственно. Тем самым на выходах блоков 23 и 24 перемены знака формируются модули напряжений Us и Uс, т.е.

Us2= U·/sin θ / и Uc2=U·/cos θ/, тождественные сигналам СКДУ в первом квадранте. Таким образом угол θ приводится в первый квадрант.

Напряжения Us2 и Uc2 сравниваются между собой на компараторе 30 блока 25 перемены функций, в результате чего на выходе компаратора 30 формируется логический сигнал Ua=0, если Us2<Uc2, либо Ua=1, если Us2>Uc2.

Аналоговый переключатель 31 управляется сигналом Ua и обеспечивает на выходах блока 25 перемены функций появление напряжений сигналов СКДУ, приведенных в первый октант: =

= =

=

=

=

Напряжения Uизм и Uоп поступают на информационный и опорный входы АЦП 18 отношения сигналов. АЦП осуществляет преобразование отношения напряжений, т. е. sin β/cos β =tg β , в цифровой эквивалент тангенса приведенного угла β. Таким образом, в конце цикла преобразования на цифровом выходе АЦП 18 формируется двоичный код тангенса угла β.

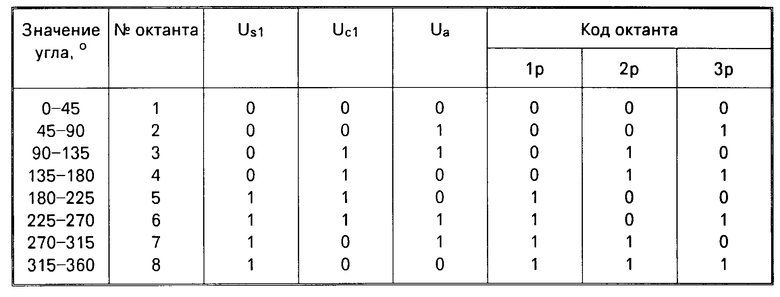

Старший разряд (1р) кода угла θ совпадает со значениями сигнала Us1. Второй (2р) и третий (3р) разряды угла θ формируются в определителе октантов, осуществляющем преобразования:

2P = Us1⊕ Uc1, 3p = 2p ⊕ Ua

Значения логических сигналов на выходе блоков 23 и 24 перемены знака и блока 25 перемены функций, соответствующие изменению угла θ в диапазоне 0-360о (в пределах одного шага измерительного растра СКДУ) приведены в таблице.

С выхода АЦП 18 цифровой код тангенса угла β поступает на адресный вход функционального арктангенсного преобразователя 19, выполненного на базе постоянного запоминающего устройства (ПЗУ), запрограммированного по закону арктангенса в диапазоне изменения угла β от 0 до 45о. ПЗУ 19 формирует на выходе цифровой код приведенного угла β, при этом нулевому входному коду tg β соответствует нулевой код угла, а максимальному входному коду tg β соответствует максимальный код N=2n-1, где n-разрядность функционального преобразователя 19.

При вращении рабочего вала выходной код приведенного угла β изменяется по линейно-треугольному закону, причем в нечетных октантах код угла β совпадает со значением угла θ в пределах октанта, а в четных октантах является инверсным значением угла θ, т.е. дополняющим угол θ до 45о. Учитывая это, для получения младших разрядов кода угла θ в четных октантах в преобразователе 2 осуществляют преобразование выходного кода АЦП 18 по сигналу младшего разряда кода номера октантов с выхода аналогового коммутатора 17, поданному на вход управления выходным кодом АЦП 18. В нечетных октантах, когда младший разряд кода номера октантов равен нулю, на выход АЦП 18 проходит прямой код угла β, а в четных октантах, когда младший разряд кода номера октантов равен единице, на выходе АЦП 18 фоpмиpуется инверсный код угла β, дополняющий угол θ до 45о, т.е. равный 45о- β. Поэтому в пределах каждого октанта формируется "цифровая пила", т.е. сигнал на выходе младших разрядов преобразователя 2 "угол-код" изменяется от нуля до значения 2n-1. Таким образом, код номера октанта и код, формируемый на выходе АЦП 18, образуют циклический код угла θ, при его изменении в пределах каждого шага измерительного растра СКДУ от 0 до 360о, т.е. преобразуют угол θ поворота вала СКДУ в его цифровой эквивалент - код.

Сигнал младшего разряда кода угла θ с выхода преобразователя 2 и сигнал младшего разряда кода номера октанта аналогового коммутатора 17 поступают на вход формирователей 5 и 8 счетных импульсов, имеющих одинаковое исполнение. Этот сигнал инвертируется инвертором 34 и подается на элемент 35 задержки, выполненный в виде интегрирующей RC-цепи. При переключениях инвертора 34 напряжение на выходе элемента 35 задержки изменяется по экспотенциальному закону. Когда напряжение на выходе элемента задержки достигает значения, равного напряжению переключения развязывающего элемента 36, последний переключается в другое состояние. Учитывая, что переключение развязывающего элемента 36 из единичного состояния в нулевое (из нулевого состояния в единичное) происходит при напряжении, равном приблизительно половине напряжения питания, импульсы на выходе развязывающего элемента сдвинуты относительно входного сигнала формирователя 5 (8) счетных импульсов на время, равное Δ t=0,7RC.

Входной и задержанный сигналы поступают на входы логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, на выходе которого на каждый входной импульс формируются два счетных импульса, передние фронты которых совпадают с передним и задним фронтами входного импульса, а длительность счетных импульсов равна времени задержки сигнала.

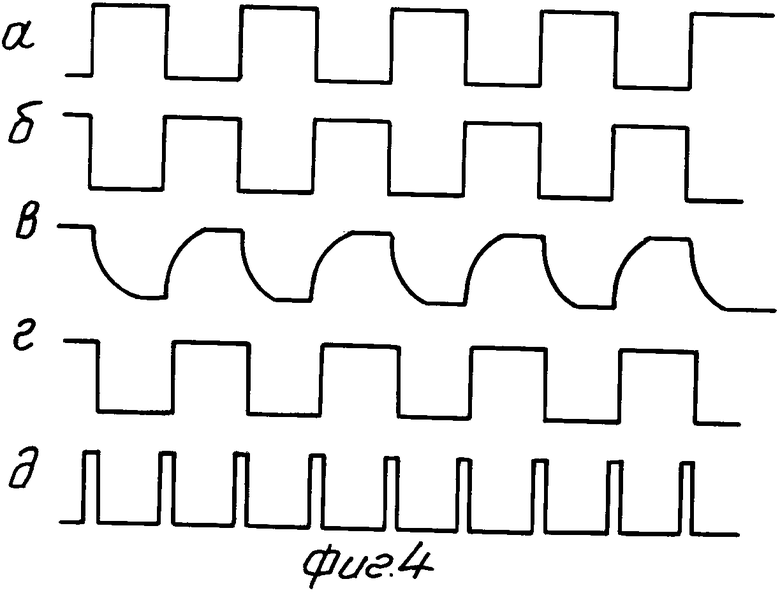

На фиг.4 представлены временные диаграммы, поясняющие работу формирователя 5 (8) счетных импульсов.

Сформированные формирователем 5 счетные импульсы поступают на информационный вход ключа 6. При работе устройства в нижней части диапазона скоростей, когда скорость рабочего вала меньше скорости, заданной задатчиком 14, на второй управляющий вход ключа 6 и второй вход логического элемента И 11 постоянно подан сигнал логической единицы с выхода цифрового компаратора 15. Ключ 6 в каждом цикле измерения открывается сигналом фиксированного интервала времени, формируемого на втором выходе блока 16 управления, на время, равное этому интервалу. В результате счетные импульсы проходят на выход ключа 6 и поступают на синхронизирующий вход счетчика 7. Счетчик 7 подсчитывает число этих импульсов. Счетчики 7 и 10 включены последовательно, поэтому импульсы переполнения счетчика 7 через логический элемент И 11 и элемент ИЛИ 12 поступают на синхронизирующий вход счетчика 10 и подсчитываются им. Так как частота счетных импульсов пропорциональна скорости вращения вала СКДУ, в конце фиксированного интервала времени в счетчиках 7 и 10 будет записано число, представляющее собой цифровой эквивалент скорости вращения вала. После окончания фиксированного интервала времени по сигналу, сформированному на четвертом выходе блока 16 управления, результат измерения из счетчиков 7 и 10 параллельным кодом переносится к регистр 13. Полученный цифровой эквивалент скорости вращения вала (число А) в каждом цикле сравнивается цифровым компаратором 15 с заданным значением кода скорости переключения (число В) задатчика 14. Если скорость вращения вала ниже заданной, то устройство продолжает работать так, как это описано выше, при этом перед началом очередного цикла счетчики обнуляются.

Определение направления вращения и, следовательно, знака кода скорости производится блоком 4. Направление вращения определяется в начале движения, т.е. при скорости вращения вала, меньшей скорости, заданной задатчиком. При превышении скорости, заданной задатчиком (А>В), результат определения знака кода скорости запоминается и используется при работе в верхней части диапазона скоростей.

Для определения направления вращения вала предварительно формируют опорный сигнал, производя с помощью логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20 логическое суммирование сигналов двух младших разрядов кода угла преобразователя 2. Полученный опорный сигнал сдвинут на четверть периода относительно сигнала второго младшего разряда кода угла. При этом фаза опорного сигнала не изменяется при изменении направления вращения вала.

Фазы сигналов второго младшего разряда кода угла и опорного сигнала сравниваются JK-триггером 21, имеющим логические элементы И на информационных входах. JK-триггер включен по схеме D-триггера и имеет управляющий вход, образованный соединенными друг с другом вторыми информационными J2 и К2-входами. Сигнал второго младшего разряда кода угла подается на информационный J1-вход JK-триггера и через инвертор 22 - на информационный вход К1, а опорный сигнал, сформированный элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 20, - на синхронизирующий вход JK-триггера 21. При подаче логической единицы на управляющий вход JK-триггера (работа устройства в нижней части диапазона скоростей) в момент формирования фронта импульса на синхронизирующем входе JK-триггер 21 фиксирует опережение или отставание сигнала, поданного на информационный J1-вход относительно опорного сигнала. При этом опорный сигнал своим фронтом переводит JK-триггер 21 в состояние, определяемое уровнем напряжения на его информационном J-входе в данный момент времени. При перемещении в одном направлении сигнал второго младшего разряда кода угла опережает по фазе опорный сигнал, вследствие чего на прямом выходе JK-тригера 21 устанавливается напряжение, соответствующее логической единице, а при перемещении в противоположном направлении сигнал второго младшего разряда кода угла будет отставать по фазе от опорного сигнала и на прямом выходе JK-триггера 21 устанавливается напряжение, соответствующее логическому нулю.

Таким образом, сигнал с прямого выхода JK-триггера 21 определяет направление вращения вала и используется в качестве сигнала знака кода скорости вращения вала.

При возрастании скорости выше скорости, заданной задатчиком 14, JK-триггер 21 переводится в режим запоминания предыдущего состояния за счет подачи логического нуля на управляющий вход блока 4 с выхода цифрового компаратора 15. Это позволяет исключить неправильную работу JK-триггера в том случае, когда частота входных сигналов, поданных на информационный и опорный входы, превышает рабочий диапазон частот JK-триггера.

При достижении рабочим валом скорости вращения, равной или большей фиксированного значения, установленного в задатчике 14, по сигналу с выхода цифрового компаратора 15 включается второй канал измерения скорости и устройство автоматически переходит на счет импульсов, сформированных формирователем 8 из сигналов третьего старшего разряда кода угла,"вес" которого соответствует октанту. Частота этих импульсов также пропорциональна скорости вращения вала СКДУ. При этом цифровой компаратор 15 блокирует работу ключа 6, устанавливая на его втором управляющем входе сигнал логического нуля, и одновременно разрешает работу ключа 9, устанавливая на его втором управляющем входе сигнал логической единицы, т.е. осуществляется переключение с первого на второй канал измерения.

Работа устройства на втором канале измерения аналогична работе на первом канале. Счетные импульсы с выхода формирователя 8 поступают на информационный вход ключа 9. Ключ 9 открывается в каждом цикле измерения сигналом фиксированного интервала времени, формируемого на втором выходе блока 16 управления. При этом начало фиксированного интервала времени совпадает с моментом появления очередного счетного импульса формирователя 8. Счетные импульсы с выхода ключа 9 поступают через логический элемент ИЛИ 12 на вход тактовой частоты счетчика 10, формирующего старшие разряды кода скорости. Счетчик 10 подсчитывает число этих импульсов, соответствующее числу целых октантов за фиксированный интервал времени, в конце которого в счетчике будут записаны старшие разряды кода скорости вращения вала.

Для формирования младших разрядов кода скорости в момент окончания фиксированного интервала времени по сигналу "Перенос", сформированному блоком 16 управления на своем третьем выходе, осуществляется трансляция информации с выхода n-разрядного кода угла преобразователя 2 через преобразователь 3 кода и ее запись в счетчик 7. При этом для использования младших разрядов кода угла θ в качестве младших разрядов кода скорости вращения вала в зависимости от направления вращения рабочего вала производится преобразование прямого n-разрядного кода угла преобразователя 2, на обратный код, осуществляемое по сигналу с выхода блока 4 определения направления вращения.

N-разрядный код угла преобразователя 2 поступает на цифровой вход преобразователя 3 кода, выполненного в виде установленных по числу разрядов кода логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых являются цифровым входом преобразователя 3 кода, а вторые входы элементов соединены друг с другом и являются его входом управления. При вращении рабочего вала СКДУ в направлении, соответствующем нарастанию кода угла θ в первом октанте, т.е. когда на управляющем входе преобразователя 3 кода сигнал равен единице, на выход преобразователя 3 транслируется прямой код угла θ, а при вращении рабочего вала в противоположном направлении сигнал на управляющем входе преобразователя 3 равен нулю и на его выход проходит обратный код угла θ. Таким образом, при вращении в любом направлении код, транслируемый на вход счетчика 7, нарастает в пределах любого октанта синхронно с изменением кода угла θ. Поэтому в момент окончания фиксированного интервала времени в счетчик 7 будет записано число, соответствующее углу поворота рабочего вала в течение времени от появления последнего счетного импульса до момента окончания фиксированного интервала времени, т.е. цифровой эквивалент соответствующей доли октанта гармонических сигналов СКДУ 1.

Сформированные младшие разряды кода скорости, записанные в счетчике 7, и старшие разряды кода скорости, записанные в счетчике 10, по команде, сформированной на четвертом выходе блока 16 управления, переносятся параллельным кодом в регистр 13.

Перед началом очередного цикла измерения счетчики 7 и 11 устанавливаются в нулевое состояние по команде "Сброс", сформированной на пятом выходе блока 16 управления.

Из приведенного выше описания видно, что измерительная часть предлагаемого устройства представляет собой цифровой частотомер. Процессом преобразования информации в устройстве управляет блок 16 управления, который формирует две импульсные последовательности, одна из которых обеспечивает режим счета импульсов за фиксированный интервал времени, а другая - режим считывания информации.

Блок 16 управления работает в двух режимах: в нижней части диапазона скоростей в режиме автогенератора; в верхней части диапазона скоростей в режиме одновибратора с запуском от сформированных формирователем 8 счетных импульсов.

Работа блока 16 управления после прихода очередного импульса "Сброс" происходит следующим образом.

Спад положительного напряжения на четвертом выходе дешифратора 46 и на входе S триггера 41 переводит триггер в единичное состояние. При этом на прямом выходе триггера 41 формируется положительный перепад напряжения, который подается на первый вход логического элемента И 43 и на вход дешифратора 46, запрещая работу дешифратора. Поэтому в момент срабатывания триггера 41 команда "Сброс" с четвертого выхода дешифратора 46 снимается и на всех его выходах устанавливается высокий потенциал. Одновременно сигнал с прямого выхода триггера 41 поступает на синхронизирующий вход С триггера 42 и устанавливает его в нулевое состояние, при этом на прямом выходе триггера 42 формируется отрицательный, а на инверсном выходе - положительный перепад напряжения.

Сигнал с прямого выхода триггера 42 разрешает параллельную запись кода с выхода задатчика 44 в счетчик 45. Обратный код фиксированного интервала времени, постоянно присутствующий на входе D счетчика 45 с выхода задатчика 44, записывается в счетчик 45. Одновременно положительный фронт сигнала с инверсного выхода триггера 42 поступает на третий вход логического элемента И 40. При работе в нижней части диапазона скоростей на первом входе блока 16 управления установлен сигнал логического нуля, поданный с первого выхода (A>B) цифрового компаратора 15. Этот сигнал инвертируется инвертором 38 и через логический элемент ИЛИ 39 подается на первый вход логического элемента И 40. Таким образом, подача положительного перепада напряжения с инверсного выхода триггера 42 на третий вход логического элемента И 40 приводит к тому, что очередной импульс генератора 49 из постоянно поступающих на второй вход логического элемента И 40 проходит на установочный вход S триггера 42 и своим передним фронтом возвращает триггер 42 в единичное состояние. Триггер 42 снимает сигнал разрешения параллельной записи с входа V счетчика 46, разрешая тем самым его работу, и формирует передний фронт импульса фиксированного интервала времени, подавая на второй вход первого элемента И 43 положительный перепад напряжения, сформированного на прямом выходе триггера. Таким образом, на второй выход блока 16 управления поступает команда, разрешающая счет импульсов счетчиком 7 устройства, и одновременно начинается счет импульсов, поступающих на вход С счетчика 46 блока управления с генератора 49, т.е. отсчет фиксированного интервала времени. Так как к выходу С счетчика 45 подключен задающий генератор 49, счетчик считает импульсы, частота следования которых fo. Поэтому уровень логической единицы на его выходе переполнения появляется через строго фиксированное время Тизм, которое определяется периодом частоты следования fo и кодом введенного в счетчик числа  . После отсчета заданного числа импульсов на выходе Р счетчика 45 появляется импульс переполнения, который переключит триггер 41 в нулевое состояние. Спад положительного напряжения на прямом выходе триггера 41 формирует задний фронт сигнала фиксированного интервала времени на выходе элемента И 43 и подает команду разрешения работы на вход V дешифратора 46.

. После отсчета заданного числа импульсов на выходе Р счетчика 45 появляется импульс переполнения, который переключит триггер 41 в нулевое состояние. Спад положительного напряжения на прямом выходе триггера 41 формирует задний фронт сигнала фиксированного интервала времени на выходе элемента И 43 и подает команду разрешения работы на вход V дешифратора 46.

При появлении импульса переполнения на выходе счетчика 45 все разряды счетчика находятся в нулевом состоянии, а поскольку сигнал разрешения записи на входе V счетчика отсутствует, счетчик продолжает считать импульсы, приходящие на его вход С. Сигналы с выходов двух младших разрядов счетчика 45 поступают на информационные входы дешифратора 46, поэтому при каждом счетном импульсе на каждом из выходов дешифратора появляются следующие друг за другом четыре импульса, длительность каждого из которых равна периоду частоты fo. Эти импульсы используются в качестве сигналов управления, обеспечивающих работу устройства в режиме считывания информации.

При появлении сигнала на четвертом выходе дешифратора 46 цикл работы блока 16 управления заканчивается.

При работе устройства в верхней части диапазона скорости вращения вала с выхода цифрового компаратора 15 на первый вход блока 16 управления поступает сигнал логической единицы, поэтому постоянно присутствовавший сигнал логической единицы на первом входе элемента И-НЕ 40 снимается. Это переводит блок 16 управления в режим одновибратора, при котором после завершения формирования команд в очередном цикле начало следующего цикла осуществляется по сигналу с выхода формирователя 8 счетных импульсов, поступающему на второй вход блока 16 управления, т.е. начало отсчета фиксированного интервала времени начнется одновременно с началом очередного октанта гармонических сигналов СКДУ 1, а в промежутке между командами "Сброс" и появлением счетного импульса блок 16 управления находится в режиме ожидания.

В этом режиме работы сигнал разрешения параллельной записи в счетчик 7 формируется путем инвертирования сигнала с третьего выхода дешифратора 46 инвертором 47 и подачи его на второй выход логического элемента И-НЕ 48, на первый вход которого подан сигнал логической единицы.

Таким образом, последовательность управляющих команд, сформированная блоком 16 управления, обеспечивает процесс преобразования информации в устройстве.

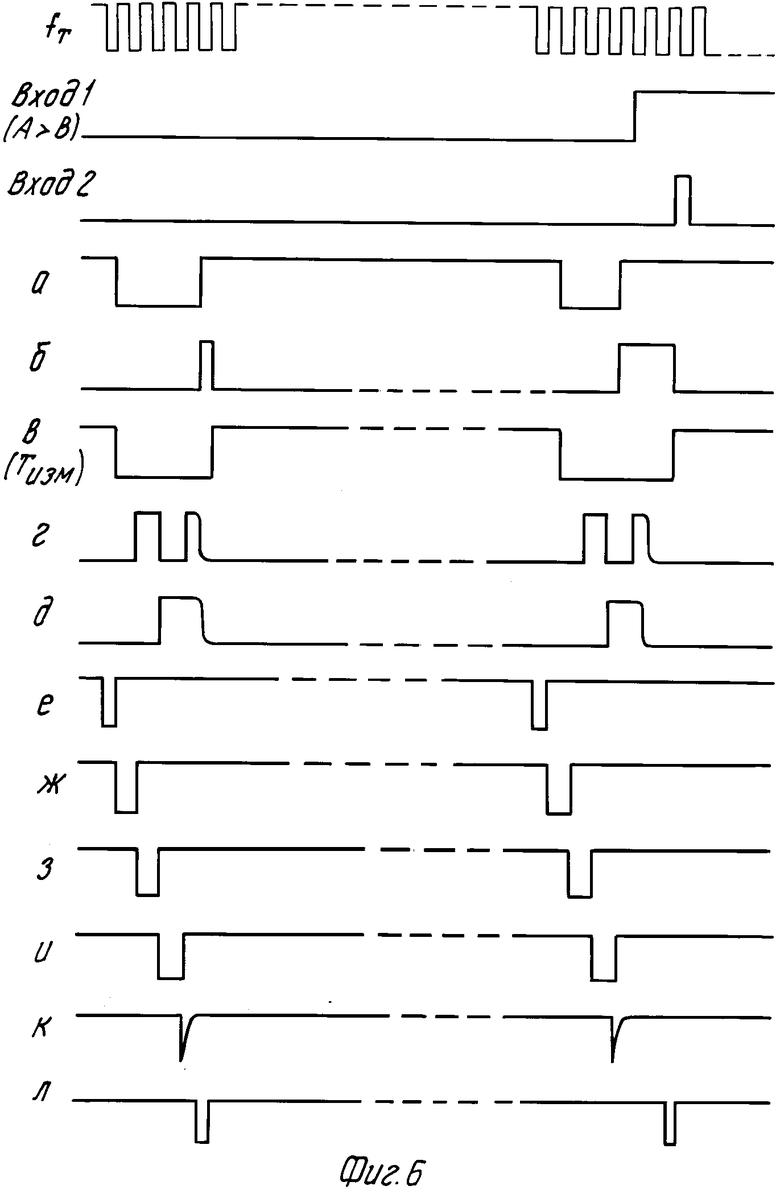

Временные диаграммы входных и выходных сигналов элементов, указанных на функциональной схеме блока 16 управления (фиг.5), поясняющие их работу, представлены на фиг.6.

Преимуществами предложенного технического решения измерения скорости вращения вала являются широкий диапазон измеряемых скоростей при высокой дискретности измерения, повышения точности измерения скорости вращения и снижение погрешности определения момента смены знака при реверсе.

Расширение диапазона измеряемых скоростей при сохранении высокой дискретности измерения достигается за счет использования второго канала измерения с большей дискретностью и одновременно использования циклического кода угла в качестве младших разрядов кода скорости в момент окончания фиксированного интервала времени.

Повышение абсолютной точности измерения при расширении диапазона скоростей достигается за счет синхронизации начала отсчета фиксированного интервала времени с моментом появления счетных импульсов.

Так как цена младшего разряда преобразователя "угол-код" сохраняется при работе во всем диапазоне скоростей, то при расширении диапазона скоростей в сторону увеличения относительная точность измерения скорости также увеличивается.

Кроме того, в предложенном устройстве существенно уменьшена динамическая погрешность определения момента смены знака скорости при реверсе за счет формирования сигнала знака скорости из сигналов двух младших разрядов циклического кода угла, имеющих высокую дискретность.

Таким образом, применение прямого преобразования сигналов растрового СКДУ с использованием преобразователя "угол-код", выполненного на основе АЦП отношения сигналов, и предложенный алгоритм обработки сигналов позволяют получить измеритель угловой скорости с широким диапазоном измерения, высокой разрешающей способностью, точностью и быстродействием при сравнительно простой технической реализации устройства на стандартной элементной базе.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МНОГОФАЗНОГО ПЕРИОДИЧЕСКОГО СИГНАЛА | 1991 |

|

RU2017063C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1991 |

|

RU2020752C1 |

| Функциональный преобразователь угла поворота вала в код | 1985 |

|

SU1309314A1 |

| Устройство для измерения перемещения объекта | 1990 |

|

SU1779923A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU748477A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1283968A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1999 |

|

RU2175812C2 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1124361A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU696516A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения скорости вращения вала. Сущность изобретения: способ, включающий преобразование угла поворота вала в двухфазную систему гармонических сигналов, преобразование двухфазной системы гармонических сигналов в циклический код угла поворота вала, формирование из этого кода первой и второй последовательностей счетных импульсов, результат подсчета импульсов первой последовательности за фиксированный интервал времени используют для определения значения скорости вращения вала в нижней части диапазона скоростей, а при превышении измеряемой скоростью заданного значения для определения скорости вращения вала используют результат подсчета импульсов второй последовательности за фиксированный интервал времени, одновременно формируют сигнал направления вращения. Устройство содержит датчик угла, преобразователь "угол-код", преобразователь кода, два формирователя счетных импульсов, два ключа, два счетчика импульсов, логический элемент И, логический элемент ИЛИ, регистр, задатчик кода фиксированной скорости, цифровой компаратор, блок управления, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, JK - триггер, инвертор. 2 с. и 1 з.п. ф-лы, 6 ил., 1 табл.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ измерения скорости вращения вала и устройство для его осуществления | 1978 |

|

SU864131A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-07-30—Публикация

1991-06-28—Подача