Изобретение относится к измерительной технике и предназначено для использования в контрольно-измерительной аппаратуре систем электро- и радиосвязи.

известно устройство для автоматического измерения амплитуды переменного сигнала, содержащее последовательно соединенные преобразователь частоты, коммутатор, усилитель промежуточной частоты, квадратичный детектор, усилитель частоты модуляции,, фазовый детектор, а также индикатор нуля и генератор опорного сигнала. Оно отличается расширенным динамическим диапазоном измерения, однако наличие в его составе детектора, отсутствие средств подавления случайных шумов и повышения быстродействия в канале измерения обуславливает невысокую точность измерения и низкую производительность при измерениях.

Известно также устройство для измерения амплитуды переменного напряжения, содержащее пиковые детекторы, установленные в каналах измерения обеих полярностей, блок регистрации, два управляемых ограничителя напряжения и два амплитудных дискриминатора, отличающееся повышенной устойчивостью к импульсным помехам, но низкой точностью и низкой производительностью из-за наличия детектирования сигнала.

Наиболее близким по технической сущности к предлагаемому устройству является селективный измеритель уровня, содержащий последовательно соединеннь1е ujnpoкополосный усилитель, блок частотного преобразования.усилитель промежуточной частоты, детекторный блок. микроЭВМ и блок индикации. Из-за нестабильности и нелинейности детектора, наличия в нем накопительной емкости, отсутствия средств подавления шумов в полосе измерения, низкой скорости обработки микроЭВМ возможности измерителя по повышению точности и быстродействия ограничены. Действительно, уменьшение случайной состяоляюи 1ей погрешности возможно только посредством увеличения количества отсчетов и их усреднения, что приводит к заметному увеличению времени измерения. Уменьшение времени одного измерения тоже невозможно, так как это должно сопровождаться уменьшением накопительной емкости детектора и, следовательно, увеличением систематической амплитудной и случайной погрешностей. Нестабильность параметров детектора, связаннуюсо старением его элементов и климатическими воздействия ми среды в измерителе невозможно устранить.

Целью настоящего изобретения является повышение точности и производительности измерителя.

Поставленная цель достигается тем. что в измерителе вместо детекторного блока и микроэвм введен аналого-цифровой преобразователь переменного тока, а также дополнительно введены блоки и узлы с их связями: блок определения начала отсчетов (БОНО) to, формирователь межпарных интервалов (ФМПИ) Т, формирователь двух парных отсчетов (ФДПО). причем отсчеты в каждой паре разделены промежутком времени Дт, 14 N-разрядных регистров для хранения отсчетов измеряемой величины, констант и промежуточных величин, связанhibix с обработкой от.счетов. блок управления записью отсчетом (БУЗО) в регистры, N-разрядный арифметико-логический блок (АЛБ), позволяющий суммировать, вычитать, умножать и устанавливать равенство поданных на его порты А и В чисел, квадратор, блок подбора корня (БПК), позволяющий рализовать процедуру вычисления корня квадратного с использованием АЛБ и квадратора, постоянный запоминающий блок (ПЗБ) и регистра управления, обеспечивающий управление работой реги-стров и других блоков при обработке отсчетов. N-разрядная шина данных и 1-я и 2-я операционные шины, обеспечивающие подключение регистров к входам и выходу АЛБ при обработке отсчетов и связанных с ней пересылках данных между регистрами, блок

управления (ВП), предназначенный для последовательной выборки команд управления из ПЗУ. 55-линейная шина управления, генератор тактовых импульсов (ГТИ). два

RS-триггера и два одновибратора с задержкой на входе.

При работе измеритель производит две пары отсчетов в течение одного-двух периодов промежуточной частоты, по которым вычисляется амплитуда а измеряемого сигнала примерно за (50+N) тактов ГТИ. Для и тактовой частоте порядка 5 МГц время вычисления амплитуды составляет 10 МКС, т.е. время измерения амплитуды при

5 промежуточной частоте 10 кГц примерно равно 100 МКС, в то время как минимальное время одного измерения равно 100 мкс, т.е. получается тысячекратное увеличение быстродействия. Увеличение точности достигается переходом от аналогового детектора к N-разрядному АЦП: при 8,..10-разрядном АЦП погрешность уменьшается в 7...15 раз. Дальнейшее увеличение точности и быстродействия измерителя связаны с выбором ве-.

5 личины Л tиз условия. корреляционной компенсации случайной погрешности, а величины Т- из условия статистической независимости двух пар.отсчетов, что дает возможность улучшить упомянутые величины во столько раз. во сколько дисперсия измерений при корреляционной компенсации меньше дисперсии измерений прототипа. Как показывают оценки. дополнительное увеличение точности и про5 изводительности возможно в сотни раз.

Других известных технических решений с признаками, сходными с признаками, отличающими заявляемое техническое решение от .прототипа, при поиске не

0 обнаружено, следовательно, заявляемое техническое решение обладает существенными отличиями.

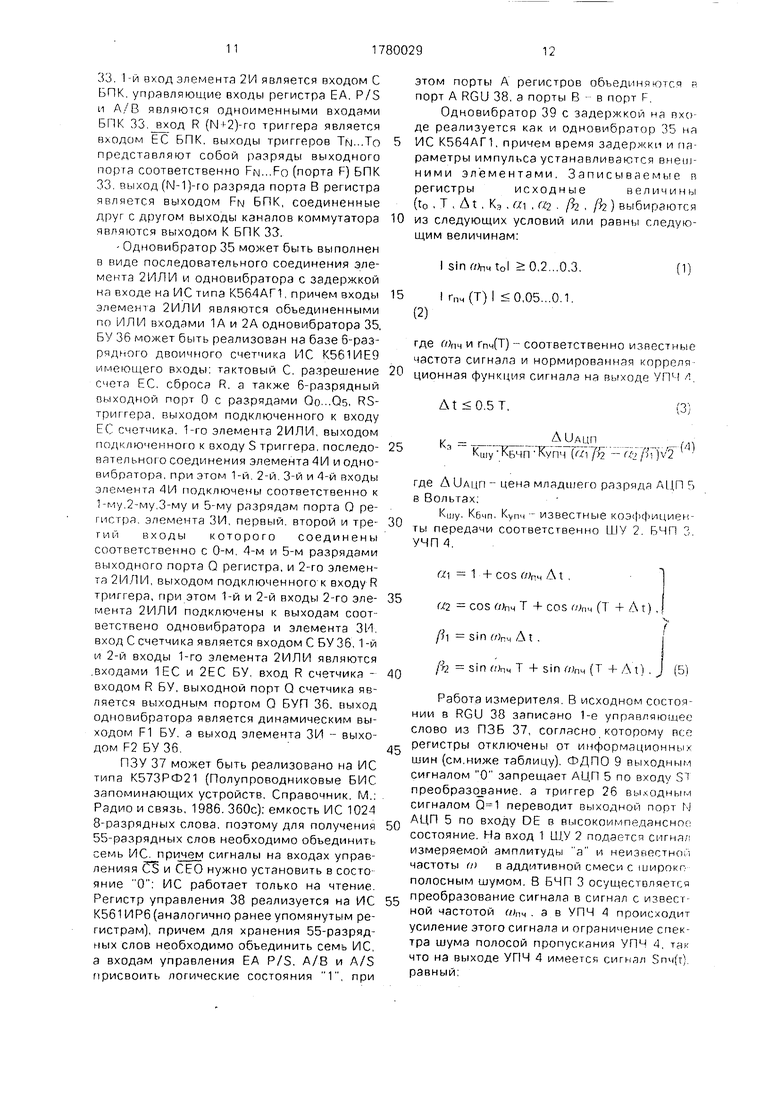

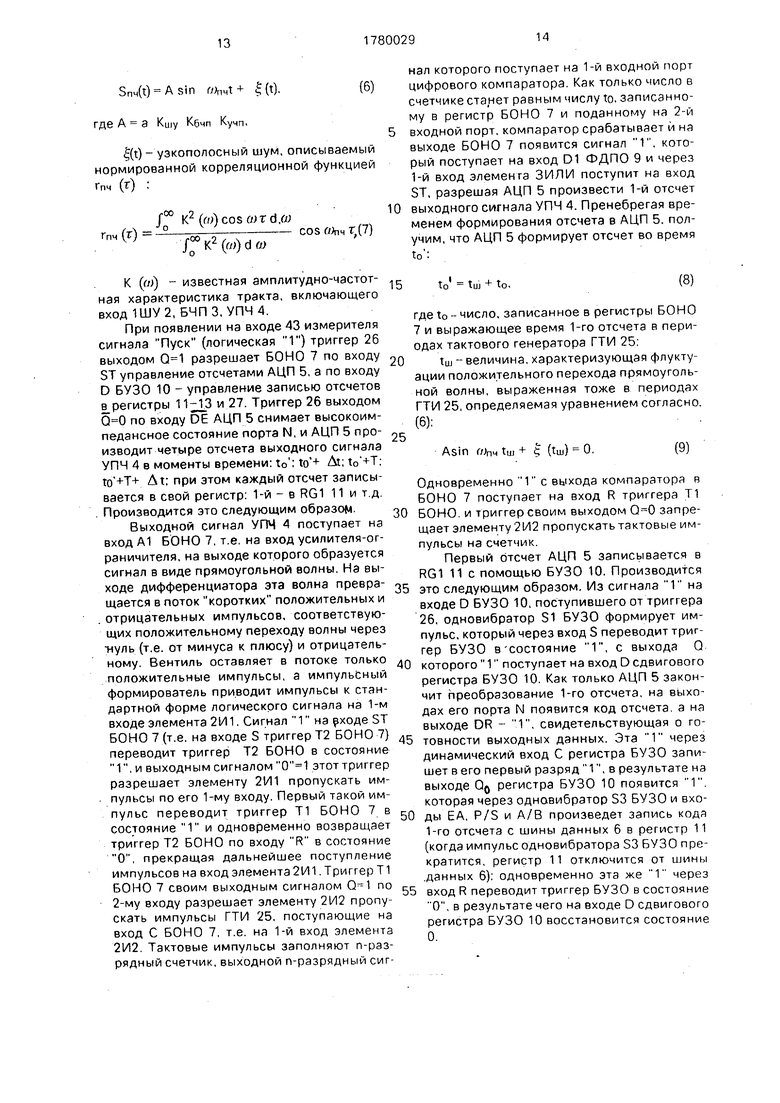

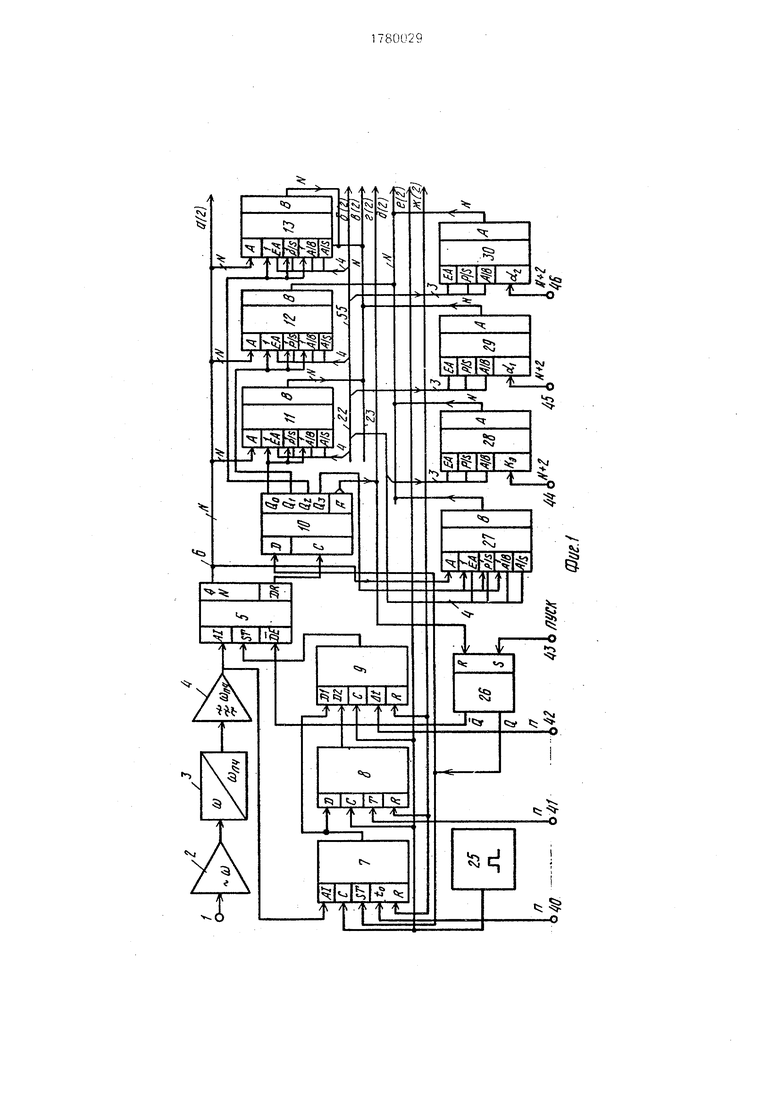

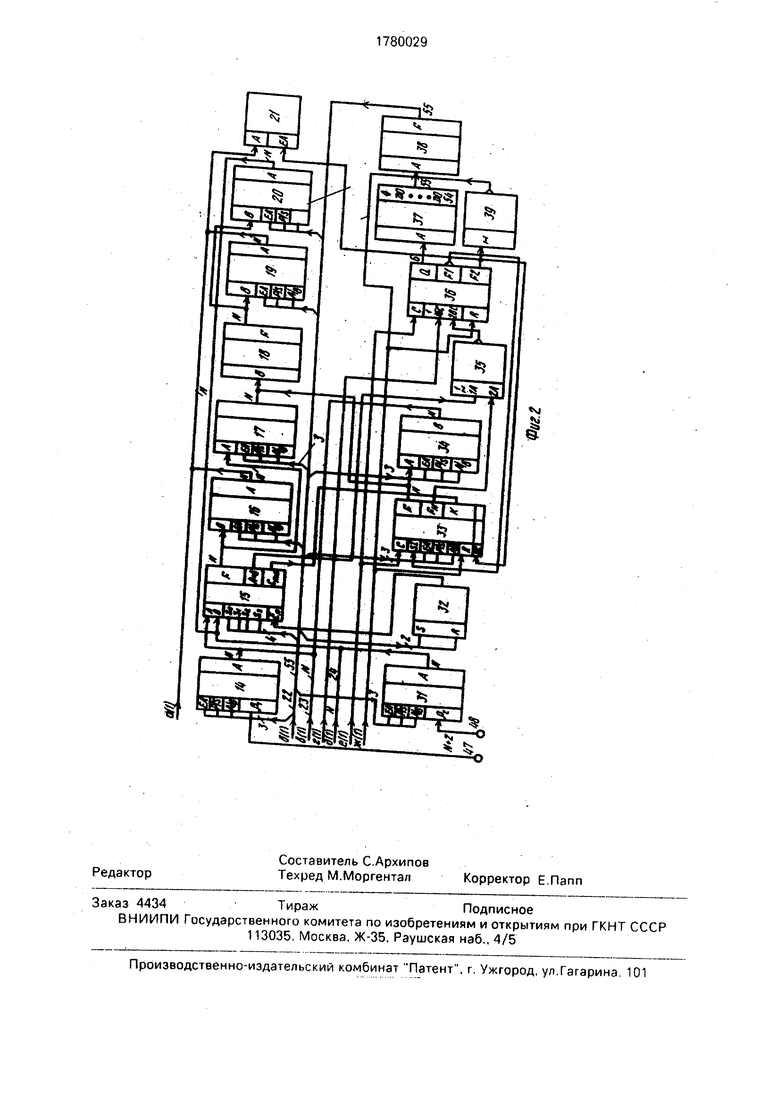

На фиг.1 и 2 представлена функциональная схема предлагаемого измерителя.

5Измеритель содержит широкополосный

усилитель (ШУ) 2, вход 1 которого является входом измерителя, блок частотного преоиразоеания (БЧП) 3, усилитель промежуточной частоты (УПЧ) 4, N-разрядный

0 аналого-цифровой преобразовате.пь (АЦП) 5 переменного тока, аналоговый вход которого А1 подключен к выходу УПЧ 4. а N-pssрядный выходной порт N соединен с N-линейной шиной данных 6. которая другим концом подключена к Ы-разряд -;ому входному порту А блока индикации (БИ) 2 1: АЦП 5 имеет два установочных входа и один выход: Преобразование (ST) и РЗысокоимпедансное состояние (DE) - при 1 на первом входе АЦП 5 осуществляет

преобразование аналог-код, а при О на втором - переводит разряды выходного порта N в высокоимпедансное состояние; установочный выход Данные готовы (DR) выдает 1, когда преобрвазование аналог код закончено и в выходном порте установлен правильный код. В измеритель также входят: определитель 7 начала отсчетов (БОНО) to с четырьмя входами (аналоговыми А1, тактовых импульсов С, начала преобразования ST, сброса R) и п-разрядным входным портом to для ввода величины начала отсчета to (п определяется требуемой точностью измерений), формирователь двух парных отсчетов (ФДПО) 9 (с двумя входами для данных D1 и D2, тактовым входом С, сходом сброса R и п-разрядным вводом промежутка времени Д t между двумя отсчетами в паре), формирователь межпарного интервала Т (ФМПИ) 8 между парами отсчетов с входами: данных D, тактовым С, сброса R и п-разрядным вводом межпарного интервала Т), блок управления записью отсчетов (БУЗО) 10, производимых АЦП 5 (с входами: данных D, входами Оо,,,0з и динамическим выходом F), четыре N-разрядных регистра RG1 11, RG2 12, RG3 13, RG4 27 для записи отсчетов АЦП 5 и промежуточных величин в процессе обработки отсчетов (с обратимыми N-разрядными портами А и В и шестью входами управления: 1-м и 2-м соединенными по ИЛИ входами отключения порта А-Е А, 1 -м и 2-м соединенными по ИЛИ входами переключения работы регистров с параллельного на последовательный режимы P/S, 1-м и 2-м соединенными по ИЛИ входами изменения потока данных между портами А и В А/В, входом выбора асинхронного (синхронного режимов работы A/S), пять N-разрядных регистров RG5 28. RG6 29, RG7 30, RG8 1-, RG9 24 для записи констант (Кэ, «1 , «2 . , ), используемых при обработке отсчетов (с входами управления ,ЕА, P/S и А/В, аналогичными входам первых четырех регистров, выходными портами А, аналогичными портам А первых четырех регистров, а входными (Ы+2)-разрядными портами для ручного ввода соответствующих констант (N - число разрядов во входных данных, 2 - число разрядов для управления записью входных данных в регистр), N-разрядный арифметико-логический блок (АЛБ) 15, по функциям аналогичный АЛБ К564 ИПЗ (с входными портами А и В, выходным F, входами управления 5о...8з, входом переноса Сп, выходами разнозначности и переноса СП+N), пять N-разрядных операционных регистров RG11 17,TG12 19, RF1320, RG14 34 (с портами А и В и входами управления ЕА, P/S и А/В, аналогичными первым четырем регистрам), 1-я и 2-я N-линейные операционные шины 23 и 24, причем 1-я подключена к порту А АЛБ, а 2-я - к порту В, 5 N-разрядный квадратор 18, блок подбора корня (БПК) 33 (с входами:тактовым С, последовательным SI, сброса R и управления ЕА, P/S, А/В, аналогичными входам управления первых четырех регистров, входом ЕС

0 разрешения счета по входу С, с выходным N-разрядным портом F, выходом N-ro разряда EN и коммутационным выходом К), блок управления (БУ) 36 - с входами: тактовым С, двумя соединенными по ИЛИ входами разрешения счета ЕС, сброса R: с 6-разрядным выходным портом Q, с двумя выходами FI и F2(Fi -динамический), управляющие началом подбора корня в БПК 33 (Fi) и выдачей информации в БИ 21 и окон0 манием цикла измерения (F2), постоянный запоминающий блок (ПЗБ) 37 на 49 55-разрядных слов (двоичных чисел), 55-разрядный управляющий регистр 38 с подключенной к его выходному порту F 555 линейной шиной управления 22, генератор тактовых импульсов (ГТИ)25, два RS-триггера Ti и Т2 соответственно 26 и 32, два одновибратора Si 35 и 82 39 с задержками на входах, при этом у 1-го одновибратора два

0 входа объединены по схеме ИЛИ.

Перечисленные блоки соединены друг с другом следующим образом, ШУ 2, БПЧ 3, УПЧ 4, вход А1 АЦП 5 соединены последовательно: шина данных 6 одним концом подключена к выходному порту N АЦП 5, а другим - к входному порту БИ 21: вход А БОНО 7 подключен к выходу УПЧ 4, а выход к входу D ФМПИ 8, к входу D1 ФДПО 9. вход D2 которого подключен к выходу ФМПИ 8;

0 выходом ФДДР 9 подключен к входу ST АЦП 5, вход DE которого соединен с выхо:, дом Q триггера Т1 26. подключенного выходом U к входам ST БОНО 7 и D БУЗО 10; выход DR АЦП 5 соединен с динамическим

5 входом С БУЗО 10, динамический выход F которого соединен с входом R триггера Т1 26 и 1 ЕС БУ 36; выход ГТИ 25 подключен к тактовым входам С блоком БОНО 7, ФМПИ 8, ФДПО 9 и БПК 33, а выходы R этих же

0 блоков соединены с выходом 2-го одновибратора S2 39; вход S 43 триггера Т1 26 является входом сигнала Пуск измерителя, по которому производится измерение амплитуды а ВЧ-сигнала; порты А регистров RG1

5 11, RG2 12, RG3 13, RG4 27. RG10 16 и RG12 19 соединены с шиной 6 данных; порты В регистров RG1 11, RG3 13, RG14 34 и порты А регистров RG6 29. RG8 14 соединены с 1-й операционной шиной 23, а со 2-й операционной шиной 24 соединены порты В регистров 12 и 27 и порты А регистров 28, 30, 24 и 20: из выходов Оо...0з БУЗО 10 соединен с первыми управляющими входами ЕА, P/S и A/S регистров соответственно 11, 12, 13 и 27; управляющие входы 2ЕА, P/S, А/В, A/S регистров 11-13 и 27, входы ЕА, P/S, А/В регистров 16, 28-30, 14, 31, входы S3...SO АЛБ 15, входы S и R триггера 32, входы ЕА, P/S и А/В регистров 1.7, 18, 20, 34 и ВПК 33 соединены соответственно с линиями Fo.,.F55 55-линейной упавляющей шины 22: выход Q триггера 32 соединен с входом С АЛБ 15, выходной N-разрядный порт F которого соединен с входным портом В регистра 16 и А регистра 17, а выходы и CiiHN АЛБ 15 соединены соответственно с входом 1А одновибратора 35 и входом К ВПК. 33, вход которс1 о S1 соединен с выходом FI БУ 36, вход ЕС соединен с выходом одновибратора S1 35, а N-разрядный порт F соединен с портом А регистра 34 и входным портом В квадратора 18, а выход FN соединен с входом 2А одновибратора S 35, подключенного выходом к входу 2ЕС БУ 36: выходной порт В регистра 17 соединен с входным портом В квадратора 18, подключенного выходным портом F к входному порту В регистров 19 и 20: 6-разрядный порт Q БУ 36 соединен с адресным портом А ПЗУ 37, подключенного своим 55-разрядным выходным портом к входному порту А регистра управления 38, а выход F2 БУ 36 соединен с входами ЕА БИ 21 и одновибратора S2 39: вход 1 ШУ 2 является входом измерителя, а входные порты to БОНО 7, Т ФМПИ 8, At ФДПО 9, Кэ RG5 28, ai RG6 29, «2R RG7 30, / G8 14, /32 RG9 24 соединены с внешними разъенами . соответственно 40-48,

Описание реализации ШУ 2, БПС 3, УПЧ 4 и БИ 21 имеется в 2, а также весьма подробное - в документации на прибор серийный SPM-16, АЦП 5 может быть реализозан на базе отечественного АЦП 8-разрядного К1107 ПВ2 с временем преобразования 0,1 МКС(Гутников В,С, Интегральная электроника в измерительных устройствах. Л,: Энергия, 1988, 304 с,) или зарубежных типа MOD-1020 (10-разрядный ,АЦП с частотой отсчетов 20 МГц, Электроника, Т,53, 1980, N 12, С,112) или AD 376 16-разрядный с временем проеобразования 17 МКС (Еибрибный 16-разрядный АЦП. Электроника, 1985: Т,58, № 4, С,104).

Шина данных 6 реализуется на печатной плате в зиде N печатных проводников, к которым подсоединены входы и выходы (порты) данных соответствующих блоков: АЦП, регистров, АЛБ и т.п.

БОНО 7 может быть выполнен в виде ,1-го последовательного соединения усилителя-ограничителя, дифференциатора, вентиля для положительных импульсов, 1-го

входа 1-й схемы 2И, входа S 1-го RS-триггера и 2-го последовательного соединения 2-й схемы 2И, п-разрядного двоичного счетчика с входом сброса R и 1-го входного порта п-разрядного цифрового компаратора, а

0 также 2-го RS-триггера и п-разрядного регистра, причем выход Q 2-го триггера подключен ко 2-му входу 1-й схемы 21/1, а его вход R -- к выходу этой же схемы: выходом Q 1-й . триггер подключен к 2-му входу 2-й схемы

5 2И, а 2-й входной порт цифрового компаратора соединен с выходом регистра, а выход компаратора соединен с входом R 1-го триггера, при этом вход усилителя-ограничителя является входом А1 БОНО 7,1-й вход 2-й

0 схемы 2И - входом С БОНО 7, вход S 2-го триггера - входом ST БОНО. вход R счетчика - входом R БОНО, входной порт регистра входным портом to БОНО 7. а выход цифрового компаратора -выходом БОНО 7.

5ФМПИ 8 реализуется в виде последовательного соединения RS-триггера. 1-го входа схемы 2И, п-разрядного счетчика, имеющего вход сброса R. 1-го входа п-разрядного цифрового компаратора, а также

0 п-разрядного регистра, выходным портом подключенного к 2-му входному порту цифрового компаратора, выход которого соединен с входом R триггера, причем вход S триггера является входом D ФМПИ 8, 2-й

5 вход схемы 2И является входом С ФМПИ. вход сброса R счетчика - входом R ФМПИ, входной порт регистра - портом Т ФМПИ, а выход цифрового компаратора - выходом ФМПИ 8,

0ФДПО 9 может быть выполнен в виде

последовательного соединения 1-й схемы 2ИЛИ, входа S RS-триггера, 1-го входа схемы 2И п-разрядного счетчика, имеющего вход сброса Я, 1-го входного порта п-раз5 рядного цифрового компаратора, 3-го входе схемы З.ИЛИ, а также п-разрядного регистра, выходным портом подключенного к 2-му входному порту цифрового компаратора, и 2-й схемы 2 ИЛИ, выходом подключенной к

Q входу R счетчика, при этом 1-й вход схемы 2 ИЛИ1 является входом D1 ФДПО 9 w одновременно соединен с 1-м входом схемы ЗИЛИ, 2-й вход схемы 2ИЛИ является входом D2 ФДПО и соединен с 2-м входом

5 схемы ЗИЛИ: входом R RS-триггер и 1-м входом схема 2ИЛИ2 подключены к цифрового компаратора: 2-й вход схемы 2И является входом С ФДПО 9, 2-й вход схемь 2ИЛИ2 является входом R ФДПО, входной порт регистра является портом ввода At

ФДГЮ, а выход схемы ЗИЛИ - выходом ФДП09.

Блок БУЗО 10 может быть выполнен в виде последовательного соединения 1-го одновибратора Si. входа S RS-триггера. входа D сдвигового регистра К5611/1Р12 (Шило В.Л. Популярные цифровые микросхемы. Челябинск: Металлургия, 1988. 350с.), имеющего также тактовый вход С, вход сброса R и выходы разрядов Оо-Оз, а также одновибратора $2 с задержкой на входе, схемы 2И и четырех одновибраторов 5з-5б, при этом выход QO регистра соединен с входом R триггера. 1-й вход схемы 21/1 соединен с выходом одновибратора 52 БУЗО, а выход с входом R регистра, каждый из выходов регистра Оо-Оз соединен с входом одного из одновибраторов соответственно 5з-5б. причем вход одновибратора Si является входом D БУЗО 10, вход С регистра, соединенный с входом одновибратора S2. входом С БУЗО, выходы одновибраторов Ss-Sa являются вь1ходами ВУЗО. а выход схемы 2И - динамическим выходом F БУЗО 10. Каждый из регистров 11 -13 и 27 может быть выполнен на базе регистров К561ИР6. объединенных в регистр требуемой разрядности N (см.стр.246 в вышеприведенном источнике), и трех элементов 2ИЛИ, причем выход 1-го элемента подключен к входу ЕА регистра, выход 2-го - к входу P/S, а выход 3-го к входу А/В регистра, при этом 1-й и 12-й входы 1-го элемента 2ИЛ1/1 образуют два объединенных по ИЛИ входа ЕА регистрового блока, а входы остальных элементов 2ИЛИ образуют объединенные по ИЛИ входы соответственно P/S и А/В регистрового блока, а вход A/S и порты А и В объединенных регистров являются одноименными элементами регистрового блока. Регистры 28-30. 14 и 31 однотипны.

Рассмотрим реализацию регистра RG5 28. Он может быть реализован на базе объединенных до нужной разрядности N 8-разрядных регистров Е561ИР6 и двух элементов 2ИЛИ, при этом выход 1-го элемента 2 ИЛИ подключен к входу ЕА регистрового блока, а выход 2-го - к входу А/В. вход A/S подключен к напряжению логическая причем 1-й вход 1-го элемента 2ИЛИ, вход RS и 1-й вход 2-го элемента 2ИЛИ образуют входы управления регистрового блока соответственно ЕА. P/S и А/В. а 2-е входы обоих элементов 2ИЛИ и N-разрядный порт В объединенных регистров образуют (Ы+2)-разрядный входной порт Кэ регистрового блока; N-разрядный порт А объединенных регистров является портом А регистрового блока.

АЛ Б 15 может быть выполнено ил базе объединения до требуемой разрядности N ИС АЛБ типа К564ИПЗ (см.стр.267 в вышеприведенном источнике). Регистры 16. 17. 19, 20 и 34 однотипны и каждый может быть выполнен на базе 8-разрядных регистров К561ИР6, объединенных до нужной разряд.ности N, а на вход управления A/S подана логическая 1.

0Квадратор 18 может быть реализован на

базе ряда АЛУ К564ИПЗ. объединенных с помощью ИС ускоренного переноса К564ИП4 в АЛУ требуемой разрядности N. причем порты А и В такого АЛБ запарелле5 лены, а на управляющие входы поданы логические сигналы, обеспечивающие ре.жим умножения: . . S1-1.SO-1, СггО. Шина управления 22. 1-я операционная шина 23 и 2-я 24 реализуются в виде соответствующего количества печатных проводников, к которым стандартным обрязом подключены ИС соответствующих блоков.

ГТИ 25 может быть выполнен на базе ИС

5 564АГ1 (стр.282 в вышеприведенном источнике), два ждущих мультивибратора которой объединены в схему кольцевого автогенератора: вне1иними элементами частота может быть установлена в диапазоне от

0 единиц Гц до единиц МГц.

RS-триггеры 26 и 32 реализуются на базе ИС К561ТР2.

ВПК 33 реализуется на базе N-разрядного блока регистров типа К561ИР6, N последовательных соединений одновибраторов Si-Sn и входов S RS-триггеров TI-TN. каждое из которых входом одновибратора подключено к противоположному разряду порта В регистра (SN подключен к Во, SN-I - к В i и т.д.),

0 элементов 2ИЛИ, каждый из которых своим выходом подключен к входу R триггера, Nканального коммутатора типа К561КТЗ (ИС объединены до N разрядов), вход каждого канала которого подключен к 2-му входу одноименного элемента 2ИЛ1/1, одновибраторов SN+1...S2N. вход каждого из которых подключен к одноименному разряду порта В регистра, а выход- к управляющему входу Е1 одноименного канала коммутатора.

0 (N+1)-ro RS-триггера. выходом подключенного к последовательному входу Si регистра, а входом R- к 1-му разряду порта В регистра, (N-b2)-ro RS-триггера и элемента 2И. выходом подключенного к входу С регистра, а 2-м входом - к выходу (N+2)-ro триггера, при этом 1-е входы всех элементов 2ИЛИ соединены друг с другом и с входом R регистра и представляют собой вход R БПК 33. объединенный вход S (N-t-l)-ro и (N-i-2)-ro триггеров является входом S1 БПК

33. 1-й вход элемента 21/1 является входом С ВПК, управляющие входы регистра ЕА, P/S и А/В являются одноименными входами ВПК 33,вход R (N+2)-ro триггера является входом ЕС ВПК. выходы триггеров TN...TO представляют собой разряды выходного порта соответственно FN...FO (порта F) ВПК 33. выход (N-l)-ro разряда порта В регистра является выходом Рм ВПК, соединенные друг с другом выходы каналов коммутатора являются выходом К ВПК 33.

Одновибратор 35 может быть выполнен в виде последовательного соединения элемента 2ИЛ1/1 и одновибратора с задержкой на входе на ИС типа К56.4АГ1, причем входы элемеша 2ИЛИ являются объединенными по ИЛИ входами 1А и 2А одновибратора 35. ВУ 36 может быть реализован на базе б-разрядного двоичного счетчика ИС К561ИЕ9 имеющего входы: тактовый С. разрешение счета ЕС. сброса R. а также 6-разрядный выходной порт О с разрядами Qo...Q5, RSтриггера. выходом подключенного к входу ЕС счетчика. 1-го элемента 2ИЛИ, выходом подключенного к входу S триггера, последовательного соединения элемента 4И и одновибратора, при этом 1-н, 2-й. 3-й и 4-й входы элемента 4И подключены соответственно к Гму.2-му.3-му и 5-му разрядам порта О регистра, элемента ЗИ, первый, второй и третий входы которого соединены соответственно с 0-м. 4-м и 5-м разрядами выходного порта Q регистра, и 2-го элемента 2ИЛИ, выходом подключенного к входу R триггера, при этом 1-й и 2-й входы 2-го элемента 2ИЛИ подключены к выходам соответствено одновибратора и элемента ЗИ. вход С счетчика является входом С ВУ 36. 1-й и 2-й входы 1-го элемента 2ИЛИ являются .входами 1ЕС и 2ЕС БУ. вход R счетчика входом R ВУ, выходной порт Q счетчика является выходным портом Q БУП 36, выход одновибратора является динамическим выходом F1 ВУ. а выход элемента ЗИ - выходом F2 ВУ 36.

ПЗУ 37 может быть реализовано на ИС типа К573РФ21 (Полупроводниковые ВИС запоминающих устройств. Справочник. М.: Радио и связь, 1986. 360с); емкость ИС 1024 8-разрядных слова, поэтому для получения 55-разрядных слов необходимо объединить семь ИС. сигналы на входах управленияя CS и СЕО нужно установить в состояние ИС работает только на чтение. Регистр управления 38 реализуется на ИС К561ИР6 (аналогично ранее упомянутым регистрам), причем для хранения 55-разрядных слов необходимо объединить семь ИС, а входам управления ЕА P/S, А/В и A/S присвоить логические состояния 1, при

этом порты А регистров объединяются а порт А RGU 38, а порты В - в порт F.

Одновибратор 39 с задержкой на входе реализуется как и Одновибратор 35 на

ИС К564АГ1, причем время задержки и параметры импульса устанавливаются внешними элементами. Записываемые п регистрыисходныевеличины

(to , Т , Дt , Кэ , «1 , «2 . fh. , Ih выбираются

из следующих условий или равны следующим величинам:

I з1по)пмЬ1 0,2...0,3,

(1) I Гпч(Т)1 0,05...0.1.

(2)

где (От и гпч(Т) - соответственно известные

частота сигнала и нормированная корреля20 ционная функ1(мя сигнала на выходе УП-1 /S.

At 0.5 Т,(З;

1 Аидцп , .

Ku,;i(n-Купч (( Vn

где Д УАЦП - цена младшего разряда АЦП S в Вольтах:

Кшу. Кбчп. Купч - известные коэффициенты передачи соответственно ШУ 2. ВЧП 3. УЧП4.

«1 1 -F cos пч Д t ,

f/2 cos Т -f- cos (пч (т -Ь Д t) , /il sin Мпч At .

/З sin Мпч т + sin (i)n (Т + А t) ,

Работа измерителя. В исходном состоянии в RGU 38 записано 1-е управляющее слово из ПЗБ 37, согласно которому все

регистры отключены от информационны: шин (см.ниже таблицу). ФДПО 9 выходным сигналом О запрещает АЦП 5 по входу S преобразование, а триггер 26 вы.чодным сигналом переводит выходной порт N

АЦП 5 по входу DE в высокоимпе.дансное состояние. На вход 1 Ш.У 2 подается сигня.п измеряемой амплитуды а и неизвестной частоты (11 в аддитивной смеси с широко полосным шумом. В БЧП 3 осуществляется

преобразование сигнала в сигнал с известной частотой Одтч . 3 в УПЧ 4 происходит усиление этого сигнала и ограничение спектра шума полосой пропускания УПЧ 4, так что на выходе УПЧ 4 имеется сигнал 5пч(т). равный: Sn4(t)Asin 0)n4t+ (t). где A - a Kuiy Кбчп Кучп, (t) - уэкополосный шум, описываемый нормированной корреляционной функцией гпч (г) ; / K2(o;)coso)Td,ftJ cos (1)пч ТД7) Гпч (г) Г К2 И d ш

К (w) - известная амплитудно-частотная характеристика тракта, включающего вход 1ШУ2, БЧПЗ,УПЧ4.

При появлении на входе 43 измерителя сигнала Пуск (логическая 1) триггер 26 выходом разрешает БОНО 7 по входу ST управление отсчетами АЦП 5, а по входу D БУЗО 10 - управление записью отсчетов в регистр1Ы и 27. Триггер 26 выходом по входу DE АЦП 5 снимает высокоимпедансное состояние порта N, и АЦП 5 производит четыре отсчета выходного сигнала УПЧ 4 в моменты времени: to; to+ At; to+T; to+T+ At; при этом каждый отсчет записывается в свой регистр: 1-й - в RG1 11 и т.д. Производится это следующим образом.

Выходной сигнал УПЧ 4 поступает на вход А1 БОНО 7, т.е. на вход усилителя-ограничителя, на выходе которого образуется сигнал в виде прямоугольной волны. На выходе дифференциатора эта волна превращается в поток коротких положительных и . отрицательных импульсов, соответствующих положительному переходу волны через нуль (т.е. от минуса к плюсу) и отрицательному. Вентиль оставляет в потоке только положительные импульсы, а импульсный формирователь приводит импульсы к стандартной форме логического сигнала на 1-м входе элемента 2И1. Сигнал 1 на рходе ST БОНО 7 (т.е. на входе S триггер Т2 БОНО 7) переводит триггер Т2 БОНО в состояние 1. и выходным сигналом этот триггер разрешает элементу 2И1 пропускать импульсы по его 1-му входу. Первый такой импульс переводит триггер Т1 БОНО 7 в состояние 1 и одновременно возвращает триггер Т2 БОНО по входу R в состояние О, прекращая дальнейшее поступление импульсов на вход элемента 2И1. Триггер Т1 БОНО 7 своим выходным сигналом по 2-му входу разрешает элементу 2И2 пропускать импульсы ГТИ 25, поступающие на вход С БОНО 7, т.е. на 1-й вход элемента 2И2. Тактовые импульсы заполняют п-разрядный счетчик, выходной п-разрядный сиг(6)

(8)

15

to tuj + to.

где to - число, записанное в регистры БОНО 7 и выражающее время 1-го отсчета в периодах тактового генератора ГТИ 25:

ш величина, характеризующая флуктуации положительного перехода прямоугольной волны, выраженная тоже в периодах ГТИ 25, определяемая уравнением согласно. (6);

Asin tm + 1 (tш) 0.

(9)

Одновременно 1 с выхода компаратора в БОНО 7 поступает на вход R триггера Т1

0 БОНО. и триггер своим выходом запрещает элементу 2И2 пропускать тактовые импульсы на счетчик.

Первый отсчет АЦП 5 запись вается в RG1 11 с помощью БУЗО 10. Производится

5 это следующим образом. Из сигнала 1 на входе D БУЗО 10, поступившего от триггера 26, одновибратор S1 БУЗО формирует импульс, который через вход S переводит триггер БУЗО всостояние 1. с выхода О

0 которого 1 поступает на вход D сдвигового регистра БУЗО 10. Как только АЦП 5 закончит преобразование 1-го отсчета, на выходах его порта N появится код отсчета, а на выходе DR - 1. свидетельствующая о го5товности выходных данных. Эта 1 через динамический вход С регистра БУЗО запишет в его первый разряд 1, в результате на выходе QQ регистра БУЗО 10 появится 1. которая через одновибратор S3 БУЗО и вхо0ды ЕА. P/S и А/В произведет запись кода 1-го отсчета с шины данных 6 в регистр 11 (когда импульс одновибратора S3 БУЗО прекратится, регистр 11 отключится от шины .данных 6): одновременно эта же 1 через

5 вход R переводит триггер БУЗО в состояние О, в результате чего на входе D сдвигового регистра БУЗО 10 восстановится состояние 0. нал которого поступает на 1-й входной порт цифрового компаратора. Как только число в счетчике станет равным числу to, записанному в регистр БОНО 7 и поданному на 2-й входной порт.компаратор срабатывает и на выходе БОНО 7 появится сигнал 1, который поступает на вход D1 ФДПО 9 и через 1-й вход элемента ЗИЛИ поступит на вход ST, разрешая АЦП 5 произвести 1-й отсчет выходного сигнала УПЧ 4. Пренебрегая временем формирования отсчета в АЦП 5, получим, что АЦП 5 формирует отсчет во время to:

Второй отсчет АЦП 5 производит через промежуток времени At после 1-го отсчета, формируемый ФДПО 9. Производится это следующим образом.

Сигнал 1-го отсчета (1)с выхода БОНО 7 поступает на вход D1 ФДПО 9, являющийся 1-м входом элемента 2ИЛ1/11 ФДПО, и с выхода этого элемента через вход S устанавливает триггер ФДПО в состояние 1, который своим выходом разрешает по 1-му входу э.мемента 2И пропускать импульсы ГТИ 25. поступающие на вход С ФДПО, являющийся одновременно 2-м входом элемента 2И. Импульсы ГТИ 25 заполняют счетчик до тех пор пока, на его п-разрядном выходе не образуется число t, равное числу, записанному в регистр ФДПО 9. С образованием такого числа N-разрядный компаратор срабатывает и через 3-й вход элемента ЗИЛИ. выход ФДПО 9 и вход ST АЦП 5 разрешает последнему произвести 2-й отсчет. Одновременно сигнал с выхода цифрового компаратора через вход R переводит триггер ФДПО в состояние О, а последний своим выходом 0-0 запрещает элементу 21/1 передавать импульсы на счетчик. Сигнал, с выхода цифрового компаратора через 1-й вход элемента 2ИЛ1Л2 и вход R счетчика сбрасывает содержимое счетчика, подготавливая его к работе ссигналом ФМПИ 8.

Второй отсчет записывается в RG2 12 следующим образом. Когда код 2-го отсчета будет готов, АЦП 5 сигналом на своем выходе DR через вход С БУЗО 10 переместит 1 из 1-го разряда регистра БУЗО 10 во 2-й. Эта 1 через одновибратор S4 БУЗО (выход 01 БУЗО) и входы ЕЛ, P/S и А/В регистра 12 запишет в последний через порт А с шины данных 6 код 2-го отсчета.

Третий отсчет АЦП 5 формируется через промежуток времени Т ( межпарный интервал) после 1-го отсчета, выдаваемый ФМПИ 8. Формирование промежутка Т происходит в следующем порядке. Сигнал 1 с выхода БОНО 7 на производство 1-го отсчета в момент to наряду с входом D1 ФДПО 9 поступает и на вход D ФМПИ 8, являющийся входом S и RS-триггера ФМПИ, переводя его в состояние 1. Триггер выходом через 1-й вход элемента 2И разрешает последнему пропускать по своему 2-му входу тактовые импульсы ГТИ 25, идущие на вход п-разрядного счетчика. Когда число импульсов в счетчике станет равным числу Т, записанному в регистр ФМПИ. срабатывает п-разрядный цифровой компаратор и на выходе ФМПИ возникает сигнал 1, который через вход D2 ФДПО 9 проходит на его выход (через 2-й вход элемента ЗИЛИ) и

через вход ST командует АЦП 5 произвести 3-й отсчет.

Выполнение 3-го отсчета АЦП 5 и его запись в регистр 13 БУЗО 10 производится

аналогично 2-му отсчету с использованием выхода Q2 БУЗО 10, Четвертый отсчет производится АЦП 5 через промежуток времени At, формируемый ФДПО 9 по сигналу 3-го отсчета, аналогично формированию 2-го отсчета по сигналу 1-го,

Запись 4-го отсчета происходит в регистр 27 с использованием выхода 03 БУЗО 10, при этом триггер 26 и БУЗО 10 одновременно переходят в исходное состояние

(подготовлены для осуществления новой тетрады отсчетов) по сигналу с выхода F БУЗО, и этот же сигнал поступает на вход 1ЕМ БУ 36 для управления дальнейшей обработкой отсчетов. Указанная операция реализуется так: АЦП5 .сигналом DR переводит 1 из 3-го разряда регистра БУЗО в 4-й и одновременно запускает одновибратор 2 БУЗО с задержкой на входе (задержка выбирается из условия надежнойзаписи кода с шины 6 данных в регистр 27 до снятия управляющих сигналов с входов этого регистра, выход 4-го разряда сигналом разрешит элементу 2И по 1-му входу пропускать импульсы одновибратора S2.

который через вxoд.R обнуляет регистр БУЗО, приводя весь блок в исходное состояние; одновременно зтот импульс поступает на вход R триггера 26, переводя его в состояние О. На основе (6) и (8) четыре отсчета

сигнала Sn4(t) на выходе УПЧ 4 дадут систему уравнений:

(to:

Sn4(to) Si Asin Ш|,ч to

5лч(ь+ At) AsinWn4 (to+A t) +f (to + At).

Sn4(to+T) - S3 Asin олш (to+T) - (). Sn4(to+T-i- A t) SA Asin (to- T At) - + (to-ьТ-: At).

в которой неизвестными будут to. А и значения шума. Если выбрать At так. чтобы при попарном сложении отсчетов напряжения шума взаимно компенсировались, то. peuJaя полученную из (10) систему уравнений с учетом (6) относительно to и А. получим следующие выражения для искомой амплитуды а на входе 1 измерител.я:

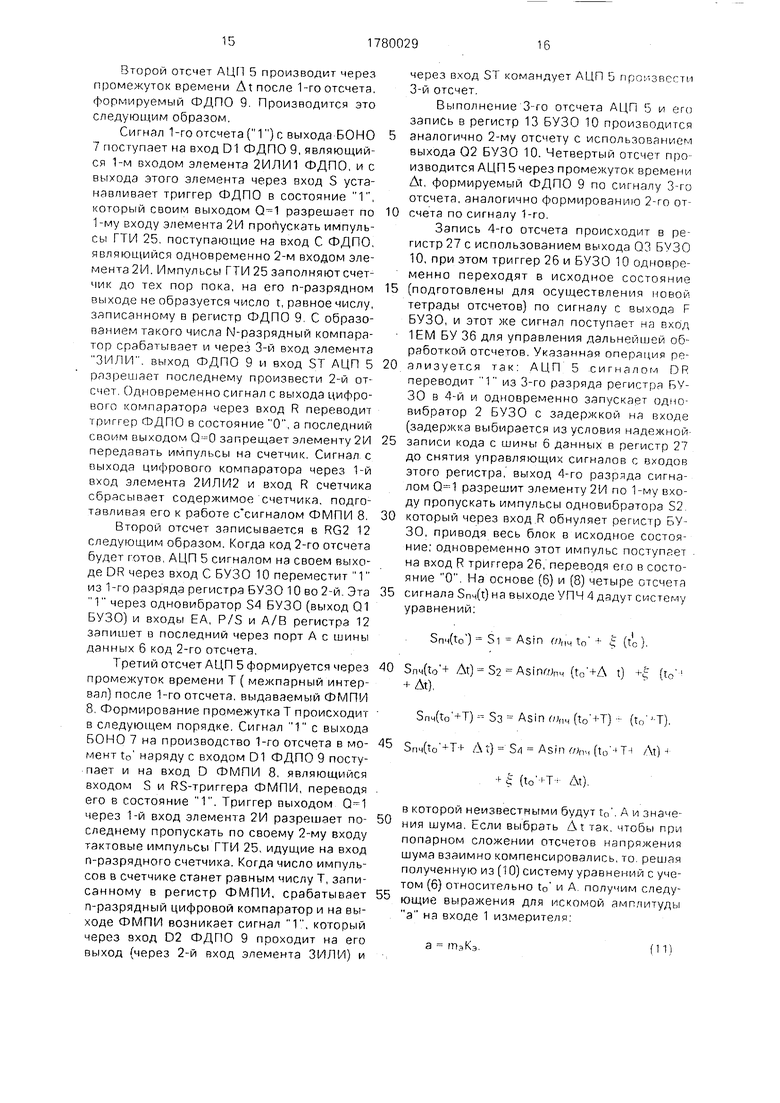

а РПзКэ.fill тэ V(mi (12 - 412 «i) + (mi - ) mi Si + 82, m2 83 + 84, где Кэ, a , «2 , /5i , / определяются выражениями (4) и (5). Дальнейшая работа схемы измерителя после записи отсчетов в регистры RG1-RG4 связана с реализацией вычислений по формуле (11). Она происходит в три этапа. На 1-м этапе вычисляется подкоренное выражение в (12), на 2-м - значение тэ и а, на 3-м осуществляется вывод значения а на БИ 21 и приведение схемы измерителя в исходное состояние. Работа на 1-м этапе. Входной сигнал 1 через вход 1ЕС БУ 36 (он является 1-м входом элемента 2ИЛИ1) переводит триггер БУ в состояние 1. который, своим выходом через вход ЕС разрешает счетчику БУ прием импульсов от ГТЙ 25 через вход С. Счетчик, накапливая импульсы, меняет сигналы на выходном порте О БУ, управляя адресным портом А ПЗБ 37, обеспечивая последовательную выборку управляющих слов из ПЗБ. Эти слова записываются в регистр управления 38 и через его выходной порт F и шину управления 22 воздействуют на управляющие входы регистра и БПК 33 (ЕА, P/S. А/В, A/S), АЛБ 15 (5о...5з) и триггер 32 (S и R), приводя к последовательному выполнению необходимых операций. Последовательность управляющих слов и результаты отдельных операций представлены в таблице. На 46-м щаге измерителем вычисляется величинд тэ и БУ 36 через выход F1 передает у правление БПК 33 для вычисления квадратного корня из величины гпэ. Этот сигнал появ 1яется на выходе элемента 4И и через одновибратор S2 БУ36 передается на выход F1 последнего, при этом сигнал появляется при наличии 1 в разрядах Oi,Q2,Q3 и Qs счетчика БУ. Одновременно сигнал с выхода однови ратора S2 БУ 1-й вход элемента 2ИЛ1/1 1 воздействует на вход R триггера БУ, переводя его в состояние О и запрещая выходом этого триггера по входу ЕС счетчику БУ JDlaльнейший прием импульсов от ГТИ 25, т.е. БУ 36 останавливается на 46-м шаге. Подбор корня БПК 33 из величины гnэ производится следующим образом. На 46-м шаге БУ 36 составляется схема, в соответствии с которой выходной порт F БПК 33 связан с входом квадратора 18, выход которого подан на входной порт В регистра 20, а выходной порт А последнего соединен с портом В АЛБ 15. Порт А АЛБ подключен к порту В RG1 11 и для управления процессом подбора корня используются два выхода АЛ: и Сп+м. Сигнал 1 с выхода F1 БУ 36 через вход S1 БПК 33 (являющийся входом S триггера TN+I переводит триггер TN+I БПК в состояние 1, и этот триггер своим выходом обеспечивает сигнал 1 на входе S1 сдвигового регистра БПК, управляющие входы которого (ЕА, P/S, А/В) обеспечивают синхронный прием информации, т.е., согласно тактовым импульсам ГТИ 25, поступающим на вход М БПК 33, 1-й тактовый импульс перемещает 1 с входа S1 в 1-й разряд БПК. Эта 1, появившись на выходе разряда Во выходного порта В регистраБПК, через вход переводит триггер TN+I БПК в состояние О, которое передается на вход S1 регистра БПК, и эта же 1 переводит триггер TN через одновибратор SN и вход S в состояние 1. Таким образом, на входе квадратора будет действовать код Х, в старшем разряде которого (N-1) будет 1, а в других - нули. После возведения в квадрат квадратором 18 этот код сравнивается с кодом числа ппэ в АЛ 15, причем если . то на выходе Cn+N АЛБ 15 появляется 1, если , то появляется сигнал О на выходе Сп+ы, а когда X тэ . то 1 появляется на выходе АЛБ 15. Сигнал 1 с разряда Во порта В регистра БПК запускает одновибратор SN+I БПК. который своим сигналом через вход Е1 1-го канала коммутатора БПК соединяет вход R триггера TN с выходом Сп-«-ы АЛБ 15. Если X тэ, то сигнал 1 на выходе Cn+N переводит триггер TN в состояние в разряде EN-I БПК появится О. Если неравенство противоположное, то 1 в разряде FN-I останется. Со следующим тактовым импульсом 1 передвинется в разряд Ры-2 и сравнение кодов повторится с оставлением 1 в триггере TN-I или с записью в него О. Переход 1 от старшего разряда к младшему будет продолжаться до тех пор. пока не установится равенство Х ГЛэ или 1 достигнет самого ммдшего разряда регистра БПК. В первом случае на выходе АЛБ 15 появится Т, которая через вход 1А одновибратора 35 передаст управление БУ 36 (через вход его 2ЕС) и одновременно через вход ЕС БПК 33 запрещает .прохождение тактовых импульсов через вход С в БПК. Во втором случае появится 1 на выходе FN БПК 33 и на выходе АЛБ 15, которая воздействует на вход одновйбратора 35. Действие выходного сигнала одновйбратора 35 аналогично предыдущему случаю.

Сигнал 1 на входе 2ЕС БУ 36 (это 2-й вход элемента 2ИЛИ1) через элемент 2ИЛ1/11 устанавливает триггер БУ в состояние 1, а он выходным сигналом вновь разрешает счетчику БУ принимать тактовые импульсы. С очередным тактовым импульсом происходит отключение регистров 11 и 20 от информационных шин; на следующем импульсе - определение а.

49-й тактовый импульс обеспечивает наличие 1 в разрядах Qo.Qi и Qs порта Q БУ, при этом на выходе элемента ЗИ появляется 1, которая поступает на вход одновибратора 39 через выход F2 БУ 36. Одновременно с этим же тактовым импульсом порт В регистра 16 отключается от АЛБ 15 и на входном порте А БИ 21 действует код величины а, а на входе ЕА - сигнал 1 (с выхода F2 БУ 36). разрешающи /; прием кода через порт А. Одновременно сигнал 1 с выхода элемента ЗИ через 2-й вход элемента 21/1ЛИ2 и вход R переводит триггер БУ 36 в состояние О, прекращая подачу тактовых импульсов через вход С счетчика БУ.

Так заканчивается 2-й этап обработки информации в измерителе.

3-й этап длится с начала появления сигнала 1 на входе одновибратора 39. Задержка на входе одновибратора выбрана такой, чтобы к моменту возникновения импульса на выходе ВИ 21 успел преобразовать информацию с порта А в визуальную форму. Появление 1 на выходе одновибратора 39 приводит к переводу всех блоков измерителя через входы R в исходное состояние. По этому сигналу обнуляются счетчики в БОНО 7 и ФМПИ 8, подтверждается обнуление счетчика ФДПО 9, сбрасывается в исходное состояние О триггеры TI-TN БПК 33, обнуляется счетчик БУ 36, что приводит к появлению на шине 22 управления исходного управляющего слова (см. 1-й шаг таблицы): все управляемые блоки приводятся в исходное состояние. Измеритель готов вновь прот извести цикл отсчетов и обработки измеряемой величины а.

Сравним прототип и предлагаемый измеритель по производительности и точности. Минимальное среднее время измерения прототипа 0.1 с. а минимальная погрешность (основная) 0,25 дВ. Время измерения предлагаемого измерителя складывается из времени производства отсчетов tor и времени вычислений ten. При fn4 104 Гц и Т 10 с время tor 210с.npMfrTM и Ы 10времяХвч (50+10)х . т.е. время измерения примерно равно 2.6 10с.

Таким образом, по производительности предлагаемое устройство почти в 400 раз

более быстродействующее, чем проттмп. Погрешность предлагаемого устройства при разрядности АЦП 5, равной 10, составляет 0,01 дБ, т.е. погрешность прототипа

приблизительно в 25 раз больше, чем у предлагаемого устройства.

Дальнейшее повышение точности и производительности можно достичь, используя корреляционную компенсацию случайной погрешности (Рыкин О.Р. Об оценке корреляционной погрешности автоматизированных измерительных комплексов систем передачи. Техника средств связи. Серия ТПС, 1983т. Вып.З. С. 11-22).

5Пусть межпарный интервал Т выбран из

условия (2) корреляционной компенсации случайной погрешности. Пусть дисперсия

шума на выходе УПЧ 4 будет cjfu, тогда доверительная погрешность измерений амплитуды при 4 отсчетах прототипа Дпт и предлагаемого измерителя Дпи равны:

(ш

(14)

Дпт 1-р-у . Дпи 1ф Кн Г7ш Q ,

где VP - доверительный коэффициент:

Кн - коэффициент наблюдений (см. приведенный выше источник), зависящий от вида корреляционной функции (7): Q - коэффициент, равный

п

.(sinr.n,.T +

Q sin

-Ь COS с/МчТ - 1) sin Wnnto + (sin Т - COS ЙМчТ - 1) COS r/Jnutol(15)

Отсюда эффективности предлагаемого измерителя, по сравнению с прототипом, Q Эпи/пт определится следующим образом.

При эквивалентной частотной характеристике УПЧ 4 в виде прямоугольника с полосой пропускания относительно frin. равной 2 Дfф

о / Л Q Эпи/пг - 5-(Тп7 .

(17)

Величина Q приблизительно равна 3 (при

sin САщТ 0,5 и sin (Опч to 0,25, О 2,82, а

при sin пчТ 0,25 и sinwrmto 0,5, О 3.13).

При характерных для прототипа величинах fn4 10 Гц и Af,}, 10 Гц величина Эпи/пт 1,4 . Для того, чтобы в прототипе также снизить погрешность, необходимо увеличить число отсчетов в Ю раз. Последняя величина характеризует также и возможное снижение производительности

прототипа по сравнению с заявляемым устройством.

Формула изобре те н и я Быстродействующий селективный измеритель амплитуды ВЧ-сигнала, содержащий последовательно соединенные широкополосный усилитель, блок частотного преобразования, уси/1итель промежуточной частоты, а также блок индикации, причем вход широкополосного усилителя соединен с входом измерителя, отличающийся тем, что, с целью повышения точности и быстродействия, в измеритель введены N-разрядный аналого-цифровой преобразователь, блок определения начала отсчетов, формирователь двух парных отсчетов, формирователь межпарного интервала, блок управления записью отсчетов, четыре N-разрядных регистра записи отсчетов, пять N-разрядных регистров записи констант, N-разрядный арифметико-логический блок, пять N-разрядных операционных регистров, N-разрядный квадратор, блок подбора корня, блок управления, постоянный запоминающий блок, управляющий регистр, генератор тактовых импульсов, первый и второй RS-триггеры, первый и второй одновибраторы, причем аналоговый вход аналого-цифрового преобразователя соединен с выходом усилителя промежуточной частоты и входом блока определения начала отсчетов, выход которого соединен с D-входом формирователя межпарного интервала и О1-входом формирователя двух парных отсчетов, О2-вход которого соединен с выходом формирователя межпарного интервала, выход формирователя двух парных отсчетов подключен к ST-входу начала преобразования. аналого-цифрового преобразователя, DE-вход которого соединен с инверсным выходом первого триггера, прямой выход которого соединен с ST-входом блока определения начала отсчетов и D-входом блока управления записью отсчетов, DR-выход аналого-цифрового преобразователя соединен с С-входом блока управления записью отсчетов, F-выход которого соединен с R-входом первого триггера и 1 ЕС-входом блока управления, выход генератора тактовых импульсов соединен с С-входами блока определения начала отсчетов, формирователя межпарного интервала, формирователя двух парных отсчетов, блока подбора корня и блока управления, R-входы которых соединены с выходом второго одновибратора, S-вход первого триггера соединены с клеммой Пуск устройства, разрядные выходы аналого-цифрового преобразователя соединены с соответствующими входами порта А первого, второго, третьего, четвертого регистров записи отсчетов и блока индикации, а также десятого и двенадцатого операционных регистров, разрядные выходы порта В первого регистра записи отсчетов соединены с соответствующими разрядными выходами портов В третьего регистра записи отсчетов и четырнадцатого операционного регистра и портов А шестого и восьмого регистров записи констант, а

0 разрядные выходь порта В второго регистра записи отсчетов соединены с соответствующими разрядными выходами порта В четвертого регистра записи отсчетов и порта Л пятого, седьмого, девятого регистров

5 записи отсчетов и тринадцатого операционного регистра, каждый из четырех Q-выходов блока управления записью отсчетов соединены с первыми объединенными управляющими входами ЕА, P/S- и А/В-входа0 ми соответственно первого, второго, третьего и четвертого регистров записи отсчетов, вторые управляющие ЕА-, P/S- и А/В-входы и A/S-ВХОД первого, второго, третьего и четвертого регистров записи отсчетов объединены и соединены с объединенными ЕА-, P/S- и А/В-входами регистров записи констант и операционных регистров, а также объединены с S-входами арифметико-логического блока, S- и R-входами

0 второго триггера, а также с объединенными ЕА-, P/S- и А/В-входами блока подбора корня и с соответствующими разрядными выходами управляющего регистра, прямой выход второго триггера соединен с Сп-вхо5 дом арифметико-логического блока, выходы порта F которого соединены с соответствующими входами порта В десятого операционного регистра и порта А одиннадцатого операционного регистра, а А/В-выходы и

0 Cn+N-входы арифметико-логического блока соединены соответственно с 1А-входом первого одновибратора и К-выходом блока подбора корня, вход которого соединен с Fl-выходом блока управления,а выходы

5 порта F соединены с соответствующими входами порта А четырнадцатого операционного регистра и входами порта В квадратора, которые соединены с соответствующими выходами порта В одиннадцатого операционного регистра, FN-ВЫход блока подбора корня соединен с 2А-ВХОДОМ первого одновибратора, выход которого соединен с 2ЕС-входом блока управления, выходы порта F квадратора соединены с соответствующими входами портов В двенадцатого и тринадцатого операционных регистров, разрядные выходы порта Q блока управления соединены с соответствующими блоками порта А постоянного запоминающего блока, разрядные

23178002924

выходы которого соединены с входами пор- блока индикации, входом второго однота А управляющего регистра, а Р2-выход вибратора и ЕС-входом блока подбора блока управления соединен с ЕА-входом корня.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронный измеритель мощности и энергии | 1988 |

|

SU1638653A1 |

| Устройство для цветовой коррекции кинофильмов,передаваемых по телевидению | 1984 |

|

SU1233162A1 |

| УСТРОЙСТВО СТАТИСТИЧЕСКОГО УПЛОТНЕНИЯ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1997 |

|

RU2110897C1 |

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

| Цифровой измеритель | 1988 |

|

SU1626170A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Панорамный измеритель частоты | 1984 |

|

SU1267273A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство для измерения времени задержки отсчета аналого-цифровых преобразователей | 1985 |

|

SU1280697A1 |

Использование: изобретение относится к измерительной технике и предназначено для использования в контрольно-измерительной аппаратуре систем электро- и радиосвязи. Существо изобретения; быстродействующий селективный измеритель амплитуды ВЧ-сигнала содержит широкополосный усилитель, вход которого является входом измерителя, блок частотного преобразования, усилитель промежуточной, частоты, аналого-цифровой преобразователь, шину данных, блок определения начала отсчетов, формирователь межпарного интервала, формирователь двух парных отсчетов, блок управления записью отсчетов, четыре регистра записи отсчетов, пять регистров записи констант, арифметико-логический блок, пять операционных регистров, квадратор, блок индикации, шину управления, первую и вторую операционные шины, генератор тактовых импульсов, два RS-триг- гера, блок подбора корня, два одновибрато- ра. блок управления памятью, постоянный запоминающий блок, регистр управления, восемь портов ручной установки параметров и вход сигнала "Пуск". 2 ил, 1 табл.(Лс

| Датчик диэлькометрического влагомера | 1980 |

|

SU894526A1 |

| Precision Electronic Measurement Equipment | |||

| Wandel and Goltermann | |||

| Пуговица | 0 |

|

SU83A1 |

| ЭЛЕКТРИЧЕСКИЙ ПРИБОР ДЛЯ ВЫБРАСЫВАНИЯ ШАРИКОВ И УКАЗАНИЯ ЦИФР ПРИ ИГРЕ В ЛОТО | 1922 |

|

SU632A1 |

| (прототип) | |||

Авторы

Даты

1992-12-07—Публикация

1990-08-06—Подача