Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны паритетные распознаватели (см., например, фиг.1 в описании изобретения к патенту РФ 2068581, кл. G 06 G 7/25, 1996 г.), которые идентифицируют равенство двух изменяющихся во времени аналоговых сигналов х1, х2.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных паритетных распознавателей, относится ограниченные функциональные возможности, так как эти распознаватели не проявляют свое идентифицирующее свойство при х1=х2=0.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип паритетный распознаватель (патент РФ 2176103, кл. G 06 G 7/25, 2001г.), который содержит сумматор и два релятора и идентифицирует равенство двух изменяющихся во времени аналоговых сигналов х1, х2.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится ограниченные функциональные возможности, так как прототип не проявляет свое идентифицирующее свойство при х1=х2=0.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения идентификации равенства двух изменяющихся во времени аналоговых сигналов х1, х2 как при х1=х2 ≠ 0, так и при х1=х2=0.

Указанный технический результат при осуществлении изобретения достигается тем, что в паритетном распознавателе, содержащем сумматор, второй вход которого соединен с первым информационным входом паритетного распознавателя, подключенного выходом к выходу второго релятора, а первый вход и выход сумматора соединены соответственно с выходом первого и третьим входом второго реляторов, каждый из которых содержит замыкающий и размыкающий ключи, подсоединенные выходами к выходу релятора, особенность заключается в том, что в каждый релятор введены дифференциальный усилитель и резистор, причем неинвертирующий и инвертирующий входы дифференциального усилителя образуют соответственно первый и второй входы релятора, третий вход которого соединен через резистор с объединенными выходами замыкающего и размыкающего ключей, подсоединенных управляющим входом и объединенными входами соответственно к выходу дифференциального усилителя и шине нулевого потенциала, первый, второй и третий входы первого релятора соединены соответственно с первым входом второго релятора, шиной нулевого потенциала и настроечным входом паритетного распознавателя, первый и второй информационные входы которого подключены соответственно к первому и второму входам второго релятора.

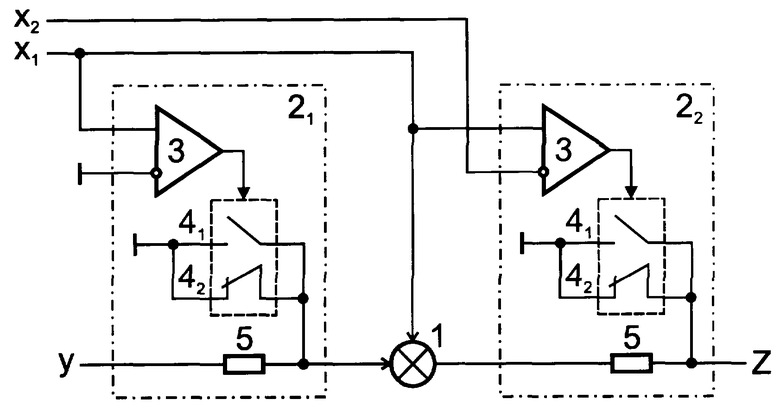

На чертеже представлена схема предлагаемого паритетного распознавателя.

Паритетный распознаватель содержит сумматор 1, первый и второй реляторы 21 и 22. Каждый релятор содержит дифференциальный усилитель 3, замыкающий и размыкающий ключи 41 и 42, резистор 5, причем резистор 5 подсоединен между третьим входом и выходом релятора, подключенного первым и вторым входами соответственно к неинвертирующему и инвертирующему входам усилителя 3, выход которого соединен с управляющим входом ключей 41, 42, подсоединенных объединенными входами и объединенными выходами соответственно к шине нулевого потенциала и выходу релятора. Второй и первый информационные входы паритетного распознавателя образованы соответственно вторым входом релятора 22 и объединенными вторым входом сумматора 1, первыми входами реляторов 21, 22, а настроечный вход паритетного распознавателя соединен с третьим входом релятора 21, подключенного вторым входом и выходом соответственно к шине нулевого потенциала и первому входу сумматора 1, выход которого соединен с третьим входом релятора 22, подключенного выходом к выходу паритетного распознавателя.

Работа предлагаемого паритетного распознавателя осуществляется следующим образом. На его первый и второй информационные входы подаются изменяющиеся во времени аналоговые сигналы (напряжения) х1 и х2, соответственно х1, х2 ∈(хmin,хmax), хmin<0, хmax>0; на его настроечном входе фиксируется аналоговый сигнал (напряжение) у∈{xmin,хmах}. Если сигнал на первом входе релятора больше либо меньше сигнала на его втором входе, то ключ 41 соответственно замкнут либо разомкнут, а ключ 42 соответственно разомкнут либо замкнут. Если сигнал на первом входе релятора равен сигналу на его втором входе, то ключи 41, 42 разомкнуты. Таким образом, предлагаемый паритетный распознаватель будет воспроизводить операцию

Здесь идентификация равенства изменяющихся во времени аналоговых сигналов х1 и х2 осуществляется либо по отличному от нуля значению x амплитудной координаты пересечения указанных сигналов, либо по сигналу y.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый паритетный распознаватель обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает идентификацию равенства двух изменяющихся во времени аналоговых сигналов х1, х2 как при х1=х2 ≠ 0, так и при х1=х2=0.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРИТЕТНЫЙ РАСПОЗНАВАТЕЛЬ | 2003 |

|

RU2230357C1 |

| ПАРИТЕТНЫЙ РАСПОЗНАВАТЕЛЬ | 2001 |

|

RU2176103C1 |

| ИНТЕРВАЛЬНЫЙ ИДЕНТИФИКАТОР | 2004 |

|

RU2251733C1 |

| ГЕНЕРАТОР ПРЕДИКАТНЫХ И АРГУМЕНТНЫХ ФУНКЦИЙ ДВУХ ПЕРЕМЕННЫХ | 1991 |

|

RU2029366C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2011 |

|

RU2445697C1 |

| Аналоговый логический элемент для воспроизведения линейно-разрывных функций (его варианты) | 1985 |

|

SU1270777A1 |

| АНАЛОГО-РАНГОВЫЙ РАСПОЗНАВАТЕЛЬ | 1999 |

|

RU2149453C1 |

| РАНГОВЫЙ ПРЕДИКАТОР | 2001 |

|

RU2204862C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2001 |

|

RU2195701C1 |

| СИЛОВОЙ РЕЛЯТОР | 2001 |

|

RU2211484C2 |

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом является расширение функциональных возможностей за счет обеспечения идентификации равенства двух изменяющихся во времени аналоговых сигналов x1, x2 как при x1=х2 ≠ 0, так и при x1=x2=0. Устройство содержит сумматор, два релятора, каждый из которых состоит из компаратора, замыкающего и размыкающего ключей, резистора. 1 ил.

Паритетный распознаватель, содержащий сумматор, второй вход которого соединен с первым информационным входом паритетного распознавателя, подключенного выходом к выходу второго релятора, а первый вход и выход сумматора соединены соответственно с выходом первого и третьим входом второго реляторов, каждый из которых содержит замыкающий и размыкающий ключи, подсоединенные выходами к выходу релятора, отличающийся тем, что в каждый релятор введены дифференциальный усилитель и резистор, причем неинвертирующий и инвертирующий входы дифференциального усилителя образуют соответственно первый и второй входы релятора, третий вход которого соединен через резистор с объединенными выходами замыкающего и размыкающего ключей, подсоединенных управляющим входом и объединенными входами соответственно к выходу дифференциального усилителя и шине нулевого потенциала, первый, второй и третий входы первого релятора соединены соответственно с первым входом второго релятора, шиной нулевого потенциала и настроенным входом паритетного распознавателя, первый и второй информационные входы которого подключены соответственно к первому и второму входам второго релятора.

| ПАРИТЕТНЫЙ РАСПОЗНАВАТЕЛЬ | 2001 |

|

RU2176103C1 |

| УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ФУНКЦИИ РАВЕНСТВА | 1992 |

|

RU2068581C1 |

| РЕЛЯТОРНЫЙ ЭЛЕМЕНТ | 2002 |

|

RU2195019C1 |

| РЕЛЯТОРНЫЙ АМПЛИТУДНЫЙ СЕЛЕКТОР | 1996 |

|

RU2112276C1 |

| SU 1568060 А1, 30.05.1990 | |||

| Дозатор сыпучих материалов | 1986 |

|

SU1392376A1 |

Авторы

Даты

2004-06-10—Публикация

2003-01-31—Подача