Настоящее изобретение в общем относится к устройству и способу кодирования/декодирования в системе мобильной связи множественного доступа с кодовым разделением каналов (МДКР) и, в частности, к устройству и способу, предназначенным для передачи обратного канала индикатора скорости (ОКнИС (R-RICH)), используемого в синхронной системе мобильной связи.

Уровень техники

В общем случае обратный дополнительный канал (ОДКн) поддерживает схему передачи данных с переменной скоростью. Понятие “схема передачи данных с переменной скоростью” подразумевает, что мобильная станция варьирует свою скорость передачи данных произвольным образом. В общем изменение скорости передачи данных обуславливает изменение кодовой скорости кодов с коррекцией ошибок, используемых при построении кадра, частоты повторения символов, а также длины и типа кодов Уолша, предназначенных для кодирования с расширением спектра. Следовательно, мобильной станции следует проинформировать базовую станцию о скорости передачи данных передаваемого в текущий момент обратного дополнительного канала так, чтобы приемник базовой станции мог корректно принимать этот обратный дополнительный канал. Канал, предназначенный для вышеописанной цели, называется обратным каналом индикатора скорости (ОКнИС).

Число доступных скоростей передачи данных, с которыми мобильная станция может передавать данные по обратному дополнительному каналу, зависит от числа доступных обратных дополнительных каналов, которые мобильная станция может использовать одновременно. Это число обратных дополнительных каналов определяется базовой станцией на основе анализа объема данных, подлежащих передаче по обратной линии связи во время установления вызова, и затем сообщается мобильной станции. Следовательно, число битов информации, передаваемых по обратному каналу индикатора скорости, меняется в зависимости от числа обратных дополнительных каналов. Иными словами, если число обратных дополнительных каналов равно 1, то мобильная станция информирует о скорости передачи данных по обратной линии связи, используя 4 бита. В то же время, если число обратных дополнительных каналов равно 2, то мобильная станция информирует о скорости передачи данных по обратной линии связи, используя 7 битов. В силу того что число доступных обратных дополнительных каналов, которые мобильная станция может использовать одновременно, нельзя изменить, пока от базовой станции не будет получена отдельная команда, мобильная станция будет передавать по обратному каналу индикатора скорости либо 4-битовый блок информации, либо 7-битовый блок информации. Иными словами, мобильная станция никогда не станет передавать одновременно и 4-битовый блок информации, и 7-битовый блок информации. Обычно код (24,4) или код (24,7) определяется как код с коррекцией ошибок, который должен использоваться для обратного канала индикатора скорости.

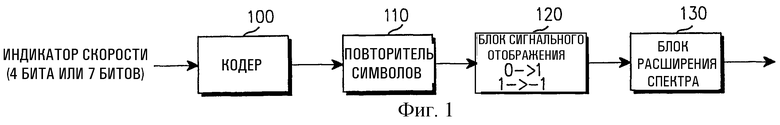

Фиг.1 иллюстрирует структуру передатчика ОКнИС. Согласно Фиг.1 кодер 100 кодирует 4-битовый или 7-битовый входной индикатор скорости и выдает 24 кодированных символа. Повторитель 110 символов 16 раз повторяет 24 кодированных символа, выдаваемых кодером 100. Посредством отображения 0 в 1 и 1 в -1 блок 120 сигнального отображения выполняет сигнальное отображение кодированных символов, выдаваемых повторителем 110 символов. Блок 130 расширения спектра кодирует символы, для которых было выполнено сигнальное отображение, с расширением спектра.

Согласно Фиг.1 индикатор скорости, состоящий из 4 или 7 битов, перед передачей кодируется в 24 кодированных символа. При наличии ошибок во время передачи индикатора скорости, кодированного в кодированные символы, индикатор скорости может дать неверную информацию о кодовой скорости соответствующего обратного дополнительного канала, частоте повторения символов, а также длине и типе кода Уолша, предназначенного для кодирования с расширением спектра. В результате приемник не сможет корректно анализировать этот обратный дополнительный канал. Следовательно, индикатор скорости следует кодировать кодером (24,4) или (24,7), обладающим высокой эффективностью. Более того, индикатор скорости следует декодировать как можно быстрее с целью анализа соответствующего дополнительного канала.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Таким образом, задачей настоящего изобретения является создание устройства и способа, предназначенных для кодирования индикатора скорости и характеризуемых оптимальной эффективностью.

Другой задачей настоящего изобретения является создание устройства и способа, предназначенных для кодирования индикатора скорости и характеризуемых минимальной сложностью.

Еще одной задачей настоящего изобретения является создание устройства и способа, предназначенных для минимизации сложности аппаратных средств посредством использования способа исключения символов из расширенного кода Рида-Мюллера первого порядка так, чтобы в процессе декодирования выполнялось обратное быстрое преобразование Адамара.

Еще одной задачей настоящего изобретения является создание устройства и способа, предназначенных для использования оптимального кодового слова посредством использования способа исключения символов из расширенного кода Рида-Мюллера первого порядка так, чтобы в процессе декодирования выполнялось обратное быстрое преобразование Адамара.

Еще одной задачей настоящего изобретения является создание устройства и способа, предназначенных для минимизации сложности аппаратных средств посредством минимизации длины ортогонального кода перед исключением символов.

Еще одной задачей настоящего изобретения является создание устройства и способа, предназначенных не только для минимизации сложности аппаратных средств посредством исключения символов из расширенного ортогонального кода, но также и для формирования кода, оптимального с точки зрения эффективности коррекции ошибок.

Еще одной задачей настоящего изобретения является создание устройства и способа, предназначенных для минимизации сложности аппаратных средств и для выполнения как кодирования (24,4), так и кодирования (24,7) для формирования кода, оптимального с точки зрения эффективности коррекции ошибок.

В соответствии с одним из аспектов настоящего изобретения предложен способ кодирования в системе мобильной связи, предназначенный для приема 4 входных битов информации, кодирования этих 4 входных битов информации с применением различных кодов Уолша длиной 16 и выдачи потока кодированных символов, состоящего из 24 кодированных символов, с использованием потока кодированных символов, состоящего из 16 кодированных символов, полученных посредством применения оператора “исключающее ИЛИ” к кодированным входным битам информации в блоке оператора “исключающее ИЛИ”. Способ кодирования заключается в том, что однократно повторяют упомянутый поток кодированных символов, состоящий из 16 кодированных символов, и, таким образом, выдают поток кодированных символов, состоящий из 32 кодированных символов, а также исключают 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 16-й символы из 32 кодированных символов и, таким образом, выдают поток из 24 кодированных символов.

В соответствии с другим аспектом настоящего изобретения предложен способ кодирования в системе мобильной связи, предназначенный для приема 7 входных битов информации, кодирования этих 7 входных битов информации с применением различных кодов Уолша длиной 32 и различных масок длиной 32 и выдачи потока кодированных символов, состоящего из 24 кодированных символов, с использованием потока кодированных символов, состоящего из 32 кодированных символов, полученного посредством применения оператора “исключающее ИЛИ” к кодированным входным битам информации в блоке оператора “исключающее ИЛИ”. Способ кодирования исключает 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й символы из 32 кодированных символов и, таким образом, выдает поток из 24 кодированных символов.

В соответствии с еще одним аспектом настоящего изобретения предложено устройство кодирования в системе мобильной связи, предназначенное для приема 4 или 7 входных битов информации, кодирования этих 4 или 7 входных битов информации с применением различных кодов Уолша или масок, причем длина каждого из кодов Уолша и каждой из масок равна 16 или 32, и выдачи потока кодированных символов, состоящего из 24 кодированных символов. Устройство кодирования включает в себя контроллер, предназначенный для определения того, является ли число входных битов информации равным 4 или 7, и управления процессом кодирования в соответствии с результатом вышеупомянутого определения; генератор кодов Уолша, предназначенный для избирательного формирования 5 различных кодов Уолша длиной 16 или 32 под управлением контроллера; генератор масок, предназначенный для избирательного формирования 2 различных масок длиной 16 или 32 под управлением контроллера; блоки умножения, предназначенные для умножения 4 или 7 входных битов информации на коды Уолша, выдаваемые генератором кодов Уолша, и на маски, выдаваемые генератором масок, на однозначной основе и выдачи потоков кодированных символов, каждый из которых состоит из 16 или 32 кодированных символов; блок оператора “исключающее ИЛИ”, предназначенный для применения оператора “исключающее ИЛИ” к потокам кодированных символов, выдаваемым блоками умножения, и выдачи одного потока кодированных символов; повторитель, предназначенный для повторения заданное число раз потока кодированных символов, выдаваемого блоком оператора “исключающее ИЛИ”, под управлением контроллера и выдачи потока кодированных символов, состоящего из 32 кодированных символов; запоминающее устройство, предназначенное для хранения 8 позиций исключения, соответствующих 4 входным битам информации, и 8 позиций исключения, соответствующих 7 входным битам информации, и блок исключения символов, предназначенный для приема от повторителя потока кодированных символов, состоящего из 32 кодированных символов, исключения кодированных символов, находящихся в 8 считанных из запоминающего устройства позициях исключения, из этих 32 кодированных символов под управлением контроллера и выдачи потока кодированных символов, состоящего из 24 кодированных символов.

В соответствии с еще одним аспектом настоящего изобретения предложено устройство кодирования в системе мобильной связи, предназначенное для приема 4 или 7 входных битов информации, кодирования этих 4 или 7 входных битов информации с применением различных кодов Уолша или масок, причем длина каждого из кодов Уолша и каждой маски равна 32, и выдачи потока кодированных символов, состоящего из 24 кодированных символов. Устройство кодирования включает в себя контроллер, предназначенный для определения того, является ли число входных битов информации равным 4 или 7, и управления процессом кодирования в соответствии с результатом вышеупомянутого определения; генератор кодов Уолша, предназначенный для избирательного формирования 5 различных кодов Уолша длиной 32; генератор масок, предназначенный для избирательного формирования 2 различных масок длиной 32; блоки умножения, предназначенные для умножения 4 или 7 входных битов информации на коды Уолша, выдаваемые генератором кодов Уолша, и на маски, выдаваемые генератором масок, на однозначной основе и выдачи потоков кодированных символов, каждый из которых состоит из 32 кодированных символов; блок оператора “исключающее ИЛИ”, предназначенный для применения оператора “исключающее ИЛИ” к потокам кодированных символов, выдаваемым блоками умножения, и выдачи одного потока кодированных символов; запоминающее устройство, предназначенное для хранения 8 позиций исключения, соответствующих 4 входным битам информации, и 8 позиций исключения, соответствующих 7 входным битам информации, и блок исключения символов, предназначенный для приема от блока оператора “исключающее ИЛИ” потока кодированных символов, состоящего из 32 кодированных символов, исключения кодированных символов, находящихся в 8 считанных из запоминающего устройства позициях исключения, из этих 32 кодированных символов под управлением контроллера и выдачи потока кодированных символов, состоящего из 24 кодированных символов.

ПЕРЕЧЕНЬ ФИГУР ЧЕРТЕЖЕЙ

Вышеупомянутые и иные задачи, признаки и преимущества настоящего изобретения становятся более очевидны при подробном описании, приведенном ниже совместно с сопровождающими его чертежами, на которых:

Фиг.1 иллюстрирует структуру передатчика обратного канала индикатора скорости (ОКнИС) в обычной системе мобильной связи МДКР;

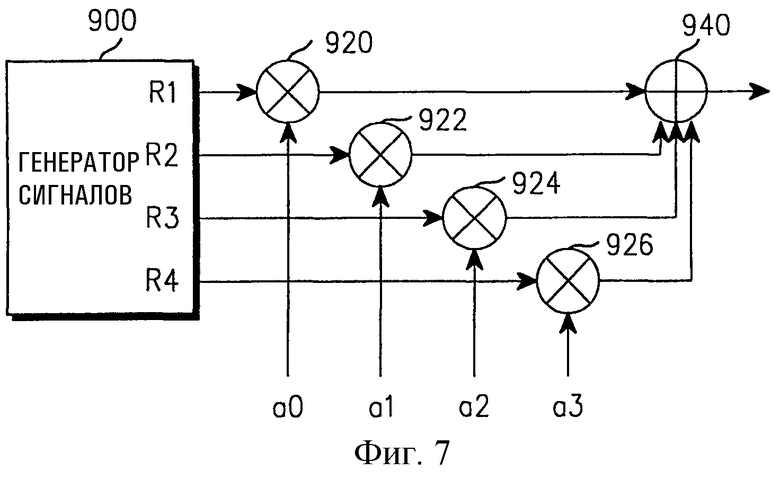

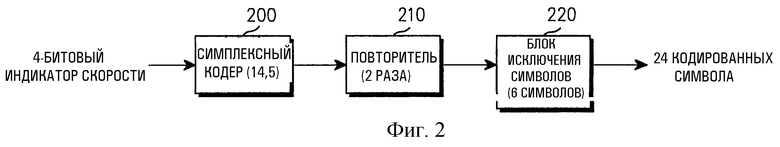

Фиг.2 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру оптимального кодера (24,4) в системе мобильной связи МДКР;

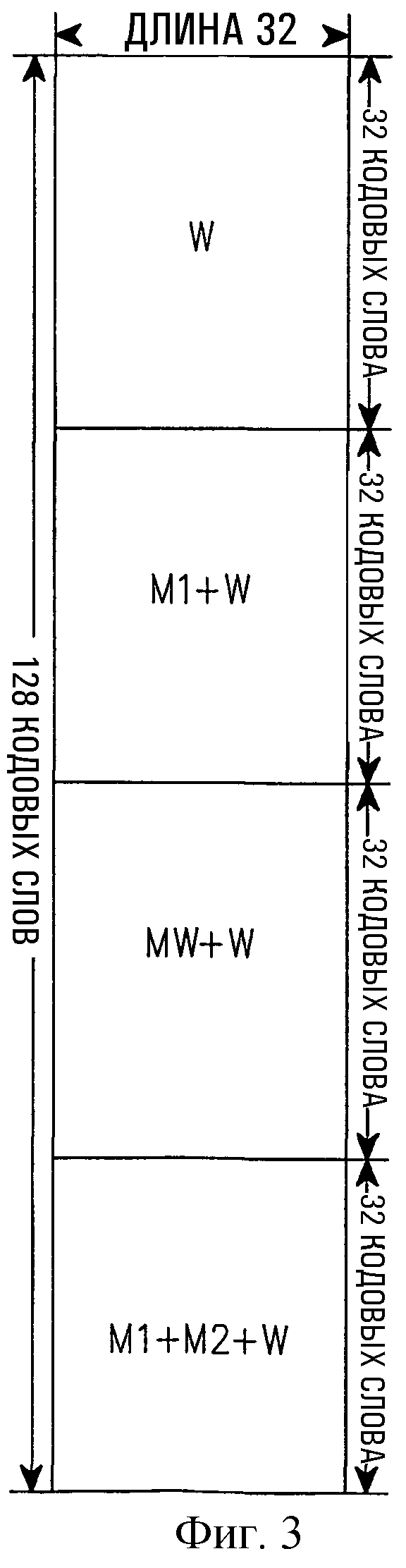

Фиг.3 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру кодового слова;

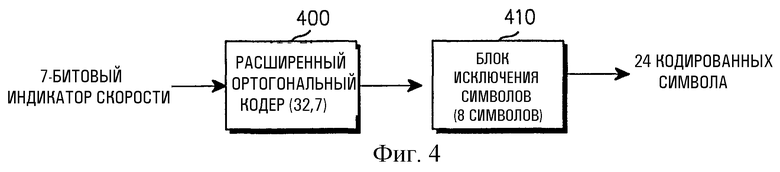

Фиг.4 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру оптимального кодера (24,7) в системе мобильной связи МДКР;

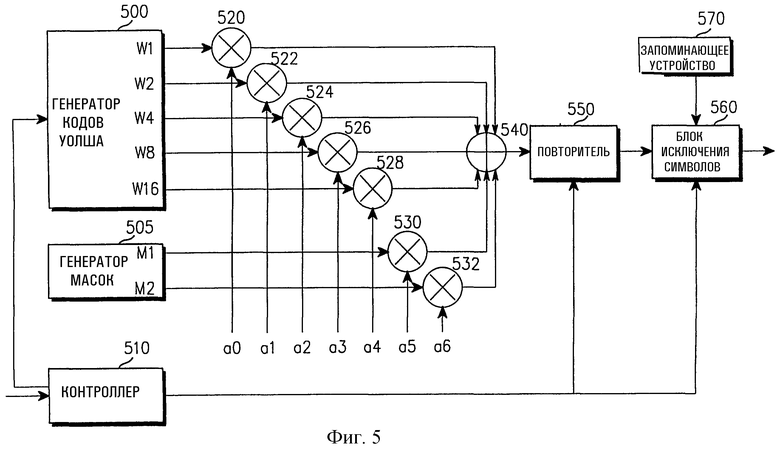

Фиг.5 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру кодера, функционирующего и как оптимальный кодер (24,4), и как оптимальный кодер (24,7) в системе мобильной связи МДКР;

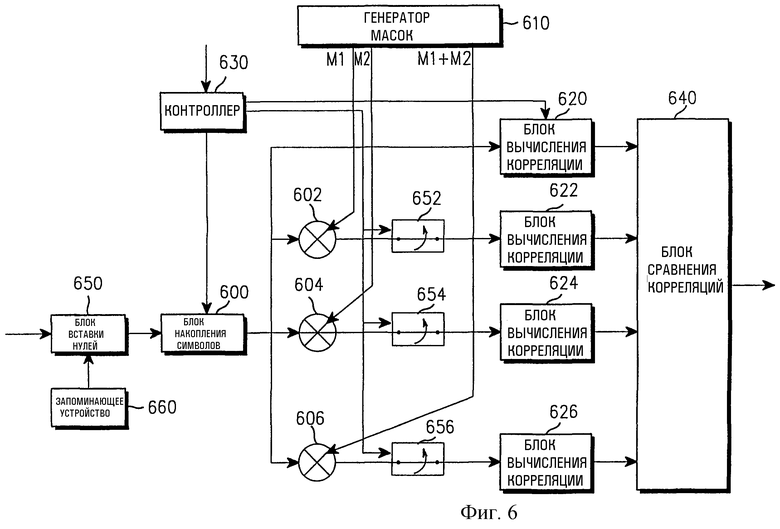

Фиг.6 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру декодера в системе мобильной связи МДКР;

Фиг.7 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру оптимального кодера (24,4) на основе формирующей матрицы;

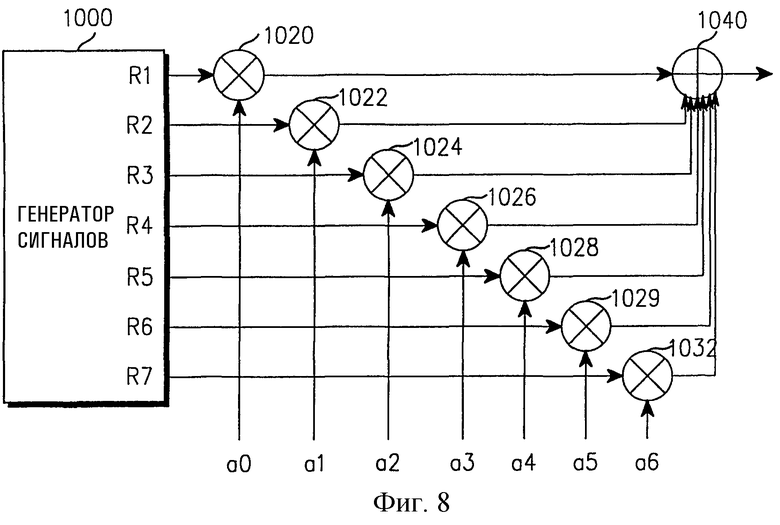

Фиг.8 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру оптимального кодера (24,7) на основе формирующей матрицы;

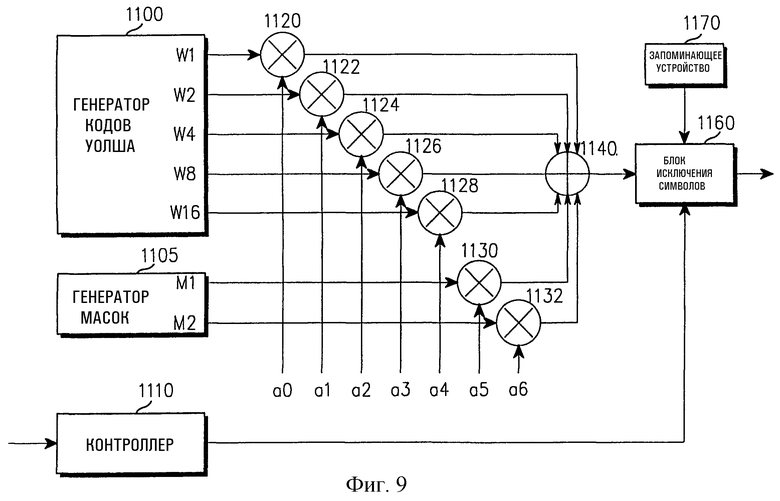

Фиг.9 иллюстрирует соответствующую варианту осуществления настоящего изобретения модифицированную структуру кодера, функционирующего и как оптимальный кодер (24,4), и как оптимальный кодер (24,7) в системе мобильной связи МДКР.

ПОДРОБНОЕ ОПИСАНИЕ

ПРЕДПОЧТИТЕЛЬНОГО ВАРИАНТА ОСУЩЕСТВЛЕНИЯ

Ниже описывается предпочтительный вариант осуществления настоящего изобретения со ссылкой на сопровождающие чертежи. В нижеизложенном описании детальное описание широко известных функций или конструкций опущено, так как излишние подробности могут затенить само изобретение.

В общем случае распределение расстояния Хэмминга для кодовых слов кодов с коррекцией ошибок служит мерой, являющейся индикатором эффективности линейных кодов с коррекцией ошибок. “Расстояние Хэмминга” указывает на число ненулевых символов в кодовом слове. Иными словами, для конкретного кодового слова ‘0111’ число символов 1, входящих в состав данного кодового слова, равно 3, следовательно, расстояние Хэмминга равно 3. Наименьшее значение среди значений расстояния Хэмминга называется “минимальным расстоянием dmin”, а увеличение минимального расстояния кодового слова повышает эффективность коррекции ошибок для кодов с коррекцией ошибок. Иными словами, понятие “оптимальный код” означает код, обладающий оптимальной эффективностью коррекции ошибок. Это подробно описано в статье The Theory of Error-Correcting Codes, F.J. Macwilliams, N.J.A. Sloane, North-Holland. Более того, статья An Updated Table of Minimum Distance Bounds for Binary Linear Codes (A.E. Brower и Tom Verhoeff, IEEE Transactions on Information Theory, т.39, №2, март 1993) описывает минимальное межкодовое расстояние, зависящее от входных и выходных значений двоичных линейных кодов для оптимального кода.

Для кодирования индикатора скорости обычно используется кодер (24,4) или кодер (24,7). В соответствии со второй из вышеупомянутых статей линейный кодер (24,4), предназначенный для приема 4 входных битов и выдачи 24 символов, характеризуется минимальным расстоянием, равным 12, в то время как линейный кодер (24,7), предназначенный для приема 7 входных битов и выдачи 24 символов, характеризуется минимальным расстоянием, равным 10.

Сначала приводится описание кодера (24,4), предназначенного для кодирования индикатора скорости.

Предлагаемый в настоящем изобретении кодер (24,4) выполнен с возможностью формирования оптимального кода (24,4) посредством двукратного повторения симплексного кода (15,4) и последующего исключения 6 символов из повторенного кода. Несмотря на то что существует множество способов формирования кода (24,4), оказывается возможным не только минимизировать сложность аппаратных средств, но и сформировать оптимальное кодовое слово посредством использования соответствующего варианту осуществления настоящего изобретения способа исключения символов из кода Рида-Мюллера первого порядка. Оказывается возможным минимизировать сложность аппаратных средств посредством минимизации длины симплексного кода перед исключением символов. Помимо этого, оказывается возможным не только минимизировать сложность аппаратных средств посредством исключения символов из симплексного кода, но также и сформировать код, оптимальный с точки зрения эффективности коррекции ошибок. Предполагается, что согласно рассматриваемому варианту осуществления настоящего изобретения код с коррекцией ошибок формируется с использованием симплексного кода.

Кодер (24,4) выдает кодовое слово, сформированное посредством формирования символов симплексного кода длиной 30, полученного двукратным повторением 15 кодированных символов, выдаваемых генератором симплексных кодов (15,4), и последующим исключением 6 символов из символов симплексного кода. Изменение позиций исключения, в которых находятся 6 символов, исключаемых из повторенных символов симплексного кода длиной 30, обуславливает изменение минимального расстояния dmin кодового слова. Следовательно, для создания кодера (24,4) с высокой эффективностью коррекции ошибок в симплексном коде (15,4) важно вычислить позиции исключения, обеспечивающие наибольшее минимальное расстояние.

6 позиций исключения, необходимых для формирования оптимального линейного кода (24,4), можно вычислить посредством экспериментирования. Простейшим шаблоном исключения является {0, 1, 2, 3, 4, 5}. В этом случае передатчику и приемнику системы мобильной связи, передающей 4 бита информации с использованием соответствующего настоящему изобретению способа кодирования/декодирования, следует заранее договориться о 6 позициях исключения. В общем случае позиции исключения определены в протоколе связи. В качестве альтернативы передатчик может заранее предоставить информацию о позициях исключения. Соответствующий настоящему изобретению способ кодирования оптимальным кодом (24,4) описывается со ссылкой на Фиг.2.

Фиг.2 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру кодера, входящего в состав передатчика. Согласно Фиг.2 4 входных бита a0, a1, a2 и a3 информации подаются в симплексный кодер 200 (15,4). В рассматриваемом случае 4 входных бита a0, a1, a2 и a3 информации составляют индикатор скорости. Симплексный кодер (или кодер Рида-Мюллера) 200 кодирует 4 входных бита a0, a1, a2 и a3 информации и выдает кодированные символы (или поток кодированных символов) длиной 15. Кодированные символы составляют симплексный код. Эти 15 кодированных символов подаются в повторитель 210. Повторитель 210 выдает 30 кодированных символов посредством двукратного повторения 15 принятых кодированных символов. После приема 30 кодированных символов блок 220 исключения символов исключает из этих 30 кодированных символов 0-й, 1-й, 2-й, 3-й, 4-й и 5-й символы, находящиеся в 6 оптимальных позициях исключения, и выдает 24 кодированных символа.

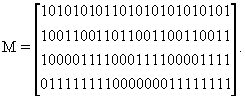

Для иллюстрации отношения отображения между входной информацией и кодированными символами общая теория кодов определяет формирующую матрицу. Когда включаются повторение символов и их исключение, формирующая матрица для конечного кодера (24,4) представляется в следующем виде.

Уравнение 1

Формирующая матрица по Уравнению 1 выбирает 24 символа из первой строки, если первый входной бит информации из 4 входных битов информации равен 1, и не выбирает никакие входные биты информации, если первый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из второй строки, если второй входной бит информации из 4 входных битов информации равен 1, и не выбирает никакие входные биты информации, если второй входной бит информации равен 0. Формирующая матрица выбирает 24 символа из третьей строки, если третий входной бит информации из 4 входных битов информации равен 1, и не выбирает никакие входные биты информации, если третий входной бит информации равен 0. Формирующая матрица выбирает 24 символа из четвертой строки, если четвертый входной бит информации из 4 входных битов информации равен 1, и не выбирает никакие входные биты информации, если четвертый входной бит информации равен 0.

Фиг.7 иллюстрирует кодер (24,4) на основе вышеприведенной формирующей матрицы. Согласно Фиг.7 из набора входных битов a0-a3 информации, значения которых равны 0 или 1, входной бит a0 информации подается в блок 920 умножения, входной бит a1 информации подается в блок 922 умножения, входной бит a2 информации подается в блок 924 умножения и входной бит a3 информации подается в блок 926 умножения соответственно. В то же время генератор 900 сигналов выдает 4 потока R1-R4 символов, составляющих хранимую в запоминающем устройстве формирующую матрицу, в блоки 920-926 умножения соответственно. Более конкретно, генератор 900 сигналов считывает поток R1=1010 1010 1101 0101 0101 0101 символов длиной 24, соответствующий первой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R1 символов в блок 920 умножения. Генератор 900 сигналов считывает поток R2=1001 1001 1011 0011 0011 0011 символов длиной 24, соответствующий второй строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R2 символов в блок 922 умножения. Генератор 900 сигналов считывает поток R3=1000 0111 1000 1111 0000 1111 символов длиной 24, соответствующий третьей строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R3 символов в блок 924 умножения. Наконец, генератор 900 сигналов считывает поток R4=0111 1111 1000 0000 1111 1111 символов длиной 24, соответствующий четвертой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R4 символов в блок 926 умножения. Далее блок 920 умножения умножает символы потока R1 символов на входной бит a0 информации и выдает поток символов длиной 24 в блок 940 оператора “исключающее ИЛИ”. Блок 922 умножения умножает символы потока R2 символов на входной бит a1 информации и выдает поток символов длиной 24 в блок 940 оператора “исключающее ИЛИ”. Блок 924 умножения умножает символы потока R3 символов на входной бит a2 информации и выдает поток символов длиной 24 в блок 940 оператора “исключающее ИЛИ”. Блок 926 умножения умножает символы потока R4 символов на входной бит a3 информации и выдает поток символов длиной 24 в блок 940 оператора “исключающее ИЛИ”. Затем блок 940 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к упомянутым 4 потокам символов длиной 24 и выдает поток кодированных символов длиной 24.

Далее приводится описание кодера (24,7), предназначенного для кодирования индикатора скорости.

Предлагаемый в настоящем изобретении кодер (24,7) выполнен с возможностью формирования оптимального кода (24,7) посредством исключения 8 символов из расширенного ортогонального кода, полученного кодированием кодового слова с расширением спектра с использованием 2 функций маски для ортогонального кода (32,5) (или кода Рида-Мюллера первого порядка).

Фиг.3 иллюстрирует структуру расширенного ортогонального кода. Согласно Фиг.3 в случае, если М1 и М2 представляют собой 2 вышеупомянутые функции маски, для верхних 32 кодовых слов используются 32 ортогональных кодовых слова W длиной 32, а для следующих 32 кодовых слов используются 32 кодовых слова (М1+W), определяемых посредством применения оператора “исключающее ИЛИ” к функции М1 маски и 32 ортогональным кодовым словам W. Далее для следующих 32 кодовых слов используются 32 кодовых слова (М2+W), определяемых посредством применения оператора “исключающее ИЛИ” к функции М2 маски и 32 ортогональным кодовым словам W, а для последних 32 кодовых слов используются 32 кодовых слова (М1+М2+W), определяемых посредством применения оператора “исключающее ИЛИ” к функциям М1 и М2 маски и 32 ортогональным кодовым словам W. Таким образом, в качестве расширенных ортогональных кодов используются кодовые слова в количестве 27=128. 2 функции маски, предназначенные для оптимизации кода (24,7), можно определить из эксперимента.

Например, пусть 2 функции М1 и М2 маски имеют следующий вид:

М1=0111 0111 0010 0100 0110 0000 0000 0000

М2=0010 0110 0101 0100 0101 0100 0100 0000.

Несмотря на то что существует множество способов формирования линейного кода (24,7), оказывается возможным не только минимизировать сложность аппаратных средств, но и сформировать оптимальное кодовое слово посредством использования соответствующего варианту осуществления настоящего изобретения способа исключения символов из расширенного кода Рида-Мюллера первого порядка. Помимо этого, оказывается возможным минимизировать сложность аппаратных средств посредством минимизации длины ортогонального кода перед исключением символов. Более того, оказывается возможным не только минимизировать сложность аппаратных средств посредством исключения символов из расширенного ортогонального кода, но также и сформировать код, оптимальный с точки зрения эффективности коррекции ошибок. Предполагается, что согласно рассматриваемому варианту осуществления настоящего изобретения код с коррекцией ошибок формируется с использованием расширенного ортогонального кода.

Кодовое слово (24,7) формируется посредством исключения 8 символов из 32 кодированных символов, выдаваемых генератором расширенных кодов (32,7). Изменение позиций исключения, в которых находятся 8 символов, исключаемые из 32 кодированных символов расширенного кода, обуславливает изменение минимального расстояния dmin кодового слова. Следовательно, для создания кодера (24,7) с высокой эффективностью коррекции ошибок в расширенном ортогональном коде (32,7) важно вычислить позиции исключения, обеспечивающие наибольшее минимальное расстояние.

8 позиций исключения, необходимых для формирования оптимального линейного кода (24,7), можно вычислить посредством экспериментирования. Простейшим шаблоном исключения является {0, 4, 8, 12, 16, 20, 24, 28}. В этом случае передатчику и приемнику системы мобильной связи, передающей 7 битов информации с использованием соответствующего настоящему изобретению способа кодирования/декодирования, следует заранее договориться о 8 позициях исключения. В общем случае позиции исключения определены в протоколе связи. В качестве альтернативы передатчик может заранее предоставить информацию о позициях исключения.

Фиг.4 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру оптимального кодера (24,7), входящего в состав передатчика. Согласно Фиг.4 7 входных битов a0, a1, a2, a3, a4, a5 и a6 информации подаются в расширенный ортогональный кодер 400 (32,7). В рассматриваемом случае 7 входных битов a0, a1, a2, a3, a4, a5 и a6 информации составляют индикатор скорости. Расширенный ортогональный кодер 400 кодирует 7 входных битов a0, a1, a2, a3, a4, a5 и a6 информации и выдает кодированные символы (или поток кодированных символов) длиной 32. 32 кодированных символа, выдаваемых расширенным ортогональным кодером 400, подаются в блок 410 исключения символов. Блок 410 исключения символов исключает из этих 32 кодированных символов 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й символы, находящиеся в 8 оптимальных позициях исключения, и выдает 24 кодированных символа.

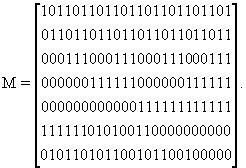

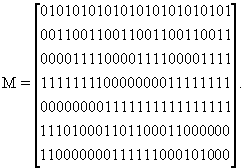

Для отображения отношения отображения между входной информацией и кодированными символами общая теория кодов определяет формирующую матрицу. Когда включается исключение символов, формирующая матрица для оконечного кодера (24,7) представляется в следующем виде.

Уравнение 2

Формирующая матрица по Уравнению 2 выбирает 24 символа из первой строки, если первый входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если первый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из второй строки, если второй входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если второй входной бит информации равен 0. Формирующая матрица выбирает 24 символа из третьей строки, если третий входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если третий входной бит информации равен 0. Формирующая матрица выбирает 24 символа из четвертой строки, если четвертый входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если четвертый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из пятой строки, если пятый входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если пятый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из шестой строки, если шестой входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если шестой входной бит информации равен 0. Формирующая матрица выбирает 24 символа из седьмой строки, если седьмой входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если седьмой входной бит информации равен 0. Кодированные символы, соответствующие входным битам информации, выдаются после того как оператор “исключающее ИЛИ” посимвольно применяется ко всем выбранным строкам.

Фиг.8 иллюстрирует кодер (24,7) на основе вышеприведенной формирующей матрицы. Согласно Фиг.8 из набора входных битов a0-a6 информации, значения которых равны 0 или 1, входной бит a0 информации подается в блок 1020 умножения, входной бит a1 информации подается в блок 1022 умножения, входной бит a2 информации подается в блок 1024 умножения, входной бит a3 информации подается в блок 1026 умножения, входной бит a4 информации подается в блок 1028 умножения, входной бит a5 информации подается в блок 1029 умножения и входной бит a6 информации подается в блок 1032 умножения соответственно. В то же время генератор 1000 сигналов выдает 7 потоков R1-R7 символов, составляющих хранимую в запоминающем устройстве формирующую матрицу, в блоки 1020-1032 умножения соответственно. Более конкретно, генератор 1000 сигналов считывает поток R1=1011 0110 1101 1011 0110 1101 символов длиной 24, соответствующий первой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R1 символов в блок 1020 умножения. Генератор 1000 сигналов считывает поток R2=0110 1101 1011 0110 1101 1011 символов длиной 24, соответствующий второй строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R2 символов в блок 1022 умножения. Генератор 1000 сигналов считывает поток R3=0001 1100 0111 0001 1100 0111 символов длиной 24, соответствующий третьей строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R3 символов в блок 1024 умножения. Генератор 1000 сигналов считывает поток R4=0000 0011 1111 0000 0011 1111 символов длиной 24, соответствующий четвертой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R4 символов в блок 1026 умножения. Генератор 1000 сигналов считывает поток R5=0000 0000 0000 1111 1111 1111 символов длиной 24, соответствующий пятой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R5 символов в блок 1028 умножения. Генератор 1000 сигналов считывает поток R6=1111 1101 0100 1100 0000 0000 символов длиной 24, соответствующий шестой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R6 символов в блок 1029 умножения. Генератор 1000 сигналов считывает поток R7=0101 1010 1100 1011 0010 0000 символов длиной 24, соответствующий седьмой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R7 символов в блок 1032 умножения. Далее блок 1020 умножения умножает символы потока R1 символов на входной бит a0 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1022 умножения умножает символы потока R2 символов на входной бит a1 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1024 умножения умножает символы потока R3 символов на входной бит a2 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1026 умножения умножает символы потока R4 символов на входной бит a3 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1028 умножения умножает символы потока R5 символов на входной бит a4 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1029 умножения умножает символы потока R6 символов на входной бит a5 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1032 умножения умножает символы потока R7 символов на входной бит a6 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Затем блок 1040 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к упомянутым 7 потокам символов длиной 24 и выдает поток кодированных символов длиной 24.

Оказывается возможным повысить эффективность кодера (24,7) и минимизировать его сложность в зависимости от позиций исключения символов. Шаблон {0, 4, 8, 12, 16, 20, 24, 28} характеризуется регулярным интервалом исключения, равным 4. Подобная регулярность позиций исключения способствует снижению сложности аппаратных средств. Однако в случае, если позиции исключения сконцентрированы в головной части кадра, оказывается возможным снизить сложность аппаратных средств, используя способ задержки. Следовательно, если позиции исключения сосредоточены в головной части кадра, то, принимая во внимание эффективность, 2 функции маски будут иметь другие структуры.

Далее со ссылкой на Фиг.3 описывается структура расширенного ортогонального кода с другими позициями исключения. В случае, если М1 и М2 представляют собой 2 вышеупомянутые функции маски, для верхних 32 кодовых слов используются 32 ортогональных кодовых слова W длиной 32, а для следующих 32 кодовых слов используются 32 кодовых слова (М1+W), определяемых посредством применения оператора “исключающее ИЛИ” к функции М1 маски и 32 ортогональным кодовым словам W. Далее для следующих 32 кодовых слов используются 32 кодовых слова (М2+W), определяемых посредством применения оператора “исключающее ИЛИ” к функции М2 маски и 32 ортогональным кодовым словам W, а для последних 32 кодовых слов используются 32 кодовых слова (М1+М2+W), определяемых посредством применения оператора “исключающее ИЛИ” к функциям М1 и М2 маски и 32 ортогональным кодовым словам W. Таким образом, в качестве расширенных ортогональных кодов используются кодовые слова в количестве 27=128. 2 функции маски, предназначенные для оптимизации кода (24,7), можно определить путем экспериментирования.

Например, пусть 2 функции М1 и М2 маски имеют следующий вид:

М1=0000 0000 1110 1000 1101 1000 1100 0000

М2=0000 0000 1100 0000 0111 1110 0010 1000.

Несмотря на то что существует множество способов формирования линейного кода (24,7), оказывается возможным не только минимизировать сложность аппаратных средств, но также и использовать оптимальное кодовое слово посредством использования соответствующего варианту осуществления настоящего изобретения способа исключения символов из расширенного кода Рида-Мюллера первого порядка. Помимо этого, оказывается возможным минимизировать сложность аппаратных средств посредством минимизации длины ортогонального кода перед исключением символов. Более того, оказывается возможным не только минимизировать сложность аппаратных средств посредством исключения символов из расширенного ортогонального кода, но также и сформировать код, оптимальный с точки зрения эффективности коррекции ошибок. Предполагается, что согласно рассматриваемому варианту осуществления настоящего изобретения код с коррекцией ошибок формируется с использованием расширенного ортогонального кода.

Кодовое слово (24,7) формируется посредством исключения 8 символов из 32 кодированных символов, выдаваемых генератором расширенных кодов (32,7). Изменение позиций исключения, в которых находятся 8 символов, исключаемых из 32 кодированных символов расширенного кода, обуславливает изменение минимального расстояния dmin кодового слова. Следовательно, для создания кодера (24,7) с высокой эффективностью коррекции ошибок в расширенном ортогональном коде (32,7) важно вычислить позиции исключения, обеспечивающие наибольшее минимальное расстояние.

8 позиций исключения, необходимых для формирования оптимального линейного кода (24,7), можно вычислить посредством экспериментирования. Простейшим шаблоном исключения является {0, 1, 2, 3, 4, 5, 6, 7}. В этом случае передатчику и приемнику системы мобильной связи, передающей 7 битов информации с использованием соответствующего настоящему изобретению способа кодирования/декодирования, следует заранее договориться о 8 позициях исключения. В общем случае позиции исключения определены в протоколе связи. В качестве альтернативы передатчик может заранее предоставить информацию о позициях исключения.

Фиг.4 иллюстрирует соответствующую варианту осуществления настоящего изобретения структуру оптимального кодера (24,7), входящего в состав передатчика. Согласно Фиг.4 7 входных битов a0, a1, a2, a3, a4, a5 и a6 информации подаются в расширенный ортогональный кодер 400 (32,7). В рассматриваемом случае 7 входных битов a0, a1, a2, a3, a4, a5 и a6 информации составляют индикатор скорости. Расширенный ортогональный кодер 400 кодирует 7 входных битов a0, a1, a2, a3, a4, a5 и a6 информации и выдает кодированные символы (или поток кодированных символов) длиной 32. 32 кодированных символа, выдаваемых расширенным ортогональным кодером 400, подаются в блок 410 исключения символов. Блок 410 исключения символов исключает из этих 32 кодированных символов 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й символы, находящиеся в 8 оптимальных позициях исключения, и выдает 24 кодированных символа.

Для отображения отношения отображения между входной информацией и кодированными символами общая теория кодов определяет формирующую матрицу. Когда включается исключение символов, формирующая матрица для оконечного кодера (24,7) представляется в следующем виде.

Уравнение 3

Формирующая матрица по Уравнению 3 выбирает 24 символа из первой строки, если первый входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если первый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из второй строки, если второй входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если второй входной бит информации равен 0. Формирующая матрица выбирает 24 символа из третьей строки, если третий входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если третий входной бит информации равен 0. Формирующая матрица выбирает 24 символа из четвертой строки, если четвертый входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если четвертый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из пятой строки, если пятый входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если пятый входной бит информации равен 0. Формирующая матрица выбирает 24 символа из шестой строки, если шестой входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если шестой входной бит информации равен 0. Формирующая матрица выбирает 24 символа из седьмой строки, если седьмой входной бит информации из 7 входных битов информации равен 1, и не выбирает никакие входные биты информации, если седьмой входной бит информации равен 0. Кодированные символы, соответствующие входным битам информации, выдаются после того как оператор “исключающее ИЛИ” посимвольно применяется ко всем выбранным строкам.

Фиг.8 иллюстрирует кодер (24,7) на основе вышеприведенной формирующей матрицы. Согласно Фиг.8 из набора входных битов a0-a6 информации, значения которых равны 0 или 1, входной бит a0 информации подается в блок 1020 умножения, входной бит a1 информации подается в блок 1022 умножения, входной бит a2 информации подается в блок 1024 умножения, входной бит a3 информации подается в блок 1026 умножения, входной бит a4 информации подается в блок 1028 умножения, входной бит a5 информации подается в блок 1029 умножения и входной бит a6 информации подается в блок 1032 умножения соответственно. В то же время генератор 1000 сигналов выдает 7 потоков R1-R7 символов, составляющих хранимую в запоминающем устройстве формирующую матрицу, в блоки 1020-1032 умножения соответственно. Более конкретно, генератор 1000 сигналов считывает поток R1=0101 0101 0101 0101 0101 0101 символов длиной 24, соответствующий первой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R1 символов в блок 1020 умножения. Генератор 1000 сигналов считывает поток R2=0011 0011 0011 0011 0011 0011 символов длиной 24, соответствующий второй строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R2 символов в блок 1022 умножения. Генератор 1000 сигналов считывает поток

R3=0000 1111 0000 1111 0000 1111 символов длиной 24, соответствующий третьей строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R3 символов в блок 1024 умножения. Генератор 1000 сигналов считывает поток R4=1111 1111 0000 0000 1111 1111 символов длиной 24, соответствующий четвертой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R4 символов в блок 1026 умножения. Генератор 1000 сигналов считывает поток R5=0000 0000 1111 1111 1111 1111 символов длиной 24, соответствующий пятой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R5 символов в блок 1028 умножения. Генератор 1000 сигналов считывает поток R6=1110 1000 1101 1000 1100 0000 символов длиной 24, соответствующий шестой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R6 символов в блок 1029 умножения. Генератор 1000 сигналов считывает поток R7=1100 0000 0111 1110 0010 1000 символов длиной 24, соответствующий седьмой строке хранимой в запоминающем устройстве формирующей матрицы, и выдает считанный поток R7 символов в блок 1032 умножения. Далее блок 1020 умножения умножает символы потока R1 символов на входной бит a0 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1022 умножения умножает символы потока R2 символов на входной бит a1 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1024 умножения умножает символы потока R3 символов на входной бит a2 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1026 умножения умножает символы потока R4 символов на входной бит a3 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1028 умножения умножает символы потока R5 символов на входной бит a4 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1029 умножения умножает символы потока R6 символов на входной бит a5 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Блок 1032 умножения умножает символы потока R7 символов на входной бит a6 информации и выдает поток символов длиной 24 в блок 1040 оператора “исключающее ИЛИ”. Затем блок 1040 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к упомянутым 7 потокам символов длиной 24 и выдает поток кодированных символов длиной 24.

Кодер (24,4) и кодер (24,7) имеют некие общие черты в том смысле, что оба они основаны на структуре ортогонального кода. То есть используемый в кодере (24,4) симплексный код (15,4) получается посредством исключения 0-й строки из ортогонального кода (16,4), а используемый в кодере (24,7) расширенный ортогональный код (32,7) получается посредством расширения, выполняемого кодером (32,5) с использованием основ 2 дополнительных кодовых слов (функций маски). Таким образом, на основе вышеупомянутых общих черт кодера (24,4) и кодера (24,7) в описываемом ниже первом варианте осуществления предлагается кодер, функционирующий и как кодер (24,4), и как кодер (24,7) с разными длинами.

Первый вариант осуществления (кодер)

Фиг.5 иллюстрирует структуру кодера, функционирующего и как кодер (24,4), и как кодер (24,7) с разными длинами. То есть кодер по Фиг.5 кодирует 4 или 7 входных битов информации с применением различных кодов Уолша или масок, причем длина каждого кода Уолша и каждой маски равна 16 или 32, и выдает поток кодированных символов, состоящий из 24 кодированных символов.

Согласно Фиг.5 контроллер 510 управляет процессом кодирования посредством определения того, является ли число входных битов информации равным 4 или 7. Иными словами, в случае, когда число входных битов информации равно 4, контроллер 510 предписывает генератору 500 кодов Уолша и генератору 505 масок сформировать 5 различных кодов Уолша и 2 различные маски соответственно, причем длина каждого из кодов Уолша и каждой из масок равна 16. Помимо этого, контроллер 510 устанавливает частоту повторений повторителя 550 равной 1 и предписывает блоку 560 исключения символов исключить символы, находящиеся в 8 позициях исключения, соответствующих 4 входным битам информации. Однако в случае, когда число входных битов информации равно 7, контроллер 510 предписывает генератору 500 кодов Уолша и генератору 505 масок сформировать 5 различных кодов Уолша и 2 различные маски соответственно, причем длина каждого из кодов Уолша и каждой из масок равна 32. Помимо этого, контроллер 510 устанавливает частоту повторений повторителя 550 равной 0 и предписывает блоку 560 исключения символов исключить символы, находящиеся в 8 позициях исключения, соответствующих 7 входным битам информации.

Под управлением контроллера 510 генератор 500 кодов Уолша избирательно формирует различные коды Уолша длиной 16 или 32. Например, после приема 4 входных битов информации генератор 500 кодов Уолша формирует 5 различных кодов Уолша длиной 16 под управлением контроллера 510. После приема 7 входных битов информации генератор 500 формирует 5 различных кодов Уолша длиной 32 под управлением контроллера 510. Число кодов Уолша, формируемых генератором 500 кодов Уолша, может меняться в зависимости от числа (4 или 7) входных битов информации. Например, после приема 4 входных битов информации генератор 500 кодов Уолша может сформировать 4 кода Уолша длиной 16, а после приема 7 входных битов информации данный генератор может сформировать 5 кодов Уолша длиной 32.

Под управлением контроллера 510 генератор 505 масок избирательно формирует различные маски длиной 16 или 32. Например, после приема 4 входных битов информации генератор 505 масок формирует 2 различные маски длиной 16 под управлением контроллера 510. После приема 7 входных битов информации генератор 505 формирует 2 различные маски длиной 32 под управлением контроллера 510. В качестве альтернативы генератор 505 масок можно сконструировать так, чтобы он непрерывно формировал 2 различные маски без управления со стороны контроллера 510. Фиг.5 иллюстрирует последний пример, в котором генератор 505 масок не управляется контроллером 510. В случае, если генератор 505 масок функционирует под управлением контроллера 510, на генератор 505 масок подается сигнал управления от контроллера 510.

Блоки 520-532 умножения умножают 4 или 7 входных битов информации на коды Уолша и маски, выдаваемые генератором 500 кодов Уолша и генератором 505 масок, на однозначной основе и выдают потоки кодированных символов, каждый из которых состоит из 16 или 32 кодированных символов. В случае, когда в качестве входных битов информации приняты 4 входных бита, в качестве остающихся входных битов a4, a5 и a6 информации предоставляются входные биты, значения которых равны ‘0’, так что выходные значения остаются без изменений. Блок 540 оператора “исключающее ИЛИ” применяет оператор “исключающее ИЛИ” к потокам кодированных символов, выдаваемым блоками 520-532 умножения, и выдает один поток кодированных символов, состоящий из 16 или 32 кодированных символов. Под управлением контроллера 510 повторитель 550 заданное число раз повторяет поток кодированных символов, выдаваемый блоком 540 оператора “исключающее ИЛИ”, и выдает поток кодированных символов, состоящий из 32 кодированных символов. Иными словами, после приема потока кодированных символов, состоящего из 16 кодированных символов, повторитель 550 однократно повторяет принятый поток кодированных символов и выдает поток кодированных символов, состоящий из 32 кодированных символов. Однако после приема потока кодированных символов, состоящего из 32 кодированных символов, повторитель 550 выдает принятый поток кодированных символов без изменений, не выполняя при этом повторения. Запоминающее устройство 570 хранит 8 позиций исключения, соответствующих 4 входным битам информации, и 8 позиций исключения, соответствующих 7 входным битам информации. Хранимые в запоминающем устройстве 570 8 позиций исключения, соответствующие 4 входным битам информации, - это 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 16-я позиции символов, в то время как хранимые в запоминающем устройстве 570 8 позиций исключения, соответствующие 7 входным битам информации, - это 0-я, 4-я, 8-я, 12-я, 16-я, 20-я, 24-я и 28-я позиции символов или 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 7-я позиции символов.

Блок 560 исключения символов принимает от повторителя 550 поток кодированных символов, состоящий из 32 кодированных символов, под управлением контроллера 510 исключает кодированные символы, находящиеся в 8 считанных из запоминающего устройства 570 позициях исключения, из этих 32 кодированных символов и выдает поток кодированных символов, состоящий из 24 кодированных символов. То есть, если число входных битов информации равно 4, то блок 560 исключения символов под управлением контроллера 510 исключает 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 16-й символы из 32 кодированных символов, выдаваемых повторителем 550, и выдает поток кодированных символов, состоящий из 24 кодированных символов. Если же число входных битов информации равно 7, то блок 560 исключения символов под управлением контроллера 510 исключает 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й символы или 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й символы из 32 кодированных символов, выдаваемых повторителем 550, и выдает поток кодированных символов, состоящий из 24 кодированных символов.

Ниже со ссылкой на Фиг.5 приводится отдельное описание рассматриваемого кодера для случая, когда он функционирует как кодер (24,4), и отдельное описание для другого случая, когда рассматриваемый кодер функционирует как кодер (24,7). Далее по тексту предполагается, что подаваемые на кодер входные биты информации составляют индикатор скорости.

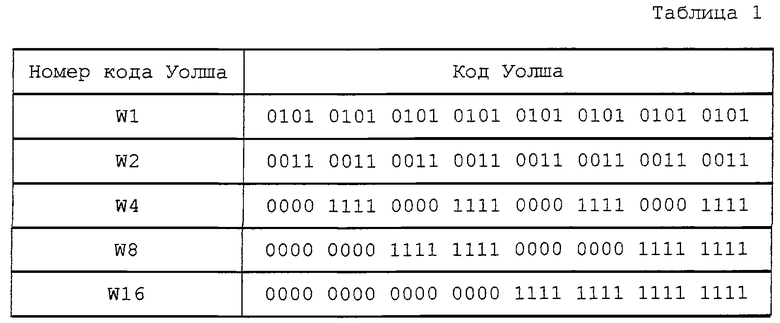

Сначала приводится описание одного из случаев, когда рассматриваемый кодер функционирует как кодер (24,7). В кодер подается 7-битовый индикатор скорости, состоящий из битов a0, a1, a2, a3, a4, a5 и a6, и в то же самое время на контроллер 510 подается информация в виде битов, указывающая на то, что в кодер поступил 7-битовый индикатор скорости. Далее контроллер 510 выдает на генератор 500 кодов Уолша сигнал управления, предписывающий ему сформировать коды Уолша длиной 32. После приема сигнала управления генератор 500 кодов Уолша формирует коды W1, W2, W4, W8 и W16 Уолша длиной 32 и выдает сформированные коды W1, W2, W4, W8 и W16 Уолша в соответствующие блоки умножения. Более конкретно, код W1 Уолша выдается в блок 520 умножения, код W2 Уолша выдается в блок 522 умножения, код W4 Уолша выдается в блок 524 умножения, код W8 Уолша выдается в блок 526 умножения и код W16 Уолша выдается в блок 528 умножения. В Таблице 1 приведены коды Уолша длиной 32, формируемые генератором 500 кодов Уолша.

В то же самое время генератор 505 масок формирует маску М1=0111 0111 0010 0100 0110 0000 0000 0000 и маску М2=0010 0110 0101 0100 0101 0100 0100 0000 и выдает сформированные маски М1 и М2 в блоки 530 и 532 умножения соответственно.

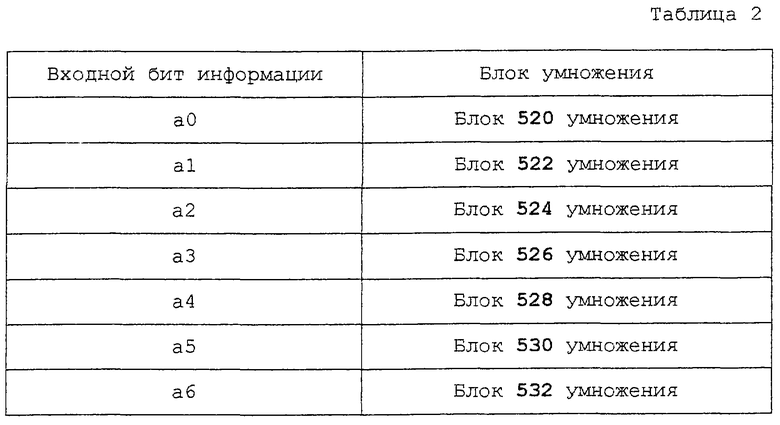

Тем временем 7 входных битов информации, составляющие индикатор скорости, подаются в соответствующие блоки умножения. В Таблице 2 приведены связи между 7 входными битами информации и соответствующими блоками умножения.

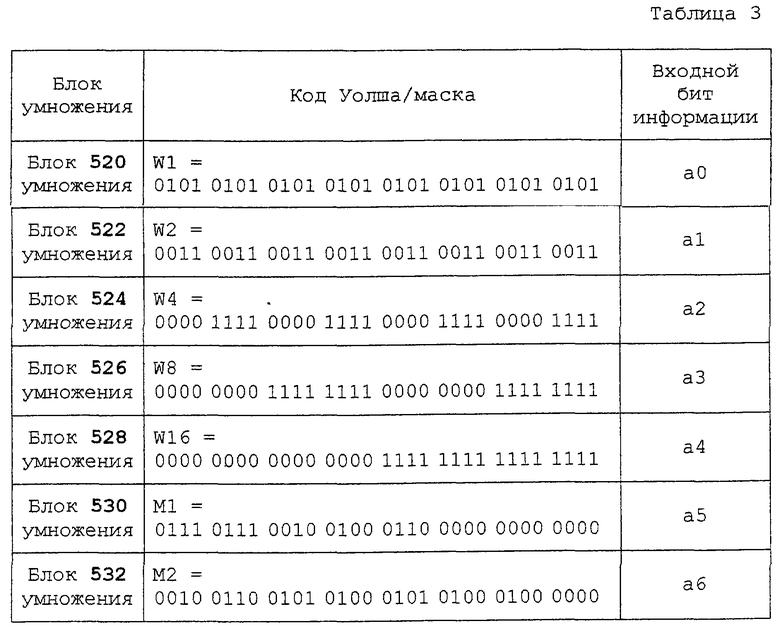

Таким образом, в Таблице 3 приводятся входные биты информации и коды Уолша или маски, подаваемые в соответствующие блоки умножения.

Блоки умножения умножают входные биты информации на коды Уолша или маски, как показано в Таблице 3, и выдают свои выходные данные в блок 540 оператора “исключающее ИЛИ”.

Более конкретно, блок 520 умножения умножает входной бит a0 информации на каждый символ кода W1 Уолша (то есть посимвольно) и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 522 умножения умножает входной бит a1 информации на каждый символ кода W2 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 524 умножения умножает входной бит a2 информации на каждый символ кода W4 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 526 умножения умножает входной бит a3 информации на каждый символ кода W8 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 528 умножения умножает входной бит a4 информации на каждый символ кода W16 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 530 умножения умножает входной бит a5 информации на каждый символ маски М1 и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 532 умножения умножает входной бит a6 информации на каждый символ маски М2 и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”.

Затем блок 540 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к потокам символов длиной 32, выдаваемым блоками умножения 520, 522, 524, 526, 528, 530 и 532, и выдает свои выходные данные в повторитель 550.

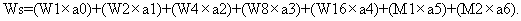

Поток Ws кодированных символов длиной 32, выдаваемый блоком 540 оператора “исключающее ИЛИ”, можно определить следующим образом.

Уравнение 4

В этот момент контроллер 510 выдает в повторитель 550 сигнал управления, предназначенный для управления частотой повторения выходных данных блока 540 оператора “исключающее ИЛИ”. В силу того что в кодере (24,7) длина потока символов, выдаваемого блоком 540 оператора “исключающее ИЛИ”, равна 32, повторитель 550 не выполняет повторения. С этой целью контроллер 510 выдает в повторитель 550 сигнал управления, предписывающий ему выдавать входной сигнал без изменений. В ответ на сигнал управления повторитель 550 выдает в блок 560 исключения символов поток символов длиной 32, полученный от блока 540 оператора “исключающее ИЛИ”, без изменений.

В этот момент контроллер 510 выдает в блок 560 исключения символов сигнал управления, предписывающий ему исключить символы, находящиеся в позициях исключения для кода (24,7). Контроллер 510 может в качестве сигнала управления предоставить блоку 560 исключения символов информацию о длине (7 бит) индикатора скорости. Далее блок 560 исключения символов принимает от запоминающего устройства 570 8 позиций исключения, соответствующих 7 входным битам информации, составляющим индикатор скорости, и исключает кодированные символы, находящиеся в упомянутых позициях исключения, из потока кодированных символов длиной 32, выдаваемого повторителем 550. То есть блок 560 исключения символов исключает 8 символов, находящихся в считанных из запоминающего устройства 570 позициях исключения, из потока кодированных символов длиной 32, выдаваемого повторителем 550. Например, в случае, если считанные из запоминающего устройства 570 позиции исключения - это 0-я, 4-я, 8-я, 12-я, 16-я, 20-я, 24-я и 28-я позиции символов, блок 560 исключения символов исключает 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й кодированные символы из потока кодированных символов длиной 32 и выдает 24 кодированных символа.

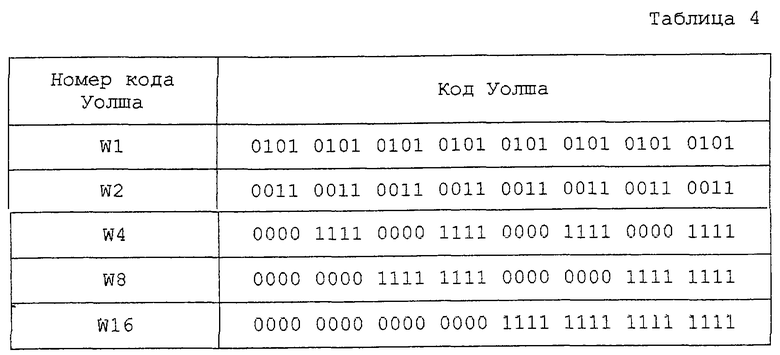

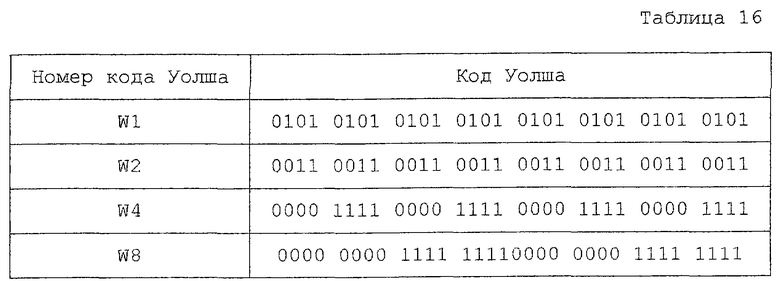

До настоящего момента функционирование кодера (24,7) описывалось со ссылкой на один из случаев, когда шаблоном исключения кодера (24,7) является {0, 4, 8, 12, 16, 20, 24, 28}. Далее описывается функционирование кодера (24,7) со ссылкой на другой случай, когда шаблоном исключения данного кодера является {0, 1, 2, 3, 4, 5, 6, 7}, с целью снижения сложности аппаратных средств, о чем говорилось ранее. В этом случае, когда в кодер подается 7-битовый индикатор скорости, состоящий из битов a0, a1, a2, a3, a4, a5 и a6, в контроллер 510 подается информация в виде битов, указывающая на то, что в кодер поступил 7-битовый индикатор скорости. Далее контроллер 510 выдает в генератор 500 кодов Уолша сигнал управления, предписывающий ему сформировать коды Уолша длиной 32. После приема сигнала управления генератор 500 кодов Уолша формирует коды W1, W2, W4, W8 и W16 Уолша длиной 32 и выдает сформированные коды W1, W2, W4, W8 и W16 Уолша в соответствующие блоки умножения. Более конкретно, код W1 Уолша выдается в блок 520 умножения, код W2 Уолша выдается в блок 522 умножения, код W4 Уолша выдается в блок 524 умножения, код W8 Уолша выдается в блок 526 умножения, и код W16 Уолша выдается в блок 528 умножения. В Таблице 4 приведены коды Уолша длиной 32, формируемые генератором 500 кодов Уолша.

В то же самое время генератор 505 масок формирует маску М1=0000 0000 1110 1000 1101 1000 1100 0000 и маску М2=0000 0000 1100 0000 0111 1110 0010 1000 и выдает сформированные маски М1 и М2 в блоки 530 и 532 умножения соответственно.

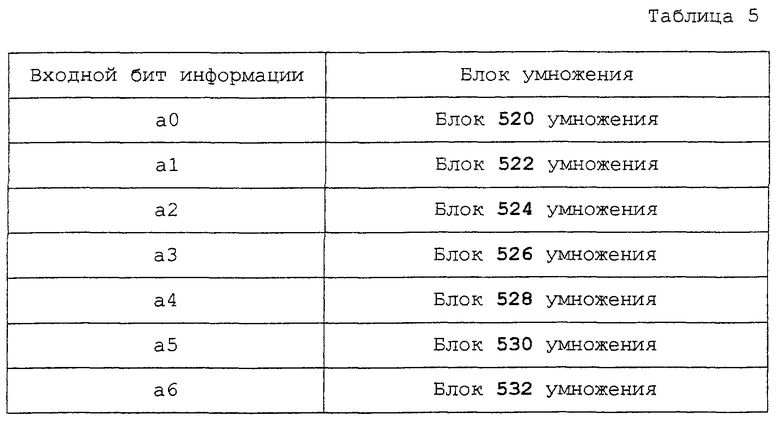

Тем временем 7 входных битов информации, составляющие индикатор скорости, подаются в соответствующие блоки умножения. В Таблице 5 приведены связи между 7 входными битами информации и соответствующими блоками умножения.

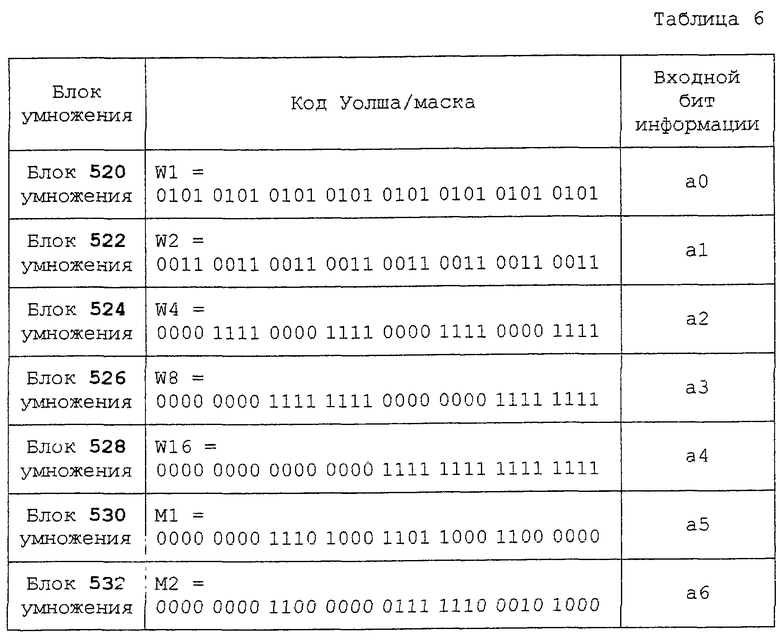

Таким образом, в Таблице 6 приводятся входные биты информации и коды Уолша или маски, подаваемые в соответствующие блоки умножения.

Блоки умножения умножают входные биты информации на коды Уолша или маски, как показано в Таблице 6, и выдают свои выходные данные в блок 540 оператора “исключающее ИЛИ”.

Более конкретно, блок 520 умножения умножает входной бит a0 информации на каждый символ кода W1 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 522 умножения умножает входной бит a1 информации на каждый символ кода W2 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 524 умножения умножает входной бит a2 информации на каждый символ кода W4 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 526 умножения умножает входной бит a3 информации на каждый символ кода W8 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 528 умножения умножает входной бит a4 информации на каждый символ кода W16 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 530 умножения умножает входной бит a5 информации на каждый символ маски М1 и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 532 умножения умножает входной бит a6 информации на каждый символ маски М2 и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”.

Затем блок 540 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к потокам символов длиной 32, выдаваемым блоками умножения 520, 522, 524, 526, 528, 530 и 532, и выдает свои выходные данные в повторитель 550.

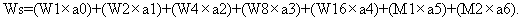

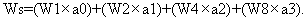

Поток Ws кодированных символов длиной 32, выдаваемый блоком 540 оператора “исключающее ИЛИ”, определяется следующим образом.

Уравнение 5

В этот момент контроллер 510 выдает в повторитель 550 сигнал управления, предназначенный для управления частотой повторения выходных данных блока 540 оператора “исключающее ИЛИ”. В силу того что в кодере (24,7) длина потока символов, выдаваемого блоком 540 оператора “исключающее ИЛИ”, равна 32, частота повторения в повторителе 550 равна ‘0’.

Следовательно, контроллер 510 выдает в повторитель 550 сигнал управления, предписывающий ему выдавать входной сигнал без изменений. В ответ на сигнал управления повторитель 550 выдает в блок 560 исключения символов поток символов длиной 32, полученный от блока 540 оператора “исключающее ИЛИ”, без изменений.

В этот момент контроллер 510 выдает в блок 560 исключения символов сигнал управления, предписывающий ему исключить символы, находящиеся в позициях исключения для кода (24,7). Далее блок 560 исключения символов принимает от запоминающего устройства 570 8 позиций исключения и исключает кодированные символы, находящиеся в упомянутых позициях исключения, из потока кодированных символов длиной 32, выдаваемого повторителем 550. То есть блок 560 исключения символов исключает 8 символов, находящихся в считанных из запоминающего устройства 570 позициях исключения, из потока кодированных символов длиной 32, выдаваемого повторителем 550. Например, в случае, если считанные из запоминающего устройства 570 позиции исключения - это 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 7-я позиции символов, блок 560 исключения символов исключает 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й кодированные символы из потока кодированных символов длиной 32 и выдает 24 кодированных символа.

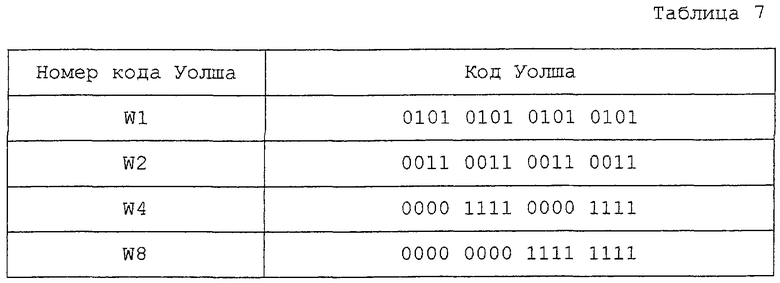

Во-вторых, приводится описание другого случая, когда рассматриваемый кодер функционирует как кодер (24,4). 4-битовый индикатор скорости, состоящий из битов a0, a1, a2 и a3, подается в кодер, а остающиеся биты a4, a5 и a6 информации инициализируются ‘0’. В то же самое время в контроллер 510 подается информация в виде битов, указывающая на то, что в кодер поступил 4-битовый индикатор скорости. Далее контроллер 510 выдает в генератор 500 кодов Уолша сигнал управления, предписывающий ему сформировать коды Уолша длиной 16. После приема сигнала управления генератор 500 кодов Уолша формирует коды W1, W2, W4 и W8 Уолша длиной 16 и выдает сформированные коды W1, W2, W4 и W8 Уолша в соответствующие блоки умножения. Более конкретно, код W1 Уолша выдается в блок 520 умножения, код W2 Уолша выдается в блок 522 умножения, код W4 Уолша выдается в блок 524 умножения, и код W8 Уолша выдается в блок 526 умножения. В Таблице 7 приведены коды Уолша длиной 16, формируемые генератором 500 кодов Уолша.

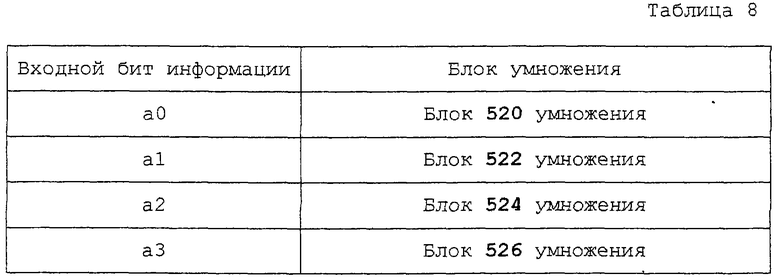

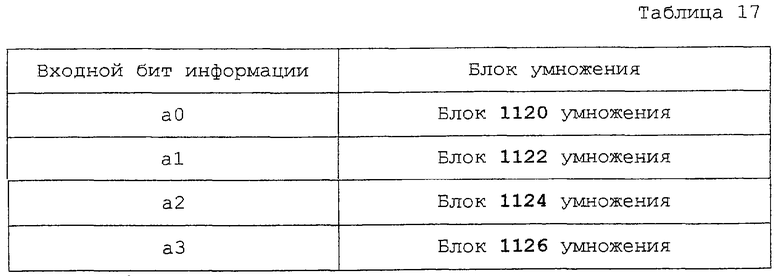

Тем временем 4 входных бита информации, составляющие индикатор скорости, подаются в соответствующие блоки умножения. В Таблице 8 приведены связи между 4 входными битами информации и соответствующими блоками умножения.

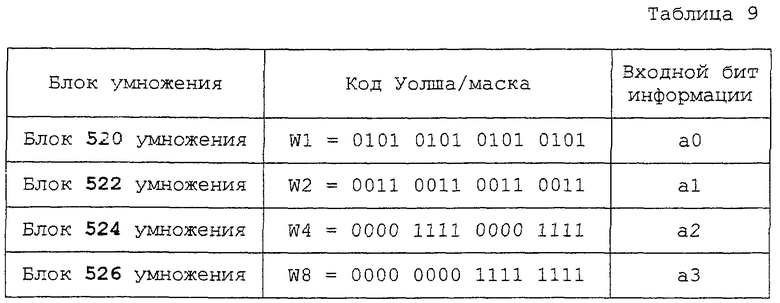

Таким образом, в Таблице 9 приводятся входные биты информации и коды Уолша, подаваемые в соответствующие блоки умножения.

Блоки умножения умножают входные биты информации на коды Уолша, как показано в Таблице 9, и выдают свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Более конкретно, блок 520 умножения умножает входной бит a0 информации на каждый символ кода W1 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 522 умножения умножает входной бит a1 информации на каждый символ кода W2 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 524 умножения умножает входной бит a2 информации на каждый символ кода W4 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”. Блок 526 умножения умножает входной бит a3 информации на каждый символ кода W8 Уолша и выдает свои выходные данные в блок 540 оператора “исключающее ИЛИ”.

В то же время в силу того, что блоки 528, 530 и 532 умножения принимают входные биты a4, a5 и a6, инициализированные ‘0’, выходные данные блоков 528, 530 и 532 умножения не оказывают никакого влияния на выходные данные блока 540 оператора “исключающее ИЛИ”, несмотря на наличие кода W16 Уолша, выдаваемого генератором 500 кодов Уолша, и масок М1 и М2, выдаваемых генератором 505 масок. Более конкретно, блок 528 умножения выдает поток символов, значения всех кодированных символов которого равны ‘0’ независимо от значения кода W16 Уолша, выдаваемого генератором 500 кодов Уолша. Аналогично, блоки 530 и 532 умножения выдают потоки символов, значения всех кодированных символов каждого из которых равны ‘0’ независимо от значений масок М1 и М2, выдаваемых генератором 505 масок. В результате выходные данные блоков 528, 530 и 532 умножения не влияют на выходные данные блока 540 оператора “исключающее ИЛИ”, несмотря на то что они подаются в блок 540 оператора “исключающее ИЛИ”. Инициализация битов a4, a5 и a6 ‘0’ эквивалентна операции переключения, предназначенной для обрезания выходных данных блоков 528, 530 и 532 умножения.

Затем блок 540 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к потокам символов длиной 16, выдаваемым блоками умножения 520, 522, 524, 526, 528, 530 и 532, и выдает свои выходные данные в повторитель 550.

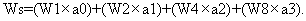

Поток Ws кодированных символов длиной 16, выдаваемый блоком 540 оператора “исключающее ИЛИ”, определяется следующим образом.

Уравнение 6

В этот момент контроллер 510 выдает в повторитель 550 сигнал управления, предназначенный для управления частотой повторения выходных данных блока 540 оператора “исключающее ИЛИ”. В силу того что в кодере (24,4) длина потока символов, выдаваемого блоком 540 оператора “исключающее ИЛИ”, равна 16, частота повторения повторителя 550 должна быть равна ‘1’. Следовательно, контроллер 510 выдает в повторитель 550 сигнал управления, предписывающий ему однократно повторить входной сигнал. В ответ на сигнал управления повторитель однократно повторяет поток символов длиной 16, выдаваемый блоком 540 оператора “исключающее ИЛИ”, и выдает в блок 560 исключения символов поток символов длиной 32.

В этот момент контроллер 510 выдает в блок 560 исключения символов сигнал управления, предписывающий ему исключить символы, находящиеся в позициях исключения для кода (24,4). Далее блок 560 исключения символов принимает считанные из запоминающего устройства 570 8 позиций исключения и исключает кодированные символы, находящиеся в упомянутых позициях исключения, из потока кодированных символов длиной 32, выдаваемого повторителем 550. То есть блок 560 исключения символов исключает 8 символов, находящихся в считанных из запоминающего устройства 570 позициях исключения, из потока кодированных символов длиной 32, выдаваемого повторителем 550. Например, в случае, если считанные из запоминающего устройства 570 позиции исключения - это 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 16-я позиции символов, блок 560 исключения символов исключает 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 16-й кодированные символы из потока кодированных символов длиной 32 и выдает 24 кодированных символа.

Второй вариант осуществления (кодер)

Фиг.9 иллюстрирует другую структуру кодера, функционирующего и как кодер (24,4), и как кодер (24,7) с разными длинами. То есть кодер по Фиг.9 кодирует 4 или 7 входных битов информации с применением различных кодов Уолша или масок, причем длина каждого кода Уолша и каждой маски равна 16 или 32, и выдает поток кодированных символов, состоящий из 24 кодированных символов. В отличие от кодера, соответствующего первому варианту осуществления, кодер, соответствующий второму варианту осуществления, не включает в себя повторитель символов.

Согласно Фиг.9 контроллер 1110 управляет процессом кодирования посредством определения того, является ли число входных битов информации равным 4 или 7. Иными словами, контроллер 1110 выдает в блок 1160 исключения символов сигнал управления, предписывающий ему исключить символы, находящиеся в 8 позициях исключения, соответствующих входным битам информации. Генератор 1100 кодов Уолша формирует коды Уолша длиной 32. Например, после приема входных битов информации генератор 1100 кодов Уолша формирует 5 различных кодов Уолша длиной 32. Генератор 1105 масок формирует маски длиной 32. Например, после приема входных битов информации генератор 1105 масок формирует 2 различные маски длиной 32.

Блоки 1120-1132 умножения умножают 4 или 7 входных битов информации на коды Уолша и маски, выдаваемые генератором 1100 кодов Уолша и генератором 1105 масок, на однозначной основе и выдают потоки кодированных символов, каждый из которых состоит из 32 кодированных символов. Блок 1140 оператора “исключающее ИЛИ” применяет оператор “исключающее ИЛИ” к потокам кодированных символов, выдаваемым блоками 1120-1132 умножения, и выдает один поток кодированных символов, состоящий из 32 кодированных символов. Запоминающее устройство 1170 хранит 8 позиций исключения, соответствующих 4 входным битам информации, или 8 позиций исключения, соответствующих 7 входным битам информации. Хранимые в запоминающем устройстве 1170 8 позиций исключения, соответствующие 4 входным битам информации, - это 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 16-я позиции символов, в то время как хранимые в запоминающем устройстве 1170 8 позиций исключения, соответствующие 7 входным битам информации, - это 0-я, 4-я, 8-я, 12-я, 16-я, 20-я, 24-я и 28-я позиции символов или 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 7-я позиции символов.

Блок 1160 исключения символов принимает от блока 1140 “исключающее ИЛИ” поток кодированных символов, состоящий из 32 кодированных символов, под управлением контроллера 1110 исключает кодированные символы, находящиеся в 8 считанных из запоминающего устройства 1170 позициях исключения, из этих 32 кодированных символов и выдает поток кодированных символов, состоящий из 24 кодированных символов. То есть, если число входных битов информации равно 4, то блок 1160 исключения символов под управлением контроллера 1110 исключает 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 16-й символы из 32 кодированных символов, выдаваемых блоком 1140 оператора “исключающее ИЛИ”, и выдает поток кодированных символов, состоящий из 24 кодированных символов. Если же число входных битов информации равно 7, то блок 1160 исключения символов под управлением контроллера 1110 исключает 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й символы или 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й символы из 32 кодированных символов, выдаваемых блоком 1140 оператора “исключающее ИЛИ”, и выдает поток кодированных символов, состоящий из 24 кодированных символов.

Ниже со ссылкой на Фиг.9 приводится отдельное описание рассматриваемого кодера для случая, когда он функционирует как кодер (24,4), и отдельное описание для другого случая, когда рассматриваемый кодер функционирует как кодер (24,7). Далее по тексту предполагается, что подаваемые на кодер входные биты информации составляют индикатор скорости.

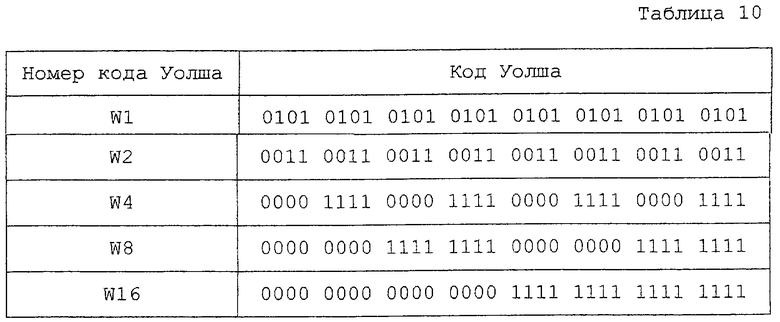

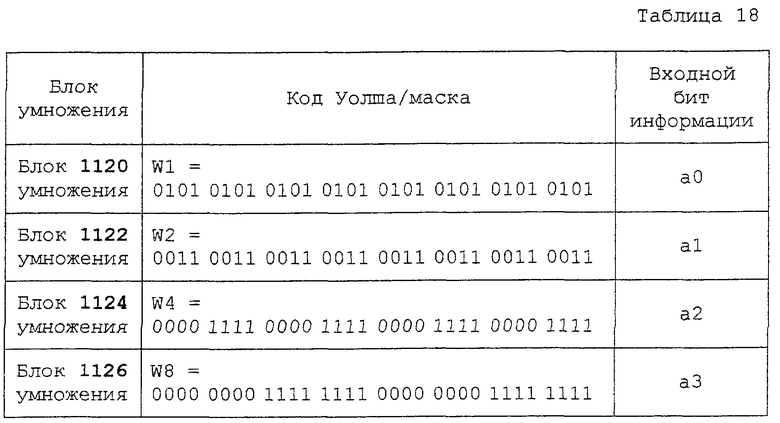

Сначала приводится описание одного из случаев, когда рассматриваемый кодер функционирует как кодер (24,7). Когда на кодер подается 7-битовый индикатор скорости, состоящий из битов a0, a1, a2, a3, a4, a5 и a6, в контроллер 1110 подается информация в виде битов, указывающая на то, что в кодер поступил 7-битовый индикатор скорости. Далее генератор 1100 кодов Уолша формирует коды W1, W2, W4, W8 и W16 Уолша длиной 32. Генератор 1100 кодов Уолша может функционировать либо под управлением контроллера 1110, либо без отдельного управления. Фиг.9 иллюстрирует пример, в котором генератор 1100 кодов Уолша функционирует без отдельного управления. Сформированные генератором 1100 кодов Уолша коды W1, W2, W4, W8 и W16 Уолша подаются в соответствующие блоки умножения. Более конкретно, код W1 Уолша подается в блок 1120 умножения, код W2 Уолша подается в блок 1122 умножения, код W4 Уолша подается в блок 1124 умножения, код W8 Уолша подается в блок 1126 умножения, и код W16 Уолша подается в блок 1128 умножения. В Таблице 10 приведены коды Уолша длиной 32, формируемые генератором 1100 кодов Уолша.

В то же самое время генератор 1105 масок формирует маску М1=0111 0111 0010 0100 0110 0000 0000 0000 и маску М2=0010 0110 0101 0100 0101 0100 0100 0000 и выдает сформированные маски М1 и М2 в блоки 1130 и 1132 умножения соответственно.

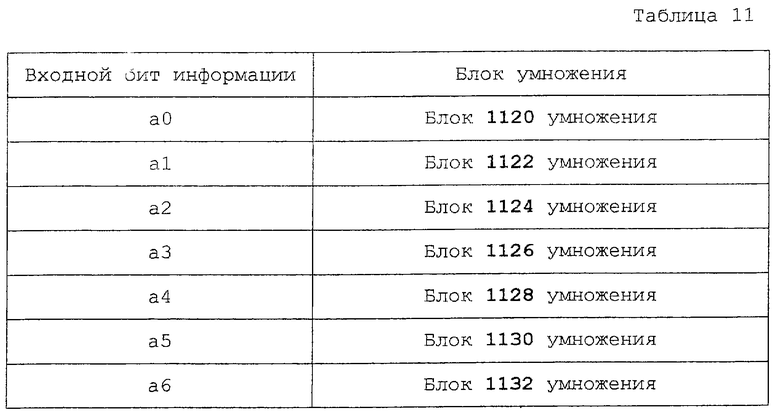

Тем временем 7 входных битов информации, составляющие индикатор скорости, подаются в соответствующие блоки умножения. В Таблице 11 приведены связи между 7 входными битами информации и соответствующими блоками умножения.

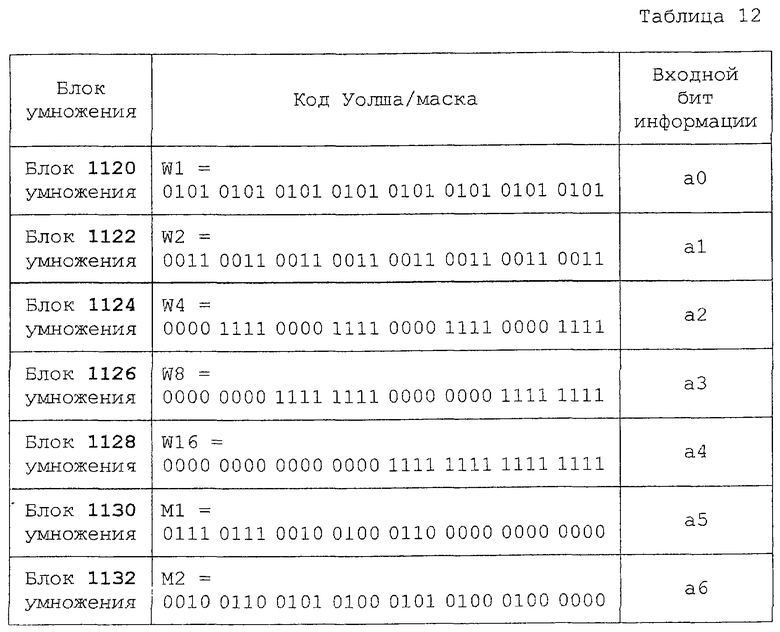

Таким образом, в Таблице 12 приводятся входные биты информации и коды Уолша или маски, подаваемые в соответствующие блоки умножения.

Блоки умножения умножают входные биты информации на коды Уолша или маски, как показано в Таблице 12, и выдают свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Более конкретно, блок 1120 умножения умножает входной бит a0 информации на каждый символ кода W1 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1122 умножения умножает входной бит a1 информации на каждый символ кода W2 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1124 умножения умножает входной бит a2 информации на каждый символ кода W4 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1126 умножения умножает входной бит a3 информации на каждый символ кода W8 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1128 умножения умножает входной бит a4 информации на каждый символ кода W16 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1130 умножения умножает входной бит a5 информации на каждый символ маски М1 и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1132 умножения умножает входной бит a6 информации на каждый символ маски М2 и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”.

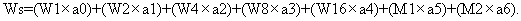

Затем блок 1140 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к потокам символов длиной 32, выдаваемым блоками умножения 1120, 1122, 1124, 1126, 1128, 1130 и 1132, и выдает свои выходные данные в блок 1160 исключения символов.

Поток Ws кодированных символов длиной 32, выдаваемый блоком 1140 оператора “исключающее ИЛИ”, определяется следующим образом.

Уравнение 7

В этот момент контроллер 1110 выдает в блок 1160 исключения символов сигнал управления, предписывающий ему исключить символы, находящиеся в позициях исключения для кода (24,7). Далее блок 1160 исключения символов принимает от запоминающего устройства 1170 8 позиций исключения и исключает кодированные символы, находящиеся в упомянутых позициях исключения, из потока кодированных символов длиной 32, выдаваемого блоком 1140 оператора “исключающее ИЛИ”. То есть блок 1160 исключения символов исключает 8 символов, находящихся в считанных из запоминающего устройства 1170 позициях исключения, из потока кодированных символов длиной 32, выдаваемого блоком 1140 оператора “исключающее ИЛИ”. Например, в случае, если считанные из запоминающего устройства 1170 позиции исключения - это 0-я, 4-я, 8-я, 12-я, 16-я, 20-я, 24-я и 28-я позиции символов, блок 1160 исключения символов исключает 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й кодированные символы из потока кодированных символов длиной 32 и выдает 24 кодированных символа.

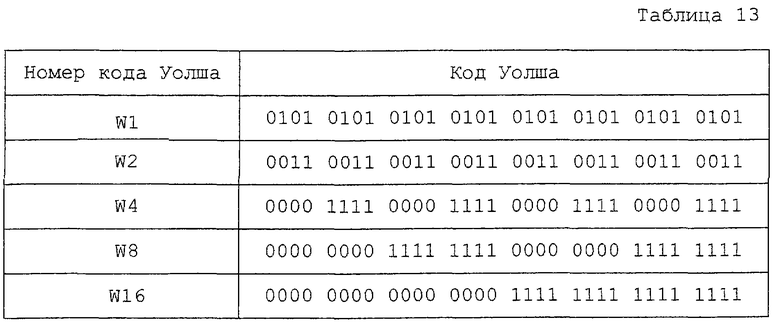

До настоящего момента функционирование кодера (24,7) описывалось со ссылкой на один из случаев, когда шаблоном исключения кодера (24,7) является {0, 4, 8, 12, 16, 20, 24, 28}. Далее описывается функционирование кодера (24,7) со ссылкой на другой случай, когда шаблоном исключения данного кодера является {0, 1, 2, 3, 4, 5, 6, 7}, с целью снижения сложности аппаратных средств, о чем говорилось ранее. В этом случае, когда в кодер подается 7-битовый индикатор скорости, состоящий из битов a0, a1, a2, a3, a4, a5 и a6, в контроллер 1110 подается информация в виде битов, указывающая на то, что в кодер поступил 7-битовый индикатор скорости. Далее генератор 1100 кодов Уолша формирует коды W1, W2, W4, W8 и W16 Уолша длиной 32. Сформированные генератором 1100 кодов Уолша коды W1, W2, W4, W8 и W16 Уолша подаются в соответствующие блоки умножения. Более конкретно, код W1 Уолша подается в блок 1120 умножения, код W2 Уолша подается в блок 1122 умножения, код W4 Уолша подается в блок 1124 умножения, код W8 Уолша подается в блок 1126 умножения и код W16 Уолша подается в блок 1128 умножения. В Таблице 13 приведены коды Уолша длиной 32, формируемые генератором 1100 кодов Уолша.

В то же самое время генератор 1105 масок формирует маску М1=0000 0000 1110 1000 1101 1000 1100 0000 и маску М2=0000 0000 1100 0000 0111 1110 0010 1000 и выдает сформированные маски М1 и М2 в блоки 1130 и 1132 умножения соответственно.

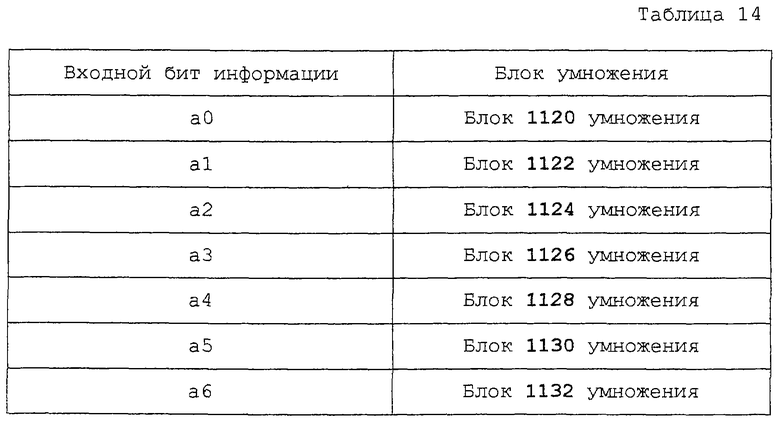

Тем временем 7 входных битов информации, составляющих индикатор скорости, подаются в соответствующие блоки умножения. В Таблице 14 приведены связи между 7 входными битами информации и соответствующими блоками умножения.

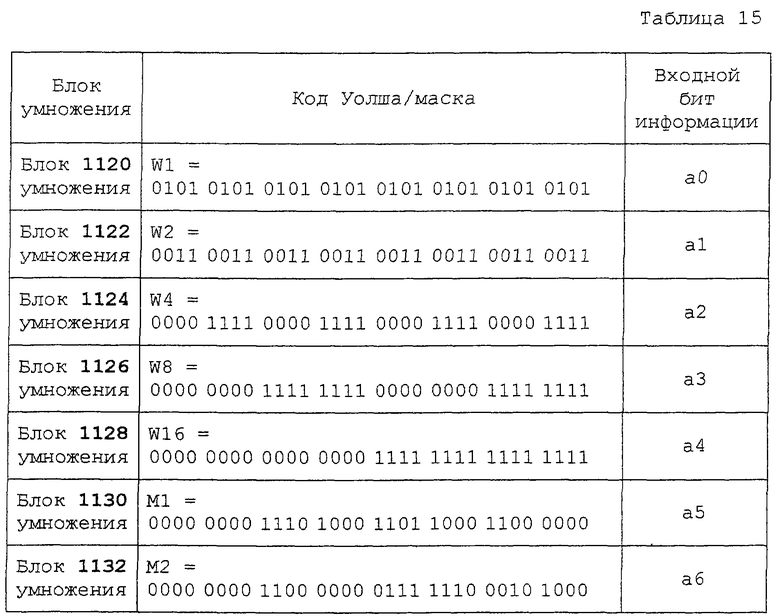

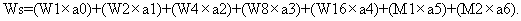

Таким образом, в Таблице 15 приводятся входные биты информации и коды Уолша или маски, подаваемые в соответствующие блоки умножения.

Блоки умножения умножают входные биты информации на коды Уолша или маски, как показано в Таблице 15, и выдают свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Более конкретно, блок 1120 умножения умножает входной бит a0 информации на каждый символ кода W1 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1122 умножения умножает входной бит a1 информации на каждый символ кода W2 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1124 умножения умножает входной бит a2 информации на каждый символ кода W4 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1126 умножения умножает входной бит a3 информации на каждый символ кода W8 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1128 умножения умножает входной бит a4 информации на каждый символ кода W16 Уолша и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1130 умножения умножает входной бит a5 информации на каждый символ маски М1 и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”. Блок 1132 умножения умножает входной бит a6 информации на каждый символ маски М2 и выдает свои выходные данные в блок 1140 оператора “исключающее ИЛИ”.

Затем блок 1140 оператора “исключающее ИЛИ” посимвольно применяет оператор “исключающее ИЛИ” к потокам символов длиной 32, выдаваемым блоками умножения 1120, 1122, 1124, 1126, 1128, 1130 и 1132, и выдает свои выходные данные в блок 1160 исключения символов.

Поток Ws кодированных символов длиной 32, выдаваемый блоком 1140 оператора “исключающее ИЛИ”, определяется следующим образом.

Уравнение 8

В этот момент контроллер 1110 выдает в блок 1160 исключения символов сигнал управления, предписывающий ему исключить символы, находящиеся в позициях исключения для кода (24,7). Далее блок 1160 исключения символов принимает от запоминающего устройства 1170 8 позиций исключения и исключает кодированные символы, находящиеся в упомянутых позициях исключения, из потока кодированных символов длиной 32, выдаваемого блоком 1140 оператора “исключающее ИЛИ”. То есть блок 1160 исключения символов исключает 8 символов, находящихся в считанных из запоминающего устройства 1170 позициях исключения, из потока кодированных символов длиной 32, выдаваемого блоком 1140 оператора “исключающее ИЛИ”. Например, в случае, если считанные из запоминающего устройства 570 позиции исключения - это 0-я, 1-я, 2-я, 3-я, 4-я, 5-я, 6-я и 7-я позиции символов, блок 1160 исключения символов исключает 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й кодированные символы из потока кодированных символов длиной 32 и выдает 24 кодированных символа.