1. Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к устройству и способу декодирования кода коррекции ошибки в системе связи и более конкретно к устройству и способу декодирования блочного кода, имеющего заданные длину информационных битов и длину блока.

2. Уровень техники

Как правило, система связи с множественным доступом с кодовым разделением каналов (МДКР, CDMA) выполняет коррекцию ошибки для исправления ошибок, возникающих из-за шумов в канале передачи. Обычно, передающая сторона передает принимающей стороне кодовое слово, полученное путем кодирования информационных битов с использованием схемы коррекции ошибки (то есть схемы кодирования). Принимающая сторона принимает кодовое слово, переданное передающей стороной, и декодирует полученное кодовое слово с использованием схемы декодирования, которая соответствует схеме кодирования, используемой передающей стороной. В результате кодовое слово восстанавливают до исходных информационных битов.

Способ коррекции ошибки, используемый, например, в системе связи CDMA, включает в себя две схемы: способ с использованием блочного кода и способ с использованием решетчатого кода. В способе коррекции ошибки с использованием блочного кода дополнительные биты (например, r битов) вводят в заданную длину передаваемых информационных битов (например, k битов) для кодирования передаваемых информационных битов в блочный код из n (n=k+r) битов и передают закодированный блочный код. Для передачи информационных битов длиной k битов передающая сторона передает блочный код длиной n битов, то есть (n, k) блочный код. Затем принимающая сторона принимает (n, k) блочный код, переданный передающей стороной, декодирует принятый (n, k) блочный код и выделяет исходные информационные биты длиной k битов. Кроме того, для улучшения возможности коррекции ошибки в способе коррекции ошибки с использованием блочного кода необходимо увеличивать количество дополнительных битов.

При использовании блочного кода структуры блока кодирования и блока декодирования изменяются в соответствии с размером кодового слова. Поэтому, когда в одной системе используют блочные коды, имеющие разную длину, в такой системе должны быть отдельно предусмотрены блоки кодирования и блоки декодирования для блочных кодов, имеющих разную длину.

Кроме того, блочный код включает код БХЧ (BCH, код Боуза-Чоудхури-Хоквенгема), код Рида-Соломона и т.д., и декодирование с жестким решением выполняется для блочного кода с помощью алгоритма Берлекампа-Масси, алгоритма Евклида и т.д.

В способе коррекции ошибки с использованием решетчатого кода для обработки сегментированных блоков не сегментируют передаваемые информационные биты на блоки, но в нем выполняют кодирование передаваемых информационных битов, представленных в решетчатом коде с помощью логической структуры после последовательного ввода в сдвиговый регистр, для передачи закодированных информационных битов.

Отношение количества выходных битов к входным передаваемым информационным битам называют коэффициентом кодирования. Когда коэффициент кодирования равен 1/k, передающая сторона кодирует информационный бит размером один бит в выходные биты количеством k битов, и передает закодированные выходные биты в соответствии с коэффициентом кодирования. Затем принимающая сторона принимает решетчатый код, коэффициент кодирования которого равен 1/k, переданный передающей стороной, декодирует полученный решетчатый код и извлекает исходные информационные биты количеством k битов.

Кроме того, для улучшения способности коррекции ошибки в способе коррекции ошибки с использованием решетчатого кода требуется уменьшать коэффициент кодирования.

Решетчатый код также содержит сверточный код, турбокод и т.д., и для решетчатого кода выполняют декодирование с мягким решением, используя алгоритм Витерби и т.д.

Как описано выше, декодирование с жестким решением выполняют для блочного кода в процессе декодирования. При выполнении декодирования с жестким решением принимаемый сигнал имеет значения 1 или -1, при этом характеристики декодирования при декодировании с жестким решением обычно ниже, чем при декодировании с мягким решением.

Кроме того, как описано выше, декодирование с мягким решением выполняют для решетчатого кода в процессе декодирования. При декодировании с мягким решением значение принимаемого сигнала определяют в соответствии с взвешенным значением и декодирование с мягким решением принимаемого сигнала выполняют так, чтобы характеристики декодирования при декодировании с мягким решением были выше, чем при декодировании с жестким решением. Обычно характеристики декодирования при декодировании с мягким решением лучше приблизительно на 2[дБ] по сравнению с декодированием с жестким решением. Однако, в отличие от декодирования с жестким решением, при использовании мягкого решения невозможно выполнить декодирование путем простого определения значения принятого сигнала, равного 1 или -1, и при выполнении декодирования необходимо рассматривать взвешенное значение. В результате не только значительно увеличивается количество операций, выполняемых в процессе декодирования, но также повышается сложность аппаратных средств. Соответственно, когда длина принимаемого блока велика, то есть, когда количество битов превышает определенное значение, декодирование с мягким решением становится трудно использовать.

Как описано выше, поскольку декодирование с мягким решением имеет лучшие характеристики по сравнению с декодированием с жестким решением, в системе связи CDMA используется блочный код для сигнала управления, имеющего относительно короткую длину блока. Однако для информационного сигнала, имеющего относительно большую длину блока, в системе связи CDMA выполняется декодирование с мягким решением, с использованием решетчатого кода, то есть сверточного кода или турбокода.

На фиг.1 показана блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с использованием обычного коррелятора. Как показано на фиг.1, сигнал r, принимаемый приемной стороной, поступает в коррелятор 100. Здесь предполагается, что передающая сторона передала сигнал, полученный в результате модуляции заданного блочного кода, с использованием способа двоичной фазовой манипуляции (ДФМН, BPSK). Например, предполагается, что передающая сторона передала модулированный сигнал, состоящий из {+1, -1}. Принимаемый сигнал r становится сигналом, в котором шумы и помехи дополнительно присутствуют в модулированном сигнале {+1, -1}, переданном передающей стороной, в силу воздействия на модулированный сигнал условий канала (среда, ситуация и т.д.). В соответствии с этим сигнал r имеет реальную величину вместо величины сигнала {+1,-1}.

На вход коррелятора 100 поступает принятый сигнал r для выполнения корреляции принятого сигнала r по отношению к каждому кодовому слову блочного кода, который может быть передан передающей стороной системы связи. Коррелятор 100 выводит величины корреляции между принятым сигналом r и каждым кодовым словом в компаратор/селектор 110. Компаратор/селектор 110 выполняет сравнение величин корреляции между принятым сигналом r и каждым кодовым словом, выбирает из результата сравнения кодовое слово, имеющее максимальную величину корреляции, и определяет выбранное кодовое слово как кодовое слово, переданное передающей стороной. В результате информационные биты, соответствующие кодовому слову, поступающему с выхода компаратора/селектора 110, восстанавливают в виде исходных информационных битов.

Например, когда передающая сторона передает (n, k) блочный код, принимающая сторона принимает принимаемый сигнал r с реальными компонентами. Принимаемый сигнал r, помимо блочного кода (n, k), содержит шумы и помехи. Сигнал r с реальными компонентами поступает в коррелятор 100. Коррелятор 100 коррелирует сигнал r с каждым кодовым словом (n, k) блочного кода, который может быть передан передающей стороной, и выдает результат корреляции в компаратор/селектор 110.

При учете всех кодовых слов, которые могут быть сгенерированы из (n, k) блочного кода, существует 2k кодовых слова, каждое из которых имеет длину n. Кроме того, поскольку корреляция должна быть выполнена по отношению к каждому из 2k кодовых слов, каждое из которых имеет длину n, необходимо выполнять nx2k процессов умножения и (n-1)x2k процессов суммирования. Например, когда предполагается, что (n, k) блочный код представляет собой (10, 3) блочный код, общее количество кодовых слов, которые могут быть сгенерированы из (10, 3) блочного кода, равно восьми, при этом каждое из кодовых слов имеет длину 10. Кроме того, поскольку корреляция должна быть выполнена по отношению к каждому из восьми кодовых слов (10, 3) блочного кода, необходимо выполнить 80 (10x8) процессов умножения и 72 (9x8) процессов суммирования.

Когда величины k и n увеличиваются, в частности, при увеличении величины k, количество выполняемых процессов умножения и процессов суммирования для выполнения корреляции увеличивается в геометрической прогрессии. В результате ухудшаются рабочие характеристики всей системы из-за нагрузки в процессе выполнения операции.

В обычном блочном коде, когда к блочному коду применяют декодирование с мягким решением, k информационных битов имеют ограниченную длину (например, меньше 14 битов). Поэтому декодирование с мягким решением нельзя будет применить к блочному коду, даже если рабочие характеристики при декодировании с мягким решением позволят получить более высокий эффект, чем декодирование с жестким решением.

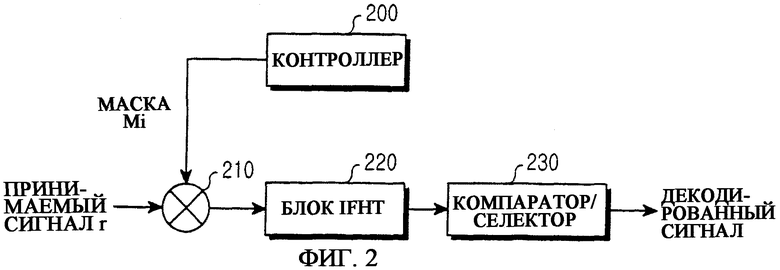

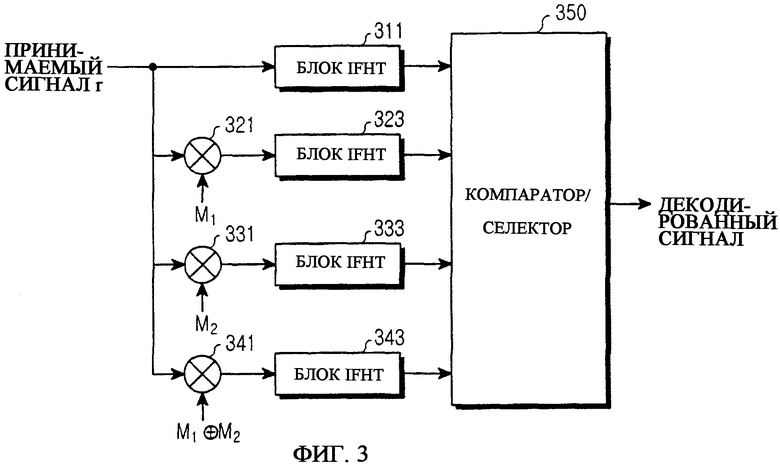

На фиг.2 показана блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с последовательной структурой, построенной с использованием обычного блока обратного быстрого преобразования Адамара (ОБПА, IFHT). Однако перед описанием устройства со ссылкой на фиг.2 вначале будет описана последовательная структура, которая представляет собой структуру, содержащую маску Мi, которая будет описана ниже. На фиг.3 показано устройство декодирования с мягким решением, с параллельной структурой, построенной с использованием блока IFHT. В этом случае параллельная структура представляет собой структуру, в которой маска Мi обрабатывается одновременно.

Как показано на фиг.2, принимаемый сигнал r, принятый принимающей стороной, вводят в умножитель 210 маски. Здесь передающая сторона, соответствующая принимающей стороне, передает блочный код, матрица генерирования которого включает в себя основания кода Уолша. Умножитель 210 маски умножает сигнал r на маску Мi, поступающую с выхода контроллера 200, и выводит сигнал, получаемый в результате умножения, в блок 220 IFHT. На вход блока 220 IFHT поступает сигнал с выхода умножителя 210 маски, в этом блоке выполняют IFHT для сигнала r, и результат поступает в компаратор/селектор 230. Здесь, поскольку устройство декодирования с мягким решением по фиг.2 имеет последовательную структуру и предполагается, что маска первоначально не применяется, контроллер 200 не выводит маскуМi.

Контроллер 200 последовательно выводит соответствующую маску Мi в умножитель 210 маски. Например, когда существуют две маски М1 иМ2, контроллер 200 первоначально не использует маску Мi. Затем контроллер 200 последовательно выводит маску М1 и маскуM2, а также результат логической операции "исключающее ИЛИ" между маской М1 и маскойM2, то есть М1 ⊕M2 в умножитель 210 маски.

Блок 220 IFHT последовательно выполняет преобразование IFHT для всех сигналов, поступающих с выхода умножителя 210 маски, то есть сигнала, к которому не применена маска (то есть сигнала r), сигнала, полученного в результате умножения сигнала r на маскуМ1, сигнала, полученного в результате умножения сигнала r на маску М2, а также сигнала, полученного путем умножения сигнала r на результат выполнения логической операции "исключающее ИЛИ" (М1 ⊕ M2) маскиM1 и маскиM2. Затем с выхода блока 220 IFHT результаты поступают в компаратор/селектор 230. Компаратор/селектор 230 выполняет сравнение величин всех результатов, поступающих с выхода блока 220 IFHT, друг с другом, выбирает кодовое слово, имеющее максимальную величину корреляции, и определяет выбранное кодовое слово, как кодовое слово, переданное передающей стороной. В результате информационные биты, соответствующие кодовому слову, поступающему с выхода компаратора/селектора 230, восстанавливают до исходных информационных битов. Работа контроллера 200 и умножителя 210 маски будет более подробно описана ниже.

Код (N, k) Рида-Мюллера, например код (8, 3) Рида-Мюллера, показан ниже в табл. 1.

Как показано в табл. 1, количество кодовых слов кода (8, 3) Рида-Мюллера, которые могут быть сгенерированы, равно 23 или 8, когда вводят 3 информационных бита. Когда информационные биты представлены как 000, генерируется кодовое слово '00000000', когда информационные биты представлены как 001, генерируется кодовое слово '01010101', когда информационные биты представлены как 010, генерируется кодовое слово '00110011', когда информационные биты представлены как 011, генерируется кодовое слово '01100110', когда информационные биты представлены как 100, генерируется кодовое слово '00001111', когда информационные биты представлены как 101, генерируется кодовое слово '01011010', когда информационные биты представлены как 110, генерируется кодовое слово '00111100', и когда информационные биты представлены как 111, генерируется кодовое слово '01101001'.

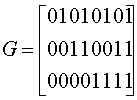

Матрица генерирования кода (8, 3) Рида-Мюллера, показанного в табл. 1, представлена Уравнением 1, приведенным ниже.

Уравнение 1

В уравнении 1 G представляет собой матрицу генерирования. Поскольку количество строк равно количеству k входных информационных битов и количество столбцов равно количеству n выходных битов, код Рида-Мюллера, сгенерированный в соответствии с матрицей генерирования, представляет собой код (8, 3) Рида-Мюллера. Кроме того, поскольку каждая строка матрицы генерирования представляет собой основу, в матрице генерирования существуют три основы.

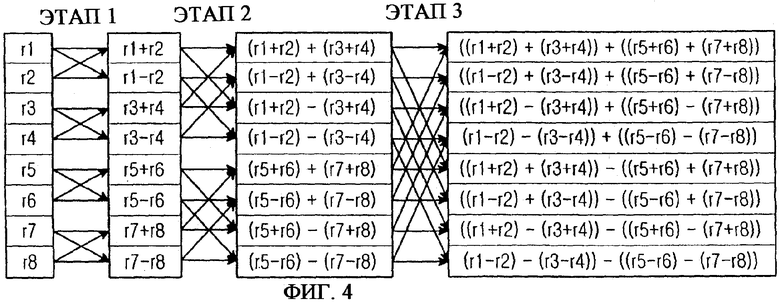

Как указано выше, для кода (8, 3) Рида-Мюллера существует восемь кодовых слов, каждое из которых имеет длину 8. Кроме того, в отношении каждого из восьми кодовых слов должно быть выполнено IFHT. Ниже, со ссылкой на фиг.4, будет описан процесс, с помощью которого выполняют преобразование IFHT для кода (8, 3) Рида-Мюллера.

На фиг.4 показана схема, иллюстрирующая процесс, с помощью которого выполняют обычное IFHT. Как показано на фиг.4, поскольку принимаемый сигнал r представляет собой сигнал, получаемый из кодового слова кода (8, 3) Рида-Мюллера, к которому добавлены шумы и помехи, принимаемый сигнал r может быть выражен как r=r1r2r3r4r5r6r7r8, где каждый из r1-r8 ниже называется "принятым символом".

Кроме того, для обеспечения 100%-ных рабочих характеристик декодирования с мягким решением, аналогично коррелятору 100, описанному со ссылкой на фиг.1, блок 220 IFHT должен учитывать корреляцию между каждым из кодовых слов, которые могут быть сгенерированы из кода (8, 3) Рида-Мюллера и принимаемым сигналом r. При обеспечении 100%-ных рабочих характеристик декодирование с мягким решением означает выполнение корреляции для каждого из кодовых слов, которые могут быть переданы передающей стороной, по отношению к принимаемому сигналу r.

Кроме того, код (8, 3) Рида-Мюллера, показанный в табл. 1, выражен цифровыми данными. Однако, поскольку цифровые данные были модулированы с использованием заданного способа, например способа BPSK, во время передачи они были переведены в состоянии, когда цифровые данные 0 соответствуют +1, и цифровые данные 1 соответствуют -1. В соответствии с этим, когда код (8, 3) Рида-Мюллера, показанный в табл. 1, соответствует компонентам, модулированным с помощью способа BPSK, получают табл. 2.

При 100% декодировании с мягким решением должна быть выполнена корреляция для каждого кодового слова, модулированного способом BPSK, как показано в табл. 2, при приеме сигнала r (то есть r1r2r3r4r5r6r7r8). Когда выполняют IFHT, становится возможным выполнить корреляцию для каждого из кодовых слов, модулированных способом BPSK, по отношению к принимаемому сигналу r, поскольку IFHT выполняется с использованием структуры логики по схеме типа "бабочка", как показано на фиг.4.

Более конкретно, если эти этапы выполняют k раз (количество входных информационных битов), то есть три раза, в отношении принимаемого сигнала r1r2r3r4r5r6r7r8, при возведении 2 в степень, становится возможным выполнить корреляцию для каждого из кодовых слов, модулированных способом BPSK. Здесь на каждом этапе выполняется операция суммирования и операция вычитания по отношению к каждому компоненту принимаемого сигнала r путем возведения 2 в степень. На первом этапе выполняется операция суммирования (или сложения) и операция вычитания (или отнимания), в отношении к каждому компоненту принимаемого сигнала r, на 2° (1). То есть, r1 и r2 подвергают операции суммирования и операции вычитания. r3 и r4 подвергают операции суммирования и операции вычитания, r5 и r6 подвергают операции суммирования и операции вычитания, и r7 и r8 подвергают операции суммирования и операции вычитания.

На втором этапе выполняют операцию суммирования и операцию вычитания по отношению к каждому компоненту результатов, полученных на первом этапе, то есть r1+r2, r1-r2, r3+r4, r3-r4, r5+r6, r5-r6 и r7+r8, r7-r8, на 21 (2). Более конкретно, r1+r2 и r3+r4 подвергают операции суммирования и операции вычитания, r1-r2 и r3-r4 подвергают операции суммирования и операции вычитания, r5+r6 и r7+r8 подвергают операции суммирования и операции вычитания, и r5-r6 и r7-r8 подвергают операции суммирования и операции вычитания.

На третьем этапе выполняют операцию суммирования и операцию вычитания по отношению к каждому компоненту результатов второго этапа, то есть (r1+r2+r3+r4), (r1-r2)+(r3-r4), (r1+r2)-(r3+r4), (r1-r2)-(r3-r4), (r5+r6)+(r7+r8), (r5-r6)+(r7-r8), (r5+r6)-(r7+r8), (r5-r6)-(r7-r8), на 22 (4). Более конкретно, (r1+r2)+(r3+r4) и (r5+r6)+(r7+r8) подвергают операции суммирования и операции вычитания, (r1-r2)+(r3-r4) и (r5-r6)+(r7-r8) подвергают операции суммирования и операции вычитания, (r1+r2)-(r3+r4) и (r5+r6)-(r7+r8) подвергают операции суммирования и операции вычитания и (r1-r2)-(r3-r4), и (r5-r6)-(r7-r8) подвергают операции суммирования и операции вычитания.

Таким образом, в соответствии с результатом, полученным на этапах 1-3, можно видеть, что для каждого кодового слова, модулированного с помощью способа BPSK, как описано в табл. 2, была выполнена корреляция по отношению к принимаемому сигналу r1r2r3r4r5r6r7r8. То есть, результат корреляции для первого кодового слова (то есть ++++++++), модулированного с помощью способа BPSK, представленного в табл. 2, в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1+r2)+(r3+r4j}+{(r5+r6)+(r7+r8)}, результат корреляции для второго кодового слова (то есть +-+-+-+-) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1-r2)+(r3-r4)}+{(r5-r6)+(r7-r8)}, результат корреляции для третьего кодового слова (то есть ++--++--) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1+r2)-(r3+r4)}+{(r5+r6)-(r7+r8)}, результат корреляции для четвертого кодового слова (то есть +--++--+) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1-r2)-(r3-r4)}+{(r5-r6)-(r7-r8)}, результат корреляции для пятого кодового слова (то есть ++++----) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1+r2)+(r3+r4)}-{(r5+r6)+(r7+r8)}, результат корреляции для шестого кодового слова (то есть +-+--+-+) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1-r2)+(r3-r4)}-{(r5-r6)+(r7-r8)}, результат корреляции для седьмого кодового слова (то есть ++----++) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1+r2)-(r3+r4)}-{(r5+r6)-(r7+r8)}, и результат корреляции для восьмого кодового слова (то есть +--+-++-) в отношении принимаемого сигнала r1r2r3r4r5r6r7r8 представляет собой {(r1-r2)-(r3-r4)}-{(r5-r6)-(r7-r8)}. В результате была на 100% выполнена корреляция для кодовых слов кода (8, 3) Рида-Мюллера, модулированного способом BPSK, представленного в табл. 2, в отношении принимаемого сигнала r1r2r3r4r5r6r7r8.

Когда учитывают количество выполняемых операций при воплощении IFHT для кода (8, 3) Рида-Мюллера, требуется выполнять всего 24 (1og28) (операций суммирования, операций вычитания) процессов, то есть для трех (log28) этапов требуются восемь процессов суммирования на первом этапе, восемь процессов суммирования на втором этапе и восемь процессов суммирования на третьем этапе. Тем временем, с учетом количества выполняемых операций при получении корреляции кода (8, 3) Рида-Мюллера с помощью коррелятора, необходимо использовать 64 (8x23) процессов умножения и 56 {(8-1)x23} процессов суммирования.

Наконец, при учете всех кодовых слов для (n, k) блочного кода существуют 2k кодовых слов, каждое из которых имеет длину n. Кроме того, поскольку корреляция должна быть выполнена в отношении каждого из 2k кодовых слов, каждое из которых имеет длину n, при выполнении корреляции с использованием коррелятора необходимо выполнить nx2k процессов умножения и (n-1)x2k процессов суммирования. Однако, когда выполняют IFHT в отношении всех кодовых слов для блочного кода (n, k), требуется выполнятьnlog2n процессов суммирования. В результате, когда выполняют декодирование с мягким решением с использованием IFHT в отношении всех блочных кодов, можно обеспечить 100%-ное декодирование с мягким решением, с учетом корреляции. Кроме того, минимизируется количество выполняемых операций, и обеспечиваются максимальные рабочие характеристики декодирования с мягким решением.

Применение маски к коду Рида-Мюллера означает, что основание, которое будет использоваться как маска, добавляют к основанию матрицы генерирования. То есть, как описано выше, матрица генерирования то же количество оснований, что и количество входных информационных битов. Здесь же, когда применяют маску, матрица генерирования не только имеет то же количество оснований, что и количество входных битов, но также имеет основание, которое должно быть использовано как маска.

Например, когда маску, состоящую из одних единиц, применяют к коду (8, 3) Рида-Мюллера, как показано в табл. 1, матрица генерирования соответствует Уравнению 2, приведенному ниже.

Уравнение 2

В уравнении 2 G представляет собой матрицу генерирования, а четвертая строка матрицы генерирования в Уравнении 2, состоящая из одних единиц, представляет собой основание маски кода (8, 3) Рида-Мюллера.

Когда принимаемый сигнал r принимают в первый раз, контроллер 200 управляет маской Мi так, что она не выводится при допущении, что маска не была применена. То есть, контроллер 200 управляет блоком 220 IFHT для выполнения IFHT в отношении принятого сигнала r. Здесь, как описано выше, контроллер 200 первоначально не учитывает маску, а затем снова может учитывать маску Мi. Кроме того, когда маску не применяют, контроллер 200 может выводить маску Мi, все элементы которой заполнены единицами в умножитель 210 маски при допущении, что была применена маска, состоящая из всех единиц.

Даже когда маску, все элементы которой заполнены единицами, умножают на принятый сигнал, не происходит какое-либо изменение. Соответственно, устройство работает так же, как в случае, когда маску не прикладывают.

Как описано выше, используют маску, в которой все элементы заполнены единицами, так, что структура аппаратных средств, сформированная для случая, когда маску в действительности применяют, остается идентичной структуре аппаратных средств, когда маску не применяют. Однако, поскольку маску в действительности применили к принимаемому сигналу r, контроллер 200 передает маску Мi, которая соответствует основанию маски, в умножитель 210 маски. Здесь, поскольку основание маски матрицы генерирования представлено одними единицами, все элементы маски Mi состоят из единиц.

Умножитель 210 маски умножает принимаемый сигнал r на маску Mi для вывода результата умножения в блок 220 IFHT. Поскольку устройство декодирования с мягким решением, представленное на фиг.2, имеет последовательную структуру, рассматривают случай, когда вектор Мi маски учитывают, и случай, когда вектор Мi маски не учитывают.

На фиг.3 представлена блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с параллельной структурой, в котором используется обычный блок IFHT. Как показано на фиг.3, сигнал r, принимаемый принимающей стороной, вводят в блок 311 IFHT и в множество умножителей 321, 331 и 341 маски. Кроме того, количество умножителей маски, предусмотренных на принимающей стороне, определяют в соответствии с количеством оснований, применяемых в качестве маски на передающей стороне. На фиг.3 предполагается, что количество оснований, применяемых в качестве маски, равно двум. В соответствии с этим на принимающей стороне используют умножитель 321 маски, умножитель 331 маски и умножитель 341 маски. Умножитель 321 маски умножает принимаемый сигнал r на первую маску M1, соответствующую первому основанию m1 маски, умножитель 331 маски умножает принимаемый сигнал r на вторую маску M2, соответствующую второму основанию маскиm2, и умножитель 341 маски умножает принимаемый сигнал r на маску, соответствующую результату применения логической операции "исключающее ИЛИ" к первому основанию m1 маски и второму основанию m2 (ниже обозначается как:'М1 ⊕ М2').

В блок 311 IFHT поступает принимаемый сигнал r, в блоке выполняется IFHT в отношении сигнала r, и на его выход поступает результат выполнения, который передают в компаратор/селектор 350. Умножитель 321 маски умножает принятый сигнал r на первую маску М1 для вывода результата выполнения в блок 323 IFHT. Умножитель 331 маски умножает принятый сигнал r на вторую маскуM2 для вывода результата выполнения в блок 333 IFHT. Умножитель 341 маски умножает принятый сигнал r на маску (М1 ⊕ М2) для вывода результата выполнения в блок 343 IFHT. В каждый из блоков 323, 333 и 343 IFHT поступают входные сигналы с выхода умножителей 321, 331 и 341 маски, в этих блоках выполняют IFHT для сигналов, и результаты с выхода каждого из этих блоков поступают в компаратор/селектор 350. Компаратор/селектор 350 сравнивает результаты, поступающие с выхода от каждого из блоков 323, 333 и 343 IFHT, и выбирает кодовое слово, имеющее максимальное значение корреляции, для определения выбранного кодового слова в качестве кодового слова, переданного передающей стороной. В результате информационные биты, соответствующие кодовому слову, поступающему с выхода компаратора/селектора 330, восстанавливают как исходные информационные биты.

Как описано выше, когда учитывают все кодовые слова для (n, k) блочного кода, существуют 2k кодовых слова, каждое из которых имеет длину n. Кроме того, поскольку должна быть выполнена корреляция в отношении каждого из 2k кодовых слов, каждое из которых имеет длину n, при выполнении корреляции в корреляторе требуется выполнять 2k процессов умножения и (n-1)Ч2k процессов сложения. Однако, когда IFHT выполняют в отношении всех кодовых слов для (n, k) блочного кода с помощью блока IFHT, необходимо выполнить только nlog2n процессов суммирования, и при этом обеспечивается минимальное количество операций. В результате получают максимальные рабочие характеристики декодирования с мягким решением. Однако устройство декодирования с мягким решением, в котором используют коррелятор, описанное со ссылкой на фиг.1, может выполнять декодирование с мягким решением для заданных блочных кодов, но устройство декодирования с мягким решением, с использованием блока IFHT, описанное со ссылкой на фиг.2, может выполнять декодирование с мягким решением только для блочных кодов матрицы генерирования, которая содержит основание кода Уолша. То есть, устройство декодирования с мягким решением, с использованием блока IFHT, может выполнять декодирование с мягким решением, с минимальным количеством операций, но блочные коды, используемые в качестве объекта декодирования мягкого решения, должны содержать основание кода Уолша.

Раскрытие изобретения

В соответствии с этим настоящее изобретение было разработано для решения вышеуказанных недостатков известного уровня техники, и первой целью настоящего изобретения является обеспечение устройства и способа, предназначенных для декодирования кода коррекции ошибок в системе связи.

Вторая цель настоящего изобретения состоит в создании устройства и способа, предназначенных для декодирования кода коррекции ошибки в системе связи, в которых используется минимальное количество операций.

Третьей целью настоящего изобретения является разработка устройства и способа, предназначенных для выполнения декодирования с мягким решением, которые выполняют минимальное количество операций для блочных кодов, имеющих заданную длину информационных битов и длину блока.

Четвертая цель настоящего изобретения состоит в создании устройства и способа, предназначенных для выполнения в системе связи декодирования с мягким решением, для заданных блочных кодов, с использованием блока IFHT.

Для выполнения вышеуказанных и других целей, в соответствии с одним аспектом настоящего изобретения, предложено устройство, предназначенное для декодирования n принятых символов с использованием информации матрицы генерирования блочного кода, имеющей k строк и n столбцов, содержащее: контроллер для определения информации положения символа, для перемещения каждого принятого символа, с использованием информации матрицы генерирования блочного кода и информации размера IFHT, для выполнения IFHT принятых символов; блок размещения символа, предназначенный для перемещения каждого принятого символа на вход блока IFHT, в соответствии с информацией о положении символа, определенной контроллером; блок IFHT для ввода символов, перемещенных блоком размещения символа, для выполнения IFHT для символов; и компаратор/селектор, предназначенный для вывода, в качестве сигнала декодирования, кодового слова блочного кода, которое имеет максимальное значение корреляции среди значений, полученных посредством выполнения IFHT.

В соответствии с другим аспектом настоящего изобретения предложено устройство для декодирования блочного кода, включающего в себя n принятых символов, с использованием информации матрицы генерирования блочного кода, имеющей k строк и n столбцов, содержащее: контроллер для определения информации размера IFHT для выполнения IFHT принятых символов и информации положения символа для перемещения каждого принятого символа, с использованием информации матрицы генерирования блочного кода; блок размещения символа для перемещения каждого принятого символа на вход блока IFHT, в соответствии с информацией о положении символа, определенной контроллером; блок IFHT для ввода символов, перемещенных блоком размещения символа, для выполнения IFHT для символов; и компаратор/селектор для вывода, в качестве сигнала декодирования, кодового слова блочного кода, которое имеет максимальное значение корреляции среди значений, полученных посредством выполнения IFHT.

В соответствии с дополнительным аспектом настоящего изобретения предложено устройство для декодирования n принятых символов с использованием матрицы генерирования блочного кода, имеющей k строк и n столбцов, содержащее: контроллер, предназначенный для ввода n принятых символов и расчета положения символов для n столбцов в матрице генерирования блочного кода; и блок размещения символа, включающий в себя сумматоры, предназначенные для накопления и перемещения n принятых символов в рассчитанные положения символа.

В соответствии с еще одним аспектом настоящего изобретения предложен способ декодирования n принятых символов с использованием информации матрицы генерирования блочного кода, имеющей k строк и n столбцов, содержащий следующие этапы: a) определение информации положения символа для перемещения каждого принятого символа с использованием информации матрицы генерирования блочного кода и информации размера IFHT для выполнения IFHT для принятых символов; b) перемещение каждого принятого символа на вход блока IFHT, в соответствии с определенной информацией положения символа; ввод перемещенных символов для выполнения IFHT символов; и c) вывод, в качестве сигнала декодирования, кодового слова блочного кода, которое имеет максимальное значение корреляции среди значений, полученных в результате выполнения IFHT.

В соответствии с другим аспектом настоящего изобретения предложен способ декодирования n принятых символов с использованием информации матрицы генерирования блочного кода, имеющей k строк и n столбцов, содержащий следующие этапы: a) определение информации размера IFHT для выполнения IFHT принятых символов и информации положения символа для перемещения каждого принятого символа с использованием информации матрицы генерирования блочного кода; b) перемещение каждого принятого символа в качестве входа блока IFHT, в соответствии с определенной информацией положения символа; c) ввод перемещенных символов для выполнения IFHT для символов; и d) вывод, в качестве сигнала декодирования, кодового слова блочного кода, которое имеет максимальное значение корреляции среди значений, полученных в результате выполнения IFHT, в качестве декодированного сигнала.

В соответствии с другим аспектом настоящего изобретения предложен способ декодирования n принятых символов с использованием информации матрицы генерирования блочного кода, имеющей k строк и n столбцов, содержащий следующие этапы: расчет положений символов для n столбцов в матрице генерирования блочного кода; и накопление и перемещение n принятых символов в рассчитанные положения символов.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Указанные выше и другие цели, свойства и преимущества настоящего изобретения очевидны из следующего подробного описания, приводимого совместно с прилагаемыми чертежами, на которых:

фиг.1 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с использованием обычного коррелятора;

фиг.2 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с последовательной структурой, с использованием обычного IFHT;

фиг.3 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с параллельной структурой, с использованием обычного блока IFHT;

фиг.4 - схема процесса, посредством которого выполняют обычное IFHT;

фиг.5 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, которое декодирует обычный проколотый код Рида-Мюллера, с использованием блока IFHT;

фиг.6 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, которое декодирует обычный повторяющийся код Рида-Мюллера с использованием блока IFHT;

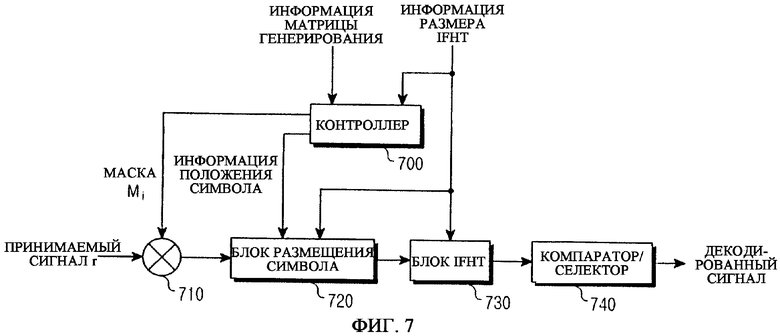

фиг.7 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с использованием блока IFHT, в соответствии с первым вариантом осуществления настоящего изобретения;

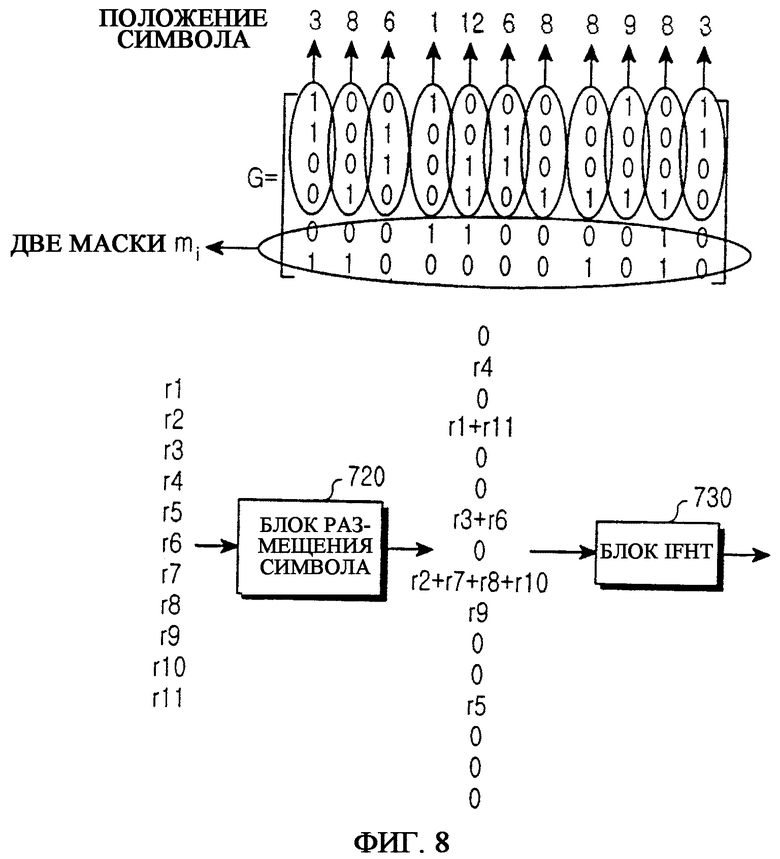

фиг.8 - схема, иллюстрирующая процесс принятия решения в отношении информации положения символа, выполняемый контроллером 700, и процесс перемещения символа, выполняемый блоком 720 размещения символа, которые представлены на фиг.7;

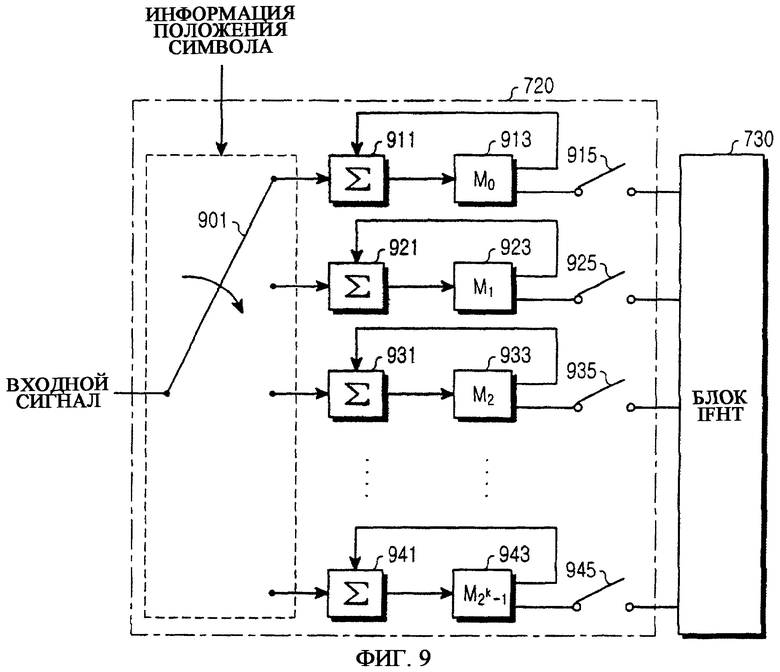

фиг.9 - внутренняя структура блока 720 размещения символа, представленного на фиг.7;

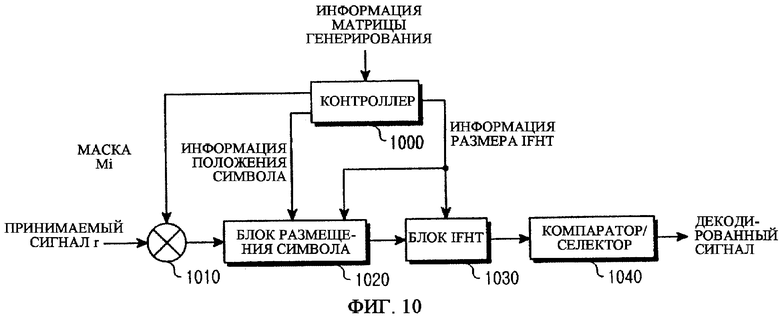

фиг.10 - блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, с использованием блока IFHT, в соответствии со вторым вариантом осуществления настоящего изобретения;

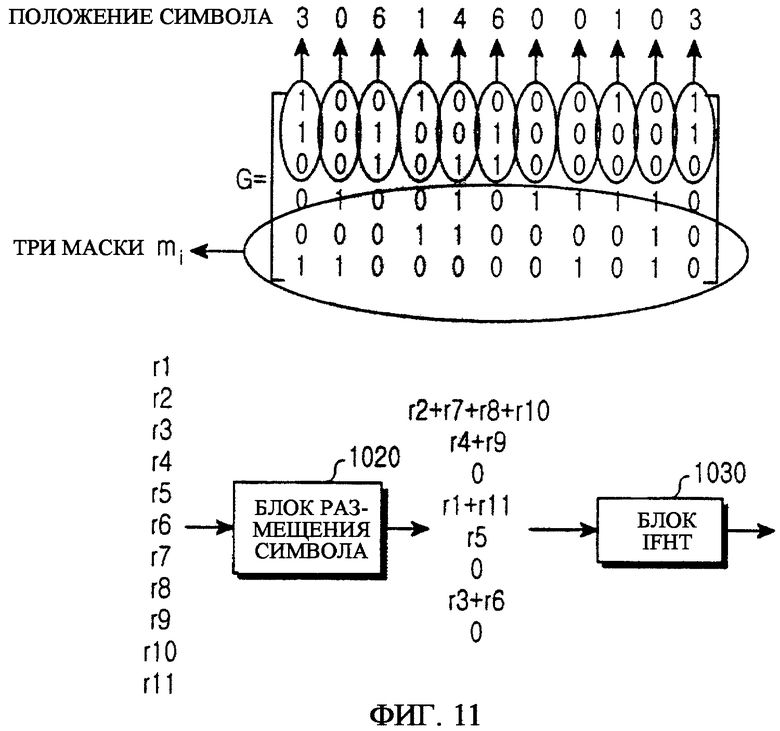

фиг.11 - схема, иллюстрирующая процесс принятия решения в отношении информации положения символа с помощью контроллера 1000, и процесс перемещения символа с помощью блока 1020 размещения символа, представленных на фиг.10.

Осуществление изобретения

Ниже подробно описаны предпочтительные варианты осуществления настоящего изобретения со ссылкой на прилагаемые чертежи. В следующем описании настоящего изобретения подробное описание известных функций и использованных здесь конфигураций исключено, когда оно может привести к затруднению понимания объекта настоящего изобретения.

Как описано выше, декодирование с мягким решением с использованием блока обратного быстрого преобразования Адамара (блок IFHT) имеет такие же рабочие характеристики при использовании мягкого решения, что и при декодировании с мягким решением с использованием коррелятора. Однако декодирование с мягким решением с использованием блока IFHT предполагает меньшее количество выполняемых операций (требует выполнения меньшего количества операций на практике), чем в соответствии с вариантом осуществления с использованием корреляции с помощью коррелятора, в результате чего сводится к минимуму нагрузка на операционный процесс. Однако, поскольку декодирование с мягким решением с использованием блока IFHT применимо только для блочных кодов, у которых матрица генерирования содержит основание кода Уолша, декодирование с мягким решением с использованием блока IFHT часто нельзя использовать, даже, если оно имеет значительно лучшие рабочие характеристики, чем при декодировании с мягким решением с использованием коррелятора.

В соответствии с этим в настоящем изобретении предложена схема обеспечения максимальных рабочих характеристик при декодировании, путем выполнения декодирования с мягким решением с использованием блока IFHT, даже для блочных кодов, матрица генерирования которых не содержит основание кода Уолша.

Перед описанием характеристик IFHT, как описано в известном уровне техники, вновь будет описан блочный код, содержащий основание кода Уолша, то есть код Рида-Мюллера. Код (n, k) Рида-Мюллера, например код (8, 3) Рида-Мюллера, идентичен коду, представленному в табл. 1, описанной при изложении известного уровня техники. Здесь k представляет длину входных информационных битов, и n (2k) представляет длину выходного блока. То есть, как показано в табл. 1, количество кодовых слов кода (8, 3) Рида-Мюллера, которые могут быть сгенерированы, когда на вход подают информационные биты длиной по 3 бита, составляет 23 (то есть восемь). Когда информационные биты представляют собой 000, генерируется кодовое слово '00000000', когда информационные биты представляют собой 001, генерируется кодовое слово '01010101', когда информационные биты представляют собой 010, генерируется кодовое слово '00110011', когда информационные биты представляют собой 011, генерируется кодовое слово '01100110', когда информационные биты представляют собой 100, генерируется кодовое слово '00001111', когда информационные биты представляют собой 101, генерируется кодовое слово '01011010', когда информационные биты представляют собой 110, генерируется кодовое слово '00111100', и когда информационные биты представляют собой 111, генерируется кодовое слово '01101001'. Когда каждое кодовое слово кода (8, 3) Рида-Мюллера модулируют на практике с помощью некоторого способа, например способа BPSK, цифровые данные 0 и 1 соответствуют +1 и -1, соответственно, при реальной передаче.

Когда все кодовые слова, которые могут быть сгенерированы из кода (8, 3) Рида-Мюллера, модулируют с помощью способа BPSK, кодовое слово '00000000' модулируется в виде ++++++++, кодовое слово '01010101' модулируется в виде +-+-+-+-, кодовое слово '00110011' модулируется в виде ++--++--, кодовое слово '01100110' модулируется в виде +--++--+, кодовое слово '00001111' модулируется в виде ++++----, кодовое слово '01011010' модулируется в виде +-+--+-+, кодовое слово '00111100' модулируется в виде ++----++, и кодовое слово '01101001' модулируется в виде +--+-++-. Кроме того, для случая, когда каждое кодовое слово, которое может быть сгенерировано из кода (8, 3) Рида-Мюллера, модулируют с помощью способа BPSK, компоненты модуляции показаны ниже в табл. 3.

В табл. 3 первый ряд соответствует компоненту модуляции BPSK кодового слова '00000000', второй ряд соответствует компоненту модуляции BPSK кодового слова "01010101", третий ряд соответствует компоненту модуляции BPSK кодового слова '00110011', четвертый ряд соответствует компоненту модуляции BPSK кодового слова '01100110', пятый ряд соответствует компоненту модуляции BPSK кодового слова '00001111', шестой ряд соответствует компоненту модуляции BPSK кодового слова '01011010', седьмой ряд соответствует компоненту модуляции BPSK кодового слова '00111100', и восьмой ряд соответствует компоненту модуляции BPSK кодового слова '01101001'.

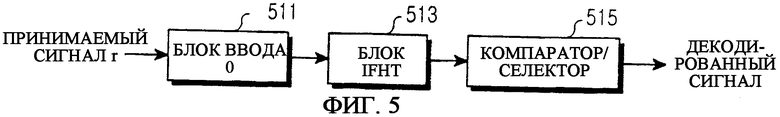

Ниже со ссылкой на фиг.5 будет описан процесс, с помощью которого выполняют IFHT для проколотого кода Рида-Мюллера, то есть кода (n-t, k) Рида-Мюллера, например кода (6, 3) Рида-Мюллера, получаемого в результате прокалывания заданных 2 битов кода (8, 3) Рида-Мюллера. Здесь t представляет количество проколотых битов.

На фиг.5 показана блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, предназначенным для декодирования обычного проколотого кода Рида-Мюллера, с использованием блока IFHT.

Перед описанием фиг.5 будет описан код (6, 3) Рида-Мюллера, который получают путем прокалывания предыдущих двух битов в каждом кодовом слове кода (8, 3) Рида-Мюллера, описанного со ссылкой на табл. 1. Код (6, 3) Рида-Мюллера показан в приведенной ниже табл. 4.

Кроме того, когда каждое кодовое слово, которое может быть сгенерировано из кода (6, 3) Рида-Мюллера с помощью способа BPSK, компоненты модуляции представлены в табл. 5.

Как показано на фиг.5, принимаемый сигнал r получают из кода (6, 3) Рида-Мюллера, в который введены шумы и помехи, и принимаемый сигнал r выражен как r=r1r2r3r4r5r6. Принимаемый сигнал r передают в блок 511 ввода 0. В блок 511 ввода 0 поступает входной сигнал r, в этом блоке в заданные положения вводят 0, и затем результат с его выхода поступает в блок 513 IFHT. Здесь блок 511 ввода 0 вводит 0 в положение, в котором бит проколот в коде (8, 3) Рида-Мюллера на передающей стороне и информация, относящаяся к положению прокола, известна передающей стороне и принимающей стороне.

Сигнал с выхода блока 511 ввода 0 поступает на вход блока 513 IFHT, где выполняется IFHT сигнала, и результат с выхода этого блока поступает в компаратор/селектор 515. Компаратор/селектор 515 производит сравнение всех получаемых в результате IFHT значений, поступающих с выхода блока 513 IFHT, и выбирает кодовое слово, имеющее максимальное значение корреляции, для определения выбранного кодового слова как кодового слова, переданного передающей стороной. В результате информационные биты, соответствующие кодовому слову, поступающему с выхода компаратора/селектора 515, восстанавливают в исходные информационные биты. Поскольку процесс выполнения IFHT был описан в известном уровне техники со ссылкой на фиг.4, более подробное его описание не приводится.

В соответствии с этим при выполнении декодирования с мягким решением для проколотого кода (n-t, k) Рида-Мюллера с использованием IFHT, получают тот же результат, что и при вводе "0" в биты, расположенные в проколотых положениях в коде (n, k) Рида-Мюллера, и выполнении декодирования с мягким решением для кода (n, k) Рида-Мюллера с использованием IFHT. Кроме того, для декодирования с мягким решением кода (n-t, k) Рида-Мюллера требуется выполнять то же количество операций, что и для кода (n, k) Рида-Мюллера.

Как описано выше, вариант выполнения IFHT для проколотого кода Рида-Мюллера, то есть для кода (n-t, k) Рида-Мюллера, был описан со ссылкой на фиг.5. Ниже, со ссылкой на фиг.6, будет описан процесс, с помощью которого выполняется IFHT для повторяющегося кода Рида-Мюллера, то есть кода (n+t, k) Рида-Мюллера, например кода (10, 3) Рида-Мюллера, получаемого путем повторения заданных 2 битов кода (8, 3) Рида-Мюллера. Здесь t представляет собой количество повторяющихся битов.

На фиг.6 показана блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением для декодирования обычного повторяющегося кода Рида-Мюллера с использованием блока IFHT.

Однако перед описанием фиг.6 код (10, 3) Рида-Мюллера будет получен путем повторения предыдущих двух битов в каждом кодовом слове кода (8, 3) Рида-Мюллера, показанном в табл. 1. Код (10, 3) Рида-Мюллера представлен ниже в табл. 6.

Кроме того, когда каждое кодовое слово, которое может быть сгенерировано из кода (10, 3) Рида-Мюллера, модулируют с помощью способа BPSK, получают компоненты модуляции, представленные в табл. 7.

На фиг.6 показан принимаемый сигнал r как сигнал, получаемый из кода (10, 3) Рида-Мюллера, в который введены шумы и помехи. Принимаемый сигнал r выражен как r=r1r2r3r4r5r6r7r8r9r10. Принимаемый сигнал r передают в накопитель 611. Накопитель 611 выполняет накопление 2 битов из младших значащих битов (МЗБ, LSB) переданного принимаемого сигнала r и 2 битов из старших значащих битов (СЗБ, MSB) переданного принятого сигнала r и подает на выход результат накопления, поступающий в блок 613 IFHT. Здесь накопитель 611 выполняет накопление битов в повторяющихся позициях в коде (8, 3) Рида-Мюллера на передающей стороне, и информация, относящаяся к позициям повторения, известна на передающей стороне и на принимающей стороне приема.

На вход блока 613 IFHT поступает сигнал с выхода накопителя 611, этот блок выполняет IFHT для сигнала, и с его выхода результаты поступают в компаратор/селектор 615. Компаратор/селектор 615 выполняет сравнение всех полученных значений, поступающих с выхода блока 613 IFHT, и выбирает кодовое слово, имеющее максимальное значение корреляции, для определения выбранного кодового слова в качестве кодового слова, переданного передающей стороной. В результате информационные биты, соответствующие кодовому слову, поступающему с выхода компаратора/селектора 615, восстанавливают как исходные информационные биты. Поскольку процесс выполнения IFHT был описан в известном уровне техники со ссылкой на фиг.4, более подробное его описание не приводится.

В соответствии с этим, путем выполнения декодирования с мягким решением для повторяющегося кода (n+t, k) Рида-Мюллера,с использованием IFHT, получают тот же результат, что и путем накопления битов в повторяющихся позициях в коде (n, k) Рида-Мюллера, с выполнением декодирования с мягким решением для кода (n, k) Рида-Мюллера с использованием IFHT. Кроме того, для декодирования с мягким решением кода (n+t, k) Рида-Мюллера требуется использовать то же количество операций, что и для кода (n, k) Рида-Мюллера.

Как описано выше, когда код Рида-Мюллера представляет собой код Рида-Мюллера проколотого типа, в позицию прокола вводят 0 и выполняют IFHT. Кроме того, когда код Рида-Мюллера представляет собой код Рида-Мюллера повторяющегося типа, повторяющиеся биты накапливают и выполняют IFHT. Таким образом, можно проводить декодирование с мягким решением.

В вышеприведенном описании используется пример, в котором маску не применяют к коду Рида-Мюллера. Однако, когда к коду Рида-Мюллера применяют маску, выполняют ту же операцию, что и в случае применения IFHT, с учетом использования маски, в соответствии с известным уровнем техники.

Настоящее изобретение обеспечивает способ выполнения декодирования с мягким решением блочных кодов, имеющих заданное количество информационных битов и заданное количество битов блока, с использованием характеристики IFHT, как описано выше, и при условии, что заданные биты кода Рида-Мюллера являются проколотыми, повторяются или закрыты маской.

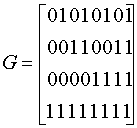

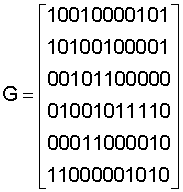

На фиг.7 показана блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением с использованием блока IFHT, в соответствии с первым вариантом осуществления настоящего изобретения. Как показано на фиг.7, устройство декодирования с мягким решением, в соответствии с первым вариантом осуществления настоящего изобретения, включает в себя контроллер 700, умножитель 710 маски, блок 720 размещения символа, блок 730 IFHT и компаратор/селектор 740. Кроме того, предполагается, что матрица генерирования, которую применяют для переданного или принятого блочного кода в первом варианте осуществления настоящего изобретения и втором варианте осуществления настоящего изобретения, который будет описан ниже, является идентичной матрице, используемой в Уравнении 3.

Уравнение 3

Матрица генерирования представляет собой матрицу 6х11, и, когда применяют матрицу генерирования в соответствии с Уравнением 3, осуществляется генерирование (11, 6) блочного кода. Кроме того, предполагается, что четыре основания высоких порядков, с первой по четвертую строки, используют в качестве входных данных IFHT из шести оснований матрицы G генерирования, а два других основания низких порядков, кроме четырех оснований высоких порядком, то есть основания пятой и шестой строк, используют как основания маски. В соответствии с этим, поскольку только четыре основания используют в качестве входных данных IFHT, размер входных данных IFHT для корреляции (11, 6) блочного кода равен 16 (24). В первом варианте осуществления настоящего изобретения как на передающей стороне, так и на принимающей стороне распознают информацию размера IFHT и информацию генераторной матрицы друг друга.

Кроме того, как описано выше, (11, 6) блочный код, переданный передающей стороной, принимают принимающей стороной в форме принятого сигнала r, содержащего шумы и помехи. Принятый сигнал r выражен как r=r1r2r3r4r5r6r7r8r9r10r11, где r1-r11 обозначают принятые символы.

Принятый сигнал r передают в умножитель 710 маски. Умножитель 710 маски умножает принятый сигнал r на маску Мi, поступающую с выхода контроллера 700, и с выхода умножителя результат умножения поступает в блок 720 размещения символа. Контроллер 700 принимает информацию размера IFHT и информацию матрицы генерирования из главного контроллера (не показан) на принимающей стороне и генерирует маску Mi и информацию положения символов, с использованием принятой информации матрицы генерирования, и информации размера IFHT. С выхода контроллера 700 сгенерированная маска Мi и информация положения символа поступает в умножитель 710 маски, а также в блок 720 размещения символа соответственно. Здесь, поскольку предполагается, что два основания низких порядков матрицы генерирования используют как основания маски, контроллер 700 определяет пятый ряд и шестой ряд матрицы генерирования как основания m1 иm2 маски соответственно. В соответствии с этим основания маски, используемые в качестве маски, представляют собой основание m1,основаниеm2 и "исключающее ИЛИ" основания m1 иоснования m2 (далее обозначаемое m1 ⊕ m2).

Кроме того, поскольку устройство декодирования с мягким решением, в соответствии с первым вариантом осуществления настоящего изобретения, имеет последовательную структуру, маску, состоящую из одних единиц, дополнительно применяют для постоянного учета работы аппаратных средств в случае, когда маску в действительности не применяют, и учета работы аппаратных средств, когда маску требуется применять. То есть, с выхода контроллера 700 поступает маска, содержащая одни единицы, в умножитель 710 маски, в результате чего в настоящем изобретении обеспечивается возможность использования структуры, которая в действительности не учитывает маску, даже при использовании той же структуры аппаратных средств, в которой используется маска. Основание маски m1, основание маскиm2 и основание, представляющее "исключающее ИЛИ" (m⊕ m2), соответственно модулируют с использованием способа PBSK для использования в качестве масок.

Как описано в известном уровне техники, поскольку цифровые данные модулируют с помощью способа PBSK, цифровые данные 0 соответствуют +1 и цифровые данные 1 соответствуют -1. Кроме того, как описано в известном уровне техники, когда маска не используется, на выход контроллера 700 не поступает маска, содержащая все единицы, и операция, выполняемая умножителем 710 маски, может быть пропущена.

Как известно из уровня техники, устройство декодирования с мягким решением с использованием IFHT может иметь последовательную структуру или параллельную структуру. При последовательной структуре выполняется последовательная обработка маски Мi. Однако в параллельной структуре выполняется одновременная обработка маски Мi.

В настоящем изобретении для удобства изложения раскрыто только устройство декодирования с мягким решением, имеющее последовательную структуру, но настоящее изобретение можно использовать и для устройства декодирования с мягким решением, имеющего параллельную структуру.

В блок 720 размещения символа поступают сигналы с выхода умножителя 710 маски (то есть принимаемый сигнал r), этот блок изменяет положение символов, составляющих принимаемый сигнал r, в соответствии с информацией положения символа, поступающей с контроллера 700, и с его выхода принимаемый сигнал r поступает в блок 730 IFHT. Более подробное описание процесса принятия решения в отношении информации положения символа, выполняемого контроллером 700, и процесса перемещения символа, выполняемого блоком 720 размещения символа, приведено ниже.

Главный контроллер передает информацию размера IFHT в контроллер 700, а также в блок 730 IFHT. Блок 730 IFHT формирует входные данные для IFHT и при этом IFHT имеет соответствующий этап, который соответствует информации размера IFHT, переданной из главного контроллера. Кроме того, блок 730 IFHT выполняет IFHT для сигнала, поступающего с выхода блока 720 размещения символа, для передачи результата выполнения в компаратор/селектор 740. Компаратор/селектор 740 выполняет сравнение всех полученных в результате значений, поступающих с выхода блока 730 IFHT, друг с другом, выбирает кодовое слово, имеющее максимальное значение корреляции, и определяет выбранное кодовое слово как кодовое слово, переданное передающей стороной. В результате информационные биты, соответствующие кодовому слову, поступающему с выхода компаратора/селектора 740, восстанавливают как исходные информационные биты.

На фиг.8 схематично представлен процесс принятия решения в отношении информации положения символа, выполняемый контроллером 700, и процесс перемещения символа, выполняемый блоком 720 размещения символа. Как показано на фиг.8, поскольку предполагается, что четыре основания высоких порядков с первой по четвертую строк матрицы генерирования, в соответствии с Уравнением 3, используют в качестве входных данных IFHT, требуется шестнадцать (24) наборов входных данных блока 730 IFHT. Здесь количество наборов входных данных блока 730 IFHT составляет шестнадцать, от 0 до 15. Ниже, для удобства, входные данные, соответствующие 0, называются 0-м входом, и входные данные, соответствующие 15, называются 15-м входом. Фактически, 0-й вход представляет собой первые входные данные блока 730 IFHT, и 15-й вход представляет собой шестнадцатые входные данные блока 730 IFHT.

Ниже описан процесс, посредством которого контроллер 700 определяет информацию положения каждого символа (то есть r1, r2, r3, r4, r5, r6, r6, r7, r8, r9, r10, r11), составляющего принимаемый сигнал r, для учета принимаемого сигнала r (то есть r1r2r3r4r5r6r7r8r9r10r11), в качестве входного сигнала блока 730 IFHT.

Контроллер 700 определяет положение символа, в соответствии с которым каждый символ принимаемого сигнала r соответствует входу блока 730 IFHT в обычной последовательности (то есть последовательно от r1 до r11). Контроллер 700 выбирает только четыре бита высоких порядков из первого столбца матрицы генерирования, генерируют двоичную последовательность 0011, в которой элемент первого ряда используется как LSB и элемент четвертого ряда используется как MSB, и преобразует двоичную последовательность 0011 в десятичное число. Когда двоичная последовательность 0011 преобразована в десятичное число, получают 3. В соответствии с этим контроллер 700 определяет положение символа таким образом, что первый символ r1 принимаемого сигнала r может поступать на третий вход блока 730 IFHT, который имеет входной размер 16 (24) (то есть от 0 до 15).

Затем контроллер 700 выбирает только четыре бита высоких порядков из второго столбца матрицы генерирования, генерирует двоичную последовательность 1000, в которой элемент первой строки использован как LSB, а элемент четвертой строки использован как MSB, и преобразует двоичную последовательность 1000 в десятичное число. Когда двоичная последовательность 1000 преобразована в десятичное число, получают 8. В соответствии с этим контроллер 700 определяет положение символа таким образом, что второй символ r2 принимаемого сигнала r может поступать на восьмой вход блока 730 IFHT.

Затем контроллер 700 выбирает только четыре бита высоких порядков в третьем столбце матрицы генерирования, генерирует двоичную последовательность 0110, в которой элемент первой строки использован как LSB, а элемент четвертой строки использован как MSB, и преобразует двоичную последовательность 0110 в десятичное число. Когда двоичная последовательность 0110 преобразована в десятичное число, получают 6. В соответствии с этим контроллер 700 определяет положение символа таким образом, что второй символ r3 принимаемого сигнала r может поступать на шестой вход блока 730 IFHT. Таким же образом контроллер 700 определяет положения символа так, что символы с четвертого символа r4 по одиннадцатый символ r11 принимаемого сигнала r поступают на соответствующие входы блока 730 IFHT.

Более конкретно, как показано на фиг.8, контроллер 700 определяет положения символов от первого символа r1 по одиннадцатый символ r11 принимаемого сигнала r таким образом, что первый символ r1 принимаемого сигнала r поступает на третий вход блока 730 IFHT, второй символ r2 принимаемого сигнала r поступает на восьмой вход блока 730 IFHT, третий символ r3 принимаемого сигнала r поступает на шестой вход блока 730 IFHT, четвертый символ r4 принимаемого сигнала r поступает на первый вход блока 730 IFHT, пятый символ r5 принимаемого сигнала r поступает на двенадцатый вход блока 730 IFHT, шестой символ r6 принимаемого сигнала r поступает на шестой вход блока 730 IFHT, седьмой символ r7 принимаемого сигнала r поступает на восьмой вход блока 730 IFHT, восьмой символ r8 принимаемого сигнала r поступает на восьмой вход блока 730 IFHT, девятый символ r9 принимаемого сигнала r поступает на девятый вход блока 730 IFHT, десятый символ r10 принимаемого сигнала r поступает на восьмой вход блока 730 IFHT и одиннадцатый символ r11 принимаемого сигнала r поступает на третий вход блока 730 IFHT.

Поскольку первый символ r1 и одиннадцатый символ r11 принимаемого сигнала r имеют одинаковое десятичное число (то есть 3), контроллер 700 определяет положение символа таким образом, что первый символ r1 добавляется к одиннадцатому символу r11, и их сумма r1+r11 поступает на третий вход блока 730 IFHT. Кроме того, поскольку третий символ r3 и шестой символ r6 принимаемого сигнала r имеют одинаковое десятичное число (то есть 6), контроллер 700 определяет положение символов таким образом, что третий символ r3 добавляют к шестому символу r6, и сумма r3+r6 поступает на шестой вход блока 730 IFHT. Аналогично, поскольку второй символ r2, седьмой символ r7, восьмой символ r8 и десятый символ r10 принимаемого сигнала r имеют одинаковое десятичное число (то есть 8), контроллер 700 определяет положение символа таким образом, что второй символ r2, седьмой символ r7, восьмой символ r8 и десятый символ r10 добавляют друг к другу, и сумма r2+r7+r8+r10 поступает на восьмой вход блока 730 IFHT.

Контроллер 700 генерирует информацию положения символа в соответствии с определенными положениями символа для вывода сгенерированной информации положения символа в блок 720 размещения символа. Блок 720 размещения символа перемещает каждый символ принимаемого сигнала r на входы блока 730 IFHT в соответствии с информацией положения символов, поступающей с выхода контроллера 700.

Далее описан процесс, с помощью которого контроллер 700 генерирует информацию положения символов. Матрица генерирования представляет собой матрицу k x n.

Кроме того, предполагается, что (k-m) оснований высоких порядков из k оснований матрицы генерирования используют в качестве входных данных IFHT для выполнения IFHT, а другие m оснований низкого порядка, помимо (k-m) оснований высоких порядков, используют как основания маски.

(N, k) блочный код, сгенерированный в соответствии с матрицей генерирования, принимают на принимающей стороне в форме принятого сигнала r, который содержит шумы и помехи канала, и принятый сигнал r может быть выражен в виде выражения r=r1,r2 •• r(n-1),rn. Контроллер 700 выбирает только (k-m) битов из (k-m) строк высоких порядков от первой строки до (k-m)-й строки в каждом из всех n столбцов последовательно, от первого столбца до n-го столбца, генерирует двоичные последовательности, в которых элемент в первой строке используют как LSB, а элемент в (k-m)-й строке используют как MSB, и преобразует каждую из сгенерированных двоичных последовательностей в десятичные числа. Контроллер 700 затем определяет позиции символов таким способом, что с первого r1 символа по n-й символ rn принимаемого сигнала r последовательно размещают на входах, которые соответствуют преобразованным десятичным числам, блока 730 IFHT, который имеет 2(k-m) входов. Здесь количество входов блока 730 IFHT составляет 2(k-m) от 0 до (2k-m-1), при этом вход, соответствующий 0, называют 0-м входом, и вход, соответствующий (2k-m-1), называют (2k-m-1)-м входом. Однако, в действительности, 0-й вход представляет собой первый вход блока 730 IFHT, и (2k-m-1)-й вход представляет собой 2k-m-й вход блока 730 IFHT. Кроме того, когда i-й столбец и j-й столбец имеют одинаковое значение десятичного числа "а", контроллер 700 определяет положение символа таким образом, что суммарный символ ri+rj, который получают путем сложения i-го символа r1 принимаемого сигнала r с j-м символом rj принимаемого сигнала r, располагается на a-м входе блока 730 IFHT.

На фиг.9 показана внутренняя структура блока 720 размещения символа, представленного на фиг.7. Блок 720 размещения символа перемещает каждый символ сигнала, поступающего с выхода умножителя 710 маски, в соответствии с информацией положения символа, поступающей с выхода контроллера 700, и формирует сигналы на входах блока 730 IFHT. Блок 720 размещения символа включает в себя переключатель 901, 2k-m сумматоров 911, 921, 931, •••, 941, 2k-m запоминающих устройств 913, 923, 933, •••, 943 и 2k-m переключателей 915, 925, 935, •••, 945. Здесь каждое из 2k-m запоминающих устройств 913, 923, 933, •••, 943 первоначально установлено на 0. Входной сигнал, который представляет собой выходной сигнал умножителя 710 маски, и информацию положения символа подают на вход блока 720 размещения символа. Ниже, для удобства описания, будет изложен, в качестве примера, случай, в котором умножитель 710 маски использует маску, состоящую из одних единиц. Однако, когда используют информацию, состоящую из одних единиц, получают тот же результат, что и когда в действительности не используют маску, содержащую одни единицы. Когда используют маску Мi, в умножителе 710 маски умножают на принятый сигнал r только величину маски. В соответствии с этим выполняется тот же процесс перемещения символа, что и в случае, когда маску Мi не используют.

Поскольку предполагается, что к принимаемому сигналу r была применена маска, содержащая одни единицы, сигнал, поступающий с выхода умножителя 710 маски, идентичен принимаемому сигналу r. Как описано выше, принимаемый сигнал r представляет собой r1r2r3r4r5r6r7r8r9r10r11. Когда принимаемый сигнал r поступает на вход блока 720 размещения символа, переключатель 901 подключает каждый принятый символ принимаемого сигнала r к соответствующему сумматору, в соответствии с информацией положения символа, передаваемой из контроллера 700. Например, как показано на фиг.8, поскольку информация положения символа для принятого символа r4 представлена десятичным числом 1, переключатель 901 подключает r4 к сумматору 921, который расположен перед запоминающим устройством М1 923. Соответственно, переключатель 901 подключает каждый принятый символ к каждому сумматору, расположенному перед соответствующим запоминающим устройством. Каждый из 2k-m сумматоров 911, 921, 931, •••, 941 суммирует сигнал, подключаемый переключателем 901, с сигналом, поступающим по цепи обратной связи, от каждого из 2k-m запоминающих устройств 913, 923, 933, •••, 943 и подает с выхода суммированный сигнал в каждое из 2k-m запоминающих устройств 913, 923, 933, •••, 943. Здесь, всякий раз, когда на вход подается сигнал, каждое из 2k-m запоминающих устройств 913, 923, 933, •••, 943 суммирует сигнал, который поступает на вход через петлю (контур) обратной связи, с существующим записанным сигналом и сохраняет обновленный сигнал. В соответствии с этим, когда переключатель 901 не соединен с каждым из 2k-m сумматоров 911, 921, 931, •••, 941, расположенных перед каждым из 2k-m запоминающих устройств 913, 923, 933, •••, 943, поскольку вновь вводимый сигнал отсутствует, каждое из 2k-m запоминающих устройств 913, 923, 933, •••, 943 поддерживает существующий записанный сигнал без изменений.

Затем, когда перемещение символа для каждого принятого символа принимаемого сигнала r будет завершено, блок 720 размещения символа управляет переключением каждого из 2k-m переключателей 915, 925, 935, •••, 945 так, что сигналы, которые были записаны в запоминающем устройствеМ0 913 - запоминающем устройствеM2 k -1 943, последовательно поступают на входы блока 730 IFHT. То есть, переключатель 915, подключенный к запоминающему устройству М0 913, вначале подключают к первому блоку 730 IFHT. Таким образом, переключатель 945, подключенный к запоминающему устройству M2 k -1 943, становится подключенным к блоку 730 IFHT. Затем блок 730 IFHT последовательно вводит сигналы, сохраненные в запоминающем устройствеМ0 913, в запоминающее устройство M2 k -1 943 для выполнения IFHT для входных сигналов.

На фиг.9 показана структура, в которой каждое из 2k-m запоминающих устройств 913, 923, 933, •••,943, подключено к каждому из 2k-m переключателей 915, 925, 935, •••,945. Однако, вместо 2k-m переключателей 915, 925, 935, •••, 945, можно использовать преобразователь параллельного кода в последовательный код. Преобразователь параллельного кода в последовательный код выполняет преобразование в последовательный код 2k-m параллельных входных кодов 2k-m запоминающих устройств 913, 923, 933, •••, 943, при этом выходной сигнал запоминающего устройстваМ0 913 будет расположен самым первым, и с его выхода преобразованные сигналы поступают в блок 730 IFHT.

Кроме того, блок 730 IFHT имеет максимум 2k-m входов и выполняет операции h этапов, для h (hk), c использованием 2h входов. Здесь количество входов блока 730 IFHT может быть заранее установлено или может быть адаптивно изменено, в соответствии с обстоятельствами. Блок 730 IFHT учитывает количество операций для определения количества входов. То есть, как описано выше, в блоке 730 IFHT требуется выполнять 2hlog22h процессов суммирования в ходе декодирования (n, k) блочного кода. С учетом этого, поскольку блок 730 IFHT выполняет минимальное количество операций, когда количество входов минимально, блок 730 IFHT определяет с изменением количество входов, имеющих минимальное количество операций. Ниже описан процесс, с помощью которого блок 730 IFHT определяет количество входов.

Когда определяют количество 2h входов блока 730 IFHT, количество функций маски, используемых в устройстве декодирования, равно 2k-h. В соответствии с этим определяют общее количество операций устройства декодирования. Здесь количество операций устройства декодирования рассчитывают в отношении всех "h" (0, h, k). Определяют величину "h", которая имеет минимальное количество операций среди всех "h", при этом количество входов блока 730 IFHT определяют как 2h. Если рассматривать общее количество операций устройства декодирования в соответствии с величиной "h", то часть операций, с помощью которых выполняют умножение функции маски, и часть операций, с помощью которых выполняют IFHT, занимают большую часть всего количества операций устройства декодирования. Здесь, при учете количества операций, требуемых для умножения одного входного сигнала, имеющего длину n битов, и одной маски требуется выполнение n операций умножения и (n-1) операций сложения. В соответствии с предположением 2k-h маски используют в соответствии со значением "h". Когда 2k-h масок умножают на входной сигнал, общее количество операций составляет 2k-hЧn процессов умножения и 2k-hЧ(n-1) процессов суммирования. Кроме того, поскольку количество операций в одном блоке IFHT требует выполнения 2hlog22h(h•2h) операций сложения и операцию IFHT во всем устройстве декодирования выполняют столько раз, сколько имеется масок, количество операций при выполнении операций IFHT во всем устройстве декодирования составляет h•2k(h•2hЧ2k-h). В соответствии с этим общее количество операций устройства декодирования, в соответствии с переменной величиной "h", составляет 2k-hЧn процессов умножения и (n-1)•2k-h+h•2k процессов суммирования.

Если предположить, что процесс умножения имеет ту же сложность операций, что и процесс суммирования, общее количество операций составит (2n-1)-2k-h+h•2k{n•2k-h+(n-1)•2k-h+h•2k}. В соответствии с этим при определении количества входов блока IFHT в устройстве декодирования блок 730 IFHT вычисляет все значения количества операций в соответствии со всеми возможными значениями "h" (0, h, k), выбирает "h", имеющее наименьшее количество операций, и определяет количество (то есть размер) входов IFHT.

В первом варианте осуществления настоящего изобретения декодирование с мягким решением было описано для случая, когда основной контроллер формирует информацию размера IFHT и информацию матрицы генерирования. Ниже декодирование с мягким решением будет описано для случая, когда основной контроллер формирует только информацию матрицы генерирования.

На фиг.10 показана блок-схема, иллюстрирующая внутреннюю структуру устройства декодирования с мягким решением, в котором используется блок IFHT, в соответствии со вторым вариантом осуществления настоящего изобретения. На фиг.10 устройство декодирования с мягким решением, в соответствии со вторым вариантом осуществления настоящего изобретения, включает в себя контроллер 1000, умножитель 1010 маски, блок 1020 размещения символа, блок 1030 IFHT и компаратор/селектор 1040. Кроме того, предполагается, что матрица генерирования, которую применяют к переданному блочному коду, во втором варианте осуществления настоящего изобретения идентична матрице, определяемой в соответствии с Уравнением 3. Матрица генерирования в соответствии с Уравнением 3 представляет собой матрицу размером 6 x 11, и (11, 6) блочный код генерируется при использовании матрицы генерирования в соответствии с Уравнением 3. Контроллер 1000 принимает информацию матрицы генерирования, связанную с матрицей генерирования, из главного контроллера (не показан) принимающей стороны и генерирует маску Мi, информацию положения символа и информацию размера IFHT с использованием принятой информации матрицы генерирования. В результате различие между первым вариантом осуществления настоящего изобретения и вторым вариантом осуществления настоящего изобретения существует в операциях, выполняемых контроллером устройства декодирования с мягким решением. То есть, в первом варианте осуществления настоящего изобретения контроллер 700 принимает информацию матрицы генерирования, и информацию размера IFHT от основного контроллера для определения маски Мi, и информацию положения символа, как описано со ссылкой на фиг.7. Однако во втором варианте осуществления настоящего изобретения контроллер 1000 принимает только информацию матрицы генерирования из основного контроллера для генерирования маски Мi, информации положения символа и информации размера IFHT.

Контроллер 1000 определяет количество входов блока 1030 IFHT с использованием информации матрицы генерирования, принятой от основного контроллера, то есть определяет количество оснований, используемых в качестве входов блока 1030 IFHT. Ниже будет описан процесс, с помощью которого контроллер 1000 определяет количество входов блока 1030 IFHT.

Когда определяется количество 2h входов блока 730 IFHT, количество функций маски, используемых в устройстве декодирования, равно 2k-h. В соответствии с этим определяется общее количество операций, выполняемых устройством декодирования. Здесь количество операций устройства декодирования рассчитывают по отношению ко всем "h" (0, h, k). Определяют величину "h", имеющую минимальное количество операций, из всех "h", при этом количество входов блока 730 IFHT определяют как 2h. Когда учитывают общее количество операций устройства декодирования, в соответствии с величиной заданной переменной "h", часть операций, с помощью которых умножают функцию маски, и часть операций выполнения IFHT составляют большую часть всего количества операций устройства декодирования. Здесь, с учетом количества операций, выполняемых для умножения одного входного сигнала, имеющего длину n битов, и одной маски требуется n операций умножения и (n-1) операций суммирования. Можно предположить, что в соответствии со значением "h" используются 2k-h масок. Когда 2k-h масок умножают на входной сигнал, общее количество операций составляет 2k-hЧn операций умножения и 2k-hЧ(n-1) операций суммирования. Кроме того, поскольку в одном блоке IFHT требуется выполнять 2hlog22h(h•2h) операции суммирования и операция IFHT во всем устройстве декодирования выполняется столько раз, каково количество масок, количество операций при выполнении операции IFHT во всем устройстве декодирования составляет h•2k(h•2hЧ2k-h). В соответствии с этим общее количество операций устройства декодирования, в соответствии с переменной величиной "h", равно 2k-hЧn процессов умножения и (n-1)•2k-h+h•2k процессов суммирования.

Если предполагают, что процесс умножения имеет ту же сложность операций, что и процесс суммирования, общее количество операций составит (2n-1)•2k-h+h•2k{n•2k-h+(n-1)•2k-h+h•2k}. В соответствии с этим при определении количества входов блока IFHT в устройстве декодирования блок 1030 IFHT вычисляет все значения количества операций, в соответствии со всеми возможными значениями "h" (0, h, k), выбирает "h", имеющее наименьшее количество операций, и определяет количество (то есть размер) входов IFHT.

Контроллер 1000 учитывает количество операций, сложность системы и время выполнения IFHT и т. д. при выполнении IFHT и определяет количество входов IFHT. То есть, контроллер 1000 определяет количество входов IFHT, имеющих минимальное количество операций, минимальную сложность системы и минимальное время осуществления IFHT. Например, когда матрица генерирования представляет собой матрицу kЧn, на основе матрицы k x n генерируют (n, k) блочный код. Когда в качестве входа IFHT используют одно основание из k оснований матрицы kЧn и (k-1) оснований из k оснований матрицы, kЧn используют в качестве оснований маски, операцию на одном этапе выполняют для 21 входов в IFHT и декодирование с мягким решением повторно выполняют для суммарного количества 2k-1 оснований маски.

На фиг.10 представлена ситуация, когда три основания высоких порядков с первой строки по третью строку из шести оснований матрицы генерирования в уравнении 3 используют в качестве входа IFHT для выполнения IFHT, а другие три основания низких порядков, кроме этих указанных трех оснований высоких порядков, то есть основания с четвертой строки по шестую строку, используют в качестве оснований маски. Контроллер 1000 передает на выход маску Мi, соответствующую определенным основаниям маски, которая поступает в умножитель 1010 маски, определяет информацию положения символа для каждого принятого символа r, в соответствии с определенным количеством входов IFHT, и выводит, таким образом, информацию положения символа в блок 1020 размещения символа. Затем контроллер 1000 передает на выход информацию размера IFHT в блок 1020 размещения символа и в блок 1030 IFHT.

Здесь, поскольку предполагается, что три основания низких порядков матрицы генерирования используются в качестве оснований маски, контроллер 1000 определяет четвертую строку и шестую строку матрицы генерирования, как первое основание m1 маски по третье основание m3 маски соответственно. В соответствии с этим основания маски, используемые в качестве маски, представляют собой основание m1,основаниеm2 и "исключающее ИЛИ" основания m1 иоснования m2 (далее обозначаемое как m1 ⊕ m2), "исключающее ИЛИ" основания m1 иоснования m3 (далее обозначаемое как m1 ⊕ m3), "исключающее ИЛИ"основания m2 иоснования m3 (далее обозначаемое как m2 ⊕ m3) и "исключающее ИЛИ" основанияm1 иоснования m2, а также основания m3 (далее обозначаемое как m1 ⊕m2 ⊕m3).

Кроме того, поскольку устройство декодирования с мягким решением, в соответствии со вторым вариантом осуществления настоящего изобретения, имеет последовательную структуру, дополнительно применяют маску, состоящую из одних единиц, для постоянного учета работы аппаратных средств, когда маску в действительности не применяют, и для учета работы аппаратных средств, когда маску следует применять. То есть, контроллер 1000 выводит маску, состоящую из одних единиц, в умножитель 1010 маски так, что настоящее изобретение позволяет использовать структуру, в действительности не имеющую маску, даже при использовании той же структуры аппаратных средств, которые содержат маску. Основание m1 маски, основание m2 маски и "исключающее ИЛИ" оснований масок (m1 ⊕ m2), "исключающее ИЛИ" (m1 ⊕ m3), "исключающее ИЛИ" (m2 ⊕ m3) и "исключающее ИЛИ" (m1 ⊕ m2 ⊕m3), основание m2 и основание m3 соответственно, модулируют с использованием способа BPSK для использования в качестве масок.

Как известно из уровня техники, поскольку цифровые данные модулируют с использованием способа BPSK, цифровые данные 0 соответствуют +1 и цифровые данные 1 соответствуют -1. Кроме того, как известно из уровня техники, когда маска не была применена, контроллер 1000 не выводит маску, полностью состоящую из единиц, что позволяет пропускать операцию, выполняемую умножителем 1010 маски.

Как известно из уровня техники, устройство декодирования с мягким решением с использованием IFHT может иметь последовательную структуру или параллельную структуру. В настоящем изобретении, для удобства описания, поскольку описано только устройство декодирования с мягким решением, имеющее последовательную структуру, устройство декодирования с мягким решением, представленное на фиг.10, также имеет параллельную структуру. Затем, когда принимают принимаемый сигнал r, контроллер 1000 выводит маску, состоящую из одних единиц, в умножитель 1010 маски при условии, что первоначально применялась маска, состоящая из одних единиц. Умножитель 1010 маски умножает принимаемый сигнал r на маску, состоящую из одних единиц, и выводит результат умножения в блок 1020 размещения символа. На вход блока 1020 размещения символа поступают сигналы с выхода умножителя 1010 маски (то есть принимаемый сигнал r), этот блок перемещает положения символов, составляющих принимаемый сигнал r, в соответствии с информацией положения символа, поступающей с контроллера 1000, и выводит принимаемый сигнал r в блок 1030 IFHT.