Настоящее изобретение относится, в общем случае, к устройству и к способу кодирования/декодирования в системе мобильной связи МДКР (CDMA) (множественного доступа с кодовым разделением) и, в частности, к устройству и способу передачи канала указателя скорости передачи по обратному каналу связи (КУСП-ОБР) (R-RICH), используемому в системе мобильной связи с синхронной передачей данных.

В общем случае, функционирование схемы передачи с переменной скоростью передачи обеспечивают, по существу, посредством дополнительного обратного канала (ДК-ОБР) (R-SCH). В "схеме передачи с переменной скоростью передачи" подвижная станция произвольным образом изменяет скорость своей передачи. Изменение скорости передачи данных, в общем случае, приводит к изменению скорости передачи кодов с исправлением ошибок, используемых при построении кадра, частоты повторения символов, а также длины и типа кодов Уолша, используемых для разнесения по спектру. Следовательно, подвижная станция должна передать в базовую станцию уведомление о скорости передачи данных по дополнительному обратному каналу в текущий момент времени для того, чтобы приемник базовой станции мог правильно осуществлять прием по дополнительному обратному каналу. Предназначенный для этого канал называют каналом указателя скорости передачи по обратному каналу связи (КУСП-ОБР) (R-RICH).

Количество различных скоростей передачи данных, которые могут быть переданы подвижной станцией по дополнительному обратному каналу, зависит от количества дополнительных обратных каналов, которые могут быть одновременно использованы подвижной станцией. Количество дополнительных обратных каналов определяет базовая станция, которая во время процедуры установления телефонного соединения учитывает объем данных, предназначенный для передачи по обратному каналу, а затем передает сообщение об этом в подвижную станцию. Поэтому количество информационных битов, передаваемых по каналу указателя скорости передачи по обратному каналу связи, изменяется в зависимости от количества дополнительных обратных каналов. То есть, в том случае, когда количество дополнительных обратных каналов равно 1, подвижная станция посылает уведомление о скорости передачи данных по обратному каналу с использованием 4-х битов. А в том случае, когда количество дополнительных обратных каналов равно 2, подвижная станция посылает уведомление о скорости передачи данных по обратному каналу с использованием 7-ми битов. Поскольку количество дополнительных обратных каналов, которые могут быть одновременно использованы подвижной станцией, не может быть изменено до тех пор, пока из базовой станции не будет принята специальная команда, подвижная станция осуществляет передачу по каналу указателя скорости передачи по обратному каналу связи либо информации, состоящей из 7-ми битов, либо информации, состоящей из 4-х битов. То есть, подвижная станция никогда не осуществляет одновременную передачу информации, состоящей из 4-х битов, и информации, состоящей из 7-ми битов. В качестве кода с исправлением ошибок, используемого в канале указателя скорости передачи по обратному каналу связи, обычно задают код типа (24,4) или типа (24,7).

Недостаток канала указателя скорости передачи по обратному каналу связи (КУСП-ОБР) (R-RICH) состоит в том, что количество передаваемых битов, посредством которых осуществляют передачу сведений о скоростях передачи по обратному каналу связи, зависит только от количества дополнительных обратных каналов. То есть, при определении количества битов, передаваемых по дополнительному обратному каналу, не учитывают количество различных скоростей передачи данных, на которых подвижная станция может осуществлять передачу по дополнительному обратному каналу. В том случае, когда количество передаваемых битов задают вне зависимости от количества различных скоростей передачи данных, на которых подвижная станция может производить передачу по дополнительному обратному каналу, может оказаться, что подвижная станция осуществляет передачу большего количества битов, чем фактически требуемое количество битов. Например, в том случае, когда количество дополнительных обратных каналов равно 1, а количество различных скоростей передачи данных (или их "разновидностей"), на которых подвижная станция может осуществлять передачу по дополнительному обратному каналу, равно 4, минимальное количество битов, необходимых для передачи сведений о скоростях передачи данных, равно 2. Однако в системах из известного уровня техники, в том случае, когда количество дополнительных обратных каналов равно 1, минимальное количество битов, требуемых для передачи сведений о скоростях передачи данных, равно 4.

В общепринятом способе, в котором количество битов, предназначенных для передачи по каналу указателя скорости передачи по обратному каналу связи, зависит от количества дополнительных обратных каналов, количество битов, передаваемых по каналу указателя скорости передачи по обратному каналу связи, превышает их необходимое количество. Передача избыточного количества битов по каналу указателя скорости передачи по обратному каналу приводит к возрастанию скорости кодирования посредством устройства кодирования, что затрудняет применение оптимального способа кодирования.

На фиг.1 показана структура передатчика КУСП-ОБР (R-RICH). Со ссылкой на фиг.1, устройство 100 кодирования осуществляет кодирование указателя скорости передачи на входе, состоящего либо из 4-х битов, либо из 7-ми битов, и осуществляет вывод 24-х закодированных символов. Повторитель 110 символов выполняет 16-кратное повторение 24-х закодированных символов, поступивших из устройства 100 кодирования. Преобразователь 120 сигнала выполняет операцию преобразования сигнала с закодированными символами, полученными с выхода повторителя 110 символов, путем их преобразования из 0 в 1 и из 1 в -1. Устройство 130 разнесения по спектру осуществляет разнесение символов, подвергнутых преобразованию сигнала, по спектру.

Как показано на фиг.1, указатель скорости передачи состоит из 4-х битов или из 7-ми битов, а перед передачей осуществляют его кодирование в виде 24-х закодированных символов. В случае возникновения ошибок при передаче закодированного указателя скорости передачи в виде закодированных символов, указатель скорости передачи может неправильно указывать скорость передачи кода по соответствующему дополнительному обратному каналу, частоту повторения символов, а также длину и вид кода Уолша, посредством которого осуществляют разнесение по спектру. В результате, приемник не может правильно осуществлять анализ дополнительного обратного канала. Поэтому кодирование указателя скорости передачи необходимо осуществлять посредством устройства кодирования типа (24,4) или типа (24,7), имеющего хорошую производительность. Помимо этого, для обеспечения выполнения анализа соответствующего дополнительного канала декодирование указателя скорости передачи необходимо осуществлять с максимально возможной скоростью.

Следовательно, задачей настоящего изобретения является создание такого устройства и способа кодирования указателя скорости передачи, которые имеют оптимальную производительность.

Другой задачей настоящего изобретения является создание такого устройства и способа кодирования указателя скорости передачи, которые являются наиболее простыми.

Еще одной задачей настоящего изобретения является создание такого устройства и способа, посредством которых сводят к минимуму сложность аппаратных средств за счет использования способа удаления (прокалывания) отдельных символов расширенного кода Рида-Мюллера первого порядка таким образом, чтобы процесс декодирования мог быть выполнен посредством быстрого обратного преобразования Адамара.

Еще одной задачей настоящего изобретения является создание такого устройства и способа, посредством которых осуществляют использование оптимального кодового слова за счет применения способа удаления отдельных символов расширенного кода Рида-Мюллера первого порядка таким образом, чтобы процесс декодирования мог быть выполнен посредством быстрого обратного преобразования Адамара.

Еще одной задачей настоящего изобретения является создание такого устройства и способа, посредством которых сводят к минимуму сложность аппаратных средств за счет минимизации длины ортогонального кода перед удалением его отдельных символов.

Еще одной задачей настоящего изобретения является создание такого устройства и способа, посредством которых не только сводят к минимуму сложность аппаратных средств, осуществляя удаление отдельных символов расширенного ортогонального кода, но также осуществляют генерацию кода, который является оптимальным с точки зрения эффективности исправления ошибок.

Еще одной задачей настоящего изобретения является создание такого устройства и способа, посредством которых сводят к минимуму сложность аппаратных средств и выполняют все операции кодирования, начиная с кодирования типа (24,1) и заканчивая кодированием типа (24,7), осуществляя генерацию кода, который является оптимальным с точки зрения эффективности исправления ошибок.

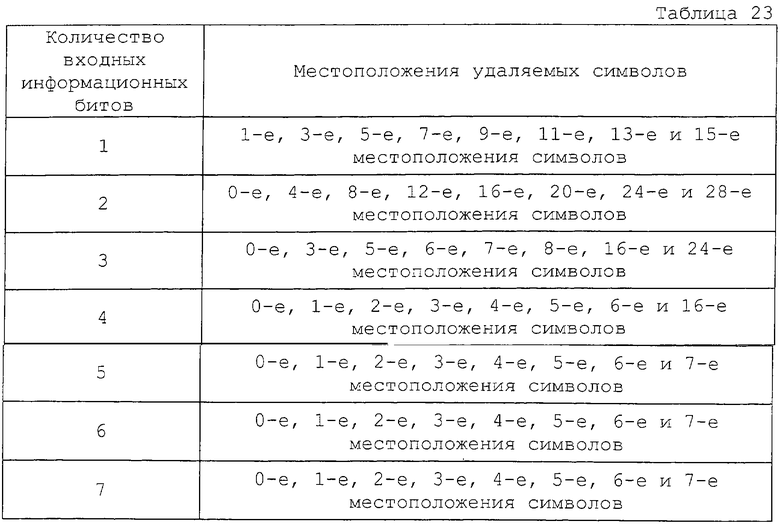

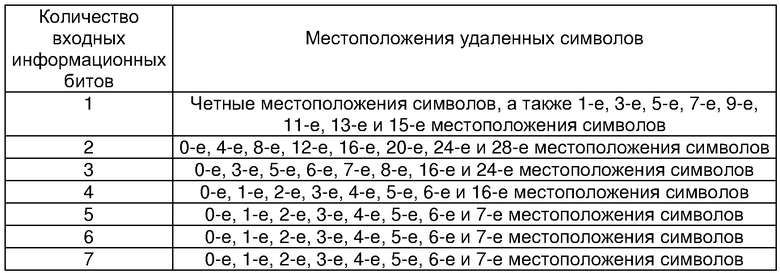

В соответствии с одной из особенностей настоящего изобретения, в нем предложен способ кодирования в системе мобильной связи, посредством которого осуществляют прием от 1-го до 7-ми входных информационных битов и вывод потока закодированных символов, содержащего в себе 24 закодированных символа, зависящих от заранее заданного количества входных информационных битов. Способ кодирования содержит в себе следующие операции: (a) выполняют кодирование входных информационных битов посредством кодов Уолша W1, W2, W4, W8 и W16 и масок М1 и M2, все из которых имеют заранее заданную длину, и осуществляют вывод потока закодированных символов, содержащего в себе заранее заданное количество закодированных символов; (б) заранее определяют множество совокупностей местоположений удаляемых символов, соответствующих каждому из возможных вариантов количества входных информационных битов, и определяют местоположения удаляемых символов, соответствующие количеству входных информационных битов, из заранее определенных совокупностей местоположений удаляемых символов; и (в) из потока закодированных символов, содержащего в себе заранее заданное количество закодированных символов, удаляют отдельные закодированные символы, находящиеся в полученных в результате операции определения местоположениях удаляемых символов, и осуществляют вывод потока закодированных символов, содержащего в себе 24 закодированных символа.

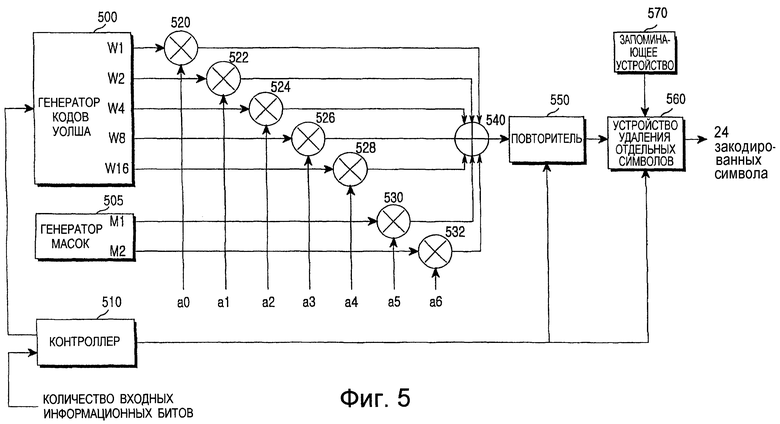

В соответствии с другой особенностью настоящего изобретения, в нем предложено устройство кодирования в системе мобильной связи, посредством которого осуществляют прием от 1-го до 7-ми входных информационных битов и вывод потока закодированных символов, содержащего в себе 24 закодированных символа, зависящих от заранее заданного количества входных информационных битов. Устройство кодирования содержит в себе: генератор кодов Уолша, посредством которого осуществляют генерацию 5-ти различных кодов Уолша W1, W2, W4, W8 и W16, имеющих заранее заданную длину; генератор масок, посредством которого осуществляют генерацию 2-х различных масок M1 и M2; множество умножителей, посредством которых взаимно-однозначным способом выполняют умножение входных информационных битов на коды Уолша W1, W2, W4, W8 и W16 и маски М1 и M2 и осуществляют вывод заранее заданного количества потоков закодированных символов; средство выполнения операции "исключающее ИЛИ", посредством которого выполняют операцию "исключающее ИЛИ" над потоками закодированных символов, поступающими из умножителей, и осуществляют вывод одного потока закодированных символов; и устройство удаления отдельных символов, посредством которого определяют местоположения удаляемых символов, соответствующие количеству входных информационных битов, во множестве совокупностей местоположений удаляемых символов, соответствующих каждому из возможных вариантов количества входных информационных битов, выполняют удаление из потока закодированных символов, поступающего из средства выполнения операции "исключающее ИЛИ", закодированных символов, расположенных в тех местоположениях удаляемых символов, которые получены в результате операции определения, и осуществляют вывод потока закодированных символов, содержащего в себе 24 закодированных символа.

В соответствии с еще одной особенностью настоящего изобретения, в нем предложен способ декодирования в системе мобильной связи, посредством которого осуществляют прием потока закодированных символов, содержащего в себе 24 закодированных символа, и вывод от 1-го до 7-ми входных информационных битов, полученных из потока закодированных символов. Способ декодирования содержит в себе следующие операции: определяют местоположения удаленных символов исходя из информации о длине последовательности входных информационных битов; вставляют нули (0) в полученные в результате операции определения местоположения удаленных символов в потоке закодированных символов и осуществляют вывод потока закодированных символов, содержащего в себе заранее заданное количество закодированных символов; измеряют значения корреляции потока закодированных символов, в который вставлены нули, с кодами Уолша W1, W2, W4, W8 и W16 и с масками M1 и M2, имеющими конкретную длину, определенную исходя из информации о длине последовательности входных информационных битов; и осуществляют вывод входных информационных битов исходя из измеренных значений корреляции.

В соответствии с еще одной особенностью настоящего изобретения, в нем предложено устройство декодирования в системе мобильной связи, посредством которого осуществляют прием потока закодированных символов, содержащего в себе 24 закодированных символа, и вывод от 1-го до 7-ми входных информационных битов, полученных из потока закодированных символов. Устройство декодирования содержит в себе устройство вставки нулей, посредством которого осуществляют вставку нулей (0) в различные местоположения удаленных символов в потоке закодированных символов в зависимости от информации о длине последовательности входных информационных битов; устройство измерения корреляции, посредством которого осуществляют измерение значений корреляции потока закодированных символов, в который вставлены нули, с кодами Уолша W1, W2, W4, W8 и W16 и с масками M1 и M2, длину которых определяют исходя из информации о длине последовательности входных информационных битов; и корреляционный компаратор, посредством которого осуществляют вывод входных информационных битов исходя из измеренных значений корреляции.

Вышеуказанные и иные задачи, отличительные признаки и преимущества настоящего изобретения станут более очевидными из приведенного ниже подробного описания при его рассмотрении в совокупности с сопроводительными чертежами, на которых:

На фиг.1 показана структура передатчика КУСП-ОБР (канала указателя скорости передачи по обратному каналу связи) в обычной системе мобильной связи МДКР;

на фиг.2 показана структура устройства оптимального кодирования типа (24,4) в системе мобильной связи МДКР согласно варианту осуществления настоящего изобретения;

на фиг.3 показана структура кодового слова согласно варианту осуществления настоящего изобретения;

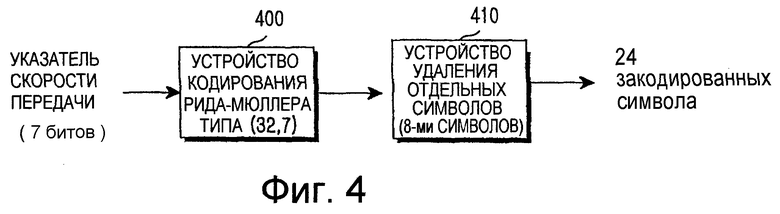

на фиг.4 показана структура устройства оптимального кодирования типа (24,7) в системе мобильной связи МДКР согласно варианту осуществления настоящего изобретения;

на фиг.5 показана структура устройства кодирования, служащего как в качестве устройства оптимального кодирования типа (24,4), так и в качестве устройства оптимального кодирования типа (24,7), в системе мобильной связи МДКР согласно варианту осуществления настоящего изобретения;

на фиг.6 показана структура устройства декодирования в системе мобильной связи МДКР согласно варианту осуществления настоящего изобретения;

на фиг.7 показана структура устройства кодирования типа (24,4), основанного на порождающей матрице из варианта осуществления настоящего изобретения;

на фиг.8 показана структура устройства кодирования типа (24,7), основанного на порождающей матрице из варианта осуществления настоящего изобретения;

на фиг.9 показана видоизмененная структура устройства кодирования, используемого в качестве всех устройств кодирования, начиная с устройства оптимального кодирования типа (24,1) и заканчивая устройством оптимального кодирования типа (24,7), в системе мобильной связи МДКР согласно варианту осуществления настоящего изобретения;

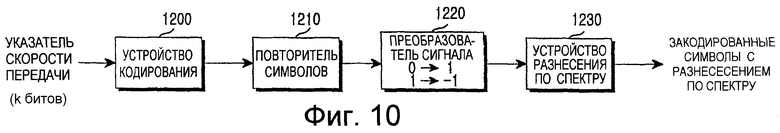

на фиг.10 показана структура передатчика КУСП-ОБР (R-RICH), посредством которого обеспечивают минимальное количество битов, присвоенных указателю скорости передачи, согласно варианту осуществления настоящего изобретения;

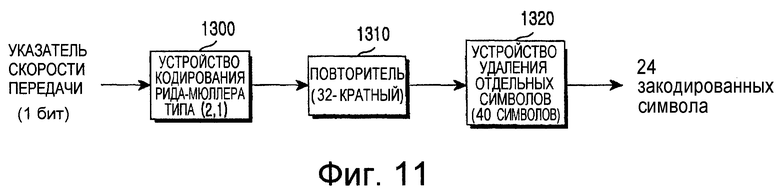

на фиг.11 показана структура устройства кодирования типа (24,1), входящего в состав передатчика согласно варианту осуществления настоящего изобретения;

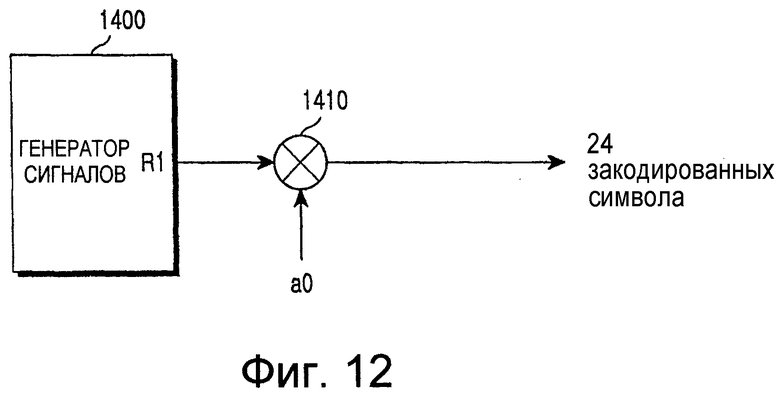

на фиг.12 показано устройство кодирования типа (24,1), основанное на порождающей матрице из фиг.11;

на фиг.13 показана структура устройства кодирования типа (24,2), входящего в состав передатчика согласно варианту осуществления настоящего изобретения;

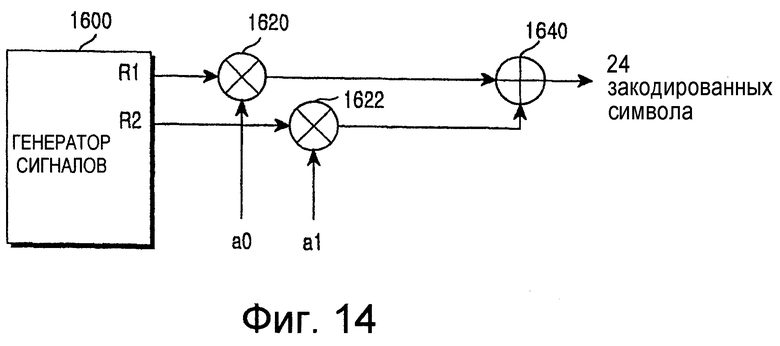

на фиг.14 показано устройство кодирования типа (24,2), основанное на порождающей матрице из фиг.13;

на фиг.15 показана структура устройства кодирования типа (24,3), входящего в состав передатчика согласно варианту осуществления настоящего изобретения;

на фиг.16 показано устройство кодирования типа (24,3), основанное на порождающей матрице из фиг.15;

на фиг.17 показана структура устройства кодирования типа (24,5), входящего в состав передатчика согласно варианту осуществления настоящего изобретения;

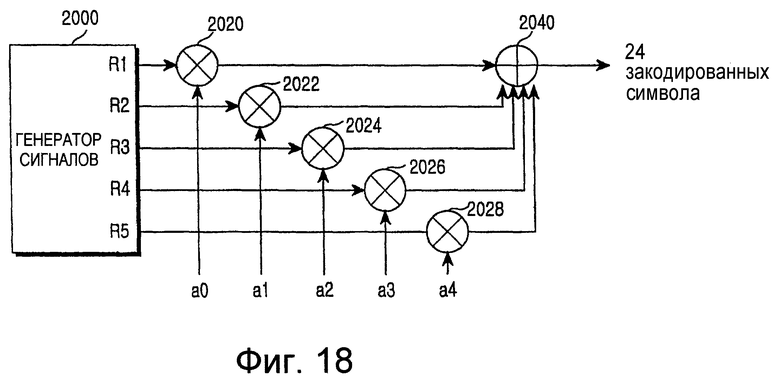

на фиг.18 показано устройство кодирования типа (24,5), основанное на порождающей матрице из фиг.17;

на фиг.19 показана структура расширенного ортогонального кода согласно варианту осуществления настоящего изобретения;

на фиг.20 показана структура устройства кодирования типа (24,6), входящего в состав передатчика согласно варианту осуществления настоящего изобретения; и

на фиг.21 показано устройство кодирования типа (24,6), основанное на порождающей матрице из фиг.20.

Ниже приведено описание предпочтительного варианта осуществления настоящего изобретения со ссылкой на сопроводительные чертежи. В приведенном ниже описании отсутствует подробное описание известных функций или устройств, поскольку это затруднило бы понимание предмета изобретения из-за наличия излишних подробностей.

В общем случае, критерием оценки эффективности линейных кодов с исправлением ошибок служит распределение расстояния Хемминга для кодовых слов в кодах с исправлением ошибок. Посредством "расстояния Хемминга" указывают количество ненулевых символов в кодовом слове. То есть, для определенного кодового слова ‘0111’ количество единиц (1), содержащихся в кодовом слове, равно 3, поэтому расстояние Хемминга равно 3. Наименьшее из значений расстояний Хемминга называют "минимальным расстоянием dmin", а увеличение минимального расстояния в кодовом слове повышает эффективность исправления ошибок посредством кодов с исправлением ошибок. Другими словами, понятие "оптимальный код" означает собой код, имеющий оптимальную эффективность исправления ошибок. Этот вопрос подробно рассмотрен в публикации Ф.Дж.Маквильямса и Н.Дж.Эй.Слоэна "Теория кодов с исправлением ошибок", издательство "Северная Голландия" (The Theory of Error-Correcting Codes, F.J.Macwilliams, N.J.A. Sloane, North-Holland). Кроме того, в статье А.И.Броуэра и Тома Верхоэффа "Обновленная таблица границ минимальных расстояний для линейных двоичных кодов", Труды ИИЭР (Института инженеров по электротехнике и радиоэлектронике, США) по теории информации, том 39, №2, март 1993 г. (Table of Minimum-Distance Bounds for Binary Linear Codes by A.E. Brouwer and Tom Verhoeff, IEEE Transactions on information Theory, Vol. 39, No.2, March 1993) раскрыто минимальное межкодовое расстояние, зависящее от входных и выходных значений линейных двоичных кодов, для получения оптимального кода.

На фиг.10 показана структура передатчика КУСП-ОБР (R-RICH), посредством которого обеспечивают минимизацию количества битов, присвоенных указателю скорости передачи, согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.10, посредством устройства 1200 кодирования осуществляют кодирование указателя скорости передачи, состоящего из k битов, и вывод потока закодированных символов, содержащего в себе 24 закодированных символа. Количество битов k, присвоенных указателю скорости передачи, задают в зависимости от количества различных скоростей передачи данных, на которых подвижная станция может осуществлять передачу по дополнительному обратному каналу. В зависимости от количества k входных битов устройство 1200 кодирования служит в качестве любого из следующих устройств кодирования: устройства кодирования типа (24,1), устройства кодирования типа (24,2), устройства кодирования типа (24,3), устройства кодирования типа (24,4), устройства кодирования типа (24,5), устройства кодирования типа (24,6) или устройства кодирования типа (24,7). Повторитель 1210 символов выполняет 16-кратное повторение 24-х закодированных символов, поступивших из устройства 1200 кодирования. Преобразователь 1220 сигнала выполняет операцию преобразования сигнала с закодированными символами, полученными с выхода повторителя 1210 символов, путем их преобразования из 0 в 1 и из 1 в -1. Устройство 1230 разнесения по спектру осуществляет разнесение символов, подвергнутых преобразованию сигнала, по спектру.

Как указано выше, минимизация количества битов, присвоенных указателю скорости передачи, приводит к уменьшению скорости генерации кода в устройстве кодирования, что, следовательно, обеспечивает улучшение пропускной способности канала указателя скорости передачи.

Устройство кодирования, посредством которого осуществляют кодирование канала указателя скорости передачи, содержит в себе устройство кодирования типа (24,1), устройство кодирования типа (24,2), устройство кодирования типа (24,3), устройство кодирования типа (24,4), устройство кодирования типа (24,5), устройство кодирования типа (24,6) и устройство кодирования типа (24,7). Согласно изложенному в вышеупомянутой статье, устройство оптимального линейного кодирования типа (24,1), на вход которого поступает 1 бит, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 24; устройство оптимального линейного кодирования типа (24,2), на вход которого поступает 2 бита, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 16; устройство оптимального линейного кодирования типа (24,3), на вход которого поступает 3 бита, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 13; устройство оптимального линейного кодирования типа (24,4), на вход которого поступает 4 бита, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 12; устройство оптимального линейного кодирования типа (24,5), на вход которого поступает 5 битов, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 12; устройство оптимального линейного кодирования типа (24,6), на вход которого поступает 6 битов, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 10; а устройство оптимального линейного кодирования типа (24,7), на вход которого поступает 7 битов, а на выходе которого получают 24 бита, имеет максимальное расстояние, равное 10.

Ниже приведено поочередное описание устройств кодирования, начиная с устройства кодирования типа (24,1) и заканчивая устройством кодирования типа (24,7), посредством которых осуществляют кодирование указателя скорости передачи.

1. Устройство кодирования типа (24,1)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,1) осуществляют генерацию оптимального кода (24,1) путем 32-кратного повторения кода Рида-Мюллера типа (2,1), после чего из повторяющегося кода удаляют 40 отдельных символов. Несмотря на то что существует множество способов создания кода типа (24,1), использование способа удаления отдельных символов кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок. Предполагают, что генерацию кодов с исправлением ошибок в варианте осуществления настоящего изобретения осуществляют с использованием кода Рида-Мюллера. К тому же, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины кода Рида-Мюллера перед удалением его отдельных символов.

Получение последовательности закодированных символов длиной 24 бита на выходе устройства кодирования типа (24,1) осуществляют путем 32-кратного повторения 2-х закодированных символов, полученных с выхода генератора кода Рида-Мюллера типа (2,1), и последующего удаления 40 отдельных символов из повторяющихся закодированных символов. Изменение местоположений удаляемых символов при удалении этих 40 отдельных символов из последовательности повторяющихся закодированных символов длиной 64 бита приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,1), обладающего высокой эффективностью исправления ошибок в последовательности закодированных символов длиной 64 бита, важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Наиболее простой схемой удаления символов из этих 40 местоположений удаляемых символов, которую необходимо применить для осуществления генерации оптимального линейного кода типа (24,1), является следующая: {четные местоположения удаляемых символов и местоположения 1, 3, 5, 7, 9, 11, 13, 15}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 1-го информационного бита посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 40 удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

Ниже приведено описание способа кодирования посредством оптимального кода типа (24,1) согласно варианту осуществления настоящего изобретения со ссылкой на фиг.11. На фиг.11 показана структура устройства кодирования, входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.11, в устройство 1300 кодирования Рида-Мюллера типа (2,1) подают один входной информационный бит a0. Здесь входной информационный бит a0 представляет собой указатель скорости передачи. Устройство 1300 кодирования Рида-Мюллера осуществляет кодирование входного информационного бита a0 и вывод последовательности закодированных символов длиной 2 бита (или потока закодированных символов). Закодированные символы образуют собой код Рида-Мюллера. Эти 2 закодированных символа подают в повторитель 1310. Повторитель 1310 осуществляет вывод 64-х закодированных символов путем 32-кратного повторения 2-х полученных закодированных символов. После получения этих 64-х закодированных символов устройство 1320 удаления отдельных символов удаляет из полученных 64-х закодированных символов те закодированные символы, которые расположены в 40 оптимальных местоположениях удаляемых символов, и осуществляет вывод последовательности закодированных символов длиной 24 бита. Устройство 1320 удаления отдельных символов удаляет из 64-х полученных закодированных символов символы с четными номерами, а также 1-й, 3-й, 5-й, 7-й, 9-й, 11-й, 13-й и 15-й символы, которые расположены в вышеуказанных 40 оптимальных местоположениях удаляемых символов, а затем осуществляет вывод 24-х закодированных символов.

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,1) имеет следующий вид:

уравнение 1

M=[1111 1111 1111 1111 1111 1111].

Посредством порождающей матрицы из уравнения 1 осуществляют выбор 24-х символов в первой строке в том случае, если входной сигнал, состоящий из 1-го бита, равен 1, и не осуществляют выбор ни одного символа в том случае, если входной сигнал, состоящий из 1-го бита, равен 0. В том случае, когда не выбран ни один символ, поток символов состоит из 24-х нулей (0).

На фиг.12 показано устройство кодирования типа (24,1), основанное на вышеуказанной порождающей матрице. Со ссылкой на фиг.12, входной информационный бит a0, имеющий значение 0 или 1, подают в умножитель 1410. В тот же самый момент времени генератор 1400 сигналов осуществляет вывод одного потока символов, представляющего собой порождающую матрицу, хранящуюся в запоминающем устройстве. То есть, в генераторе 1400 сигналов запоминают поток символов R1=1111 1111 1111 1111 1111 1111, имеющий длину 24 бита и соответствующий порождающей матрице, хранящейся в запоминающем устройстве, а поток R1 запомненных символов подают в умножитель 1410. Затем в умножителе 1410 выполняют умножение символов из потока R1 символов на входной информационный бит a0 и осуществляют вывод потока закодированных символов длиной 24 бита.

2. Устройство кодирования типа (24,2)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,2) осуществляют генерацию оптимального кода (24,2) путем 8-кратного повторения кода Рида-Мюллера типа (4,2), после чего из повторяющегося кода удаляют 8 отдельных символов. Несмотря на то что существует множество способов создания кода типа (24,2), использование способа удаления отдельных символов кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок. Предполагают, что генерацию кодов с исправлением ошибок в варианте осуществления настоящего изобретения осуществляют с использованием кода Рида-Мюллера. К тому же, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины кода Рида-Мюллера перед удалением его отдельных символов.

Получение последовательности закодированных символов длиной 24 бита на выходе устройства кодирования типа (24,2) осуществляют путем 8-кратного повторения 4-х закодированных символов, полученных с выхода генератора кода Рида-Мюллера типа (4,2), и последующего удаления 8-ми отдельных символов из повторяющихся закодированных символов. Изменение местоположений удаляемых символов при удалении этих 8-ми отдельных символов из последовательности повторяющихся закодированных символов длиной 32 бита, приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,2), обладающего высокой эффективностью исправления ошибок в последовательности закодированных символов длиной 32 бита, важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Наиболее простой схемой удаления символов из этих 8-ми местоположений удаляемых символов, которую необходимо применить для осуществления генерации оптимального линейного кода типа (24,2), является следующая: {0, 4, 8, 12, 16, 20, 24, 28}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 2-х информационных битов посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 8-ми удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

Ниже приведено описание способа кодирования посредством оптимального кода типа (24,2) согласно варианту осуществления настоящего изобретения со ссылкой на фиг.13. На фиг.13 показана структура устройства кодирования, входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.13, в устройство 1500 кодирования Рида-Мюллера типа (4,2) подают два входных информационных бита а0 и а1. Здесь входные информационные биты а0 и а1 образуют собой указатель скорости передачи. Устройство 1500 кодирования Рида-Мюллера осуществляет кодирование входных информационных битов а0 и а1 и вывод последовательности закодированных символов длиной 4 бита (или потока закодированных символов). Закодированные символы образуют собой код Рида-Мюллера. Эти 4 закодированных символа подают в повторитель 1510. Повторитель 1510 осуществляет вывод 32-х закодированных символов путем 8-кратного повторения полученных последовательностей закодированных символов длиной 4 бита. После получения 32-х закодированных символов устройство 1320 удаления отдельных символов удаляет из этих 32-х закодированных символов 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й символы, находящиеся в вышеуказанных 8-ми оптимальных местоположениях удаляемых символов, и таким образом осуществляет вывод 24-х закодированных символов.

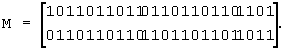

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,2) имеет следующий вид:

уравнение 2

Посредством порождающей матрицы из уравнения 2 осуществляют выбор 24-х символов из первой строки в том случае, если первый входной информационный бит из 2-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если первый входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из второй строки в том случае, если второй входной информационный бит из 2-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если второй входной информационный бит равен 0. Генерацию потока закодированных символов для входных информационных битов осуществляют посредством операции "исключающее ИЛИ", которую выполняют посимвольным способом для всех выбранных потоков.

На фиг.14 показано устройство кодирования типа (24,2), основанное на вышеуказанной порождающей матрице. Со ссылкой на фиг.14, из входных информационных битов а0 и а1, принимающих значения 0 или 1, входной информационный бит а0 подают в соответствующий умножитель 1620, а входной информационный бит а1 подают в соответствующий умножитель 1622. В тот же самый момент времени генератор 1600 сигналов осуществляет вывод в соответствующие умножители двух потоков символов, образующих собой порождающую матрицу, хранящуюся в запоминающем устройстве. То есть, в генераторе 1600 сигналов запоминают поток символов R1=101 101 101 101 101 101 101 101, имеющий длину 24 бита и соответствующий первой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подают поток R1 запомненных символов в умножитель 1620. Кроме того, в генераторе 1600 сигналов запоминают поток символов R2=011 011 011 011 011 011 011 011, имеющий длину 24 бита и соответствующий второй строке порождающей матрицы, хранящейся в запоминающем устройстве, и подают поток R2 запомненных символов в умножитель 1622. Затем в умножителе 1620 выполняют умножение символов из потока R1 символов на входной информационный бит a0 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 1640 выполнения операции "исключающее ИЛИ". Помимо этого, в умножителе 1622 выполняют умножение символов из потока R2 символов на входной информационный бит a1 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 1640 выполнения операции "исключающее ИЛИ". После этого средство 1640 выполнения операции "исключающее ИЛИ" осуществляет посимвольное выполнение операции "исключающее ИЛИ" над двумя полученными потоками символов, каждый из которых имеет длину 24 бита, и вывод потока закодированных символов длиной 24 бита.

3. Устройство кодирования типа (24,3)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,3) осуществляют генерацию оптимального кода типа (24,3) путем 4-кратного повторения кода Рида-Мюллера типа (8,3), после чего из повторяющегося кода удаляют 8 отдельных символов. Несмотря на то что существует множество способов создания кода типа (24,3), использование способа удаления отдельных символов кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок. Предполагают, что генерацию кодов с исправлением ошибок в варианте осуществления настоящего изобретения осуществляют с использованием кода Рида-Мюллера. К тому же, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины кода Рида-Мюллера перед удалением его отдельных символов.

Получение последовательности закодированных символов длиной 24 бита на выходе устройства кодирования типа (24,3) осуществляют путем 4-кратного повторения 8-ми закодированных символов, полученных с выхода генератора кода Рида-Мюллера типа (8,3), и последующего удаления 8-ми отдельных символов из повторяющихся закодированных символов. Изменение местоположений удаляемых символов при удалении этих 8-ми отдельных символов из последовательности повторяющихся закодированных символов длиной 32 бита приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,3), обладающего высокой эффективностью исправления ошибок в последовательности закодированных символов длиной 32 бита, важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Наиболее простой схемой удаления символов из этих 8-ми местоположений удаляемых символов, которую необходимо применить для осуществления генерации оптимального линейного кода типа (24,3), является следующая: {0, 3, 5, 6, 7, 8, 16, 24}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 3-х информационных битов посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 8-ми удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

Ниже приведено описание способа кодирования посредством оптимального кода типа (24,3) согласно варианту осуществления настоящего изобретения со ссылкой на фиг.15. На фиг.15 показана структура устройства кодирования, входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.15, в устройство 1700 кодирования Рида-Мюллера типа (8,3) подают три входных информационных бита а0, а1 и а2. Здесь входные информационные биты а0, а1 и а2 образуют собой указатель скорости передачи. Устройство 1700 кодирования Рида-Мюллера осуществляет кодирование входных информационных битов а0, а1 и а2 и вывод последовательности закодированных символов длиной 8 битов (или потока закодированных символов). Закодированные символы образуют собой код Рида-Мюллера. Эти 8 закодированных символов подают в повторитель 1710. Повторитель 1710 осуществляет вывод 32-х закодированных символов путем четырехкратного повторения полученных последовательностей закодированных символов длиной по 8 битов. После получения 32-х закодированных символов устройство 1720 удаления отдельных символов удаляет из этих 32-х закодированных символов 0-й, 3-й, 5-й, 6-й, 7-й, 8-й, 16-й и 24-й символы, находящиеся в вышеуказанных 8-ми оптимальных местоположениях удаляемых символов, и осуществляет вывод 24-х закодированных символов.

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,3) имеет следующий вид:

уравнение 3

Посредством порождающей матрицы из уравнения 3 осуществляют выбор 24-х символов из первой строки в том случае, если первый входной информационный бит из 3-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если первый входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из второй строки в том случае, если второй входной информационный бит из 3-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если второй входной информационный бит равен 0. Кроме того, посредством этой порождающей матрицы осуществляют выбор 24-х символов из третьей строки в том случае, если третий входной информационный бит из 3-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если третий входной информационный бит равен 0. Генерацию потока закодированных символов для входных информационных битов осуществляют посредством операции "исключающее ИЛИ", которую выполняют посимвольным способом для всех выбранных потоков.

На фиг.16 показано устройство кодирования типа (24,3), основанное на вышеуказанной порождающей матрице. Со ссылкой на фиг.16, из входных информационных битов а0, а1 и а2, принимающих значения 0 или 1, входной информационный бит а0 подают в соответствующий умножитель 1820, входной информационный бит а1 подают в соответствующий умножитель 1822, а входной информационный бит а2 подают в соответствующий умножитель 1824. В тот же самый момент времени генератор 1800 сигналов осуществляет вывод в соответствующие умножители трех потоков символов, образующих собой порождающую матрицу, хранящуюся в запоминающем устройстве. То есть, в генераторе 1800 сигналов запоминают поток символов R1 = 100 101 0101 101 0101 101 0101, имеющий длину 24 бита и соответствующий первой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подают поток R1 запомненных символов в умножитель 1820. В генераторе 1800 сигналов запоминают поток символов R2 = 010 011 0011 011 0011 011 0011, имеющий длину 24 бита и соответствующий второй строке порождающей матрицы, хранящейся в запоминающем устройстве, и подают поток R2 запомненных символов в умножитель 1822. Кроме того, в генераторе 1600 сигналов запоминают поток символов R3 = 001 000 1111 000 1111 000 1111, имеющий длину 24 бита и соответствующий третьей строке порождающей матрицы, хранящейся в запоминающем устройстве, а поток R3 запомненных символов подают в умножитель 1824. Затем в умножителе 1820 выполняют умножение символов из потока R1 символов на входной информационный бит a0 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 1840 выполнения операции "исключающее ИЛИ". В умножителе 1822 выполняют умножение символов из потока R2 символов на входной информационный бит a1 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 1840 выполнения операции "исключающее ИЛИ". Кроме того, в умножителе 1824 выполняют умножение символов из потока R3 символов на входной информационный бит a2 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 1640 выполнения операции "исключающее ИЛИ". После этого средство 1840 выполнения операции "исключающее ИЛИ" осуществляет посимвольное выполнение операции "исключающее ИЛИ" над 3-мя полученными потоками символов, каждый из который имеет длину 24 бита, и вывод потока закодированных символов длиной 24 бита.

4. Устройство кодирования типа (24,4)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,4) осуществляют генерацию оптимального кода типа (24,4) путем 4-кратного повторения кода Рида-Мюллера типа (16,4), после чего из повторяющегося кода удаляют 8 отдельных символов. Несмотря на то что существует множество способов создания кода типа (24,4), использование способа удаления отдельных символов кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок. К тому же, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины кода Рида-Мюллера перед удалением его отдельных символов. Предполагают, что генерацию кодов с исправлением ошибок в варианте осуществления настоящего изобретения осуществляют с использованием кода Рида-Мюллера.

Получение последовательности закодированных символов длиной 24 бита на выходе устройства кодирования типа (24,4) осуществляют путем двукратного повторения 16-ти закодированных символов, полученных с выхода генератора кода Рида-Мюллера типа (16,4), и последующего удаления 8-ми отдельных символов из повторяющихся закодированных символов. Изменение местоположений удаляемых символов при удалении этих 8-ми отдельных символов из последовательности повторяющихся закодированных символов длиной 32 бита приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,4), обладающего высокой эффективностью исправления ошибок в последовательности закодированных символов длиной 32 бита, важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Наиболее простой схемой удаления символов из этих 8-ми местоположений удаляемых символов, которую необходимо применить для осуществления генерации оптимального линейного кода типа (24,4), является следующая: {0, 1, 2, 3, 4, 5, 6, 16}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 4-х информационных битов посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 8-ми удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

Ниже приведено описание способа кодирования посредством оптимального кода типа (24,4) согласно варианту осуществления настоящего изобретения со ссылкой на фиг.2. На фиг.2 показана структура устройства кодирования, входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.2, в устройство 200 кодирования Рида-Мюллера типа (16,4) подают 4 входных информационных бита а0, а1, а2 и а3. Здесь входные информационные биты а0, а1, а2 и а3 образуют собой указатель скорости передачи. Устройство 200 кодирования Рида-Мюллера осуществляет кодирование входных информационных битов а0, а1, а2 и а3 и вывод последовательности закодированных символов длиной 16 битов (или потока закодированных символов). Закодированные символы образуют собой код Рида-Мюллера. Эти 16 закодированных символов подают в повторитель 210. Повторитель 210 осуществляет вывод 32-х закодированных символов путем двукратного повторения полученных последовательностей закодированных символов длиной по 16 битов. После получения 32-х закодированных символов устройство 220 удаления отдельных символов удаляет из этих 32-х закодированных символов 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 16-й символы, находящиеся в 8-ми оптимальных местоположениях удаляемых символов, и осуществляет вывод 24-х закодированных символов.

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,4) имеет следующий вид:

уравнение 4

Посредством порождающей матрицы из уравнения 4 осуществляют выбор 24-х символов из первой строки в том случае, если первый входной информационный бит из 4-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если первый входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из второй строки в том случае, если второй входной информационный бит из 4-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если второй входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из третьей строки в том случае, если третий входной информационный бит из 4-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если третий входной информационный бит равен 0. Кроме того, посредством этой порождающей матрицы осуществляют выбор 24-х символов из четвертой строки в том случае, если четвертый входной информационный бит из 4-х входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если четвертый входной информационный бит равен 0. Генерацию потока закодированных символов для входных информационных битов осуществляют посредством операции "исключающее ИЛИ", которую выполняют посимвольным способом для всех выбранных потоков.

На фиг.7 показано устройство кодирования типа (24,4), основанное на вышеуказанной порождающей матрице. Со ссылкой на фиг.7, из входных информационных битов а0-а3, принимающих значения 0 или 1, входной информационный бит а0 подают в соответствующий умножитель 920, входной информационный бит а1 подают в соответствующий умножитель 922, входной информационный бит а2 подают в соответствующий умножитель 924, а входной информационный бит а3 подают в соответствующий умножитель 926. В тот же самый момент времени генератор 900 сигналов осуществляет вывод 4-х потоков символов R1-R4, образующих собой порождающую матрицу, хранящуюся в запоминающем устройстве, в соответствующие умножители 920-926. В частности, генератор 900 сигналов осуществляет считывание потока символов R1=1010 1010 1101 0101 0101 0101, имеющего длину 24 бита и соответствующего первой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R1 символов в умножитель 920. Генератор 900 сигналов осуществляет считывание потока символов R2=1001 1001 1011 0011 0011 0011, имеющего длину 24 бита и соответствующего второй строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R2 символов в умножитель 922. Генератор 900 сигналов осуществляет считывание потока символов R3=1000 0111 1000 1111 0000 1111, имеющего длину 24 бита и соответствующего третьей строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R3 символов в умножитель 924. И, наконец, генератор 900 сигналов осуществляет считывание потока символов R4=0111 1111 1000 0000 1111 1111, имеющего длину 24 бита и соответствующего четвертой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R4 символов в умножитель 926. Затем в умножителе 920 выполняют умножение символов из потока R1 символов на входной информационный бит a0 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 940 выполнения операции "исключающее ИЛИ". В умножителе 922 выполняют умножение символов из потока R2 символов на входной информационный бит a1 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 940 выполнения операции "исключающее ИЛИ". В умножителе 924 выполняют умножение символов из потока R3 символов на входной информационный бит a2 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 940 выполнения операции "исключающее ИЛИ". В умножителе 926 выполняют умножение символов из потока R4 символов на входной информационный бит a3 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 940 выполнения операции "исключающее ИЛИ". После этого средство 940 выполнения операции "исключающее ИЛИ" осуществляет посимвольное выполнение операции "исключающее ИЛИ" над четырьмя полученными потоками символов, каждый из которых имеет длину 24 бита, и вывод потока закодированных символов длиной 24 бита.

5. Устройство кодирования типа (24,5)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,5) осуществляют генерацию оптимального кода типа (24,5) путем удаления 8-ми отдельных символов из кода Рида-Мюллера первого порядка типа (32,5). Несмотря на то что существует множество способов создания кода типа (24,5), использование способа удаления отдельных символов кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок. Предполагают, что генерацию кодов с исправлением ошибок в варианте осуществления настоящего изобретения осуществляют с использованием кода Рида-Мюллера. К тому же, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины кода Рида-Мюллера перед удалением его отдельных символов.

Получение последовательности закодированных символов длиной 24 бита на выходе устройства кодирования типа (24,5) осуществляют путем вывода 32-х закодированных символов, созданных посредством генератора кода Рида-Мюллера типа (32,5), и последующего удаления 8-ми отдельных символов из 32-х закодированных символов. Изменение местоположений удаляемых символов при удалении этих 8-ми отдельных символов из последовательности закодированных символов длиной 32 бита приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,5), обладающего высокой эффективностью исправления ошибок в коде Рида-Мюллера первого порядка типа (32,5), важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Наиболее простой схемой удаления символов из этих 8-ми местоположений удаляемых символов, которую необходимо применить для осуществления генерации оптимального линейного кода типа (24,5), является следующая: {0, 1, 2, 3, 4, 5, 6, 7}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 5-ти информационных битов посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 8-ми удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

Ниже приведено описание способа кодирования посредством оптимального кода типа (24,5) согласно варианту осуществления настоящего изобретения со ссылкой на фиг.17. На фиг.17 показана структура устройства кодирования, входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.17, в устройство 1900 кодирования Рида-Мюллера типа (32,5) подают 5 входных информационных битов а0, а1, а2, а3 и а4. Здесь входные информационные биты а0, а1, а2, а3 и а4 образуют собой указатель скорости передачи. Устройство 1900 кодирования Рида-Мюллера осуществляет кодирование входных информационных битов а0, а1, а2 а3 и а4 и вывод последовательности закодированных символов длиной 32 бита (или потока закодированных символов). После получения 32-х закодированных символов устройство 1920 удаления отдельных символов удаляет из этих 32-х закодированных символов 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й символы, находящиеся в 8-ми оптимальных местоположениях удаляемых символов, и осуществляет вывод 24-х закодированных символов.

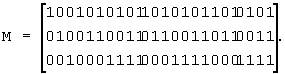

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,5) имеет следующий вид:

уравнение 5

Посредством порождающей матрицы из уравнения 5 осуществляют выбор 24-х символов из первой строки в том случае, если первый входной информационный бит из 5-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если первый входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из второй строки в том случае, если второй входной информационный бит из 5-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если второй входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из третьей строки в том случае, если третий входной информационный бит из 5-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если третий входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из четвертой строки в том случае, если четвертый входной информационный бит из 5-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если четвертый входной информационный бит равен 0. Кроме того, посредством этой порождающей матрицы осуществляют выбор 24-х символов из пятой строки в том случае, если пятый входной информационный бит из 5-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если пятый входной информационный бит равен 0. Генерацию потока закодированных символов для входных информационных битов осуществляют посредством операции "исключающее ИЛИ", которую выполняют посимвольным способом для всех выбранных потоков.

На фиг.18 показано устройство кодирования типа (24,5), основанное на вышеуказанной порождающей матрице. Со ссылкой на фиг.18, из входных информационных битов а0-а4, принимающих значения 0 или 1, входной информационный бит а0 подают в соответствующий умножитель 2020, входной информационный бит а1 подают в соответствующий умножитель 2022, входной информационный бит а2 подают в соответствующий умножитель 2024, входной информационный бит а3 подают в соответствующий умножитель 2026, а входной информационный бит а4 подают в соответствующий умножитель 2028. В тот же самый момент времени генератор 2000 сигналов осуществляет вывод 5-ти потоков символов R1-R5, образующих собой порождающую матрицу, хранящуюся в запоминающем устройстве, в соответствующие умножители 2020-2028. В частности, генератор 2000 сигналов осуществляет считывание потока символов R1=0101 0101 0101 0101 0101 0101, имеющего длину 24 бита и соответствующего первой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R1 символов в умножитель 2020. Генератор 2000 сигналов осуществляет считывание потока символов R2=0011 0011 0011 0011 0011 0011, имеющего длину 24 бита и соответствующего второй строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R2 символов в умножитель 2022. Генератор 2000 сигналов осуществляет считывание потока символов R3=0000 1111 0000 1111 0000 1111, имеющего длину 24 бита и соответствующего третьей строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R3 символов в умножитель 2024. Генератор 2000 сигналов осуществляет считывание потока символов R4=1111 1111 0000 0000 1111 1111, имеющего длину 24 бита и соответствующего четвертой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R4 символов в умножитель 2026. И, наконец, генератор 2000 сигналов осуществляет считывание потока символов R5=0000 0000 1111 1111 1111 1111, имеющего длину 24 бита и соответствующего пятой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R5 символов в умножитель 2028. Затем в умножителе 2020 выполняют умножение символов из потока R1 символов на входной информационный бит a0 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2040 выполнения операции "исключающее ИЛИ". В умножителе 2022 выполняют умножение символов из потока R2 символов на входной информационный бит a1 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2040 выполнения операции "исключающее ИЛИ". В умножителе 2024 выполняют умножение символов из потока R3 символов на входной информационный бит a2 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2040 выполнения операции "исключающее ИЛИ". В умножителе 2026 выполняют умножение символов из потока R4 символов на входной информационный бит a3 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2040 выполнения операции "исключающее ИЛИ". В умножителе 2028 выполняют умножение символов из потока R5 символов на входной информационный бит a4 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2040 выполнения операции "исключающее ИЛИ". После этого средство 2040 выполнения операции "исключающее ИЛИ" осуществляет посимвольное выполнение операции "исключающее ИЛИ" над пятью полученными потоками символов, каждый из которых имеет длину 24 бита, и вывод потока закодированных символов длиной 24 бита.

6. Устройство кодирования типа (24,6)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,6) осуществляют генерацию оптимального кода типа (24,6) посредством удаления 8-ми отдельных символов из расширенного ортогонального кода, полученного путем расширения кодового слова с использованием одной функции маски для ортогонального кода типа (32,5) (или кода Рида-Мюллера первого порядка).

На фиг.19 показана структура расширенного ортогонального кода. Со ссылкой на фиг.19, в том случае, когда используемой функцией маски является M1, в качестве верхних 32-х кодовых слов используют 32 ортогональных кодовых слова W длиной по 32 бита, а в качестве следующих 32-х кодовых слов используют 32 кодовых слова (M1+W), полученных посредством выполнения операции "исключающее ИЛИ" над функцией маски M1 и 32-мя ортогональными кодовыми словами W. Следовательно, в качестве расширенных ортогональных кодов используют всего 26=64 кодовых слова. Функцию маски, обеспечивающую оптимизацию кода типа (24,6), определяют экспериментально.

Функция маски M1 может иметь, например, следующий вид:

M1=0000 0000 1110 1000 1101 1000 1100 0000.

Несмотря на то что существует множество способов создания кода типа (24,6), использование способа удаления отдельных символов из расширенного кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок, что позволяет осуществлять декодирование посредством быстрого обратного преобразования Адамара. Генерацию кода с исправлением ошибок в варианте осуществления настоящего изобретения выполняют с использованием расширенного ортогонального кода. Кроме того, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины ортогонального кода перед удалением его отдельных символов.

Генерацию кодового слова типа (24,6) осуществляют путем удаления 8-ми отдельных символов из 32-х закодированных символов, получаемых на выходе генератора расширенного кода типа (32,6). При этом, изменение местоположений удаляемых символов при удалении этих 8-ми отдельных символов из расширенной последовательности, состоящей из 32-х закодированных символов, приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,6), обладающего высокой эффективностью исправления ошибок в расширенном ортогональном коде типа (32,6), важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Местоположения 8-ми удаляемых символов, необходимых для осуществления генерации оптимального линейного кода типа (24,6), вычисляют экспериментально. Наиболее простой схемой удаления символов является следующая: {0, 1, 2, 3, 4, 5, 6, 7}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 6-ти информационных битов посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 8-ми удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

На фиг.20 показана структура устройства оптимального кодирования типа (24,6), входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.20, в устройство 2100 расширенного ортогонального кодирования типа (32,6) подают 6 входных информационных битов а0, а1, а2, а3, а4 и а5. Здесь входные информационные биты а0, а1, а2 а3 а4 и а5 образуют собой указатель скорости передачи. Устройство 2100 расширенного ортогонального кодирования осуществляет кодирование шести входных информационных битов а0, а1, а2, а3, а4 и а5 и вывод последовательности закодированных символов длиной 32 бита (или потока закодированных символов). 32 закодированных символа, полученных на выходе устройства 2100 расширенного ортогонального кодирования, подают в устройство 2110 удаления отдельных символов. Устройство 2110 удаления отдельных символов удаляет из этих 32-х закодированных символов 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й символы, находящиеся в 8-ми оптимальных местоположениях удаляемых символов, и осуществляет вывод 24-х закодированных символов.

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,6) имеет следующий вид:

уравнение 6

Посредством порождающей матрицы из уравнения 6 осуществляют выбор 24-х символов из первой строки в том случае, если первый входной информационный бит из 6-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если первый входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из второй строки в том случае, если второй входной информационный бит из 6-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если второй входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из третьей строки в том случае, если третий входной информационный бит из 6-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если третий входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из четвертой строки в том случае, если четвертый входной информационный бит из 6-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если четвертый входной информационный бит равен 0. Посредством этой порождающей матрицы осуществляют выбор 24-х символов из пятой строки в том случае, если пятый входной информационный бит из 6-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если пятый входной информационный бит равен 0. И, наконец, посредством этой порождающей матрицы осуществляют выбор 24-х символов из шестой строки в том случае, если шестой входной информационный бит из 6-ти входных информационных битов равен 1, и не осуществляют выбор ни одного символа в том случае, если шестой входной информационный бит равен 0. Генерацию потока закодированных символов для входных информационных битов осуществляют посредством операции "исключающее ИЛИ", которую выполняют посимвольным способом для всех выбранных потоков.

На фиг.21 показано устройство кодирования типа (24,6), основанное на вышеуказанной порождающей матрице. Со ссылкой на фиг 21, из входных информационных битов а0-а5, принимающих значения 0 или 1, входной информационный бит а0 подают в соответствующий умножитель 2220, входной информационный бит а1 подают в соответствующий умножитель 2222, входной информационный бит а2 подают в соответствующий умножитель 2224, входной информационный бит а3 подают в соответствующий умножитель 2226, входной информационный бит а4 подают в соответствующий умножитель 2228, а входной информационный бит а5 подают в соответствующий умножитель 2230. В тот же самый момент времени генератор 2200 сигналов осуществляет вывод 6-ти потоков символов R1-R6, образующих собой порождающую матрицу, хранящуюся в запоминающем устройстве, в соответствующие умножители 2220-2230. В частности, генератор 2200 сигналов осуществляет считывание потока символов R1=0101 0101 0101 0101 0101 0101, имеющего длину 24 бита и соответствующего первой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R1 символов в умножитель 2220. Генератор 2200 сигналов осуществляет считывание потока символов R2=0011 0011 0011 0011 0011 0011, имеющего длину 24 бита и соответствующего второй строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R2 символов в умножитель 2222. Генератор 2200 сигналов осуществляет считывание потока символов R=0000 1111 0000 1111 0000 1111, имеющего длину 24 бита и соответствующего третьей строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R3 символов в умножитель 2224. Генератор 2200 сигналов осуществляет считывание потока символов R4=1111 1111 0000 0000 1111 1111, имеющего длину 24 бита и соответствующего четвертой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R4 символов в умножитель 2226. Генератор 2200 сигналов осуществляет считывание потока символов R5=0000 0000 1111 1111 1111 1111, имеющего длину 24 бита и соответствующего пятой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R5 символов в умножитель 2228. Генератор 2200 сигналов осуществляет считывание потока символов R6=1110 1000 1101 1000 1100 0000, имеющего длину 24 бита и соответствующего шестой строке порождающей матрицы, хранящейся в запоминающем устройстве, и подает считанный поток R6 символов в умножитель 2230. Затем в умножителе 2220 выполняют умножение символов из полученного потока R1 символов на входной информационный бит a0 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2240 выполнения операции "исключающее ИЛИ". В умножителе 2222 выполняют умножение символов из полученного потока R2 символов на входной информационный бит a1 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2240 выполнения операции "исключающее ИЛИ". В умножителе 2224 выполняют умножение символов из полученного потока R3 символов на входной информационный бит a2 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2240 выполнения операции "исключающее ИЛИ". В умножителе 2226 выполняют умножение символов из полученного потока R4 символов на входной информационный бит a3 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2240 выполнения операции "исключающее ИЛИ". В умножителе 2228 выполняют умножение символов из полученного потока R5 символов на входной информационный бит a4 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2240 выполнения операции "исключающее ИЛИ". В умножителе 2230 выполняют умножение символов из полученного потока R6 символов на входной информационный бит a5 и осуществляют вывод потока закодированных символов длиной 24 бита в средство 2240 выполнения операции "исключающее ИЛИ". После этого средство 2240 выполнения операции "исключающее ИЛИ" осуществляет посимвольное выполнение операции "исключающее ИЛИ" над этими шестью потоками символов, каждый из которых имеет длину 24 бита, и вывод потока закодированных символов длиной 24 бита.

7. Устройство кодирования типа (24,7)

Посредством предложенного в настоящем изобретении устройства кодирования типа (24,7) осуществляют генерацию оптимального кода типа (24,7) посредством удаления 8-ми отдельных символов из расширенного ортогонального кода, полученного путем расширения кодового слова с использованием двух функций маски для ортогонального кода типа (32,5) (или кода Рида-Мюллера первого порядка).

На фиг.3 показана структура расширенного ортогонального кода. Со ссылкой на фиг.3, в том случае, когда двумя используемыми функциями маски являются М1 и М2, в качестве верхних 32-х кодовых слов используют 32 ортогональных кодовых слова W длиной по 32 бита, а в качестве следующих 32-х кодовых слов используют 32 кодовых слова (M1+W), полученных путем выполнения операции "исключающее ИЛИ" над функцией маски M1 и 32-мя ортогональными кодовыми словами W. В качестве дальнейших 32-х кодовых слов используют 32 кодовых слова (M2+W), полученных путем выполнения операции "исключающее ИЛИ" над функцией маски M2 и 32-мя ортогональными кодовыми словами W, а в качестве последних 32-х кодовых слов используют 32 кодовых слова (M1+М2+W), полученных путем выполнения операции "исключающее ИЛИ" над функцией маски M1 и М2 и 32-мя ортогональными кодовыми словами W. Следовательно, в качестве расширенных ортогональных кодов используют всего 27=128 кодовых слова. Эти две функции маски, обеспечивающие оптимизацию кода типа (24,7), определяют экспериментально.

Функции маски M1 и М2 могут иметь, например, следующий вид:

M1=0000 0000 1110 1000 1101 1000 1100 0000,

M2=0000 0000 1100 0000 0111 1110 0010 1000.

Несмотря на то что существует множество способов создания кода типа (24,7), использование способа удаления отдельных символов из расширенного кода Рида-Мюллера первого порядка согласно варианту осуществления настоящего изобретения позволяет не только свести к минимуму сложность аппаратных средств, но также создать такое кодовое слово, которое является оптимальным с точки зрения эффективности исправления ошибок, что позволяет осуществлять декодирование посредством быстрого обратного преобразования Адамара. Кроме того, существует возможность свести к минимуму сложность аппаратных средств путем минимизации длины ортогонального кода перед удалением его отдельных символов. Предполагают, что генерацию кода с исправлением ошибок в варианте осуществления настоящего изобретения выполняют с использованием расширенного ортогонального кода.

Генерацию кодового слова типа (24,7) осуществляют путем удаления 8-ми отдельных символов из 32-х закодированных символов, получаемых на выходе генератора расширенного кода типа (32,7). При этом, изменение местоположений удаляемых символов при удалении этих 8-ми отдельных символов из расширенной последовательности, состоящей из 32-х закодированных символов, приводит к изменению минимального расстояния dmin кодового слова. Следовательно, для реализации устройства кодирования типа (24,7), обладающего высокой эффективностью исправления ошибок в расширенном ортогональном коде типа (32,7), важно осуществить вычисление таких местоположений удаляемых символов, посредством которых может быть получено наибольшее минимальное расстояние.

Местоположения 8-ми удаляемых символов, необходимых для осуществления генерации оптимального линейного кода типа (24,7), могут быть вычислены экспериментально. Наиболее простыми схемами удаления символов являются следующие: {0, 4, 8, 12, 16, 20, 24, 28} или {0, 1, 2, 3, 4, 5, 6, 7}. В этом случае передатчик и приемник системы мобильной связи, производящие передачу 7-ми информационных битов посредством способа кодирования/декодирования из настоящего изобретения, заранее осуществляют обмен данными о местоположении этих 8-ми удаляемых символов или выполняют их предварительное запоминание иным способом. Местоположения удаляемых символов обычно указывают в протоколе связи. В альтернативном варианте информация о местоположении удаляемых символов может быть заранее предоставлена посредством передатчика.

На фиг.4 показана структура устройства оптимального кодирования типа (24,7), входящего в состав передатчика согласно варианту осуществления настоящего изобретения. Со ссылкой на фиг.4, в устройство 400 расширенного ортогонального кодирования типа (32,7) подают 7 входных информационных битов а0, а1, а2, а3, а4, а5 и а6. Здесь входные информационные биты а0, а1, а2, а3, а4, а5 и а6 образуют собой указатель скорости передачи. Устройство 400 расширенного ортогонального кодирования осуществляет кодирование семи входных информационных битов а0, а1, а2, а3, а4, а5 и а6 и вывод последовательности закодированных символов длиной 32 бита (или потока закодированных символов). 32 закодированных символа, полученные на выходе устройства 400 расширенного ортогонального кодирования, подают в устройство 410 удаления отдельных символов. Устройство 410 удаления отдельных символов удаляет из этих 32-х закодированных символов 0-й, 4-й, 8-й, 12-й, 16-й, 20-й, 24-й и 28-й символы либо 0-й, 1-й, 2-й, 3-й, 4-й, 5-й, 6-й и 7-й символы, находящиеся в 8-ми оптимальных местоположениях удаляемых символов, и осуществляет вывод 24-х закодированных символов.

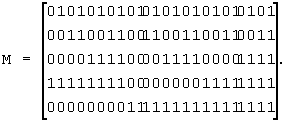

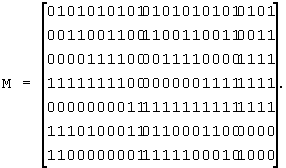

В общей теории кодирования отображение взаимосвязи между входной информацией и закодированными символами осуществляют посредством порождающей матрицы. При наличии операций повторения символов и удаления отдельных символов порождающая матрица для конечного устройства кодирования типа (24,7) имеет следующий вид:

уравнение 7