Настоящее изобретение относится к абонентскому блоку, входящему в состав беспроводной цифровой телефонной системы, в которую этот блок включается для обеспечения беспроводной связи с основной станцией.

Уже известен из US № 4644561 абонентский блок для беспроводной цифровой телефонной системы, содержащий процессор передачи данных, подсоединенный через последовательно соединенные кодер-декодер и интерфейс с абонентским аппаратом, а также с информационным входом процессора модуляции-демодуляции, информационный выход которого через последовательно соединенные передающий блок памяти, интерполятор, программирующую логическую матрицу и цифровой/аналоговый преобразователь соединен с первым входом перемножителя, выход которого соединен с антенной через передающий блок, имеющий переключатель, при этом переключатель соединен с приемным блоком, выход которого подсоединен к информационному входу процессора модуляции-демодуляции через последовательно соединенные блок выборки, аналоговый/цифровой преобразователь и приемный блок памяти, а также задающий генератор, подсоединенный к передающему и приемному блокам.

Недостатки известного абонентского блока заключаются в том, что при его работе могут возникать ложные сигналы (глитч) или кратковременные импульсные помехи, что приводит к снижению качества передачи.

Задача настоящего изобретения заключается в создании абонентского блока для беспроводной цифровой телефонной системы с повышенной помехоустойчивостью и повышенным качеством передачи.

Согласно предложенному изобретению абонентский блок также включает в себя последовательно соединенные делитель частоты, блок синхронизации и формирователь бланкирующего сигнала, причем вход делителя частоты соединен с задающим генератором, выход формирователя бланкирующего сигнала соединен со вторым входом перемножителя, а выход процессора модуляции-демодуляции соединен с другим входом блока синхронизации.

В соответствии с изобретением процессор модуляции-демодуляции содержит демультиплексор, первый и второй выходы которого соединены соответственно с первым и вторым входами эквалайзера, первый и второй выход которого соединены соответственно с первым и вторым входами вычислительного блока, выход которого соединен с входом блока автоматического контроля частоты, первый выход которого соединен со входом кодирующего-декодирующего блока Грея, второй выход соединен через блок весовых коэффициентов с первым входом суммирующего блока, а третий выход соединен с блоком синхронизации абонентского блока, первый и второй выходы эквалайзера также соединены соответственно с первым и вторым входами блока отслеживания частоты, выход которого соединен со вторым входом суммирующего блока.

При этом блок отслеживания частоты в соответствии с изобретением имеет первый и второй суммирующие блоки, причем прямые первый и второй входы первого суммирующего блока соединены соответственно с первым и вторым выходами эквалайзера процессора модуляции-демодуляции, а прямой и инвертирующий входы второго суммирующего блока соединены соответственно с первым и вторым выходами эквалайзера процессора модуляции-демодуляции, при этом выходы первого и второго суммирующих блоков соединены соответственно с входами первого и второго блоков вычисления величины частоты, причем выход первого блока вычисления величины частоты соединен с прямым входом третьего суммирующего блока, а выход второго блока вычисления величины частоты соединен с инвертирующим входом третьего суммирующего блока.

В соответствии с изобретением блок автоматического контроля частоты содержит первый суммирующий блок, прямой вход которого соединен с выходом вычислительного блока процессора модуляции-демодуляции, причем выход указанного первого суммирующего блока соединен со входом блока обнаружения символов, выход которого подключен к первому входу блока временного слежения, выход которого подсоединен к блоку синхронизации абонентского блока, при этом указанный выход блока обнаружения символов соединен также с инвертирующим входом второго суммирующего блока, прямой вход которого соединен с выходом первого суммирующего блока, при этом выход второго суммирующего блока соединен со входом фильтра нижних частот второго порядка, выход которого соединен с блоком весовых коэффициентов процессора модуляции-демодуляции, а выход второго суммирующего блока соединен со вторым входом блока временного слежения, причем выход указанного блока обнаружения символов также соединен с кодирующим/декодирующим блоком Грея процессора модуляции-демодуляции, а второй выход фильтра нижних частот второго порядка соединен с инвертирующим входом первого суммирующего блока.

Таким образом, процессор передачи данных этого абонентского блока выполняет большое количество функций, включающих автоматическое кодирование входных и выходных сигналов из одного типа потока бит в другой и обеспечение эхокомпенсации. Этот блок действует так же, как управляющий микропроцессор, например, с целью подачи команды на синтезирующее устройство в системе с тем, чтобы задать требуемую рабочую частоту. Кроме того, абонентский блок подключается к запоминающему устройству для приема и хранения различных функций, выполняемых или принимаемых в связи с этим.

Процессор передачи данных подключается к процессору модуляции-демодуляции при помощи устройства прямого доступа, которое предотвращает одновременный доступ двумя указанными процессорами, но оба процессора связаны между собой, а процессор модуляции-демодуляции, который действует в системе как ведущий процессор, может делать выборку из памяти процессора передачи данных посредством устройства прямого доступа. В то же время в системе предусмотрено устройство блокировки, посредством которого при некоторых обстоятельствах управление процессором передачи данных со стороны процессора модуляции-демодуляции прекращается.

Процессор модуляции-демодуляции выдает сигналы на заранее определенной частоте амплитудно-импульсной модуляции через сложный сигнал с частотным кодированием, который преобразуется в аналоговый сигнал. Этот аналоговый сигнал подвергается обработке с целью устранения паразитных импульсов путем использования процесса бланкирования (запирания). Обработанный таким образом сигнал преобразуется и фильтруется, чтобы получить сигнал промежуточной частоты, который затем усиливается. Частота усиленного сигнала промежуточной частоты складывается с частотой, вырабатываемой вышеупомянутым синтезирующим устройством, и результирующий сигнал высокой частоты усиливается и подается на антенну.

Абонентский блок использует непрерывно повторяющиеся блоки данных, на которых он передает в течение одной части каждого блока (группы) данных и принимает в течение другой части этого блока. Эти участки обозначаются как области памяти. За счет определенных сигналов, принимаемых от основной станции, процессор передачи данных вырабатывает инициирующие сигналы, которые устанавливают, в каком режиме находится абонентский блок - в режиме передачи или в режиме приема.

В промежутках между действием системы используется режим обучения, в течение которого заданный сигнал от процессора модуляции-демодуляции сравнивается с сигналом контура управления для получения корректирующих коэффициентов, чтобы скомпенсировать нежелательные изменения в сигнале промежуточной частоты, вызванные колебаниями температуры, значений заданных величин и др. Эти корректирующие коэффициенты заносятся в память для использования с целью коррекции реально получаемых (принимаемых) сигналов.

В течение демодуляции модулированные цифровые сигналы подаются на процессор модуляции-демодуляции в форме мультиплексной передачи с временным разделением эталонов I и Q, где они демультиплексируются. Демультиплексированные сигналы I и Q подаются на эквалайзер и схему частотной коррекции для минимизации ошибок, что вызывает появление сигналов частотной коррекции, которые используются для корректирования любых ошибок, возникающих при синхронизации системы и на выходе синтезирующего устройства.

Преимущество изобретения состоит в том, что с его помощью удалось создать средства, позволяющие устранить глитч или кратковременную импульсную помеху в испускающей ветви и различные погрешности в принимающей ветви, причем первое достигается подачей гасящих импульсов в сигнал в схеме испускающей ветви, которые гасят случайные выходные потенциалы после прохождения сигнальных символов по мультиплексированной сигнальной линии, а второе достигается включением в принимающую ветвь фильтра с конечной импульсной характеристикой, который минимизирует погрешности.

Далее изобретение подробно поясняется на примерах выполнения с ссылкой на прилагаемые чертежи, где:

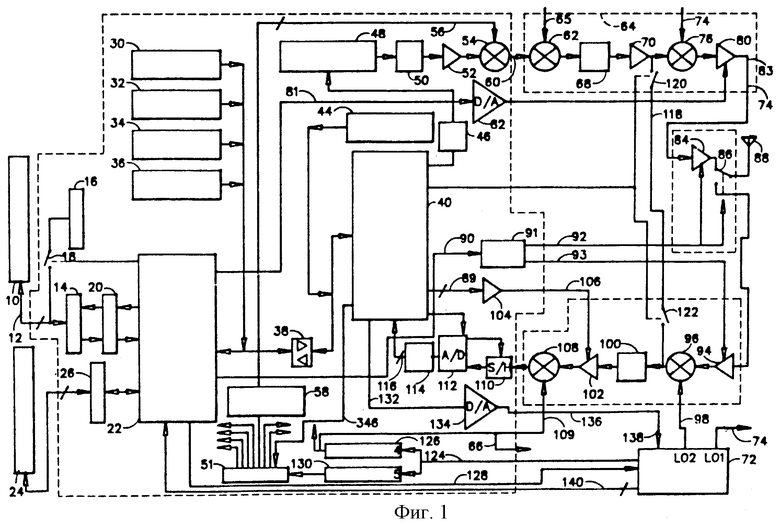

на фиг.1 представлена блок-схема абонентского блока, включенного в настоящее изобретение,

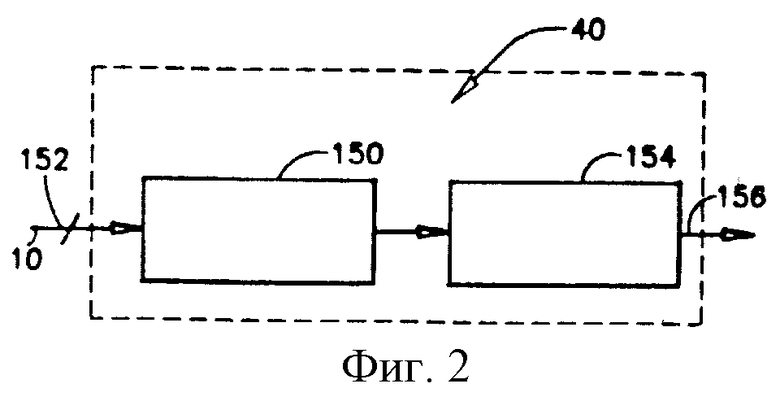

на фиг.2 показана блок-схема модуляции части процессора модуляции-демодуляции, показанного на фиг.1,

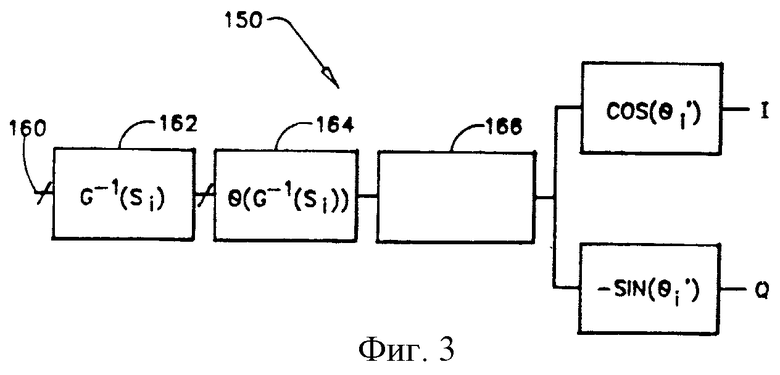

на фиг.3 представлена блок-схема блока преобразования клавиатурной модуляции дифференциального фазового сдвига, показанного на фиг.2,

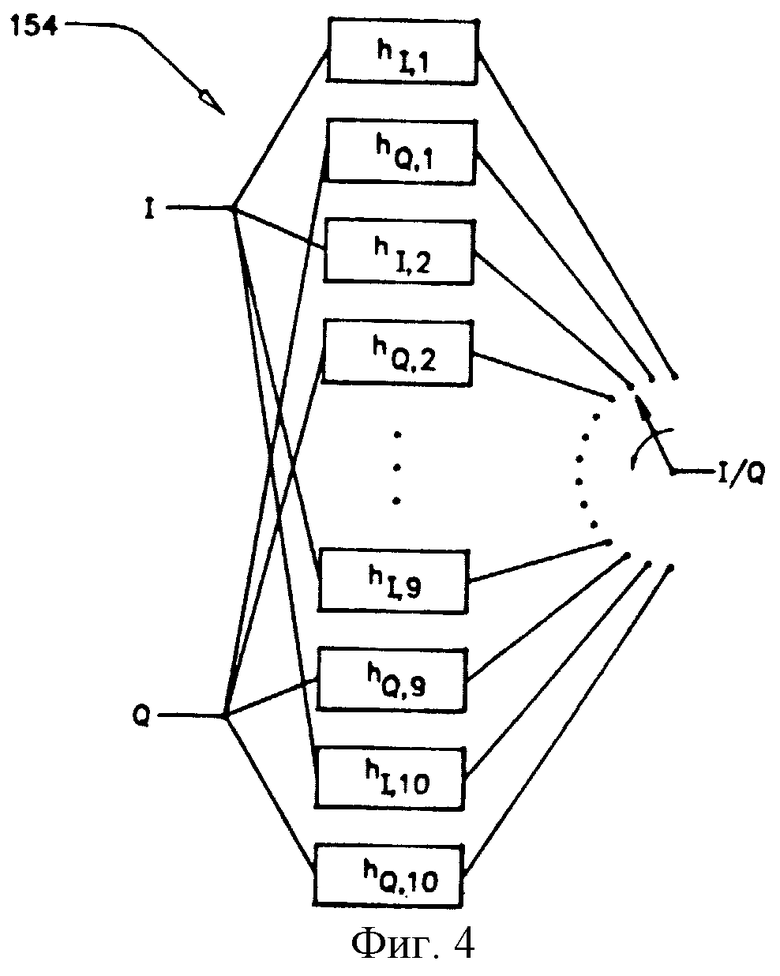

на фиг.4 показаны состав и выполняемые функции фильтра ограниченной импульсной характеристики, изображенного на фиг.2,

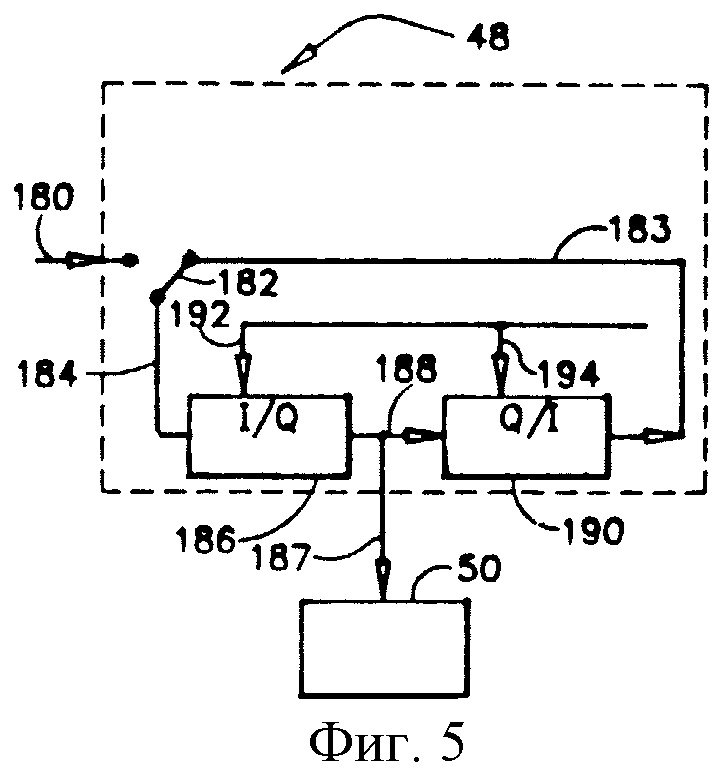

на фиг.5 представлена блок-схема интерполятора, показанного на фиг.1,

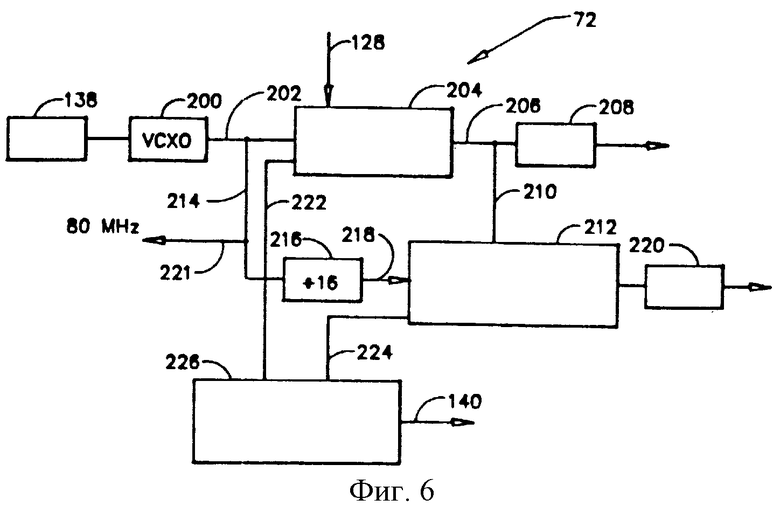

на фиг.6 представлена блок-схема синтезирующего устройства, показанного на фиг.1,

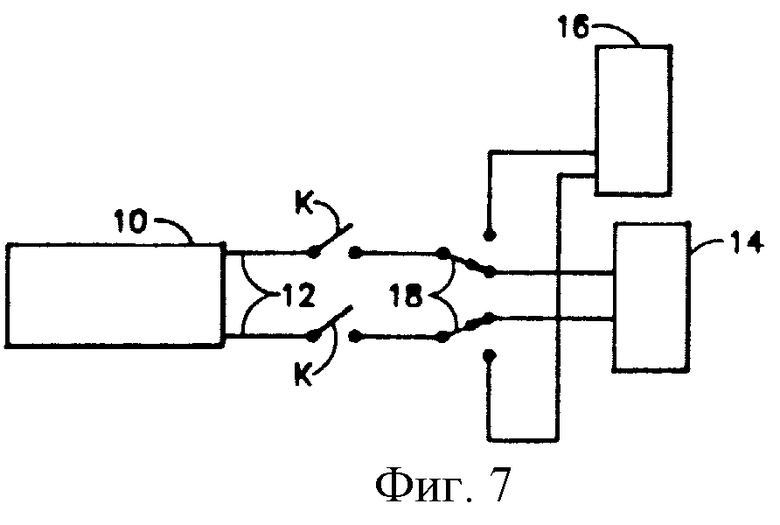

на фиг.7 показана модифицированная форма входной части системы, изображенной на фиг.1,

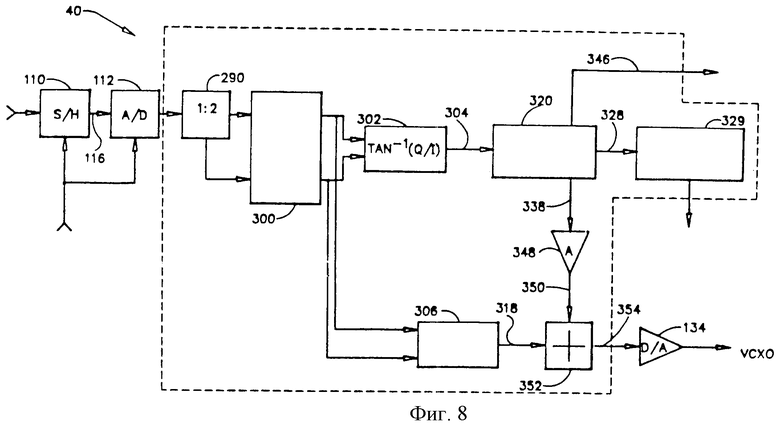

на фиг.8 представлена блок-схема демодулятора процессора модуляции-демодуляции, изображенного на фиг.1,

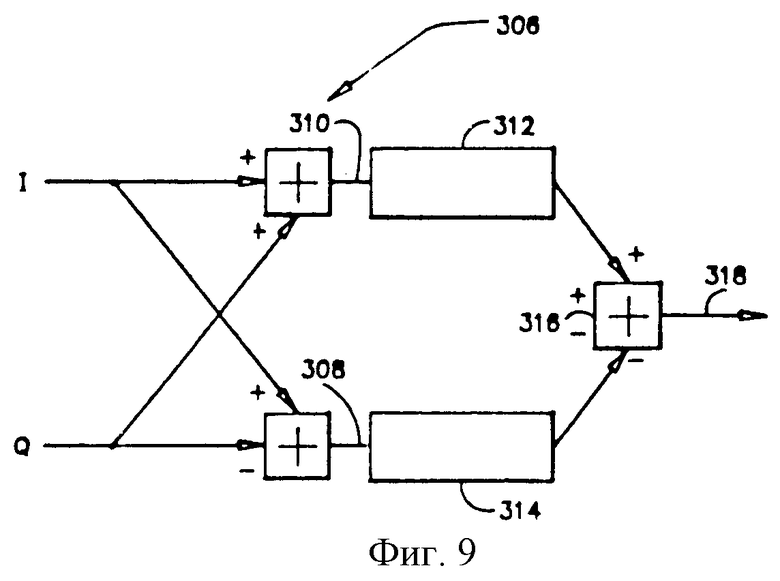

на фиг.9 представлена блок-схема блока управления чередованием частоты, изображенного на фиг.8,

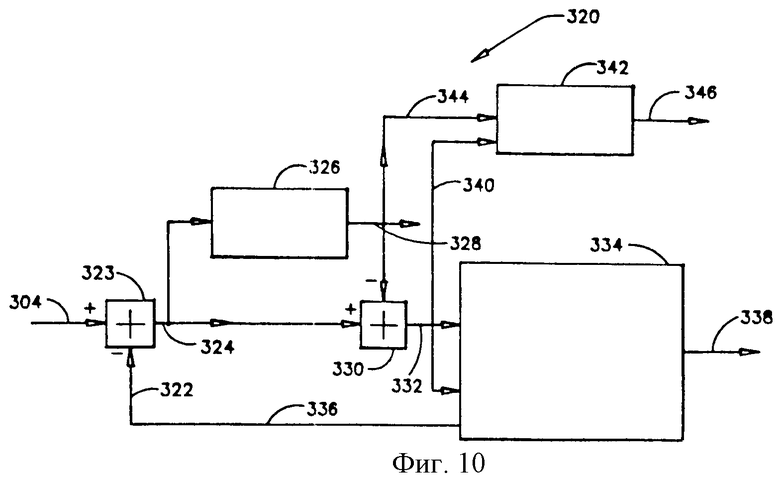

на фиг.10 представлена блок-схема модуля автоматической регулировки частоты и синхронизации символов, изображенного на фиг.8.

Для более полного понимания изобретения ниже приводится словарь специальных обозначений и слов, используемых в описании изобретения:

A/D - аналого-цифровой преобразователь;

ADJ - настраиваемый вход;

AFC - автоматическая регулировка частоты;

AGC - автоматическая регулировка усиления;

BLANKING (запирание) - способ управления для формирования сигнала, который удерживается на заранее определенном уровне амплитуды во время действия устройства управления;

CODEC - совмещенный шифратор и дешифратор;

СРЕ - оборудование пользователя (телефон);

D/A - цифроаналоговый преобразователь;

DMA - прямой доступ к памяти;

DPCK - клавиатурная модуляция дифференциального фазового сдвига;

DS - выборка данных;

ЕЕР ROM - электрически стираемое программируемое постоянное запоминающее устройство;

EP ROM - стираемое программируемое постоянное запоминающее устройство;

FIFO - запоминающее устройство последовательного обслуживания;

FIR - ограниченная (конечная) импульсная характеристика;

GLITCH - нежелательный транзитный сигнал;

HOLD - холостой режим;

I - синфазный;

IF - промежуточная частота;

KвpS - килобит/сек;

nS - наносекунда;

PAL - программируемая логическая матрица;

РСМ - кодово-импульсная модуляция;

PROM - программируемая постоянная память;

PSK - клавиатурная модуляция фазового сдвига;

Q - квадратура;

RAM - память с произвольным доступом;

RELP - линейное прогнозирование возбуждаемое остатком;

RF - высокая частота;

R/W - считывание/запись;

S/H - выборка и блокировка;

SLIC - схема абонентского циклического интерфейса;

STPOBE - сигнал выборки;

VART - универсальный асинхронный приемопередатчик;

VCXO - кварцевый генератор, управляемый напряжением;

XF - внешний (по признаку) выход, используемый для управления других процессоров.

Настоящее изобретение относится к системам связи для беспроводной передачи многочисленных сигналов информации, использующим цифровые схемы временного разделения между основной станцией и одной или более абонентскими станциями. Более конкретно, изобретение относится к структуре и функционированию такой абонентской станции.

Рассмотрим более подробно схемы, на которых имеются соответствующие обозначения, относящиеся к отдельным блокам системы. На фиг.1 показан интерфейс 10, через который осуществляется подключение к оборудованию, поставляемому пользователю. Линейная пара 12 подается от интерфейса 10 на схему абонентского циклического интерфейса 14 и, кроме того, подключается к кольцевой схеме 16 через реле 18. Абонентский интерфейс 14 представляет собой стандартный чип, обеспечивающий различные функции, такие, как подачу питания, защиту от перенапряжения, зацикливание ("звон"), детектирование сигналов в зависимости от поворотного диска, положения телефонной трубки (микротелефона), линейного контроля и др. Этот интерфейс имеет также гибридную схему, которая осуществляет разделение множество голосов во входном и выходном сигналах.

Абонентский интерфейс подключается к кодеру-декодеру 20, имеющему входную и выходную линию к и от процессора 22 передачи данных, где происходит преобразование во входном направлении аналоговых речевых сигналов в цифровые, т.е. со скоростью 64 килобит/сек по закону кодово-импульсной модуляции. В то же время в направлении выхода осуществляется преобразование цифрового сигнала (сигналов) в аналоговые речевые сигналы. Иногда может потребоваться шунтирование кодера-декодера так, чтобы абонентский интерфейс 14 подключался бы непосредственно к процессору 22 передачи данных.

Имеется альтернативный доступ к процессору 22 передачи данных через интерфейс 24 и универсальный асинхронный приемопередатчик 26, который обеспечивает непосредственную цифровую связь с процессором 22 передачи данных, что дает возможность зашунтировать абонентский интерфейс и кодер-декодер. Такой прямой доступ служит для реализации двух целей: 1) пропускать только цифровые сигналы, когда это потребуется, тем самым блокируя все аналоговые соединения; и 2) обеспечить прямой доступ к процессорам и запоминающим устройствам для упрощения обслуживания и контроля.

Процессор 22 передачи данных выполняет несколько функций, одна из которых состоит в преобразовании сигнала, поступающего со скоростью 64 килобит/сек по закону кодово-импульсной модуляции в сигналы 14, 57... килобит/сек путем транскодирования, которое обеспечивается, например, за счет линейного прогнозирования, возбуждаемого остатком. Процессор также обеспечивает эхокомпенсацию и, кроме того, действует подобно управляющему микропроцессору, например, для подачи команды на синтезирующее устройство, используемое в системе, с тем, чтобы задать требуемую рабочую частоту.

Процессор 22 передачи данных подключается к чипу, являющимся самозагружаемым запоминающим устройством, а также к блоку 30, который является электрически стираемым программируемым постоянным запоминающим устройством, т.е. энергонезависимой памятью, в которой выбранные биты могут быть электрически стерты без стирания оставшихся в памяти битов. Это запоминающее устройство 30 используется для хранения как абонентского номера идентификации, так и номера идентификации станции, с которой абонентский блок используется.

Кроме того, процессор 22 передачи данных подключается к высокоскоростному запоминающему устройству 32 с произвольной выборкой, в котором хранятся сигналы, принимаемые процессором. Это запоминающее устройство 32 включает в себя быстродействующую буферную память большой емкости и используется как память с произвольной выборкой для преобразования в режиме линейного прогнозирования, эхокомпенсации и других управляющих функций.

Процессор 22 передачи данных подключается также к полускоростному стираемому программируемому постоянному запоминающему устройству 34 и полноскоростному программируемому постоянному запоминающему устройству 36, в которых происходит хранение режима линейного прогнозирования и эхокомпенсации, а также различных других функций, таких как управление. Процессор 22 передачи данных подключается также через устройство 38 прямого доступа к памяти процессора 40 модуляции-демодуляции.

Устройство 38 прямого доступа к памяти предотвращает возможность одновременного доступа к памяти запоминающего устройства 32 с произвольной выборкой процессора передачи данных и процессора модуляции-демодуляции.

Устройство прямого доступа к памяти используется для обмена речевых и управляющих данных между процессором передачи данных и процессором модуляции-демодуляции. Процессор 40 модуляции-демодуляции работает как ведущий процессор и управляет процессом процессора 22 передачи данных через блокировочные линии (не показаны на схемы). Процессор 40 модуляции-демодуляции имеет возможность доступа к процессору 22 передачи данных, осуществлять соответствующую остановку при его работе и воздействовать на линии управления, адресную шину и шину данных с тем, чтобы обеспечить высокий импеданс трехпозиционного выхода.

Такая способность процессора 40 модуляции-демодуляции обеспечивает ему доступ к памяти процессора 22 передачи данных через устройство прямого доступа к памяти и считывать или заносить данные в нее.

Эта способность достигается путем утверждения бита внешнего выхода процессора 40 модуляции-демодуляции, который подается на вход холостого режима процессора передачи данных. Когда процессор 22 передачи данных принимает такой сигнал, он закончит выполнение текущей команды, сделает остановку, вызовет шину данных и адресную шину, обеспечив тем самым высокий импеданс трехпозиционного выхода, и затем выдаст сигнал подтверждения холостого режима обратно на процессор модуляции-демодуляции. Немедленно после этого процессор модуляции-демодуляции выдаст команду холостого режима, которая будет сохраняться до тех пор, пока процессор передачи данных будет посылать сигнал подтверждения холостого режима. Как только процессор 40 модуляции-демодуляции примет сигнал подтверждения холостого режима, он начнет управлять шинами управления данных и адресной шиной процессора 22 передачи данных и затем считает либо занесет эти данные в устройство 38 прямого доступа к памяти с произвольной выборкой.

Далее, процессор модуляции-демодуляции выполнит выборку памяти с произвольной выборкой, после чего он снимет команду холостого режима с процессора передачи данных, который затем начнет последующую обработку данных с того места, на котором он был остановлен.

Процессор 22 передачи данных также имеет способность заблокировать процессор 40 модуляции-демодуляции путем обеспечения высокого уровня бита своего внешнего выхода, используемого для управления другими процессами. Этот бит регулируется командой холостого режима, поступающей от процессора модуляции и может превысить линию фиксации в любой точке прежде, чем процессор передачи данных перейдет в состояние фиксации. Процессор модуляции-демодуляции использует 10-битовую шину и все 16 битов шины данных. Он также использует три линии управления: линию сигнала выборки, считывания/записи и выборки данных.

Процессор 22 передачи данных или процессор 40 модуляции-демодуляции, действующие в обоих направлениях, могут получать сигналы от запоминающего устройства 32 с произвольной выборкой в соответствии с сигналами, описанными выше. Оба процессора связываются между собой частью устройства 32 памяти с произвольной выборкой, которое устанавливается в стороне, чтобы применяться в качестве кэша - быстродействующей буферной памяти большой емкости.

Процессор 40 модуляции-демодуляции также подключается к полноскоростной программируемой постоянной памяти 44, которая включает программу для этого процессора.

Процессор 40 модуляции-демодуляции в режиме модуляции подает свои сигналы через передающий блок 46 памяти последовательного обслуживания на интерполятор 48, причем эти сигналы подаются с частотой амплитудно-импульсной модуляции, равной 320 кГц. Интерполятор 48 достаточно эффективно усиливает эту частоту в 5 раз, чтобы преобразовать ее в величину 1600 киловыборок/сек (1,6 мегавыборок/сек). Интерполятор в сочетании с кварцевым фильтром, который действует как интегратор, почти соответствует 5-отводному фильтру ограниченной импульсной характеристики. Такое использование цифровой и аналоговой конструкции фильтра ограниченной импульсной характеристики делает его отличным от всех классических цифровых конструкций. Выход интерполятора подключается к программируемой логической матрице 50.

Программируемая логическая матрица 50 собирается в виде смесителя, на который подается сигнал прямоугольной формы с частотой 400 кГц, поступающий от блока 51 синхронизации, а также сигнал с частотой 1600 килосимвол/сек. Этот сигнал представляет собой сигнал с частотой 16 килосимвол/сек с нулевой несущей и заданной шириной полосы, равной 20 кГц. По-существу, программируемая логическая матрица может рассматриваться как преобразователь частоты. Схема программируемой логической матрицы, которая, когда собирается для выполнения второй дополнительной функции, управляемой сигналом прямоугольной формы с частотой 400 кГц, эффективно выполняет квадратурное микширование с временным мультиплексированием и достаточно эффективно преобразует сигнал с частотой в 20 кГц в сигнал с частотой в 400 кГц.

Выход с программируемой логической матрицы 50 представляет собой сложный сигнал, преобразованный по частоте и временным мультиплексированием, который подается на цифроаналоговый преобразователь 52, где происходит преобразование цифрового сигнала в аналоговый. Выходной сигнал от преобразователя 52 подается на перемножитель 54, на который также подается сигнал 56 деглитчирования и запирания с формирователя 58 бланкирующего сигнала. Глитч является основной помехой в системе выборки данных. Глитч или кратковременная импульсная помеха происходит в течение перехода от одного входного слова к другому.

В цифроаналоговом преобразователе 52 каждый входной бит, зависящий от его состояния, может вызвать изменение в уровне выходного аналогового сигнала. Такие изменения, вызываемые различными битами, как правило не происходят одновременно и поэтому вызывают глитчи. Классическими решениями этой проблемы являются использование выборки и блокировки после цифроаналогового преобразования или использование деглитчирования. Однако оба эти варианта являются чрезмерно дорогостоящими.

Бланкирование возвращает выходной сигнал перемножителя на промежуточный эталонный уровень в течение длительности переходных процессов, которая составляет как правило 35 нсек перед и 130 нсек после цифрового времени переключения. Благодаря этому происходит подавление значительных кратковременных импульсных помех, которые появляются на выходе цифроаналогового преобразователя. Поскольку бланкирование создает гармоники от частот, представляющих интерес, то использование относительно узкой фильтрации промежуточной частоты существенно убирает эти гармоники. Такой метод бланкирования также снижает частоту амплитудно-импульсной модуляции на выходе.

Выходной сигнал с перемножителя 54, обозначенный позицией 60, подается на перемножитель 62, находящийся в передающем блоке 64. Перемножитель 62 имеет вход для частоты 20 мГц, обозначенный позицией 65, который является общим с линией на 20 мГц, обозначенной позицией 66. Выходной сигнал перемножителя 62 является суммой сигнала 20 мГц, поступающего со входа 65, и сигнала 400 кГц, принимаемого от перемножителя 54, и равняется 20,4 мГц. Этот выходной сигнал подается на кварцевый фильтр 68, который пропускает только данный суммарный сигнал, являющийся сигналом промежуточной частоты, на усилитель 70.

Задающий генератор (синтезирующее устройство) показан под позицией 72. В это синтезирующее устройство входит синтезирующий блок, который обеспечивает выходной сигнал L01. Второй блок данного синтезирующего устройства обеспечивает выходной сигнал L02, причем второй выходной сигнал отслеживает выходной сигнал L01 на частоте, меньшей на 5 мГц, чем частота L01. Синтезирующее устройство использует в качестве эталона кварцевый генератор, управляемый напряжением с частотой 80 мГц. Выходной сигнал L01 подается через линию 74 на перемножитель 76, который также получает выходной сигнал промежуточной частоты с усилителя 70. Поскольку сигнал промежуточной частоты имеет величину 20,4 мГц, то если, например, требуется получить на выходе перемножителя 76 сигнал с частотой 455,5 мГц, то включается синтезирующее устройство, которое вырабатывает частоту 435,1 мГц, которая складывается с частотой 20,4 мГц, чтобы получить 455,5 мГц. Полученный выходной сигнал затем усиливается на усилителе 80 с переменным коэффициентом усиления.

Процессор 22 передачи данных на основе дешифровки определенных сигналов от основной станции посылает сигнал регулировки усиления в линию 81 через цифроаналоговый преобразователь 82 к усилителю 80 с переменным коэффициентом усиления. Этот усилитель имеет ограниченную ширину полосы пропускания и поэтому не пропускает различные нежелательные частоты, вырабатываемые также перемножителем 76.

Выходной сигнал усилителя 80 пропускается через линию 83 и подается на усилитель 84 мощности, который осуществляет окончательное усиление перед тем, как сигнал высокой частоты будет подан через переключатель 86 на антенну 88.

Блок использует систему, посредством которой группа данных повторяется каждые 45 млсек. В этой системе блок осуществляет передачу в течение части второй половины каждой группы данных и осуществляет прием в течение части первой половины этой группы данных. Одна конфигурация этой системы может быть таковой, когда обе части указанных половин имеют одинаковую длину (хотя они и не обязательно должны быть равными). Другая конфигурация системы может быть такой, при которой четыре части равной длины являются приемлемыми для абонента в течение передачи всей группы данных. Каждая из четырех частей может быть представлена как область. Каждая область содержит как часть своих начальных данных единственное слово, которое используется блоком для установления синхронизации приема оставшихся данных в области. Первая область из четырех выдвигается вперед посредством сигнала амплитудной модуляции, который используется для определения области, произвольно обозначенную базовой станцией как первая область. Сигнал амплитудной модуляции и единственное слово являются частью входного сигнала, поступающего от базовой станции. Длительность сигнала амплитудной модуляции позволяет определить, является ли конкретный высокочастотный канал каналом управления или речевым каналом.

Сигнал данных получается от усредненного значения сигнала, обозначенного на схеме как 116. Уровень, пропорциональный указанному среднему значению, сравнивается с неусредненными величинами. Если уровень не является завышенным за счет неусредненной величины, для заранее определенного периода времени, то допускается, что сигнал амплитудной модуляции должен быть выделен. Процессор 40 модуляции-демодуляции запоминает время, при котором определялся сигнал амплитудной модуляции в запоминающем устройстве 32 с произвольной выборкой.

Процессор 22 передачи данных на основании режима модуляции (а), времени, при котором появлялся сигнал амплитудной модуляции, находящийся в памяти запоминающего устройства 32 с произвольной выборкой (b) и времени, при котором принималось единственное слово и которое определялось отдельно процессором 22 передачи данных (с), начинает вырабатывать инициирующие сигналы, которые указывают, когда блок должен находиться в режиме передачи, а когда в режиме приема. Такие инициирующие сигналы подаются через линию 90 к блоку 91 синхронизации группы данных.

Блок 91 синхронизации групп данных преобразовывает инициирующие сигналы в две серии импульсов. Одна серия импульсов подается через линию 92 на усилитель 84 мощности и переключатель 86 и включает их так, чтобы соединить выходной сигнал усилителя 84 с антенной 88. В течение периода действия импульсов в линии 92 абонентский блок находится в режиме передачи. Когда переключатель 86 отключен, он подключает антенну 88 на вход предварительного усилителя 94.

Другая серия импульсов от блока 91 синхронизации групп данных подается через линию 93 на предварительный усилитель 94 и включает его. В течение периода действия этой серии импульсов абонентский блок находится в режиме приема. Предварительный усилитель 94 передает принятые сигналы на перемножитель 96, на который также поступает выходной сигнал L02 от задающего генератора 72 через линию 98. Выходной сигнал перемножителя 96 подается на кварцевый фильтр 100, выход которого, в свою очередь, подается на усилитель 102 промежуточной частоты.

Процессор 40 модуляции-демодуляции пропускает через линию 89 вышеупомянутый сигнал данных, который получается из среднего значения величины сигнала 116, на цифроаналоговый преобразователь 104, который воспроизводит аналоговый сигнал напряжения автоматической регулировки усиления. Этот сигнал подается через линию 116 на усилитель 102, посредством которого определяется тот коэффициент усиления, который потребуется для удержания сигнала промежуточной частоты на одной и той же амплитуде.

Усилитель 102 получает также выходной сигнал с кварцевого фильтра 100. Далее, выходной сигнал с усилителя 102 подается на перемножитель 108, на который также подается входной сигнал с частотой 20 кГц из линии 109 для получения результирующего сигнала с частотой 400 мГц. Полученный таким образом сигнал подается затем на аналогово-цифровой блок, который состоит из блока 110 выборки и блокировки и аналогово-цифрового преобразователя 112, а также приемного блока 114 памяти последовательного обслуживания.

Выходной сигнал блока преобразования аналоговых сигналов в цифровые составляет величину 64 килобит/сек и он подается через линию 116 на процессор 40 модуляции-демодуляции.

Этот процессор осуществляет демодуляцию указанного сигнала и пропускает демодулированные данные на схему быстродействующей буферной памяти большой емкости, входящей в состав запоминающего устройства 32 с произвольной выборкой, доступ к которому осуществляется при помощи процессора 22 передачи данных, в котором происходит преобразование линейного прогнозирования, возбуждаемого остатком. Результирующий выходной сигнал имеет значение 64 килобит/сек в кодово-импульсной модуляции на постоянном последовательном основании. Этот выходной сигнал подается на шифратор-дешифратор, который преобразовывает этот сигнал в аналоговый, после чего он подается на схему абонентского интерфейса, который, в свою очередь, передает его на телефонный аппарат. Имеется и другой вариант, когда сигнал 16 килобит/сек, подаваемый от буферной памяти, может быть дешифрован в цифровой сигнал, после чего он поступает на универсальный асинхронный приемопередатчик 26.

В моделирующем режиме закольцовывание обеспечивается устройством 118 между двумя реле 120 и 122. Это закольцовывание, которое осуществляется лучше на промежуточной, чем высокой частоте, уменьшает количество требуемых элементов. Моделирующий режим состоит в том, что известный сигнал передается процессором 40 модуляции-демодуляции через незадействованные элементы передатчика на усилитель 70 промежуточной частоты. Поскольку реле 120 и 122 включены, то выходной сигнал с усилителя 70 подается на вход кварцевого фильтра 100.

Кроме того, выходной сигнал процессора 22 передачей данных, обозначенный линией 90, поступает на блок 91 синхронизации групп данных и обусловливает импульс в линии 93, который полностью отключает усилитель 94 во время моделирующего режима. Более того, во время этого режима блок 91 синхронизации групп данных воспроизводит другой импульс, который подается по линии 92 и полностью отключает усилитель 84. Заданный сигнал, вырабатываемый модулятором, сравнивается с реальным сигналом, поступаемым обратно на демодулятор. Далее, устанавливается вспомогательная программа для того, чтобы скомпенсировать различные колебания, вызванные такими факторами, как изменение температуры, значений компонентов и др. Поправочные коэффициенты находятся в запоминающем устройстве 32 с произвольной выборкой. Процессор 40 модуляции-демодуляции применяет эти коэффициенты для коррекции принимаемых сигналов. Моделирующий режим осуществляется в промежутках между действиями системы.

Задающий генератор 72 (синтезирующее устройство) содержит кварцевый генератор, настроенный на частоту 80 мГц, выделяемую из принимаемого сигнала. Сигнал с частотой 80 мГц, выработанный генератором, поступает по линии 124 на делитель частоты 126 деления на 4, с выхода которого этот сигнал подается на перемножители 62 и 108. Кроме того, этот выходной сигнал подается на оба процессора с тем, чтобы обеспечить тактовые импульсы (прямоугольной формы). Также этот выходной сигнал по линии 124 идет на делитель 130 частоты деления на 5, и далее, на блок 51 синхронизации. Процессор модуляции-демодуляции устанавливает любое отклонение по частоте между основной частотой входного сигнала и полученной частотой синхронизации.

Полученная в процессоре модуляции-демодуляции результирующая частота подается по линии 132 на цифроаналоговый преобразователь 134. С выхода этого преобразователя сигнал поступает по линии 136 и настраиваемый вход 138 на кварцевый генератор таким образом, чтобы изменить его частоту с целью минимизации полученного ранее сигнала с результирующей частотой. Сигнал контроля потери синхронизации подается по линии 140 на процессор 22 передачи данных, чтобы указать на момент потери синхронизации в синтезирующем устройстве.

Процессор 40 модуляции-демодуляции, как показано на фиг.2, включает в себя преобразователь 150 клавиатурной модуляции дифференциального фазового сдвига, в который данные подаются по линии 152. От преобразователя данные затем подаются на частоте 16 кГц (символов/сек) на ограничивающий фильтр 154. Выходной сигнал с фильтра 154, обозначенный позицией 156, является сигналом асинхронных данных, включающих в себя 10 сложных эталонов/символов, разделенных по времени IQ пар. Этот выходной сигнал подается на передающий блок 46 памяти последовательного обслуживания, описанный выше, где происходит преобразование асинхронных данных в синхронные. Выходной сигнал с передающего блока 46 памяти в виде 160.000 пар слов данных/сек поступает в интерполятор 48, описанный выше, который демультиплексирует пары IQ (синфазно/квадратурно) и повторно мультиплексирует IQ эталоны на частоте 1,6 мГц.

В схеме 16-разрядной модуляции двоичная последовательность входных сигналов делится на 4-х битовые символы. В схеме 16-ти разрядной модуляции 4-битовые символы определяют фазу несущей частоты в течение периода действия заданного символа. Преобразование двоичного входного сигнала в сигнал клавиатурной модуляции фазового сдвига осуществляется модулятором.

На фиг.3 показано, как последовательность эталонов (S), обозначенная позицией 160, трансформируется в последовательность эталонов (I) "синфазно" и эталонов (Q) "квадратурно" в схеме клавиатурной модуляции дифференциального фазового сдвига, входящей в состав процессора 40 модуляции-демодуляции. Символы сначала кодируются обратным преобразованием Грея, как показано на фиг.3, с помощью устройства 162 кодирования. Это делается для того, чтобы уменьшить количество ошибок в двоичном разряде, которые происходят из-за не совсем правильной выборки в демодуляторе.

Выходной сигнал с устройства 162 кодирования обратного преобразования Грея подается на фазовый квантователь 164, который определяет величину абсолютной фазы θ, воспроизводимой текущим символом. Эта величина фазы подается на дифференциальное кодирующее устройство 166, которое вычисляет значение абсолютной фазы θj’. Величина θj’ представляет собой сумму по модулю 16 текущей дифференциальной фазы θ и предыдущего значения фазы θj-j’.

θj’=(θj+θ'-j)МОД 16

Сумма по модулю 16 соответствует сумме по модулю 360 в том случае, когда происходит сложение углов.

Дифференциальная фаза θ-j’ подается на синус/косинусовые просмотровые таблицы для вычисления элементов I и Q текущего символа.

Эталоны I и Q подаются на 6-отводный ограничительный фильтр 154, показанный более подробно на фиг.4. Функция этого фильтра состоит в том, чтобы создавать завышенную форму импульса клавиатурной модуляции фазового сдвига из эталонов I и Q. Эталоны Q подаются в банк из 10- 6-отводных ограничивающих фильтров, обозначенных как hj,j (j=1-10). Аналогично, эталоны I поступают в банк из 10-фильтров, обозначенных как haj. Выходы этих 20-ти фильтров подвергаются мультиплексированной передаче с временным разделением, как это показано на единственной параллельной шине, отслеживаемой на частоте амплитудно-импульсной модуляции, которая составляет величину, равную частоте отсчета пар I, Q на входе фильтра, повторенную десять раз.

Интерполятор 48, показанный более подробно на фиг.5, содержит вход 180 и реле 182, которое подключается к программируемой логической матрице 50 при помощи линии 183. Реле 182 может переключаться со входа 180 на линию 184. В линии 183 может выборочно устанавливаться перемножитель, который может использоваться для перемножения входов (входных сигналов), поступающих по линии 183. Кроме того, может использоваться добавочно вход 187, который может подаваться от процессора модуляции-демодуляции или любого вспомогательного запоминающего устройства.

Реле 182 подключается к программируемой логической матрице 50 посредством линии 183, а линия 184 подается с запоминающего устройства для эталонов "I", обозначенного позицией 186, которое имеет вход 188 от запоминающего устройства для эталонов Q, обозначенного позицией 190. Входной сигнал на частоте 1,6 мГц предусматривается для обоих запоминающих устройств I/Q и Q/I соответственно линиями 192 и 194. Интерполятор демультиплексирует мультиплексированные эталоны I и Q на частоте 160 кГц и затем осуществляет восстановление эталонов и повторное мультиплексирование на частоте 800 кГц.

Синтезирующее устройство 72, функционально описанное выше, приводится на фиг.6, на которой показан блок 200 кварцевого генератора с частотой 80 мГц, который принимает сигналы от регулируемого входа 138. Этот вход осуществляет контроль точной частоты блока кварцевого генератора. Выходной сигнал с кварцевого генератора 200 подается по линии 202 на синтезатор 204. Этот синтезатор способен синтезировать частоты в диапазоне 438.625-439.85 мГц при соответствующей синхронизации, обеспечиваемой сигналами, поступающими по линии 202. Конкретная частота выбирается посредством сигнала на входе, поступающего по линии 128 (также показана на фиг.1).

Выходной сигнал синтезатора 204 подается по линии 206 и через фильтр 208, чтобы получить сигнал L01. Кроме того, выходной сигнал синтезатора 204 поступает по линии 210 на синхронизирующий транслятор 212. Выходной сигнал кварцевого генератора 200 поступает по линии 214 на блок 216 деления на 16, выходной сигнал которого, имеющий частоту 5 мГц, подается по линии 218 на синхронизирующий транслятор 212. Выходной сигнал по линии 214 соединяется также с эталонным выходом 221.

Синхронизирующий транслятор 212 вычитает входной сигнал с частотой 5 мГц, идущий по линии 218, из частоты сигнала, поступающего по линии 210, воспроизводя таким образом результирующую частоту, которая подается через фильтр 220 и становится сигналом L02. Полученные таким образом частоты, которые становятся сигналами L02, изменяются в диапазоне между 433.625 и 434.65 мГц, в результате чего частота сигнала L02 имеет значение всегда ниже на 5 мГц сигнала L01.

Кроме того, выходной сигнал с синтезатора 204, идущий по линии 222, и выходной сигнал с синхронизирующего транслятора 212, поступающий по линии 224, совмещаются в детекторе 226 синхронизации таким образом, чтобы в случае, если частота в линии 206 не синхронизируется с частотой в линии 202 или выходная частота синхронизирующего транслятора 212 не синхронизируется с комбинацией частот в линии 206 и в блоке 216 деления на 16, сигнал потери сигнализации направлялся бы по линии 140 (также показанной на фиг.1).

Определенная комбинация одного синтезатора 204 и блока 216 деления на 16, а также синхронизирующего транслятора 212 обеспечивает ту же самую функцию, что и два используемых ранее отдельных синтезирующих устройства, но с меньшим количеством деталей, большей стабильностью, более простыми отклонениями и др.

На фиг.7 изображена предпочтительная схема контроля интерфейса пользователя. В этом смысле процессор 22 (показан на фиг.1) вырабатывает в цифровом виде сигнал синусоидальной формы на частоте 1 кГц, который подается на кодер-декодер 20 (показан на фиг.1), где происходит преобразование этого сигнала в аналоговый, который, в свою очередь, пропускается через гибридную схему абонентского интерфейса 14 и подается в сдвоенную линию 12. Реле К (не показано на фиг.1) мгновенно включает интерфейс 10 так, чтобы он отключил схему. Любой отраженный сигнал от запертой сдвоенной линии 12 на разомкнутое реле К возвращается через гибридную схему абонентского интерфейса 14 и преобразовывается в цифровой сигнал кодером-декодером 20. Этот цифровой сигнал подается на процессор 22 передачи данных, который осуществляет сравнение отраженного сигнала с исходным и определяет, имеются ли какие-либо нежелательные сопротивления или соединения, например, на землю в линии 12.

На фиг.8 показана демодуляционная часть процессора 40 модуляции-демодуляции и выходной сигнал с частотой 400 кГц, идущий от перемножителя 108 (показан на фиг.1), подаваемый на блок 110 выборки и блокировки высокой точности, которая имеет погрешность, равную 25 нсек и менее. Выходной сигнал с этого блока подается на аналоговый/цифровой преобразователь 112. Выходной сигнал аналогово/цифрового преобразователя 112 подается по линии 116 на процессор 40 модуляции-демодуляции (все как показано на фиг.1). Выходной сигнал в линию 116 включает в себя мультиплексированные разделенные по времени эталоны I и Q (которые могут иметь определенные перекрестные искажения) в форме двух составных эталонов/символов. Указанные мультиплексированные с временным разделением эталоны I и Q подаются на демультиплексатор 290, где они демультиплексируются. Демультиплексированные эталоны I и Q поступают на эквалайзер 300, основная цель которого минимизировать (а) энергию ошибки принимаемого потока данных, (b) модифицировать энергию ошибки потока данных, задерживаемых на 0,05Т (где Т=1/16000 сек), (с) модифицировать энергию ошибки потока данных, передаваемого с опережением на 0,05 Т, (d) энергию потока данных от смежного верхнего канала (требуемая частота приема плюс 25 кГц), (е) энергию от потока данных смежного нижнего канала передачи (требуемая частота приема минус 25 кГц).

Эквалайзер представляет собой сложный 28-отводный фильтр ограничения импульсной характеристики, влияние которого определяется минимизацией вышеупомянутых целей. В этом случае пять моделирующих сигналов вырабатывается модулятором. К таким сигналам относятся: (а) сигнал заданной частоты, на которой происходит синхронизация синхроимпульсов передатчика и приемника; (b) аналогичный сигнал, но при котором синхроимпульс приемника опережает синхроимпульс передатчика на величину 0,05 Т; (с) сигнал (b), но с задержкой на 0,05 Т; (d) сигнал (а), но при котором несущая частота увеличивается на 25 кГц; и (е) сигнал (d), при котором несущая частота уменьшается на 25 кГц. В случае (d) и (е) для того, чтобы выработать модулирующий сигнал с отклонением в 25 кГц, процессор модуляции-демодуляции сдвигает коэффициенты передачи фильтра ограничения импульсной характеристики на 25 кГц.

Путем сравнения реальных входных сигналов во время представления каждого из пяти модулирующих сигналов с серией требуемых выходных сигналов получаются взвешивающие коэффициенты, которые при обработке их в эквалайзере способствуют достижению вышеупомянутых целей. Эти взвешивающие коэффициенты заносятся в запоминающее устройство 32 с произвольной выборкой.

Скомпенсированные эталоны I и Q подаются на блок 302, который вырабатывает сигнал, являющийся арктангенсом отношения выровненных эталонов I и Q. Этот выходной сигнал, обозначенный позицией 304, отображает фазу принимаемого сигнала.

Скомпенсированные эталоны I и Q также одновременно подаются на блок 306 отслеживания частоты, показанный более подробно на фиг.9. Эталоны I и Q суммируются для формирования более низкой боковой полосы частот 308 (как показано на фиг.9) и одновременно вырабатывается разностный сигнал между эталонами I и Q для формирования верхней полосы (боковой) частот 310. Расчет величины частоты выполняется затем как в нижней боковой полосе, так и в верхней боковой полосе, что обозначается соответственно позициями 312 и 314. Вычисление разностного значения между величинами производится на устройстве 316. Этот разностный сигнал находится в линии 318 и представляет собой ошибку частоты.

Как показано на фиг.8, выход 304 блока 302 арктангенса подключается к блоку 320 синхронизации символов и автоматического контроля частоты (который показан более подробно на фиг.10). Величина фазовой коррекции, обозначенная на фиг.10 как 322, вычитается из величины выделенной фазы 304, в результате чего в линию 324 подается скорректированная фаза. Скорректированная фаза 324 подается на блок 326 обнаружения символов, который выделяет текущий символ в единицах величины фазы и квантует фазу с приращением в 22,5 градусов. Квантованная фаза 328 вычитается из скорректированной фазы 324 в блоке 330. В результате в линии 332 появляется сигнал фазовой ошибки. Этот сигнал ошибки поступает в блок 334, который рассчитывает величину фазовой коррекции, подаваемую в линию 336, и величину частотной коррекции, подаваемую в линию 338. Этот сигнал частотной коррекции подается к кварцевому генератору по линии 132, изображенной на фиг.1.

Сигнал 332 фазовой ошибки подается по линии 340 на блок 342 синхронизации символов, который также получает выходной сигнал с блока 326 обнаружения символов по линии 344. Блок 342 синхронизации символов использует алгоритм, посредством которого отслеживается фаза вдоль множества заранее определенных символов, начиная с начальной фазы первого и до фазы последнего символа, а затем определяет угловой коэффициент. Этот блок, исходя из зависимости фазы от времени, пытается определить реально существующие нулевые пересечения и сравнить с теми, которые могут произойти, после чего рассчитывается временная регулировка, необходимая для компенсации полученной разницы. Синхронизация символа должна будет настраиваться в начале следующей области. Блок 342 синхронизации символов обеспечивает выходной сигнал 346, который подается на блок 51 синхронизации (показан на фиг.1).

Сигнал 338 коррекции частоты с блока 342 синхронизации символов и автоматического контроля частоты подается на блок 348 весовых коэффициентов (как показано на фиг.8), где происходит взвешивание данного сигнала. Выходной сигнал 350 с блока 348 подается в суммирующий блок 352, где сигнал 350 суммируется с выходным сигналом 318 с блока 306 для того, чтобы обеспечить выходной сигнал 354, который подается на цифроаналоговый преобразователь 134, Выходной сигнал с цифроаналогового преобразователя изображается на фиг.1 поступающим на синтезирующее устройство 72.

Несмотря на то, что данное изобретение, как это описано выше, обеспечивают различные отдельные элементы, допускается включить все функции, выполняемые этими отдельными элементами, такие как, например, полноскоростная программируемая постоянная память 44, передающий блок 46 памяти последовательного обслуживания, интерполятор 48 и программируемая логическая матрица 50 внутрь процессора модуляции-демодуляции со значительно расширенной емкостью памяти. Это также может касаться таких элементов, как блок 91 синхронизации групп данных, формирователь 58 бланкирующего сигнала, устройство 51 синхронизации, делителей частоты 126 и 130 соответственно на 4 и на 5 и некоторых или всех синтезирующих устройств 72. Кроме того, процессор 22 передачи данных и процессор 40 модуляции-демодуляции могут быть также совмещены в одном блоке, который также может включать в себя кодер-декодер и универсальный асинхронный приемопередатчик.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОБРАБОТКИ СИГНАЛОВ СВЯЗИ В АБОНЕНТСКОМ ПУНКТЕ БЕСПРОВОДНОЙ СИСТЕМЫ ЭЛЕКТРОСВЯЗИ | 1990 |

|

RU2159007C2 |

| РАДИОТЕЛЕФОННАЯ СИСТЕМА ДЛЯ ГРУПП УДАЛЕННЫХ АБОНЕНТОВ | 2004 |

|

RU2341038C2 |

| АБОНЕНТСКИЙ ПУНКТ В СИСТЕМЕ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СВЯЗИ | 1990 |

|

RU2154360C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ПОМОЩЬЮ ШУМОПОДОБНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2007 |

|

RU2362273C2 |

| АБОНЕНТСКИЙ ПУНКТ В АБОНЕНТСКОЙ СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 1990 |

|

RU2138122C1 |

| РАДИОТЕЛЕФОННАЯ СИСТЕМА ДЛЯ ГРУПП УДАЛЕННЫХ АБОНЕНТОВ | 1994 |

|

RU2246185C2 |

| СЕТЬ БЕСПРОВОДНОЙ СВЯЗИ С РАСШИРЕННОЙ ЗОНОЙ ПОКРЫТИЯ | 2006 |

|

RU2380823C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ГИБРИДНОЙ КОРРЕКЦИИ С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ | 2005 |

|

RU2407197C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ И ДЛЯ ОЦЕНКИ ПАРАМЕТРОВ КАНАЛА | 2004 |

|

RU2271070C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РЕЖИМА ПЕРЕДАЧИ И СИНХРОНИЗАЦИИ СИГНАЛА ЦИФРОВОГО АУДИОВЕЩАНИЯ | 2000 |

|

RU2248673C2 |

Изобретение относится к абонентскому блоку, входящему в состав беспроводной цифровой телефонной системы. Абонентский блок содержит процессор передачи данных, соединенный через последовательно соединенные кодер-декодер и интерфейс с абонентским аппаратом, а также с информационным входом процессора модуляции-демодуляции, информационный выход которого через последовательно соединенные передающий блок памяти, интерполятор, программирующую логическую матрицу и цифровой/аналоговый преобразователь соединен с первым входом перемножителя, выход которого соединен с антенной через передающий блок, имеющий переключатель, который соединен с приемным блоком, выход которого подсоединен к информационному входу процессора модуляции-демодуляции через последовательно соединенные блок выборки, аналоговый/цифровой преобразователь и приемный блок памяти, а также задающий генератор, подсоединенный к передающему и приемному блокам, и последовательно соединенные делитель частоты, блок синхронизации и формирователь бланкирующего сигнала, причем вход делителя частоты соединен с задающим генератором, выход формирователя бланкирующего сигнала соединен со вторым входом перемножителя, а выход процессора модуляции-демодуляции соединен с другим входом блока синхронизации. 1 с. и 3 з.п. ф-лы, 10 ил.

| DE 3609394 A1, 25.09.1986 | |||

| US 4627046, 02.12.1986 | |||

| Устройство для передачи и приема сигналов с фазовой манипуляцией | 1986 |

|

SU1363519A1 |

| ПНЕВМАТИЧЕСКИЙ РЕГУЛЯТОР ТЕМПЕРАТУРЫ | 0 |

|

SU206203A1 |

| Горный компас | 0 |

|

SU81A1 |

| Многоканальный модулятор-демодулятор с фазоразностной модуляцией | 1985 |

|

SU1282350A1 |

Авторы

Даты

2004-06-20—Публикация

1988-07-08—Подача