Изобретение относится к электротехнике и может быть использовано в устройствах релейной защиты в качестве реле регулирования частоты и фазы генератора при его подключении в сеть.

Известно устройство, содержащее последовательно соединенные генератор тактовых импульсов, двоичный счетчик, дешифратор, формирователь импульсов и исполнительный элемент, выполненный в виде транзистора [1].

Недостатком устройства является относительно узкие функциональные возможности, не позволяющие использовать его в качестве релейного регулятора.

Наиболее близким по технической сущности к предлагаемому, является устройство, содержащее частотный дискриминатор, первый и второй входы которого являются входами, соответственно, частоты сети и частоты генератора, а выход - соединен с входом компаратора, первый и второй выходы которого соединены с входами соответственно первого и второго элементов И, и с входом генератора импульсов, выход которого соединен с входом реле частоты, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом автономного генератора импульсов, а выход - соединен со вторыми входами первого и второго элементов И [2].

Недостатком наиболее близкого технического решения является относительно узкие функциональные возможности, поскольку оно вырабатывает сигнал подстройки частоты генератора, но не позволяет произвести подстройку фазы генератора, когда частота генератора согласована с частотой сети.

Техническим результатом изобретения является расширение функциональных возможностей.

Этот технический результат достигается тем, что в устройство, содержащее первый компаратор, первый, второй и третий элементы И, генератор импульсов и частотный дискриминатор, первый и второй входы которого являются входами сигналов соответственно генератора и сети, введены последовательно соединенные аналого-цифровой преобразователь, вход которого соединен с выходом частотного дискриминатора, первый нерекурсивный фильтр, тактовый вход которого соединен с тактовым входом аналого-цифрового преобразователя и с выходом генератора импульсов, и первый двухпороговый компаратор, выход “больше” которого соединен с первым входом первого элемента И, выход которого является выходом регулирования частоты генератора в сторону понижения, а выход “меньше” - соединен с первым входом второго элемента И, выход которого является выходом регулирования частоты генератора в сторону повышения, четвертый элемент И, первый и второй инверсные входы которого соединены соответственно с выходами первого и второго элементов И, делитель частоты импульсов, вход которого соединен с выходом генератора импульсов, а выход - соединен со вторыми входами первого и второго элементов И, одновибратор, выход которого соединен с входом запуска генератора импульсов, второй компаратор, вход которого соединен с входом сигнала сети, первый и второй счетчики импульсов, пятый элемент И, первый вход которого соединен с первым входом третьего элемента И и с выходом первого компаратора, вход которого соединен с входом сигнала генератора, выход третьего элемента И соединен со счетным входом второго счетчика импульсов, второй вход пятого элемента И соединен со вторым входом третьего элемента И и с выходом генератора импульсов, а выход - соединен со счетным входом первого счетчика импульсов, второй и третий нерекурсивные фильтры, информационные входы которых соединены с выходами соответственно первого и второго счетчиков импульсов, блок вычитания, первый и второй входы которого соединены с выходами соответственно второго и третьего нерекурсивных фильтров, второй двухпороговый компаратор, вход которого соединен с выходом блока вычитания, шестой и седьмой элементы И, первые входы которых соединены соответственно с выходом “больше” и с выходом “меньше” второго двухпорогового компаратора, вторые входы объединены и соединены с выходом делителя частоты импульсов, третьи входы объединены и соединены с выходом четвертого элемента И, а выходы являются выходами уменьшения и увеличения фазового сдвига сигнала генератора соответственно, последовательно соединенные формирователь импульсов, вход которого соединен с выходом второго компаратора, блок задержки и первый формирователь короткого импульса, выход которого соединен с тактовым входом второго нерекурсивного фильтра и с входом установки в ноль первого счетчика импульсов, а также второй формирователь короткого импульса, вход которого соединен с выходом формирователя импульса, а выход - соединен с тактовым входом третьего нерекурсивного фильтра и с входом установки в ноль второго счетчика импульсов, при этом выходы формирователя импульсов и блока задержки соединены с третьими входами третьего и пятого элементов И соответственно.

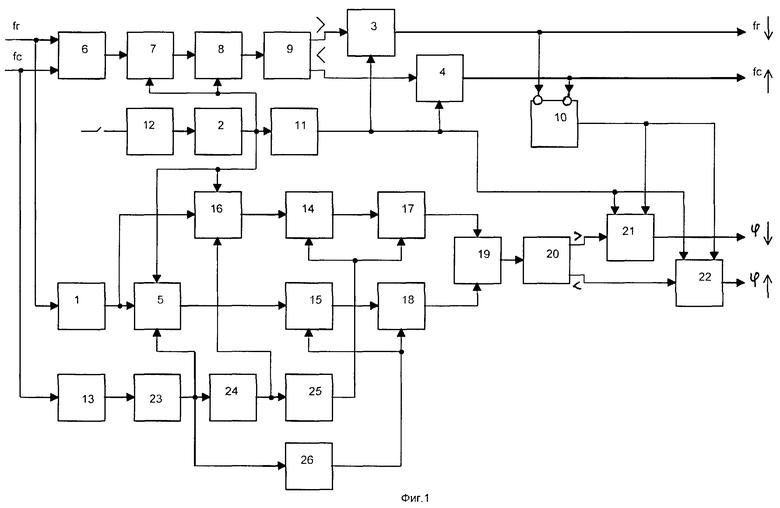

На фиг.1 представлена электрическая структурная схема релейного регулятора; на фиг.2 - нерекурсивного фильтра.

Релейный регулятор (фиг.1) содержит первый компаратор 1, генератор 2 импульсов, первый 3, второй 4 и третий 5 элементы И, частотный дискриминатор 6, первый и второй входы которого являются входами сигналов соответственно генератора и сети, последовательно соединенные аналого-цифровой преобразователь (АЦП) 7, вход которого соединен с выходом частотного дискриминатора 6, первый нерекурсивный фильтр 8, тактовый вход которого соединен с тактовым входом аналого-цифрового преобразователя 7 и с выходом генератора 2 импульсов, и первый двухпороговый компаратор 9, выход “больше” которого соединен с первым входом первого элемента И 3, выход которого является выходом регулирования частоты генератора в сторону понижения, а выход “меньше” - соединен с первым входом второго элемента И 4, выход которого является выходом регулирования частоты генератора в сторону повышения, четвертый элемент И 10, первый и второй инверсные входы которого соединены соответственно с выходами первого 3 и второго 4 элементов И, делитель 11 частоты импульсов, вход которого соединен с выходом генератора 2 импульсов, а выход - соединен со вторыми входами первого 3 и второго 4 элементов И, одновибратор 12, выход которого соединен с входом запуска генератора 2 импульсов, последовательно соединенные второй компаратор 13, вход которого соединен с входом сигнала сети, первый 14 и второй 15 счетчики импульсов, пятый элемент И 16, первый вход которого соединен с первым входом третьего элемента И 5 и с выходом первого компаратора 1, вход которого соединен с входом сигнала генератора, выход третьего элемента И 5 соединен со счетным входом второго счетчика 15 импульсов, второй вход пятого элемента И 16 соединен со вторым входом третьего элемента И 5 и с выходом генератора 2 импульсов, а выход - соединен со счетным входом первого счетчика 14 импульсов, второй 17 и третий 18 нерекурсивные фильтры, информационные входы которых соединены с выходами соответственно первого 14 и второго 15 счетчиков импульсов, блок 19 вычитания, первый и второй входы которого соединены с выходами соответственно второго 17 и третьего 18 нерекурсивных фильтров, второй двухпороговый компаратор 20, вход которого соединен с выходом блока 19 вычитания, шестой 21 и седьмой 22 элементы И, первые входы которых соединены соответственно с выходом “больше” и с выходом “меньше” второго двухпорогового компаратора 20, вторые входы объединены и соединены с выходом делителя 11 частоты импульсов, третьи входы объединены и соединены с выходом четвертого элемента И 10, а выходы - являются выходами уменьшения и увеличения фазового сдвига сигнала генератора соответственно, последовательно соединенные формирователь 23 импульсов, вход которого соединен с выходом второго компаратора 13, блок 24 задержки и первый формирователь 25 короткого импульса, выход которого соединен с тактовым входом второго нерекурсивного фильтра 17 и с входом установки в ноль первого счетчика 14 импульсов, а также второй формирователь 26 короткого импульса, вход которого соединен с выходом формирователя 23 импульса, а выход - соединен с тактовым входом третьего нерекурсивного фильтра 18 и с входом установки в ноль второго счетчика 15 импульсов, при этом выход формирователя 23 импульсов и блока 24 задержки соединены с третьими входами соответственно третьего 5 и пятого 16 элементов И.

Частотный дискриминатор 6 может быть выполнен как в устройстве-прототипе и формировать сигнал, пропорциональный разности частот генератора и сети, поступающих на его входы. Остальные блоки являются стандартными блоками электротехники. Цепи питания элементов на чертеже не показаны как несущественные в рамках данной заявки. Кроме того, предполагается, что, как и в устройстве-прототипе, регулирование генератора производится по двум регулирующим входам, один из которых по импульсному сигналу работает на понижение частоты, а другой по аналогичному импульсному сигналу - на повышение частоты. Аналогичное регулирование предполагается и при регулировке фазы генератора.

Первый 8, второй 17 и третий 18 нерекурсивные фильтры могут быть выполнены в виде стандартного цифрового (фиг.2) и содержать, например, последовательно соединенные ячейки 27-1...27-к, вход первой из которых является информационным входом фильтра, выходы которых через соответствующий ему умножитель 28-1...28-к на величину 1/к, где к - число ячеек фильтра, соединены с входом сумматора 28, на выходе которого, являющемся выходом фильтра, формируется средняя величина поступивших отсчетов.

Работает реле регулирования частоты следующим образом.

Включение реле производится путем подачи питания на одновибратор 17, который запускает генератор 2 импульсов.

Сигналы с частотой сети и генератора поступают на вход частотного дискриминатора 6, на выходе которого формируется сигнал, пропорциональный отклонению частоты генератора от частоты сети. Этот сигнал “оцифровывается” в АЦП 7 и усредняется в первом нерекурсивном фильтре 8, после чего подается на вход первого двухпорогового компаратора 9. При превышении его входного сигнала верхнего порога, что свидетельствует о недопустимом превышении величины отклонения частоты генератора от частоты сети, на его выходе “больше” формируется уровень логической единицы, поэтому на выход снижения частоты генератора через первый элемент И 3 поступают импульсы регулирования от делителя 11 частоты импульсов. Аналогично при недопустимо большом отклонении частоты генератора в меньшую сторону сигнал логической единицы формируется на выходе “меньше” первого двухпорогового компаратора 9, что вызывает появление импульсов делителя частоты 11 на выходе уменьшения частоты генератора, поступающие через второй элемент И 4.

Если отклонение частоты генератора от частоты сети находится в допустимых пределах, то на выходе четвертого элемента И 10 формируется уровень логической единицы, который поступает на соответствующие входы шестого 21 и седьмого 22 элементов И, что позволяет, при необходимости, регулировать фазу генератора относительно фазы сети. Для этого сигнал генератора и сигнал сети подаются на входы соответственно первого 1 и второго 13 компараторов с нулевыми пороговыми уровнями, что позволяет преобразовать входные синусоидальные сигналы в импульсные сигналы с длительностью импульсов в половину периода частоты. Формирователь 23 по переднему фронту импульса сигнала сети формирует сигнал в четверть периода сигнала сети, который поступает на вход блока 24 задержки, на выходе которого также формируется сигнал в четверть периода сигнала сети, но сдвинутый на четверть периода. Поэтому через третий элемент И 5 на вход второго счетчика 15 будут проходить импульсы генератора 2 в пределах времени совпадения импульса длительностью в половину периода сигнала генератора и первой половины полупериода сигнала сети, а через пятый элемент И 16 на вход первого счетчика 14 будут проходить импульсы генератора 2 в пределах времени совпадения импульса длительностью в половину периода сигнала генератора и второй половины полупериода сигнала сети. По передним фронтам сигнала формирователя 23 и блока 24 задержки второй формирователь 26 и первый формирователь 25 соответственно формируют короткие импульсы, по которым сигналы из второго счетчика 15 переписываются в третий нерекурсивный фильтр 18, а из первого счетчика 14 - во второй нерекурсивный фильтр 17. После переписывания содержимое счетчиков обнуляется, что обеспечивается или работой входов их обнуления и входов управления нерекурсивных фильтров по разным фронтам коротких импульсов или путем включения на входах обнуления счетчиков малых задержек на время переходных процессов в нерекурсивных фильтрах. Следовательно, на выходе блока 19 вычитания формируется сигнал, пропорциональный сдвигу фазы сигнала генератора и сигнала сети. Второй двухпороговый компаратор 20 работает аналогично первому, поэтому при формировании на его выходе “больше” через шестой элемент И 21 будут поступать импульсы с выхода делителя 11 на вход сдвига фазы генератора в сторону замедления, относительно фазы сигнала сети, а при формировании на его выходе “меньше” через седьмой элемент И 22 будут поступать импульсы с выхода делителя 11 на вход сдвига фазы генератора в сторону ускорения.

Таким образом, предложенное устройство обладает более широкими функциональными возможностями, поскольку оно вырабатывает сигналы как подстройки частоты генератора, так и подстройку фазы генератора, в случае когда частота генератора согласована с частотой сети.

Источники информации

1. Электротехнический справочник, в 4-х томах, т.2: Электротехнические изделия и устройства /Под общ. ред. В.Г.Герасимова и др. - М.: Издательство МЭИ, 1998, с.390, рис.35.10.

2. Андреев В.А. Релейная защита и автоматика систем электроснабжения. - М.: Высшая школа, 1991, с.356, рис.12.17 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ РАЗНОСТИ ФАЗ | 2002 |

|

RU2222087C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2002 |

|

RU2220468C1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208865C1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2220472C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2208866C1 |

| РЕЛЕ СИНХРОНИЗАЦИИ | 2002 |

|

RU2222068C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2237312C1 |

| РЕЛЕ РЕГУЛИРОВАНИЯ ЧАСТОТЫ | 2002 |

|

RU2231913C2 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2228559C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2002 |

|

RU2220471C1 |

Изобретение относится к области электротехники и может быть использовано для регулирования частоты и фазы генератора при его включении в сеть. Технический результат заключается в расширении функциональных возможностей. Для этого устройство содержит два компаратора, два двухпороговых компаратора, генератор импульсов, семь элементов И, частотный дискриминатор, одновибратор, делитель частоты импульсов, блок вычитания, три нерекурсивных фильтра, два счетчика импульсов, аналого-цифровой преобразователь, формирователь по переднему фронту импульса сигнала сети, два формирователя коротких импульсов и блок задержки. 2 ил.

Релейный регулятор, содержащий первый компаратор, первый, второй и третий элементы И, генератор импульсов и частотный дискриминатор, первый и второй входы которого являются входами сигналов, соответственно, генератора и сети, отличающийся тем, что введены последовательно соединенные аналого-цифровой преобразователь, вход которого соединен с выходом частотного дискриминатора, первый нерекурсивный фильтр, тактовый вход которого соединен с тактовым входом аналого-цифрового преобразователя и с выходом генератора импульсов, и первый двухпороговый компаратор, выход "больше" которого соединен с первым входом первого элемента И, выход которого является выходом регулирования частоты генератора в сторону понижения, а выход "меньше" соединен с первым входом второго элемента И, выход которого является выходом регулирования частоты генератора в сторону повышения, четвертый элемент И, первый и второй инверсные входы которого соединены, соответственно, с выходами первого и второго элементов И, делитель частоты импульсов, вход которого соединен с выходом генератора импульсов, а выход соединен со вторыми входами первого и второго элементов И, одновибратор, выход которого соединен с входом запуска генератора импульсов, второй компаратор, вход которого соединен с входом сигнала сети, первый и второй счетчики импульсов, пятый элемент И, первый вход которого соединен с первым входом третьего элемента И и с выходом первого компаратора, вход которого соединен с входом сигнала генератора, выход третьего элемента И соединен со счетным входом второго счетчика импульсов, второй вход пятого элемента И соединен со вторым входом третьего элемента И и с выходом генератора импульсов, а выход соединен со счетным входом первого счетчика импульсов, второй и третий нерекурсивные фильтры, информационные входы которых соединены с выходами соответственно первого и второго счетчиков импульсов, блок вычитания, первый и второй входы которого соединены с выходами соответственно второго и третьего нерекурсивных фильтров, второй двухпороговый компаратор, вход которого соединен с выходом блока вычитания, шестой и седьмой элементы И, первые входы которых соединены соответственно с выходом "больше" и с выходом "меньше" второго двухпорогового компаратора, вторые входы объединены и соединены с выходом делителя частоты импульсов, третьи входы объединены и соединены с выходом четвертого элемента И, а выходы являются выходами уменьшения и увеличения фазового сдвига сигнала генератора, соответственно, последовательно соединенные формирователь по переднему фронту импульса сигнала сети, вход которого соединен с выходом второго компаратора, блок задержки и первый формирователь короткого импульса, выход которого соединен с тактовым входом второго нерекурсивного фильтра и с входом установки в ноль первого счетчика импульсов, а также второй формирователь короткого импульса, вход которого соединен с выходом формирователя по переднему фронту импульса сигнала сети, а выход соединен с тактовым входом третьего нерекурсивного фильтра и с входом установки в ноль второго счетчика импульсов, при этом выходы формирователя по переднему фронту импульса сигнала сети и блока задержки соединены с третьими входами третьего и пятого элементов И соответственно.

| АНДРЕЕВ В.А | |||

| Релейная защита и автоматика систем электроснабжения | |||

| - М.: Высшая школа, 1991, с.356 | |||

| АНАЛОГОВЫЙ РЕГУЛЯТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2006176C1 |

| СПОСОБ ФОРМИРОВАНИЯ УПРАВЛЯЮЩЕГО СИГНАЛА В РЕЛЕЙНЫХ СИСТЕМАХ И РЕЛЕЙНЫЙ РЕГУЛЯТОР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 1998 |

|

RU2141124C1 |

| Релейная система автоматического регулирования | 1980 |

|

SU894668A1 |

| US 3691452, 12.09.1972. | |||

Авторы

Даты

2004-06-27—Публикация

2002-09-04—Подача