Область техники

Настоящее изобретение относится к кодированию. Более конкретно, настоящее изобретение относится к новому и улучшенному способу декодирования методом максимальной апостериорной вероятности (МАП декодирование).

Предшествующий уровень техники

Турбокодирование представляет важное достижение в области прямого исправления ошибок (ПИО). Существует много вариантов турбокодирования, но в большинстве случаев используются множество этапов кодирования, разделенных этапами перемежения, в комбинации с итеративным декодированием. Такое объединение обеспечивает ранее недостижимые характеристики в отношении допустимого шума в системе связи. То есть, турбокодирование позволяет осуществлять связь при уровнях Еb/N0, которые ранее были неприемлемыми при использовании существующих методов прямого исправления ошибок.

Многие системы используют методы прямого исправления ошибок и поэтому использование турбокодирования было бы полезным. Например, турбокодирование могло бы улучшить эффективность беспроводных спутниковых линий связи, где ограниченная мощность передачи спутника по нисходящей (прямой) линии связи требует от систем приема, чтобы они могли работать при низких уровнях Еb/N0. Использование турбокодов в беспроводной спутниковой линии связи могло бы уменьшить размер антенны для системы цифрового телевидения (ЦТВ) или в альтернативном варианте, осуществлять передачу большего объема данных в пределах заданной полосы частот.

В цифровых беспроводных телекоммуникационных системах, таких как цифровые сотовые системы и телефонные системы PCS (персональная система связи), также используется прямое исправление ошибок. Например, стандарт IS-95 на интерфейс радиосвязи и производные от него стандарты, такие как IS-95B, определяют цифровую беспроводную систему связи, которая использует сверточное кодирование для получения выигрыша за счет кодирования, чтобы увеличить пропускную способность системы. Система и способ для обработки РЧ сигналов по существу в соответствии с использованием стандарта IS-95 описаны в патенте США №5103459 на “Систему и способ формирования сигналов в сотовой телефонной системе множественного доступа с кодовым разделением каналов”, переуступленном правоприемнику настоящего изобретения и включенном в настоящее описание путем ссылки.

Поскольку цифровая беспроводная система связи, подобная системе стандарта IS-95, в первую очередь используется для мобильной связи, то важно иметь устройства, которые минимизируют потребляемую мощность и имеют малые размеры и вес. Обычно это требует разработки полупроводниковой интегральной микросхемы (“чипа”) для выполнения большей части или всей необходимой обработки данных. Несмотря на относительную сложность сверточного кодирования схемы, необходимые для выполнения сверточного кодирования и декодирования, могут быть реализованы на одном чипе вместе с любыми другими необходимыми схемами.

Турбокодирование (особенно операция декодирования) значительно сложнее, чем сверточное кодирование (и декодирование). Тем не менее, было бы желательным включить турбокодирование в цифровые беспроводные телекоммуникационные системы, включая мобильные цифровые и спутниковые системы связи. Таким образом, настоящее изобретение направлено на увеличение скорости выполнения некоторых операций декодирования, для упрощения использования турбокодирования в различных системах.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Настоящее изобретение представляет собой новый и улучшенный способ декодирования с конкретным применением к турбокодированию или итеративным методам кодирования. В соответствии с одним из вариантов изобретения система декодирования содержит ОЗУ канального обращенного перемежителя для запоминания блока символьных оценок, набор из S вычислителей метрик состояния, каждый из которых предназначен для формирования множества вычислений метрик состояния, набор из S+1 ОЗУ окон, причем из ОЗУ канального обращенного перемежителя символьные оценки в виде оценки системного символа и оценки двух символов четности для каждого бита данных, соответствующего блоку канального перемежителя, считывают и записывают в последовательном порядке в адресной области S+1 окон ОЗУ, причем в любой данный момент времени запись производится только в одно окно ОЗУ, а из остальных S окон ОЗУ считывают символьные оценки на S вычислителей метрик состояния декодера максимальной апостериорной вероятности через мультиплексоры.

При этом S может быть равно 3, а объем памяти ОЗУ окон значительно меньше, чем объем памяти ОЗУ канального обращенного перемежителя.

Предпочтительно вычислители метрик состояния обрабатывают данные по окнам, с объемом данных, равным или меньшим, чем объем памяти ОЗУ окна.

Кроме того, в соответствии с изобретением декодер содержит память канального перемежителя для запоминания блока принятых оценок канального перемежителя, процессор декодера для декодирования принятых оценок, буфер декодера для одновременного считывания первого множества принятых оценок и второго множества принятых оценок в упомянутый процессор декодера и записи третьего множества принятых оценок из памяти канального перемежителя.

При этом буфер декодера дополнительно предназначен для одновременного считывания четвертого множества принятых оценок.

Кроме того, процессор декодера представляет собой процессор декодера максимальной априорной вероятности.

Процессор декодера предпочтительно содержит прямой вычислитель метрик состояния для формирования метрик состояния в прямом направлении в ответ на первое множество принятых оценок, обратный вычислитель метрик состояния для формирования метрик состояний в обратном направлении в ответ на второе множество принятых оценок.

Кроме того, процессор декодера может дополнительно содержать прямой вычислитель метрик состояния для формирования метрик состояний в прямом направлении в ответ на первое множество принятых оценок, первый обратный вычислитель метрик состояния для формирования метрик состояний в обратном направлении в ответ на второе множество принятых оценок и второй обратный вычислитель метрик состояния для формирования метрик состояний в обратном направлении в ответ на четвертое множество принятых оценок.

При этом буфер декодера содержит первую память для считывания записи принятых выборок, вторую память для считывания и записи принятых выборок и третью память для считывания и записи принятых выборок.

Также в соответствии с изобретением способ декодирования данных включает этапы, при которых осуществляют подачу на первый вычислитель метрик состояния первого множества принятых оценок для формирования значения инициализации, подачу на второй вычислитель метрик состояния второго множества принятых оценок для формирования первого множества метрик состояний, подачу третьего вычислителя метрик состояния третьего множества принятых оценок для формирования второго множества метрик состояний, запись четвертого множества принятых оценок в буфер данных, при этом вышеуказанные этапы выполняют одновременно.

Второе множество метрик состояний предпочтительно формируют с использованием ранее вычисленных значений инициализации и обрабатывают с ранее вычисленным множеством метрик состояний для формирования оценок данных.

Кроме того, способ дополнительно может включать этапы подачи на первый вычислитель метрик состояния второго множества принятых оценок, и подачи на третий вычислитель метрик состояния первого множества принятых оценок.

В другом варианте осуществления изобретения способ декодирования включает этапы, при которых осуществляют (а) выполнение первого декодирования первого окна в первом направлении и одновременно выполнение второго декодирования во втором окне во втором направлении, (b) запоминание результатов первого декодирования, (с) инициализацию третьего декодирования, используя результат второго декодирования, (d) выполнение третьего декодирования в первом окне во втором направлении и вычисление значений логарифма отношения правдоподобия с использованием метрик, вычисленных при третьем декодировании и упомянутых результатов первого декодирования, и одновременно с этапом (d) выполнение четвертого декодирования, пятого декодирования другого окна в первом направлении, а также шестого декодирования во втором направлении в новом окне, (е) запоминание результатов пятого декодирования, использование результатов шестого декодирования для значения инициализации, при этом второе направление предпочтительно является противоположным первому направлению.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Признаки, задачи и преимущества настоящего изобретения поясняются в подробном описании, изложенном ниже, со ссылками на чертежи, на которых одни и те же позиции обозначают одинаковые элементы соответственно на всех чертежах и на которых показано следующее:

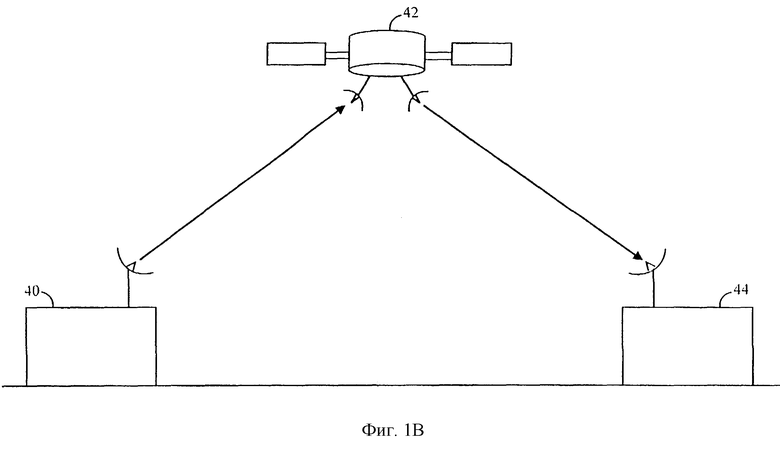

фиг.1А и 1В - блок-схемы беспроводных систем связи;

фиг.2 - блок-схема передающей системы;

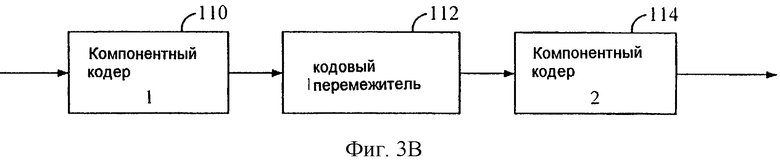

фиг.3А и 3В - схемы турбокодеров;

фиг.4 - блок-схема системы приема и обработки сигналов;

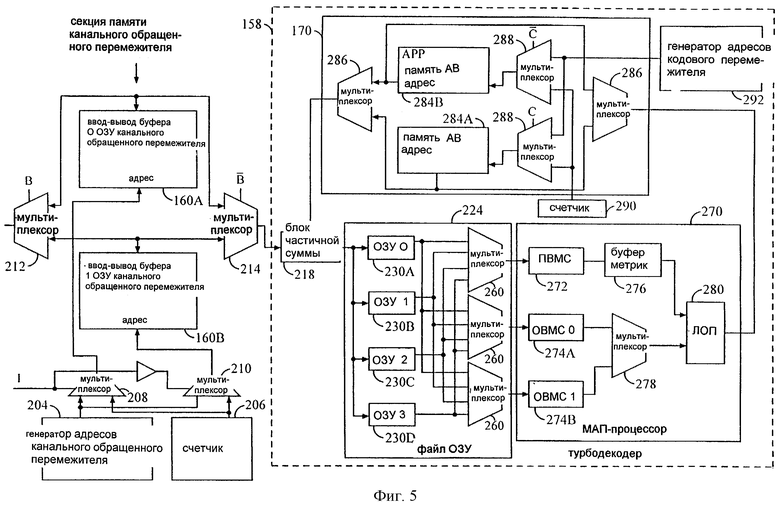

фиг.5 - блок-схема декодера и секции канального обращенного перемежителя;

фиг.6 - блок-схема выполнения этапов декодирования.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Настоящее изобретение представляет собой новый и улучшенный способ выполнения турбокодирования. Один из вариантов осуществления изобретения описан в контексте системы цифровой сотовой телефонной связи. Несмотря на то, что использование изобретения в этом контексте является предпочтительным, другие варианты осуществления изобретения могут быть реализованы в различных условиях, конфигурациях, в системах цифровой передачи данных, включая системы спутниковой связи и проводные системы связи, такие как цифровые кабельные и телефонные системы.

В принципе, различные системы, описанные здесь, могут быть выполнены с использованием программно-управляемых процессоров, интегральных схем или дискретной логики, однако предпочтительной является реализация в виде интегральной схемы. Данные, указания, команды, информация, сигналы, символы и чипы, которые упоминаются в описании, представлены с помощью напряжений, токов, электромагнитных волн, магнитных полей или частиц, оптических полей или частиц или их комбинаций. Кроме того, блоки, показанные на каждой блок-схеме, могут представлять либо аппаратные средства, либо этапы способа.

На фиг.1А представлена упрощенная схема сотовой телефонной системы, выполненной в соответствии с одним из вариантов осуществления изобретения. Для осуществления телефонных вызовов или других операций абонентские блоки 10 взаимодействуют с базовыми станциями 12 посредством РЧ сигналов. Базовые станции 12 взаимодействуют с коммутируемой телефонной сетью общего пользования через контроллер 14 базовых станций (КБС).

Фиг.1В - упрощенная схема системы спутниковой связи, выполненной в соответствии с другим вариантом осуществления изобретения. Наземная станция 40 обратной (восходящей) линии связи передает РЧ сигналы, содержащие информацию, такую как телевизионные программы, на спутник 42. Спутник 42 передает РЧ сигналы назад на Землю, где приемник 44 преобразует принимаемые РЧ сигналы в цифровые данные.

Фиг.2 - блок-схема примерной конфигурации передающей системы, выполненной в соответствии с одним из вариантов осуществления настоящего изобретения. Эта система может быть использована в абонентском устройстве 10, базовой станции 12 или наземной станции 40 обратной линии связи, а также в любой другой системе, которая генерирует цифровые сигналы для передачи. Показанная на чертеже обработка передаваемых данных представляет только один из возможных вариантов осуществления изобретения, поскольку многие другие схемы обработки передаваемых данных могут быть реализованы для получения преимуществ от использования различных вариантов осуществления изобретения.

Данные 70 подаются на генератор 72 циклического избыточного кода (ЦИК), который формирует данные контрольной суммы ЦИК для каждого предварительно определенного объема принятых данных. Полученные в результате блоки данных подаются на турбокодер 76, который генерирует кодовые символы, которые подаются на канальный перемежитель 78. Кодовые символы обычно включают повторно переданные исходные данные (системный символ) и один или несколько символов четности.

Число символов четности, передаваемых для каждого системного символа, зависит от скорости кодирования. Для скорости кодирования _ один символ четности передается для каждого системного символа, для получения в итоге двух символов, генерируемых для каждого принятого бита данных (включая ЦИК). Для турбокодера со скоростью кодирования 1/3 два символа четности генерируются для каждого системного символа, для получения в итоге трех символов, генерируемых для каждого принятого бита данных.

Кодовые символы из турбокодера 76 подаются на канальный перемежитель 78. Канальный перемежитель 78 выполняет перемежение принимаемых блоков символов и выдает перемеженные символы в блок 80 отображения. Обычно канальный перемежитель 78 выполняет блочное перемежение или битовое реверсивное перемежение. По существу и все другие типы перемежителей могут использоваться в качестве канального перемежителя.

Блок 80 отображения принимает перемеженные кодовые символы и генерируют символьные слова определенной битовой длины на основе заданной схемы отображения данных. Затем символьные слова подаются на модулятор 82, который генерирует модулированные колебания на основе принятого символьного слова. Обычные методы модуляции включают квадратурную фазовую манипуляцию (КФМн), 8-уровневую фазовую манипуляцию (ФМн) и 16-уровневую квадратурную амплитудную модуляцию (КАМ), хотя могут использоваться различные другие схемы модуляции. Модулированное колебание затем преобразуется по частоте для передачи на РЧ.

Фиг.3А - блок-схема турбокодера, выполненного в соответствии с первым вариантом осуществления изобретения. В этом первом варианте турбокодер выполнен в виде турбокодера с параллельно соединенными каскадами. В этом варианте турбокодера 76 компонентный кодер 90 и кодовый перемежитель 92 принимают данные из генератора 72 ЦИК, который, как описано выше, выдает биты входных данных и биты контрольной суммы ЦИК.

Компонентный кодер 90 также генерирует хвостовые биты для обеспечения известного состояния в конце каждого кадра.

Как известно, кодовый перемежитель 92 для наилучшей эффективности должен представлять собой перемежитель с высокой степенью рандолизации данных. Перемежитель, который обеспечивает высокую эффективность при минимальной сложности, в качестве кодового перемежителя, описан в находящихся на рассмотрении патентных заявках США №09/158459 от 22 сентября 1998 на “Систему кодирования с перемежителем на основе конечного автомата”, №09/172069 от 13 октября на “Систему кодирования с перемежителем на основе конечного автомата” и №09/205511 от 4 декабря 1998 на “Турбокодовый перемежитель, использующий линейную конгруэнтную последовательность”, переуступленных правоприемнику настоящей заявки. Указанные заявки включены в настоящее описание путем ссылки. Компонентный кодер 90 формирует на выходе системные символы 94 (обычно копия исходных входных битов, и символы 96 четности. Компонентный кодер 98 принимает перемеженные выходные данные кодового перемежителя 92 и формирует на выходе дополнительные символы 99 четности. Составляющий кодер 90 также может добавлять биты остатка для обеспечения известного состояния на конце каждого кадра.

Выходные данные компонентного кодера 90 и компонентного кодера 98 мультиплексируются в поток выходных данных для получения общей скорости кодирования R, равной 1/3. Дополнительные пары компонентных кодеров и кодовые перемежители могут быть добавлены для уменьшения скорости кодирования, чтобы повысить эффективность прямого исправления ошибок. В альтернативном варианте, некоторые символы четности 96 и 99 могут “прокалываться” (не передаваться) для того, чтобы увеличить скорость кодирования. Например, скорость кодирования может быть увеличена до _ путем прокалывания каждого второго символа четности 96 и 99 или путем прекращения передачи символов четности 96 вообще.

Компонентные кодеры 90 и 98 могут быть различных типов, включая блочные кодеры или сверточные кодеры. В качестве сверточных кодеров компонентные кодеры 90 и 98 обычно имеют ограниченную малую длину кода, например 4, для уменьшения сложности и представляют собой рекурсивные систематические сверточные кодеры. Ограниченная длина уменьшает сложность соответствующего декодера в приемной системе.

Обычно два кодера формируют на выходе один системный символ и один символ четности для каждого принятого бита, для получения составляющей скорости кодирования R=_. Однако общая скорость кодирования для турбокодера, показанного на фиг.1А, равна R=1/3, поскольку не используется системный бит из компонентного кодера 98. Как отмечалось выше, могут быть добавлены параллельно дополнительные перемежитель и пара кодеров для уменьшения скорости кодирования и улучшения исправления ошибок, или для увеличения скорости кодирования может выполняться прокалывание.

Фиг.3В иллюстрирует турбокодер 76 в виде турбокодера с последовательно соединенными каскадами в соответствии с альтернативным вариантом осуществления изобретения. В турбокодере, показанном на фиг.3В, данные из генератора 72 ЦИК принимаются компонентным кодером 110, и полученные в результате кодовые символы подаются на кодовый перемежитель 112. Полученные в результате перемеженные символы четности подаются на компонентный кодер 114, который выполняет дополнительное кодирование для генерации символов четности 115. Обычно компонентный кодер 110 (внешний кодер) может быть кодером различных типов, включая блочные кодеры или сверточные кодеры, но компонентный кодер 114 (внутренний кодер) предпочтительно является рекурсивным кодером и обычно системным рекурсивным кодером.

В качестве рекурсивных системных сверточных кодеров компонентные кодеры 110 и 114 генерируют символы со скоростью кодирования R<1. То есть для данного количества входных битов N генерируется М выходных символов, где М>N. Общая скорость кодирования для кодера на фиг.1В с последовательными каскадами равна скорости кодирования компонентного кодера 110, умноженной на скорость кодирования компонентного кодера 114. Дополнительные перемежитель и пары кодеров также могут быть добавлены последовательно для уменьшения скорости кодирования и, таким образом, для обеспечения дополнительной защиты от ошибок.

Фиг.4 - блок-схема приемной системы, выполненной в соответствии с первым вариантом осуществления изобретения. Антенна 150 обеспечивает передачу принятых РЧ сигналов в РЧ блок 152. РЧ блок выполняет преобразование с понижением частоты, фильтрацию и оцифровку РЧ сигналов. Блок 140 отображения принимает оцифрованные данные и формирует данные “мягкого” (программного) решения для канального обращенного перемежителя 156. Турбодекодер 158 декодирует данные “мягкого” решения из канального обращенного перемежителя 156 и передает полученные в результате данные “жесткого” (аппаратного) решения в процессор или блок управления в приемной системе, которая может проверить точность данных, используя данные контрольной суммы ЦИК.

Фиг.5 - блок-схема турбодекодера 158 и секции канального обращенного перемежителя, выполненных в соответствии с одним из вариантов осуществления изобретения. Как показано, турбодекодер 158 предназначен для декодирования данных от турбокодера, показанного на фиг.3А.

В описанном варианте предусмотрены два банка памяти канального обращенного перемежителя - оперативные запоминающие устройства 160а и 160в канального обращенного перемежителя, - при этом каждый банк может запоминать один блок канального перемежителя. Адресные входы двух банков памяти канального обращенного перемежителя управляются генератором 204 канальных адресов и счетчиком 206, выходные сигналы которых подаются на адресные входы через мультиплексоры 208 и 210. Мультиплексоры 208 и 210 управляются сигналом I и !I (логическая инверсия I) и поэтому, когда одно ОЗУ канального обращенного перемежителя управляется генератором 204 адресов канального обращенного перемежителя, то другое ОЗУ управляется счетчиком 206. В принципе любая выполняемая функция управления может быть обеспечена с помощью программы, выполняемой микропроцессором, хранящейся в памяти, а также с помощью дискретных логических схем, хотя использование различных других типов систем управления согласуется с использованием изобретения.

Порты ввода-вывода банков памяти канального обращенного перемежителя связаны с мультиплексорами 212 и 214. Мультиплексор 212 принимает данные “мягкого” решения из блока 140 отображения для одного из двух банков памяти канального обращенного перемежителя. С выхода мультиплексора 214 данные “мягкого” решения, хранящиеся в одном из двух банков памяти канального обращенного перемежителя, подаются в блок 218 частичной суммы. Мультиплексоры 212 и 214 управляются сигналом В и !В, соответственно, и поэтому, когда одно ОЗУ канального обращенного перемежителя принимает выборки из блока 140 отображения, то другое ОЗУ выдает выборки в блок 218 частичной суммы.

Во время работы выходной сигнал генератора 204 адресов канального обращенного перемежителя подается в банк памяти канального обращенного перемежителя, принимающий выборку из блока 140 отображения. Генератор адресов канального обращенного перемежителя генерирует адреса в обратном порядке относительно перемежения, выполненного канальным перемежителем 78, показанным на фиг.3. Следовательно, выборки считываются в банк памяти 160 канального обращенного перемежителя без перемежения (относительно канального перемежителя).

Выходной сигнал счетчика 206 подается в банк памяти канального обращенного перемежителя, выдающего “мягкое” решение в блок 218 частичной суммы. Поскольку данные “мягкого” решения были считаны в обратном порядке, то эти данные “мягкого” решения могут быть выданы без перемежения, просто используя счетчик 206. Также могут быть использованы различные другие методы буферизации данных “мягкого” решения, включая использование двухпортового запоминающего устройства. Кроме того, могут использоваться другие методы генерации адресов обращенного перемежителя, включая коммутирующий счетчик 206 и генератор 204 адресов канального обращенного перемежителя.

В турбокодере 158 блок 218 частичной суммы принимает принятые оценки (данные мягкого решения) из канального обращенного перемежителя, а также данные априорной вероятности (АВ) из памяти 170 АВ. Как хорошо известно, величины АВ представляют собой оценки переданных данных на основе предыдущей итерации декодирования. Во время первой итерации величины АВ устанавливаются в состояние с равной вероятностью.

Оценки из памяти канального обращенного перемежителя включают оценки системного символа, а также оценки двух символов четности для каждого бита данных, соответствующего блоку канального перемежителя. Блок 218 частичной суммы добавляет величину АВ к системному символу для создания “уточненной системной оценки”. Уточненная системная оценка вместе с оценками двух символов четности считывается в файл 224 ОЗУ.

В файле 224 ОЗУ величины оценок записываются в ОЗУ 230а - d окон (обозначены ОЗУ 0 - ОЗУ 3). В одном варианте изобретения оценки записываются в последовательном порядке в адресной области ОЗУ 0 - 3. Этот процесс начинается с ОЗУ 0 и продолжается до ОЗУ 3. В любой данный момент времени запись производится только в одном ОЗУ окна. Три остальных ОЗУ окна (те, в которых не происходит запись) подаются (считываются) на МАП-процессор 270 через мультиплексоры 260, как описано более подробно ниже.

В одном варианте изобретения для выполнения МАП-декодирования применяется скользящая оконная архитектура. Система и способ для выполнения такого декодирования со скользящим окном описана в находящейся на рассмотрении патентной заявке США №08/743688 на “Декодер выходных данных мягкого решения для декодирования кодовых слов, полученных методом сверточного кодирования”, переуступленной правоприемнику настоящего изобретения и включенной в настоящее описание путем ссылки.

В этой заявке МАП-декодирование выполняется в “окнах” данных. В описанном варианте изобретения банки 230 ОЗУ окон имеют размер L×q, где L - число переданных битов данных в окне, a q - число битов памяти, необходимых для запоминания оценок уточненного системного символа и двух символов четности, сформированных для каждого бита данных. В одном варианте изобретения, шесть битов используется для оценок двух символов четности и семь битов используется для оценок уточненного системного символа (которые, как описано выше, представляют собой сумму принятой оценки системного символа и величины АВ), для q, равного 18 битам.

Как отмечалось выше, оценки, включая уточненную оценку системного символа и оценки символов четности, записываются в ОЗУ 230а - d окон в последовательном порядке. Обычно только ОЗУ 230 окна записывается, а остальные три ОЗУ 230 окон считываются МАП - процессором 270.

В примерной процедуре обработки данных данные из нового канального блока сначала записываются в ОЗУ 230а окна, а затем в ОЗУ 230b окна. Следовательно, ОЗУ 230а окна содержит первое L (1L) множество оценок (где множество содержит уточненную оценку системного символа и оценки двух символов четности), а ОЗУ 230b окна содержит второе L (2L) множество оценок. Когда первые два множества, состоящие из L оценок, запомнены в ОЗУ 230 окон, мультиплексоры 260 начинают вводить данные, запомненные в ОЗУ 230 окон, в вычислители метрик состояния (ВМС) в МАП-декодере 270.

В одном варианте изобретения три ВМС состоят из прямого ВМС (ПВМС) 272 и двух обратных ВМС (ОВМС) 274а и 274b.

По мере того, как данные продолжают записываться в файл 224 ОЗУ, мультиплексоры 260 вводят оценки, запомненные в трех из четырех ОЗУ окон, в три вычислителя метрик состояния в МАП-декодере 270 в соответствии с таблицей.

В таблице помимо конкретных ОЗУ окон, вводимых в конкретные вычислители метрик состояния, также приводится список множества оценок, содержащихся в этом ОЗУ окна в данный момент времени и, таким образом, оценок, обрабатываемых соответствующим ВМС.

Окно обрабатывается один раз в прямом направлении и один раз в обратном направлении в соответствии с МАП-обработкой. Кроме того, большинство окон обрабатываются дополнительно еще раз в обратном направлении для формирования состояния инициализации для другой обратной обработки по вычислению метрик состояния. В таблице прогоны инициализации обозначены курсивным текстом. В описанном варианте каждое множество оценок обрабатывается три раза и поэтому к ОЗУ окна, в котором хранятся эти оценки, делается обращение также три раза. Использование 3 ОЗУ окон препятствует конкуренции ОЗУ.

Как также показано в таблице, в любой конкретный момент времени по меньшей мере одно ОЗУ окна не связано ни с каким ВМС и поэтому имеет возможность записи в него новых данных. Если имеется более трех окон из ОЗУ в пределах файла 224 ОЗУ, то данные могут непрерывно или с повторением поступать в МАП-процессор в правильной последовательности и в правильно выбранный вычислитель из трех ВМС, при одновременном приеме этих данных из памяти 160 канального перемежителя через блок 218 частичной суммы.

Следует также заметить, что таблица иллюстрирует связь, осуществляемую для шести (6) окон данных. Следовательно, примерный размер блока канального перемежителя равен 6L, а память канального обращенного перемежителя 6L×q. Размер канального блока в 6L приведен только для примера, а размер обычного канального блока будет больше, чем 6L.

В соответствии с фиг.5, в МАП-декодере 270 ПВМС 272 принимает оценки из файла 224 ОЗУ, как описано выше, и вычисляет на окне L величины метрик состояния в прямом направлении, которые запоминаются в буфере 276 метрик. Кроме того, согласно таблице, один ОВМС 274 вычисляет величины метрик состояния в обратном направлении по другому окну L. В одном из вариантов осуществления изобретения каждый вычислитель метрик состояния включает свой собственный отдельный вычислитель метрики перехода. В других вариантах осуществления изобретения один общий вычислитель метрик перехода может использоваться для множества метрик состояния, предпочтительно в комбинации с буфером метрик перехода.

В одном из вариантов осуществления изобретения используемый МАП-декодер представляет собой логарифмический МАП-декодер, который работает с логарифмом оценок, для уменьшения сложности аппаратных средств. Одна из реализаций логарифмического МАП-декодера, включающего вычислители метрик состояния и метрик перехода, описана в работе S.S. Pietrobon, “Implementation and Performance of a Turbo/MAP Decoder", "International Journal of Satellite Communications", February 1997 г. В этом логарифмическом МАП-декодере не используется архитектура со скользящими окнами, описанная в цитированной выше патентной заявке на “Декодер выходных данных мягкого решения для декодирования кодовых слов, полученных методом сверточного кодирования”.

Последнее значение, вычисленное первым ОВМС 274, используется для инициализации другого ОВМС 274, который выполняет вычисление метрики состояния в обратном направлении для окна L, для которого уже вычислены методики состояния в прямом направлении и хранятся в буфере 276 метрик. По мере того, как вычисляются метрики состояния в обратном направлении, они передаются через мультиплексор 278 в вычислитель 280 логарифма отношения правдоподобия (ЛОП). Вычислитель 280 ЛОП выполняет вычисление логарифма правдоподобия метрик состояния в обратном направлении, принятых из мультиплексора 278, и метрик состояния в прямом направлении, хранящихся в буфере 276 метрик. Полученные в результате оценки данных из вычислителя 280 ЛОП передаются в память 170 АВ.

При использовании способа вычисления метрик со скользящим окном объем памяти, используемый для выполнения необходимой обработки данных, уменьшается. Например, требуется только, чтобы размер ОЗУ 230 окон был таким же, как окно L, а не как размер всего блока перемежителя. Аналогично, только одно окно L метрик состояния в прямом направлении должно храниться в буфере 276 метрик в любой данный момент времени. Это значительно уменьшает размер схемы.

Кроме того, использование трех вычислителей метрик значительно увеличивает скорость, с которой может быть выполнено декодирование. Скорость увеличивается, потому что функции инициализации и декодирования могут выполняться параллельно. Инициализация увеличивает точность декодера.

В альтернативных вариантах осуществления изобретения могут использоваться два прямых вычислителя метрик состояния в сочетании с одним обратным вычислителем метрик состояния. А также может использоваться меньше вычислителей метрик состояния, если тактовые импульсы подаются с достаточно высокой частотой для того, чтобы выполнять в два раза больше операций. Однако увеличение тактовой частоты увеличивает потребляемую мощность, что нежелательно во многих случаях, включая мобильные системы связи или системы связи с питанием от аккумуляторной батареи.

Кроме того, хотя использование файла 224 ОЗУ уменьшает площадь, занимаемую схемой, и снижает конкуренцию ОЗУ в декодере, в других вариантах изобретения могут быть выбраны альтернативные архитектуры памяти.

Как описано выше со ссылкой на приведенный для примера вариант осуществления, декодирование осуществляется путем выполнения первого декодирования в первом окне в первом направлении и одновременного выполнения второго декодирования во втором окне во втором направлении. Второе направление предпочтительно является противоположным первому направлению.

Результаты первого декодирования запоминаются. Результаты второго декодирования используются для инициализации третьего декодирования, выполняемого в первом окне во втором направлении. Во время третьего декодирования вычисляются значения ЛОП с использованием величин, вычисленных во время третьего декодирования, и запомненных величин.

Одновременно с третьим декодированием выполняется четвертое декодирование другого окна в первом направлении, а также пятое декодирование во втором направлении еще в одном окне. Результаты пятого декодирования запоминаются и пятое декодирование используется для формирования значения инициализации. Эти этапы повторяются до тех пор, пока не будет декодирован весь блок канального перемежителя.

В различных альтернативных вариантах изобретения могут быть опущены некоторые шаги, используемые в описанном варианте. Однако использование совокупности описанных шагов обеспечивает быстрое и точное декодирование с минимумом памяти и дополнительных схем и, поэтому, обеспечивает значительные преимущества по эффективности.

В одном из вариантов осуществления изобретения память 170 АВ состоит из двух банков 284 памяти АВ. Мультиплексоры 286 переключают каждый банк 284 памяти между состоянием считывания из него данных с помощью блока 218 частичной суммы и состоянием записи в него данных с помощью ЛОП 280 для обеспечения работы с двойной буферизацией. На мультиплексоры 288 подаются сигналы либо со счетчика 290, либо с генератора 292 адресов кодового перемежителя, так чтобы для каждой итерации декодирования выполнялись турбокодовое перемежение и обратное перемежение.

Кроме того, банки 284 памяти АВ могут быть достаточно большими, чтобы вмещать все оценки данных для одного блока канального перемежителя, где оценки являются оценками передаваемых данных, а не символов четности. Могут быть использованы оценки шестибитового разрешения.

Весь процесс декодирования продолжается путем повторного считывания принятых оценок из буфера 160 канального обращенного перемежителя и обработки данных с величинами АВ из банка 170 памяти АВ. После серии итераций оценки должны сходиться к совокупности величин, которые затем используются для формирования “жестких” решений. Результаты декодирования затем проверяются с использованием значений ЦИК. Одновременно с декодированием другой буфер канального обращенного перемежителя принимает следующий блок оценок приема.

Фиг.6 - графическое представление программы, иллюстрирующее шаги, выполняемые во время логарифмического МАП-декодирования блока канального перемежителя в соответствии с одним из вариантов осуществления изобретения. Шаги описаны со ссылками на элементы, показанные на фиг.5.

Декодирование начинается с шага 300, и на шаге 302 индекс N окна устанавливается на 0. На шаге 304 окно {N] и окно [N+1] оценок, хранящихся в ОЗУ канального обращенного перемежителя, записываются в ОЗУ {N mod 3] окна и ОЗУ {(N+1) mod 3] окна соответственно. Как отмечено выше, окно оценок соответствует символам, сформированным для окна из L битов передаваемых данных.

На шаге 308 ПВМС обрабатывает оценки в ОЗУ[N mod 3] (в этом случае - это ОЗУ 0), и ОВМС 0 обрабатывает оценки в ОЗУ[(N+1) mod 3] (ОЗУ 1). Кроме того, окно [N+2] оценок из ОЗУ канального обращенного перемежителя записывается в ОЗУ[(N+2) mod 3] окна (ОЗУ 2).

На шаге 310 индексу N окна дается приращение, и Х устанавливается на N mod 2, a Y устанавливается на (N+1) mod 2. На шаге 312 определяется, соответствует ли N+1 последнему окну оценок, которые должны обрабатываться. Если нет, то выполняется шаг 314.

На шаге 314 ПВМС обрабатывает оценки, хранящиеся в ОЗУ[N mod 3] окна, ОВМС Х (Х=0 на первом проходе) обрабатывает оценки, хранящиеся в ОЗУ[(N+1) mod 3] окна, а ОВМС Y (Y=1 на первом проходе) обрабатывает оценки, хранящиеся в ОЗУ[(N-1) mod 3] окна. Кроме того, окно [N+2] оценок из ОЗУ канального обращенного перемежителя записывается в ОЗУ[(N+2) mod 3] окна.

Не показано, что множество значений АВ, соответствующих окну [N-1] данных, формируется на шаге 314 во время обработки данных, выполняемой ОВМС 1. При выполнении декодирования по окнам размер буфера метрик поддерживается на длине, равной числу метрик, формируемых для каждого шага декодирования, умноженному на L. Поскольку для каждого шага декодирования запоминается множество метрик, то уменьшение памяти для метрик является значительным по сравнению с запоминанием метрик состояния для целого блока канального обращенного перемежителя.

Кроме того, использование второго обратного вычислителя метрик состояния увеличивает скорость и точность. Например, второй ОВМС может вычислять новое начальное значение для следующего окна декодирования, когда обрабатывается предыдущее окно декодирования. Вычисление этого нового начального значения устраняет потребность в выполнении новых вычислений ОВМС для каждого шага декодирования, поскольку это новое значение может быть использовано для декодирования предыдущего окна.

Шаг 314 иллюстрирует высокую эффективность, достигаемую за счет обработки оценок, как пояснено, с помощью файла 224 ОЗУ. Более конкретно, шаг 314 иллюстрирует возможность одновременно выполнять четыре шага при обработке декодирования. Это увеличивает скорость, с которой может быть выполнено кодирование для данной тактовой частоты. В описанном варианте шаги включают обработку вычислений метрик состояния и запись дополнительных выборок в файл 224 ОЗУ. Кроме того, при выполнении шага 314 вычисляются значения АВ.

При завершении шага 314 индексу N окна дается приращение на шаге 310. Если величина N+1 равна последнему окну, то конвейерная обработка прерывается, и оставшиеся оценки в файле 224 ОЗУ обрабатываются на шагах с 316 по 322.

Более конкретно, на шаге 316 ПВМС обрабатывает ОЗУ[N mod 3] окна, ОВМС Х обрабатывает ОЗУ [(N+1) mod 3] окна и ОВМС Y обрабатывает ОЗУ[(N+1) mod 3] окна. На шаге 318 индекс N окна получает приращение, Х устанавливается на N mod 2, а Y устанавливается на (N+1) mod 2. На шаге 320 ПВМС обрабатывает ОЗУ [N mod 3], а ОВМС Y обрабатывает ОЗУ [(N-1) mod 3]. На шаге 322 ОВМС 1 обрабатывает ОЗУ {N mod 3]. На шаге 324 блок канального обращенного перемежителя завершается и обработка завершается.

Таким образом, описан новый и улучшенный метод выполнения турбокодирования.

Изобретение является новым и улучшенным способом декодирования применительно к турбокодированию или итеративным методам кодирования. В соответствии с одним из вариантов осуществления изобретения система декодирования включает ОЗУ канального обращенного перемежителя для запоминания блока символьных оценок, множество из S вычислителей метрик состояния и множество из S+1 ОЗУ окон. Каждый вычислитель метрик состояния предназначен для формирования множества вычислений метрик состояний, при этом S из S+1 ОЗУ окон обеспечивают символьные оценки для S вычислителей показателей состояний. Оставшееся ОЗУ окна получает символьные оценки из ОЗУ канального обращенного перемежителя. Техническим результатом, достигаемым при реализации данного изобретения, является увеличение скорости выполнения операций декодирования для упрощения использования турбокодирования в различных системах. 4 н. и 11 з.п. ф-лы, 8 ил.

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Выходное устройство декодера Витерби | 1990 |

|

SU1775858A1 |

| RU 96107771 А, 27.07.1998 | |||

| US 5450453 А, 12.09.1995 | |||

| ДЕКОДЕР ВИТЕРБИ | 1997 |

|

RU2127944C1 |

Авторы

Даты

2004-09-10—Публикация

1999-08-13—Подача