Изобретение относится к системам передачи информации шумоподобными ортогональными кодами с фазоманипулированной модуляцией несущей частоты и может быть использовано для передачи и приема данных по каналам силовых электрических сетей, а также проводным и радиоканалам связи.

Известно устройство приема и передачи информации по линиям силовых электрических сетей, содержащее генератор псевдослучайной последовательности, широкополосные модулятор и демодулятор, усилители и устройство согласования с электрической сетью, блок синхронизации генератора псевдослучайной последовательности от сигналов электрической силовой сети (см. патент США № 4864589, кл. Н 04 L 27/30). Однако такое устройство имеет низкую точность синхронизации и становится неработоспособным при пропадании сигнала переменного напряжения электрической силовой сети.

Известен метод и аппаратура для параллельной некогерентной корреляционной обработки сложных широкополосных сигналов, содержащая два канала синхронной и квадратурной обработки, каждый из которых включает последовательно соединенные перемножитель, фильтр, согласованный фильтр на два кода, выходы согласованного фильтра синфазного канала суммируются с соответствующими выходами согласованного фильтра квадратурного канала с помощью сумматоров, выходы которых через нелинейные элементы подключены через отдельный сумматор к входу нормализатора (см. патент США № 5963586, кл. Н 04 В 1/707). Однако при приеме синхронизирующей составной последовательности устройство имеет большое значение отклика бокового лепестка корреляционной функции, что снижает точность оценки задержки синхросигнала. При приеме информационно модулированного сигнала метод и аппаратура характеризуются низкой скоростью передачи информации и не защищены от столкновений в асинхронном режиме передачи сигналов несколькими приемопередатчиками, работающими в одном канале.

Прототипом изобретения является устройство приема и передачи фазоманипулированных кодовых сигналов, содержащее последовательно соединенные фазовый модулятор, усилитель, блок согласования, бинарный квантователь, блок некогерентных демодуляторов, последовательно соединенные генератор импульсов, фазовращатель, синхронный и квадратурный выходы которого подключены к соответствующим входам блока некогерентных демодуляторов, синхронный выход фазовращателя подключен к входу фазового модулятора, второй выход генератора импульсов подключен к входам многоканального некогерентного коррелятора через генератор опорных сигналов, второй выход которого подключен к входу блока принятия решения, выходы которого подключены к входам блока ввода-вывода, который имеет вход и выход для ввода и вывода данных, причем блок согласования подключен к каналу распространения фазоманипулированного сигнала через отдельный вход-выход (см. патент США № 4979183, кл. Н 04 К 1/00).

Прототип не позволяет принимать достаточно длинные фазокодированные сигналы с высокой достоверностью при расстройках несущих частот приемопередатчиков на передающем и приемном пунктах, превышающих значения, определяемые интервалом когерентности синхронизирующей последовательности и блочного кода. Прототип не защищен от столкновений (наложений во времени сигналов, передаваемых разными приемопередатчиками) в асинхронном режиме передачи сигналов несколькими приемопередатчиками, работающими в одном канале.

В основу изобретения положена задача создания простого устройства приема и передачи, позволяющего формировать в асинхронном режиме передачи сигналов несколькими приемопередатчиками, работающими в одном канале, достаточно длинные фазокодированные сигналы и эффективно их обрабатывать при значительных расстройках несущих частот приемопередатчиков на передающем и приемном пунктах.

Устройство приема и передачи фазоманипулированных кодовых сигналов, содержащее последовательно соединенные фазовый модулятор, усилитель, блок согласования, бинарный квантователь, блок некогерентных демодуляторов, последовательно соединенные генератор импульсов, фазовращатель, синхронный и квадратурный выходы которого подключены к соответствующим входам блока некогерентных демодуляторов, синхронный выход фазовращателя подключен к входу фазового модулятора, второй выход генератора импульсов подключен к входам многоканального некогерентного коррелятора через генератор опорных сигналов, второй выход которого подключен к входу блока принятия решения, выходы которого подключены к входам блока ввода-вывода, который имеет вход и выход для ввода и вывода данных, причем блок согласования подключен к каналу распространения фазоманипулированного сигнала через отдельный вход-выход, согласно изобретению дополнительно введены последовательно соединенные генератор балансного кода, блок перестановки, блок логического преобразования, блок коммутации, выход которого подключен к второму входу фазового модулятора, выход генератора балансного кода подключен к вторым входам, соответственно, блока логического преобразования и блока коммутации, третий вход которого подключен к выходу блока перестановки, второй выход генератора балансного кода подключен к второму входу блока перестановки, входу блока случайной задержки и входу формирователя сигналов управления, один выход которого подключен к третьему входу блока ввода-вывода, второй выход формирователя сигналов управления подключен к четвертому входу блока коммутации и третьему входу блока перестановки, четвертый вход которого подключен к отдельному выходу блока ввода-вывода, дополнительный выход которого подключен к второму входу блока случайной задержки, выход которого подключен к второму входу формирователя сигналов управления, синфазный и квадратурный выходы блока некогерентных демодуляторов подключены к синфазному и квадратурному входам блока обратной перестановки и через некогерентный согласованный фильтр логически преобразованного кода к синхронному и квадратурному входам некогерентного согласованного фильтра балансного кода, выход которого через сумматор подключен к входу дифференцирующего блока, отдельный выход некогерентного согласованного фильтра логически преобразованного кода подключен к второму входу сумматора, второй выход генератора импульсов подключен к синхронизирующим входам, соответственно, некогерентного согласованного фильтра логически преобразованного кода, некогерентного согласованного фильтра балансного кода, дифференцирующего блока и порогового блока, выход которого подключен к четвертому входу блока ввода-вывода и через дифференцирующий блок к входу генератора опорных сигналов, синхронизирующий вход многоканального некогерентного коррелятора объединен с синхронизирующими входами, соответственно, блока обратной перестановки, генератора балансного кода, блока перестановки, блока принятия решения и подключен к второму выходу генератора импульсов, выход сумматора подключен к второму входу порогового блока, выходы блока обратной перестановки подключены через последовательно соединенные многоканальный некогерентный коррелятор и многоканальный накопитель к второму входу блока принятия решения, второй выход которого подключен к отдельному входу многоканального накопителя, дополнительный вход которого соединен с дополнительными входами блока обратной перестановки, многоканального некогерентного коррелятора и подключен к второму выходу генератора опорных сигналов, причем третий выход формирователя сигналов управления подключен к третьему входу фазового модулятора.

Новые блоки и связи позволяют в асинхронном режиме передачи сигналов несколькими приемопередатчиками, работающими в одном канале, сформировать сегментно-сбалансированные синхронизирующий и блочно-кодированный фазоманипулированный сигнал, а в режиме приема осуществить точную блочную синхронизацию путем оценки задержки принимаемого синхросигнала фильтром, согласованным с суммой модулей сегментов, и многоканальное сегментно-модульное корреляционное декодирование сигналов блочного кода при значительных расстройках частот несущих колебаний на передающей и принимаемой стороне, а также уменьшить влияние на приемопередатчик столкновений его сигналов с сигналами других приемопередатчиков, работающих в этом же канале.

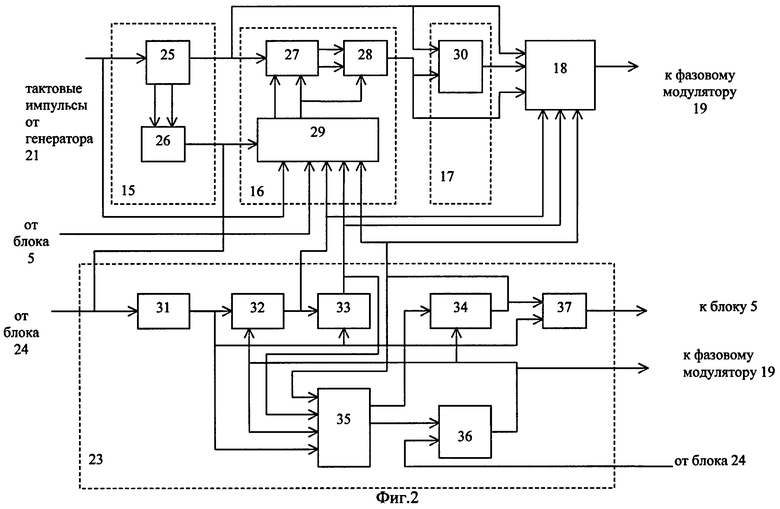

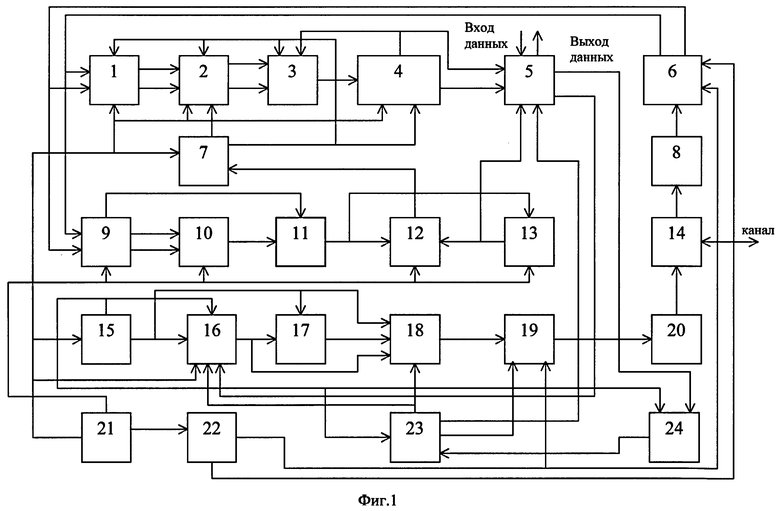

На фиг.1 изображена структурная схема устройства приема и передачи фазоманипулированных кодовых сигналов.

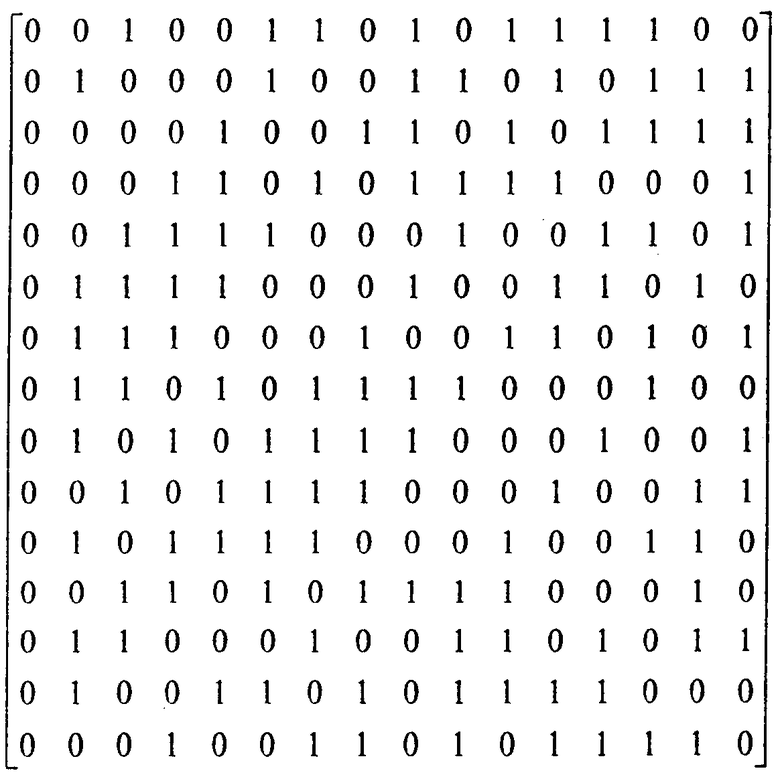

На фиг.2 изображены схемы, поясняющие работу генератора балансного кода, блока перестановки, блока логических преобразований, блока коммутации и формирователя сигналов управления.

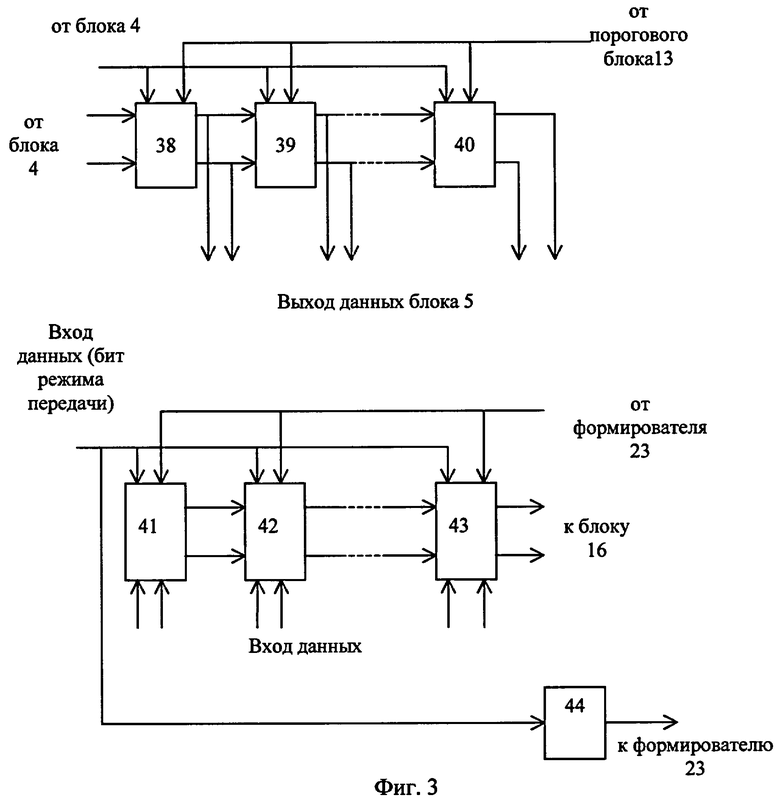

На фиг.3 изображены схемы, поясняющие работу блока ввода-вывода.

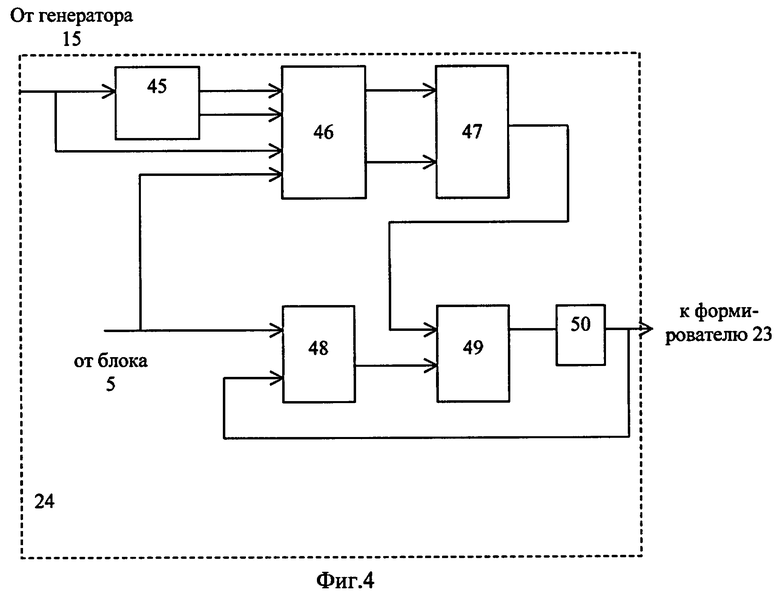

На фиг.4 изображены схемы, поясняющие работу блока случайной задержки.

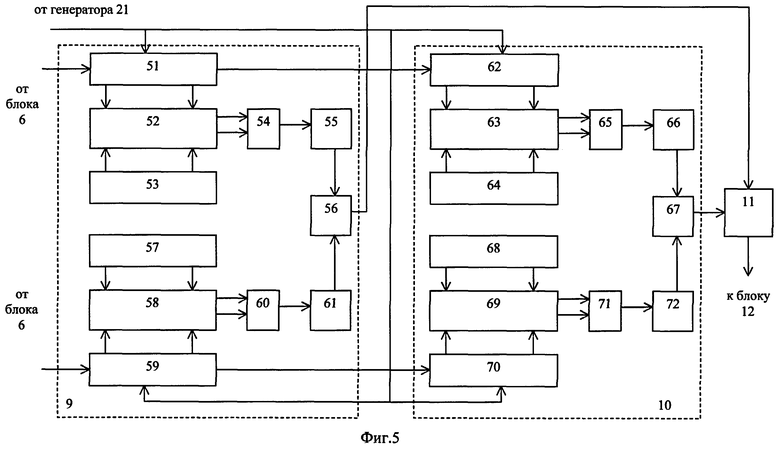

На фиг.5 изображены схемы, поясняющие работу некогерентных согласованных фильтров балансного кода и логически преобразованного кода, а также сумматора.

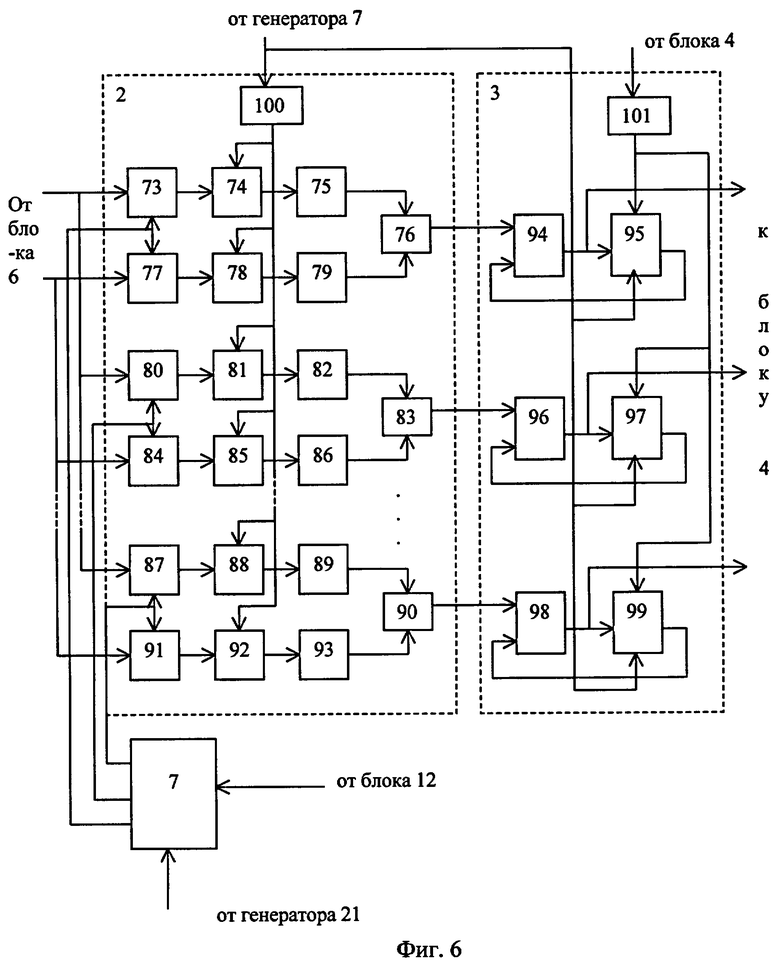

На фиг.6 изображены схемы, поясняющие работу многоканального некогерентного коррелятора и многоканального накопителя.

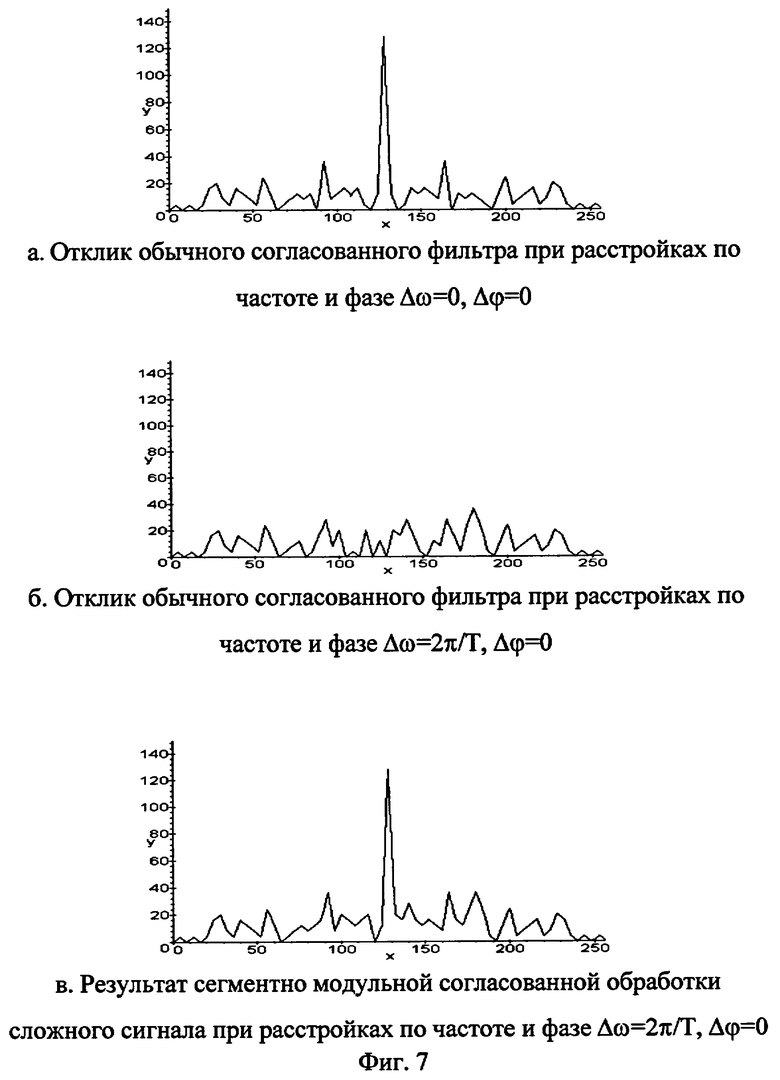

На фиг.7 изображены схемы, поясняющие эффект применения сегментно согласованной, модульной обработки сложного составного сегментно сбалансированного сигнала при расстройке частот несущих колебаний.

Устройство приема и передачи фазоманипулированных кодовых сигналов содержит последовательно соединенные фазовый модулятор 19, усилитель 20, блок 14 согласования, бинарный квантователь 8, блок 6 некогерентных демодуляторов, последовательно соединенные генератор 21 импульсов, фазовращатель 22, синхронный и квадратурный выходы которого подключены к соответствующим входам блока некогерентных демодуляторов 6. Синхронный выход фазовращателя 22 подключен к входу фазового модулятора 19, второй выход генератора 21 импульсов подключен к входам многоканального некогерентного коррелятора 3 через генератор 7 опорных сигналов, второй выход которого подключен к входу блока 4 принятия решения, выходы которого подключены к входам блока 5 ввода-вывода, который имеет вход и выход для ввода и вывода данных. Блок 14 согласования подключен к каналу распространения фазоманипулированного сигнала через отдельный вход-выход. Последовательно соединены генератор 15 балансного кода, блок 16 перестановки, блок 17 логического преобразования, блок 18 коммутации, выход которого подключен к второму входу фазового модулятора 19. Выход генератора 15 балансного кода подключен к вторым входам, соответственно, блока 17 логического преобразования и блока 18 коммутации, третий вход которого подключен к выходу блока 16 перестановки. Второй выход генератора 15 балансного кода подключен к второму входу блока 16 перестановки, входу блока 24 случайной задержки и входу формирователя 23 сигналов управления, один выход которого подключен к третьему входу блока 5 ввода-вывода. Второй выход формирователя 23 сигналов управления подключен к четвертому входу блока 18 коммутации и третьему входу блока 16 перестановки, четвертый вход которого подключен к отдельному выходу блока 5 ввода-вывода, дополнительный выход которого подключен к второму входу блока 24 случайной задержки, выход которого подключен к второму входу формирователя 23 сигналов управления. Синфазный и квадратурный выходы блока некогерентных демодуляторов 6 подключены к синфазному и квадратурному входам блока 1 обратной перестановки и через некогерентный согласованный фильтр 9 логически преобразованного кода к синхронному и квадратурному входам некогерентного согласованного фильтра 10 балансного кода, выход которого через сумматор 11 подключен ко входу дифференцирующего блока 12, отдельный выход некогерентного согласованного фильтра 9 логически преобразованного кода подключен к второму входу сумматора 11. Второй выход генератора импульсов 21 подключен к синхронизирующим входам, соответственно, некогерентного согласованного фильтра 9 логически преобразованного кода, некогерентного согласованного фильтра 11 балансного кода, дифференцирующего блока 12 и порогового блока 13, выход которого подключен к четвертому входу блока 5 ввода-вывода и через дифференцирующий блок 12 к входу генератора 7 опорных сигналов. Синхронизирующий вход многоканального некогерентного коррелятора 3 объединен с синхронизирующими входами, соответственно, блока 1 обратной перестановки, генератора 15 балансного кода, блока 16 перестановки, блока 4 принятия решения и подключен к второму выходу генератора 21 импульсов. Выход сумматора 11 подключен к второму входу порогового блока 13. Выходы блока 1 обратной перестановки подключены через последовательно соединенные многоканальный некогерентный коррелятор 2 и многоканальный накопитель 3 к второму входу блока 4 принятия решения, второй выход которого подключен к отдельному входу многоканального накопителя 3, дополнительный вход которого соединен с дополнительными входами блока 1 обратной перестановки, многоканального некогерентного коррелятора 2 и подключен к второму выходу генератора 7 опорных сигналов. Третий выход формирователя 23 сигналов управления подключен к третьему входу фазового модулятора 19.

Генератор 15 балансного кода содержит генератор 25 псевдослучайного кода, формирующего сбалансированную (содержащую одинаковое число логических 1 и логических 0) псевдослучайную последовательность и дешифратор 26, на выходе которого появляется импульс с периодом повторения, равным периоду повторения псевдослучайной последовательности.

Блок 16 перестановки выполняет перестановку символов балансного кода, формируемых генератором 15, и содержит блок 27 оперативных запоминающих устройств, коммутатор 28, генератор 29 сигналов считывания и записи.

Блок 17 логического преобразования осуществляет преобразование символов с выходов генератора 15 балансного кода и блока 16 перестановки по правилам алгебры логики. В качестве такого преобразования может выбрана, например, операция суммирования по модулю два, выполняемая сумматором 30 по модулю два.

Формирователь 23 сигналов управления формирует коды управления для блока 18 коммутации и генератора 29 сигналов считывания и записи, расположенного в блоке 16 перестановки. Формирователь 23 сигналов управления содержит делитель 31, формирователь 32 временных интервалов синхросигнала, формирователь 34 временных интервалов кадра, логические схемы И 33 и 37, блок 35 дешифраторов, триггер 36.

Блок 5 ввода-вывода содержит дифференциатор 44, а также последовательно соединенные регистры 38, 39, 40 и последовательно соединенные регистры 41, 42, 43 сдвига, осуществляющие операции записи, сдвига и хранения битов передаваемой и принимаемой информации. В состав вводимой информации входит бит режима передачи, поступающий на вход дифференциатора 44 и установочные входы регистров 41, 42, 43 сдвига.

Блок 24 случайной задержки содержит генератор 45 случайных чисел, счетчик 46, дешифратор 47, RS-триггер, D-триггер, дифференциатор 50. Блок 24 осуществляет задержку на случайную величину импульса с соответствующего выхода блока 5 ввода-вывода.

Некогерентный многоканальный коррелятор 2 выполняет многоканальную корреляционную обработку сегментов синфазной и квадратурной компоненты демодулированных слов блочного кода с неизвестной начальной фазой несущего колебания. Некогерентный многоканальный коррелятор 2 содержит перемножители 73, 77, 80, 84, 87, 91, сумматоры 74, 78, 81, 85, 88, 92, блоки 75, 79, 82, 86, 89, 93 вычисления модуля суммы, сумматоры 76, 83, 90. Установочные входы сумматоров 74, 78, 81, 85, 88, 92 объединены и подключены через элемент 100 задержки к выходу генератора 7. Входы, стробирующие запись регистров 95, 97, 99, объединены и подключены к выходу генератора 7. Одни входы перемножителей 73, 77, 80, 84, 87, 91 подключены к выходам генератора 7 опорных сигналов, а другие входы перемножителей 73, 80, 87 - к выходу синхронной компоненты блока 6 некогерентных демодуляторов. Другие входы перемножителей 77, 84, 91 подключены к выходу квадратурной компоненты блока 6 некогерентных демодуляторов.

Некогерентные согласованные фильтры 9 и 10 имеют однотипную структуру, но настроены на различные формы кодовых последовательностей и осуществляют квадратурную согласованную фильтрацию сегментов принимаемой синхропоследовательности с неизвестной начальной фазой несущего колебания. Каждый из некогерентных согласованных фильтров 9 и 10 содержит регистры 51, 62, 59, 70 сдвига, регистры 53, 57, 64, 68 хранения, блоки 52, 58, 63, 69 сумматоров по модулю два, сумматоры 54, 60, 65, 71, блоки 55, 61, 66, 72 вычисления модуля суммы, сумматоры 56 и 67. Вход регистра 51 сдвига подключен к выходу синфазной компоненты блока 6 некогерентных демодуляторов, а вход регистра 59 - к выходу квадратурной компоненты блока 6 некогерентных демодуляторов. Синхронизирующие входы регистров 51, 62, 59, 70 подключены к выходу генератора 21 импульсов.

Многоканальный накопитель 3 содержит накопители, каждый из которых содержит последовательно соединенные сумматоры 94, 96, 98 и регистры хранения 95, 97, 99, установочные входы которых подключены к выходу блока 4 принятия решения.

Устройство работает следующим образом. Возможны два режима работы устройства: режим передачи и режим приема информации.

Переход в тот или иной режим зависит от значения бита режима передачи, поступающей на вход блока 5 ввода-вывода. Если бит режима передачи равен 1, то устройство осуществляет запись данных в блок 5 ввода-вывода (регистры 41, 42, 43), их кодирование и передачу в канал с помощью фазоманипулированного кодового сигнала. Если бит режима передачи равен нулю, то осуществляется демодуляция и декодирование принимаемой из канала информации.

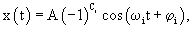

В режиме передачи через блок 14 согласования в канал передается кадр фазоманипулированных кодов. При этом генератор 21 импульсов формирует опорное гармоническое колебание вида Aгcos(ω t+ϕ ), где Аг, ω и ϕ соответственно амплитуда, угловая частота и начальная фаза. Фазовращатель 22 формирует два гармонических колебания Ф1(t) и Ф2(t), сдвинутые друг относительно друга на 90°

Ф1(t)=Acos(ω it+ϕ i);

Ф2(t)=Asin(ω it+ϕ i).

Колебание Ф1(t) подается на вход фазового модулятора 19 и используется при формировании сигнала в режиме передачи.

Манипуляцию несущего колебания осуществляет фазовый модулятор 19, на один вход которого подается код с выхода блока 18 коммутации, а на другой вход - гармоническое колебание несущей частоты, формируемое генератором 21 импульсов и поступающее на вход фазового модулятора 19 с выхода фазовращателя 22. Нулевая фаза несущего колебания соответствует логическому нулю кода, а фаза, равная 180° , - логической единице кодовой последовательности. Фазоманипулированный сигнал с выхода фазового модулятора 19 поступает в канал распространения, пройдя предварительную обработку усилителем 20 и блоком 14 согласования. Структура кадра передаваемой информации состоит из преамбулы в виде синхронизирующего сигнала и последовательно расположенных друг за другом информационно модулированных ортогональных (или квазиортогональных) кодовых последовательностей. Все множество информационно-модулированных последовательностей образует блочный ортогональный/квазиортогональный код.

Синхронизирующая последовательность состоит из двух сегментов S1 и S2, каждый из которых имеет хорошие корреляционные свойства (малые значения боковых лепестков авто- и взаимно корреляционных функций) и содержит равное число логических нулей и единиц, т.е. относится к классу балансных. Формирование первого сегмента синхронизирующей последовательности S1 осуществляется генератором 15 балансного кода с помощью генератора 25 псевдослучайного кода. В качестве такого генератора может быть использован регистр сдвига с обратными связями, формирующего расширенную на один символ М-последовательность. Так, балансный код длины N=16, сформированный на основе полинома f(x)=х4+х+1 и расширенный путем добавления одного нулевого символа, имеет вид S1=[s1,0,s1,1,... ,s1,N-1]=0000100110101111.

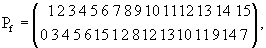

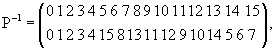

С выхода генератора 15 балансный код S1 поступает на вход блока 16 перестановки, где в блоке 27 оперативных запоминающих устройств осуществляется перестановка формы Pf символов без нарушения свойства балансности. Закон перестановки формы не должен значительно изменять в худшую сторону корреляционные свойства сигнала. Так, если перестановку символов осуществлять по правилу

то получим последовательность другой формы S3=[s3,0,s3,1,... ,s3,N-1]=0010001111010110, принадлежащую к классу псевдослучайных, балансных с хорошими корреляционными свойствами. В блоке 16 перестановка осуществляется непрерывно, для этого блок 27 оперативных запоминающих устройств содержит два запоминающих устройств, попеременно работающих на запись и считывание. Запись осуществляется в порядке очередности поступления, а считывание по закону перестановки формы. Соответственно коммутатор 28 подключает к выходу блока 16 перестановки выходы тех оперативно запоминающих устройств, которые работают в режиме считывания. Адреса записи и считывания формирует генератор 29 сигналов считывания и записи, управляемый сигналами с выходов формирователя 23 сигналов управления, блока 5 ввода-вывода, тактовые импульсы поступают на вход генератора 29 с выхода генератора 21 импульсов. В режиме формирования синхросигнала с выхода блока 5 ввода-вывода поступает нулевой код, с выхода формирователя 32 временных интервалов синхросигнала - логическая единица, с выхода схемы 33 сначала попеременно логический ноль, а затем логическая единица, с выхода формирователя 34 временных интервалов кадра - логический ноль. Начало формирования синхросигнала задается импульсом, поступающим на вход триггера 36 с выхода блока 24 случайной задержки.

Коды с выхода генератора 15 балансного кода и блока 16 перестановки поступают на входы блока 17 логического преобразования, на выходе которого формируется второй сегмент S2 синхронизирующего сигнала. Для рассматриваемого примера в качестве логической операции выбрано суммирование по модулю два, и соответственно сигнал на выходе блока 17 логического преобразования имеет вид

S2=S1⊕S3=0010101001111001.

Данный код также сбалансирован и имеет хорошие корреляционные свойства.

Синхронизирующий сигнал Sc образуется в результате конкатенации (присоединения) сигналов с выходов генератора 15 балансного кода и блока 17 логического преобразования

Sc=S1|S2=00001001101011110010101001111001.

Корреляционные свойства полученной кодовой последовательности иллюстрируются фиг.7а.

Операция присоединения выполняется блоком 18 коммутации по сигналам управления, поступающим на его входы с выходов формирователя 23 сигналов управления. При поступлении на вход блока 18 с выхода формирователя 32 временных интервалов синхросигнала логической единицы, а с выхода формирователя 34 временных интервалов кадра и с выхода логической схемы 33 И - логического нуля к выходу блока 18 коммутации подключается выход генератора 15 балансного кода. При поступлении на вход блока 18 с выхода формирователя 32 временных интервалов синхросигнала и выхода схемы 33 И логической единицы, а с выхода формирователя 34 временных интервалов кадра - логического нуля к выходу блока 18 коммутации подключается выход блока 17 логического преобразования. При поступлении на входы блока 18 блока 16 перестановки с выхода формирователя 32 временных интервалов синхросигнала и выхода схемы 33 И логического нуля, а с выхода формирователя 34 временных интервалов кадра - логической единицы заканчивается этап формирования синхросигнала, и устройство переходит в режим кодирования и передачи входных данных. В этом режиме блок 18 коммутации подключает к своему выходу сигнал с выхода блока 16 перестановки, а на выходе схемы 37 И появляется и поступает на синхронизирующие входы регистров 41, 42, 43 сигнал с периодом повторения, равным удвоенному периоду повторения балансного кода. По данному синхронизирующему сигналу осуществляется последовательная перезапись блоков данных по K≤ log2N бит из одного регистра 41-43 в другой. С выходов последнего регистра 43 блок данных поступает на вход генератора 29 сигналов считывания и записи, расположенного в блоке 16 перестановки. В соответствии с кодом блока данных в блоке 16 перестановки выполняется операция квазициклического сдвига кода S3=[s3,0,s3,1,... ,s3,N-1]. При этом символ S3,0, расположенный на нулевой позиции, остается неизменным, а символы, расположенные на позициях, начиная с первой и кончая (N-1), циклически сдвигаются. Величина сдвига задается кодом данных. Считывание кода данных из блока 5 ввода-вывода происходит с периодом в два раза большим, чем период повторения кодовой последовательности S3. Поэтому каждому блоку данных из К бит соответствуют два одинаковых сдвига сбалансированной последовательности с выхода блока 16 перестановки. Например, для К=0010 на выходе блока 18 коммутации сформируется составной сегментно сбалансированный код

S3(К)|S3(К)=0000111101011001|0000111101011001.

Количество информационных блоков в кадре регулируется емкостью формирователя 34 временных интервалов кадра. Кодирование блоков данных прекращается при появлении на выходе формирователя 34 временных интервалов кадра, формирователя 32 - временных интервалов синхросигнала, устанавливаются нулевые логические потенциалы. Сигнал с выхода блока 35 дешифраторов перебрасывает триггер 36, потенциал с выхода которого приостанавливает работу фазового модулятора 19.

Таким образом, в режиме передачи i-e устройство формирует фазоманипулированный кодовый сигнал вида

где Ci=[ci,0,.сi,1...,сi,2N(m+1)-1}=

=S1|S2|S3(K1)|S3(K1)|S3(К2)|S3(К2)|... |S3(Кm)|S3(Km) -

сегментно сбалансированная кодовая последовательность символов сi,l∈{0,1}, каждый сегмент S состоит из равного количества нулевых и единичных символов и принадлежит к классу ортогональных (квазиортогональных) кодов; K1 - величина сдвига, N - длина сегмента, m - число блоков данных в передаваемом кадре.

Устройство приема и передачи формирует и передает сигнал в случайные интервалы времени. Это осуществляется с помощью блока 15 случайной задержки, задерживающее на случайный интервал времени поступление сигнала, соответствующему биту режима передачи на вход формирователя 23 сигналов управления. Генератор 45 случайных чисел непрерывно формирует код случайного числа h. При нулевом значении бита режима передачи счетчик 46 установлен в нулевое состояние. При появлении сигнала, соответствующего единичному значению бита режима передачи, на выходе блока 5 ввода-вывода формируется импульс, перебрасывающий RS-триггер 48 и устанавливающий разряды счетчика 46 в положение, определяемое случайным кодом с выхода генератора 45 случайных чисел. Счетчик 46 имеет емкость М разрядов и считает импульсы с выхода дешифратора 26. Дешифратор 47 настроен на нулевой код выходов счетчика 46 и импульс на его выходе появляется после пересчета счетчиком 46 случайного числа (2м-h) импульсов с выхода дешифратора 26. Выход дешифратора 47 подключен к синхронизирующему входу D триггера 49, на другой вход которого подается сигнал с выхода триггера 48. После появления импульса на выхода дешифратора 47 на выходе D триггера 49 формируется потенциал выхода триггера 48, момент появления которого фиксируется дифференциатором 50.

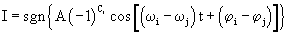

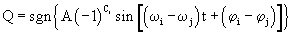

В режиме приема устройство реализует схему некогерентной обработки фазоманипулированного сигнала с неизвестной начальной фазой несущего колебания. Принимаемый сигнал, пройдя блок 14 согласования, бинарный квантователь 8, поступает на вход блока 6 некогерентных демодуляторов, который вычисляет синфазную и квадратурную компоненты на видеочастоте. При приеме сигнала от j-го передатчика на выходах некогерентного демодулятора i-го устройства приема-передачи выделяются синфазная

и квадратурная

компоненты, Δ ω =(ω i-ω j)-Δ ϕ =(ϕ i-ϕ j) - расстройки, соответственно, частот и начальных фаз несущих колебаний принимаемого и опорного сигналов.

Синфазная компонента образуется как результат фильтрации в полосе сигнала результата умножения бинарно квантованного принимаемого сигнала на синфазную гармоническую копию опорной частоты несущего колебания. Квадратурная компонента образуется как результат фильтрации в полосе сигнала результата умножения бинарно квантованного принимаемого сигнала на квадратурную гармоническую копию опорной частоты несущего колебания, сдвинутую фазовращателем 22 на 90° относительно синфазной копии опорной частоты несущего колебания.

Кадр принимаемого бинарного фазоманипулированного кодового сигнала обрабатывается за два этапа. На первом этапе осуществляется синхронизация работы генератора 7 опорных сигналов по оценке задержки принимаемой синхропоследовательности. Оценка задержки вычисляется дифференцирующим блоком 12 по максимуму сигнала на выходе сумматора 11, который вычисляет сумму откликов некогерентных согласованных фильтров 9 и 10, настроенных на сегменты S2 и S1 синхронизирующей последовательности принимаемого сигнала. Некогерентные согласованные фильтры 9 и 10 вычисляют сумму модулей сверток синфазной и квадратурной компонент с выходов блока 6 некогерентных демодуляторов с копиями сегментов синхросигналов, записанных в регистры хранения 53, 57 (копия 82) и регистры хранения 64, 68 (копия 82). Отклики фильтров 9 и 10 суммируются и поступают на входы дифференцирующего блока 12 и порогового блока 13. Область сильной корреляции определяется пороговым блоком 13, по превышении сигналом с выхода сумматора 11 заданного порога. При этом на выходе порогового блока 13 формируется сигнал, разрешающий: запись информации в регистры 38, 39, 40 блока 5 ввода-вывода; формирование кода, соответствующего оценке задержки на выходе дифференцирующего блока 12.

После синхронизации генератора 7 опорных сигналов устройство реализует второй этап декодирования слов блочного кода. На этом этапе синфазная и квадратурная компоненты с выхода блока 6 некогерентных демодуляторов подвергаются обратной перестановке в блоке 1 обратной перестановки; корреляционной обработке на интервале анализа Ta=Nτ сегментов S3(К) в многоканальном некогерентном корреляторе 2; накоплению на интервале Тн=2nτ результатов корреляционной обработки повторяющихся сегментов и вычислению блоком 4 принятия решения кода принимаемого блока данных по номеру канала многоканального накопителя 3 с максимальной корреляцией. Здесь τ - длительность элементарного дискрета опорной кодовой последовательности.

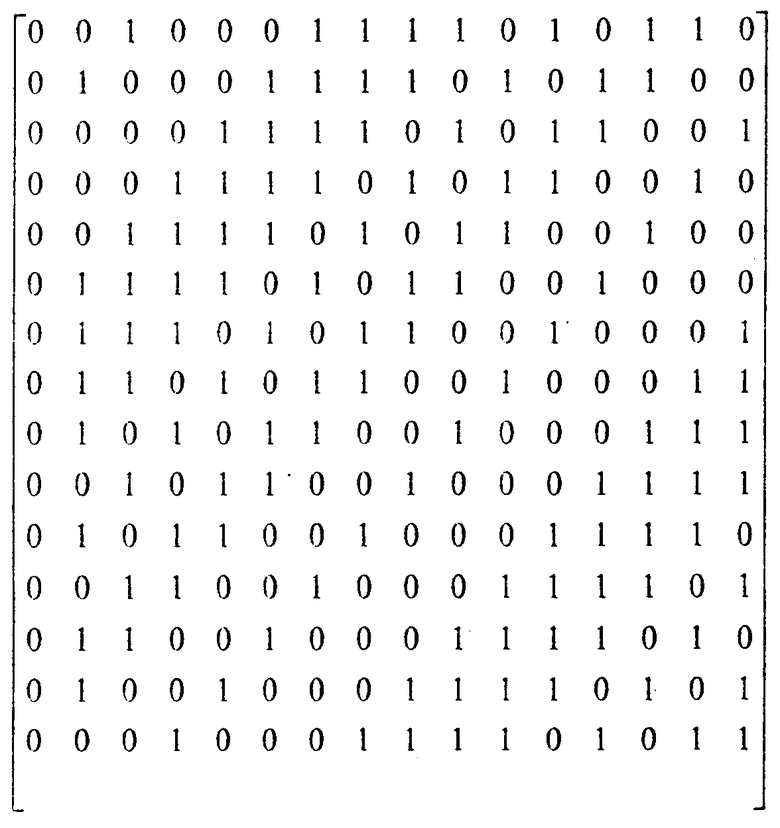

Блок 1 обратной перестановки переставляет отсчеты синфазной и квадратурной компонент по закону преобразования множества сдвигов последовательности S3 в множество сдвигов балансного кода S1. Для рассматриваемого примера перестановка

примененная к столбцам матрицы квазициклических сдвигов последовательности S3

приводит к матрице квазициклических сдвигов балансного кода S1

Каждый канал многоканального некогерентного коррелятора 2 вычисляет сумму модулей корреляции опорной копии квазициклического сдвига S3(К), формируемого генератором 7 опорных сигналов, с синфазной и квадратурной компонентами, поступающими на входы перемножителей 73, 77, 80, 84, 87, 91 с выходов блока 6. В интервале накопления блок 4 принятия решения вычисляет номер канала с многоканального накопителя 3 с максимальным значением и пересчитывает этот номер в код блока данных, который записывается в регистры 38, 39, 40 блока 5 ввода-вывода. После чего задержанным в элементе 101 импульсов происходит обнуление результатов накопления в регистрах 95, 97, 99 многоканального накопителя 3. В конце интервала анализа на установочные входы сумматоров 74, 78, 81, 85, 88, 92 многоканального некогерентного коррелятора 2 поступает задержанный элементом 100 импульс, приводящий к обнулению результатов суммирования.

Применение изобретения позволяет осуществить сегментно модульную корреляционную обработку и согласованную фильтрацию сложных сигналов при значительных расстройках несущих колебаний принимаемого и опорного сигналов. Обычная корреляционная обработка сложных сигналов на интервале [0,Т] без применения следящих систем синхронизации возможна при расстройках

Изобретение за счет сегментно сбалансированной структуры передаваемого сигнала и сегментно модульной корреляционной и согласованной фильтровой обработки при приеме позволяет синхронизировать и декодировать сигнал при более высоких расстройках  частот несущих колебаний принимаемого и опорного сигналов. На фиг.7а показан отклик обычного согласованного фильтра при обработке синхронизирующей последовательности при нулевых расстройках по частоте и фазе несущих колебаний. При увеличении расстройки до величины

частот несущих колебаний принимаемого и опорного сигналов. На фиг.7а показан отклик обычного согласованного фильтра при обработке синхронизирующей последовательности при нулевых расстройках по частоте и фазе несущих колебаний. При увеличении расстройки до величины  при нулевых рассогласованиях начальных фаз обычный согласованный фильтр может иметь подавленную область сильной корреляции (фиг.7б), что делает невозможным синхронизацию и декодирование сложного сигнала. Совокупность сумматора 11, некогерентно согласованных фильтров 9 и 10 реализуют сегментно-модульную согласованную обработку сложного сигнала. Применение сегментно-модульной согласованной обработки позволяет восстановить контрастность области сильной корреляции (фиг.7в) и выполнить оценку задержки синхросигнала и декодирование блочного кода. Минимальное значение максимального пика в области сильной корреляции не падает ниже величины ρ ≥ N, где N - длина сегмента. Формирование передаваемого кадра в случайные моменты времени снижает вероятность столкновения сигналов, передаваемых разными приемопередатчиками, работающими в одном канале распространения.

при нулевых рассогласованиях начальных фаз обычный согласованный фильтр может иметь подавленную область сильной корреляции (фиг.7б), что делает невозможным синхронизацию и декодирование сложного сигнала. Совокупность сумматора 11, некогерентно согласованных фильтров 9 и 10 реализуют сегментно-модульную согласованную обработку сложного сигнала. Применение сегментно-модульной согласованной обработки позволяет восстановить контрастность области сильной корреляции (фиг.7в) и выполнить оценку задержки синхросигнала и декодирование блочного кода. Минимальное значение максимального пика в области сильной корреляции не падает ниже величины ρ ≥ N, где N - длина сегмента. Формирование передаваемого кадра в случайные моменты времени снижает вероятность столкновения сигналов, передаваемых разными приемопередатчиками, работающими в одном канале распространения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНИЯ РАДИОСВЯЗИ С ФАЗОМАНИПУЛИРОВАННЫМ ШПС | 1999 |

|

RU2156541C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| Радиолиния, защищенная от несанкционированного доступа | 2023 |

|

RU2820855C1 |

| ЛИНИЯ РАДИОСВЯЗИ С ПОВЫШЕННОЙ СКРЫТНОСТЬЮ ПЕРЕДАВАЕМОЙ ИНФОРМАЦИИ | 2002 |

|

RU2227370C2 |

| СПОСОБ РЕГИСТРАЦИИ АРТЕРИАЛЬНОГО ДАВЛЕНИЯ И ЧАСТОТЫ ДЫХАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2345704C2 |

| ЦИФРОВОЙ КОРРЕЛЯТОР ПРИЕМНИКА СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2006 |

|

RU2310212C1 |

| ЛИНИЯ СВЯЗИ ДИСКРЕТНОЙ ИНФОРМАЦИИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1999 |

|

RU2165677C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ ПО МНОГОЛУЧЕВОМУ КАНАЛУ СВЯЗИ | 2013 |

|

RU2573586C2 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

Изобретение относится к системам передачи информации шумоподобными ортогональными кодами с фазоманипулированной модуляцией несущей частоты. Достигаемым техническим результатом является формирование в асинхронном режиме передачи сигналов несколькими приемопередатчиками, работающими в одном канале, достаточно длинных фазокодированных сигналов и эффективная их обработка при значительных расстройках несущих частот приемопередатчиков на передающем и приемном пунктах. Для этого устройство содержит блок 1 обратной перестановки, многоканальный некогерентный коррелятор 2, многоканальный накопитель 3, блок 4 принятия решения, блок 5 ввода-вывода, блок 6 некогерентных демодуляторов, генератор 7 опорных сигналов, бинарный квантователь 8, некогерентный согласованный фильтр 9 логически преобразованного кода, некогерентный согласованный фильтр 10 балансного кода, сумматор 11, дифференцирующий блок 12, пороговый блок 13, блок 14 согласования, генератор 15 балансного кода, блок 16 перестановки, блок 17 логического преобразования, блок 18 коммутации, фазовый модулятор 19, усилитель 20, генератор 21 импульсов, фазовращатель 22, формирователь 23 сигналов управления, блок 24 случайной задержки. 7 ил.

Устройство приема и передачи фазоманипулированных кодовых сигналов, содержащее последовательно соединенные фазовый модулятор, усилитель, блок согласования, бинарный квантователь, блок некогерентных демодуляторов, последовательно соединенные генератор импульсов, фазовращатель, синхронный и квадратурный выходы которого подключены к соответствующим входам блока некогерентных демодуляторов, синхронный выход фазовращателя подключен к входу фазового модулятора, второй выход генератора импульсов подключен к входам многоканального некогерентного коррелятора через генератор опорных сигналов, второй выход которого подключен к входу блока принятия решения, выходы которого подключены к входам блока ввода-вывода, который имеет вход и выход для ввода и вывода данных, причем блок согласования подключен к каналу распространения фазоманипулированного сигнала через отдельный вход-выход, отличающееся тем, что дополнительно введены последовательно соединенные генератор балансного кода, блок перестановки, блок логического преобразования, блок коммутации, выход которого подключен к второму входу фазового модулятора, выход генератора балансного кода подключен к вторым входам соответственно блока логического преобразования и блока коммутации, третий вход которого подключен к выходу блока перестановки, второй выход генератора балансного кода подключен к второму входу блока перестановки, входу блока случайной задержки и входу формирователя сигналов управления, один выход которого подключен к третьему входу блока ввода-вывода, второй выход формирователя сигналов управления подключен к четвертому входу блока коммутации и третьему входу блока перестановки, четвертый вход которого подключен к отдельному выходу блока ввода-вывода, дополнительный выход которого подключен к второму входу блока случайной задержки, выход которого подключен к второму входу формирователя сигналов управления, синфазный и квадратурный выходы блока некогерентных демодуляторов подключены к синфазному и квадратурному входам блока обратной перестановки и через некогерентный согласованный фильтр логически преобразованного кода к синхронному и квадратурному входам некогерентного согласованного фильтра балансного кода, выход которого через сумматор подключен ко входу дифференцирующего блока, отдельный выход некогерентного согласованного фильтра логически преобразованного кода подключен к второму входу сумматора, второй выход генератора импульсов подключен к синхронизирующим входам соответственно некогерентного согласованного фильтра логически преобразованного кода, некогерентного согласованного фильтра балансного кода, дифференцирующего блока и порогового блока, выход которого подключен к четвертому входу блока ввода-вывода и через дифференцирующий блок к входу генератора опорных сигналов, синхронизирующий вход многоканального некогерентного коррелятора объединен с синхронизирующими входами соответственно блока обратной перестановки, генератора балансного кода, блока перестановки, блока принятия решения и подключен к второму выходу генератора импульсов, выход сумматора подключен к второму входу порогового блока, выходы блока обратной перестановки, подключены через последовательно соединенные многоканальный некогерентный коррелятор и многоканальный накопитель к второму входу блока принятия решения, второй выход которого подключен к отдельному входу многоканального накопителя, дополнительный вход которого соединен с дополнительными входами блока обратной перестановки, многоканального некогерентного коррелятора и подключен к второму выходу генератора опорных сигналов, причем третий выход формирователя сигналов управления подключен к третьему входу фазового модулятора.

| US 4979183 A 18.12.1990.RU 2109401 C1 20.04.1998.US 5963586 A 05.10.1999.US 4864589 A 05.09.1989.WO 9512938 A 11.05.1995. |

Авторы

Даты

2004-09-10—Публикация

2002-06-20—Подача