Изобретение относится к области средств радионавигации и может быть использовано в цифровых корреляторах приемников сигналов спутниковых радионавигационных систем (СРНС), в частности в цифровых корреляторах приемников сигналов СРНС ГЛОНАСС (Россия) и GPS (США).

Известны приемники сигналов СРНС, работающие одновременно по сигналам СРНС ГЛОНАСС и GPS, описанные в работе [1] - Riley S., Howard N., Aardoom E., Daly P., Silvestrin P. "A Combined GPS/GLONASS High Precision Receiver for Spase Applications"/Pros. Jf ION GPS-95, Palm Springs, CA, US, Sept. 12-15, 1995, p.835-844, а также в патентах: [2] - RU №2146378 (C1), G01S 5/14, 10.03.2000; [3] - RU №2167431 (С2), G01S 5/14, 27.01.2001; [4] - RU №2178894 (C1), G01S 5/14, 27.01.2002; [5] - ЕР №1052786 (A1), G01S 1/00, G01S 5/14, Н04В 7/185, 15.11.2000.

Обобщенная структурная схема этих приемников состоит из блока радиочастотного преобразования, блока многоканальной корреляционной обработки и процессора (вычислителя). Блок радиочастотного преобразования осуществляет усиление принимаемых сигналов до нужного уровня, фильтрацию сигналов от помех, преобразование несущей частоты сигналов с понижением частоты и последующее преобразование сигналов в цифровую форму. Для выполнения этих функций блок радиочастотного преобразования содержит аналоговые фильтры, усилители, преобразователи частоты (аналоговые смесители), аналого-цифровые преобразователи (дискретизаторы), а также формирователи тактовых и гетеродинных сигналов. Операции по частотному преобразованию сигналов и их дискретизации осуществляются в блоке радиочастотного преобразования в раздельных каналах ГЛОНАСС и GPS, что обусловлено различиями между сигналами данных систем, а именно расположением их в разных, хотя и близких, частотных диапазонах, использованием разных псевдослучайных модулирующих кодов и применением разных способов индивидуализации (разделения) сигналов. Так, спутники СРНС GPS излучают сигналы, модулированные индивидуальными псевдослучайными кодами на одной несущей частоте, а спутники СРНС ГЛОНАСС излучают сигналы, модулированные одним и тем же псевдослучайным кодом на индивидуальных несущих (литерных) частотах, лежащих в соседней частотной области. Выходы указанных каналов образуют выходы блока радиочастотного преобразователя. Сигналы с этих выходов, т.е. преобразованные сигналы ГЛОНАСС и GPS, поступают на соответствующие входы блока многоканальной корреляционной обработки. Блок многоканальной корреляционной обработки совместно с процессором осуществляет поиск и слежение за сигналами СРНС, измерение радионавигационных параметров - псевдодальностей и псевдоскоростей объекта относительно спутников, излучающих сигналы СРНС, преобразование радионавигационных параметров в навигационные данные. Каждый из каналов блока многоканальной корреляционной обработки представляет собой цифровой коррелятор, связанный через шину обмена данными с общим для всех каналов процессором, см. [2, фиг.1, 2, блок 2, элементы 31÷3N], [3, фиг.1, 2, блок 2, элементы 31÷3N; [4, фиг.1, блок 2, элементы 31÷3N], [5, фиг.4, блок 3, элементы 41÷4N]. Выполнение цифровых корреляторов, используемых в приемниках сигналов СРНС, является предметом рассмотрения в настоящей заявке.

Цифровые корреляторы, используемые в приемниках сигналов СРНС [1]-[5], выполнены по типовой схеме, представленной в [2, фиг.4], [3, фиг.3], [4, фиг.3], [5, фиг.6]. Аналогичная схема цифрового коррелятора, отличающаяся детализацией выполнения цифрового управляемого генератора несущей, рассмотрена также в [6] - ЕР №1067395 (A1), G01S 1/00, G01S 5/02, Н04В 7/185, 10.01.2001.

В состав типовой схемы цифрового коррелятора приемника сигналов СРНС входят коммутатор сигналов СРНС (ГЛОНАСС или GPS), регистр управления, цифровой управляемый генератор несущей, цифровые смесители синфазного и квадратурного каналов обработки, последовательно соединенные блоки цифровых демодуляторов и накопительные блоки синфазного и квадратурного каналов обработки, а также последовательно соединенные цифровой управляемый генератор кода, генератор опорного кода и программируемая линия задержки, причем накопители накопительных блоков, регистр управления, цифровой управляемый генератор несущей, цифровой управляемый генератор кода и генератор опорного кода связаны через шину обмена данными с процессором. Сигнальные входы коммутатора сигналов СРНС образуют сигнальный вход цифрового коррелятора. Тактовые входы накопителей накопительных блоков, цифрового управляемого генератора кода, цифрового управляемого генератора несущей и программируемой линии задержки образуют тактовый вход цифрового коррелятора. Сигнальные входы цифровых смесителей подключены к выходу коммутатора сигналов СРНС, выходы цифровых смесителей подключены к сигнальным входам блоков цифровых демодуляторов, а опорные входы цифровых смесителей подключены к выходам цифрового управляемого генератора несущей. Управляющие входы программируемой линии задержки, генератора опорного кода и коммутатора сигналов СРНС подключены к соответствующим выходам регистра управления. Опорные входы блоков цифровых демодуляторов подключены к соответствующим выходам программируемой линии задержки.

Основные процедуры, осуществляемые цифровыми корреляторами приемников сигналов СРНС, представленными в [1]-[6], заключаются в корреляции сигнала, поступающего с выхода коммутатора сигналов СРНС, с копией искомого сигнала и накопления результатов корреляции в накопителях накопительных блоков в течение определенного интервала времени. Обычно этот интервал составляет одну миллисекунду, что соответствует длине кодовой псевдослучайной последовательности (ПСП) опорного С/А кода СРНС GPS и ГЛОНАСС. Указанная корреляция осуществляется путем умножения цифровых отсчетов входного сигнала на генерируемую внутри цифрового коррелятора локальную копию искомого сигнала, т.е. копию сигнала выбранного спутника СРНС. Замыкание петель слежения за задержкой опорного кода и частотой сигнала осуществляется с помощью процессора. Процессор считывает информацию из накопителей, обрабатывает ее с помощью соответствующих программ и вырабатывает управляющие сигналы обратной связи для цифровых генераторов несущей и кода, замыкая тем самым петли слежения.

Процедуре слежения предшествует на начальном этапе процедура поиска и обнаружения сигнала. Поиск сигнала осуществляется по двум параметрам - частоте и символам ПСП опорного кода. Совокупность всех позиций поиска по частоте и символам ПСП опорного кода определяет область поиска. Изменение позиций поиска по частоте осуществляется путем дискретного изменения частоты выходных сигналов цифрового управляемого генератора несущей. Изменение позиций поиска по символам ПСП опорного кода осуществляется путем дискретного изменения задержки опорного кода в программируемой линии задержки. Процедура поиска сигнала заключается в последовательном переборе всех частотно-временных позиций области поиска и сравнении накопленных результатов корреляционной обработки с заданным порогом обнаружения.

В цифровых корреляторах приемников сигналов СРНС, представленных в [1]-[6], этот порог устанавливается исходя из заданных вероятностей пропуска и ложной тревоги для наименьшего уровня сигналов. По результатам исследований конкретной частотно-временной позиции принимается решение об отсутствии или наличии сигнала на данной позиции.

Особенностью цифровых корреляторов приемников сигналов СРНС, представленных в [1]-[6], является то, что процедуры сравнения накопленных результатов корреляционной обработки с заданным порогом обнаружения и принятие решения о наличии или отсутствии сигнала производятся процессором, т.е. исключительно с помощью программных средств. Это требует определенных вычислительных ресурсов, увеличивает нагрузку на процессор и сужает возможность его использования для решения дополнительных задач, не связанных с обнаружением сигналов.

Известен цифровой коррелятор приемника сигналов СРНС, описанный в [7] - ЕР №1063536 (A1), G01S 5/14, Н04В 7/185, 27.12.2000 ("Digital correlator for a receptor of signals from satellite radio-navigation systems"), в котором предпринята попытка уменьшить нагрузку на процессор за счет использования двухэтапной процедуры поиска сигнала, суть которого заключается в том, что на первом этапе осуществляется поиск сильного сигнала с использованием обнаружителя сигнала, реализованного аппаратными средствами, а на втором этапе (в случае отрицательного результата на первом этапе) осуществляется стандартный поиск программными средствами. Этот цифровой коррелятор приемника сигналов СРНС принят в качестве прототипа.

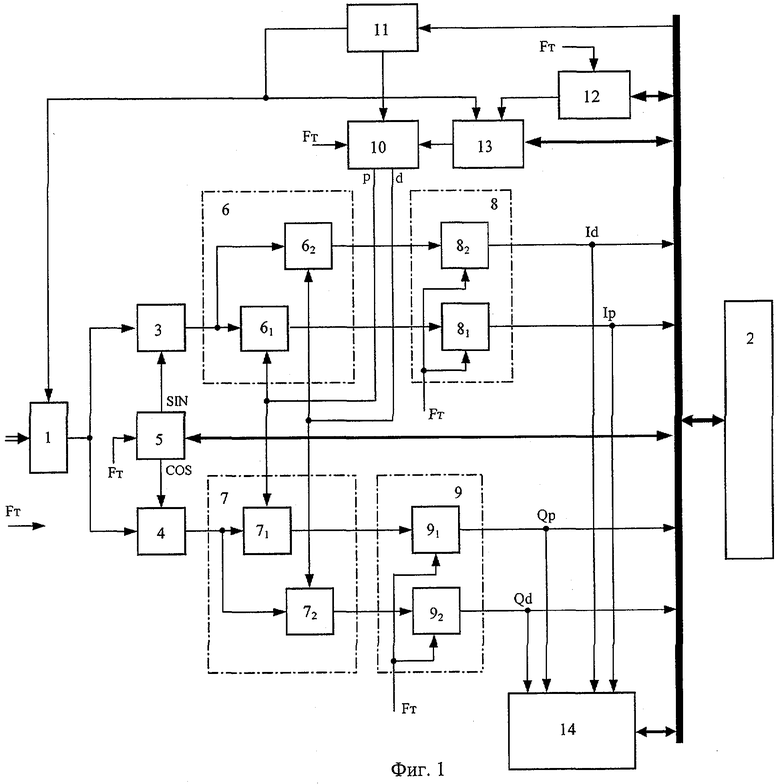

Цифровой коррелятор приемника сигналов СРНС, принятый в качестве прототипа, содержит (см. фиг.1) коммутатор 1 сигналов СРНС, процессор 2, первый 3 и второй 4 цифровые смесители, относящиеся, соответственно, к синфазному и квадратурному каналам обработки, цифровой управляемый генератор 5 несущей, первый 6 и второй 7 блоки цифровых демодуляторов, относящиеся, соответственно, к синфазному и квадратурному каналам обработки, первый 8 и второй 9 накопительные блоки, относящиеся, соответственно, к синфазному и квадратурному каналам обработки, программируемую линию задержки 10, регистр 11 управления, цифровой управляемый генератор 12 кода, генератор 13 опорного кода и обнаружитель сигнала 14.

Блок 6 цифровых демодуляторов содержит группу из двух цифровых демодуляторов 61 и 62, блок 7 цифровых демодуляторов содержит группу из двух цифровых демодуляторов 71 и 72, накопительный блок 8 содержит группу из двух накопителей 81 и 82, а накопительный блок 9 содержит группу из двух накопителей 91 и 92. Сигнальные входы цифровых демодуляторов 61 и 62 соединены между собой и образуют сигнальный вход блока 6, выходы цифровых демодуляторов 61 и 62 образуют группу выходов блока 6, а опорные входы цифровых демодуляторов 61 и 62 образуют группу опорных входов блока 6. Сигнальные входы цифровых демодуляторов 71 и 72 соединены между собой и образуют сигнальный вход блока 7, выходы цифровых демодуляторов 71 и 72 образуют группу выходов блока 7, а опорные входы цифровых демодуляторов 71 и 72. образуют группу опорных входов блока 7.

Выходы накопителей 81 и 82 образуют группу выходов блока 8, сигнальные входы накопителей 81 и 82 образуют группу сигнальных входов блока 8, а соединенные между собой тактовые входы накопителей 81 и 82 образуют тактовый вход блока 8. Выходы накопителей 91 и 92 образуют группу выходов блока 9, сигнальные входы накопителей 91 и 92 образуют группу сигнальных входов блока 9, а соединенные между собой тактовые входы накопителей 91 и 92 образуют тактовый вход блока 9.

Сигнальные входы коммутатора 1 сигналов СРНС образуют сигнальный вход цифрового коррелятора.

Сигнальные входы цифровых смесителей 3 и 4 связаны с выходом коммутатора 1 сигналов СРНС, а их опорные входы связаны, соответственно, с первым и вторым выходами цифрового управляемого генератора 5 несущей.

Сигнальные входы цифровых демодуляторов 6 и 7 связаны с выходами соответствующих цифровых смесителей 3 и 4, а группы их выходов связаны с группами входов соответствующих накопительных блоков 8 и 9.

Группы выходов накопительных блоков 8 и 9 связаны с первой и второй группами сигнальных входов обнаружителя сигналов 14, а также - через шину обмена данными - с процессором 2.

Выход цифрового управляемого генератора 12 кода связан с сигнальным входом генератора 13 опорного кода, выход которого связан с сигнальным входом программируемой линии задержки 10.

Группа из двух выходов управляемой линии задержки 10 связана с группами опорных входов блоков 6 и 7 цифровых демодуляторов. При этом первый выход в этой группе, на котором формируется "точная" ("р") копия опорного кода, связан с опорными входами цифровых демодуляторов 61 и 71, а второй выход в этой группе, на котором формируется "смещенная" ("d") копия опорного кода, связан с опорными входами цифровых демодуляторов 62 и 72. Управляющий вход программируемой линии задержки 10 связан с первым выходом регистра 11 управления, второй выход которого связан с управляющими входами коммутатора 1 сигналов СРНС и генератора 13 опорного кода.

Цифровой управляемый генератор 5 несущей, регистр 11 управления, цифровой управляемый генератор 12 кода, генератор 13 опорного кода и обнаружитель сигнала 14 связаны через шину обмена данными с процессором 2.

Тактовые входы цифрового управляемого генератора 5 несущей, накопительных блоков 8 и 9, программируемой линии задержки 10, цифрового управляемого генератора 12 кода связаны с тактовым входом цифрового коррелятора.

Обнаружитель сигнала 14 реализует в прототипе функцию простого модульного обнаружителя, осуществляющего сравнение по отдельности модулей результатов корреляционной обработки в синфазном и квадратурном каналах с первым порогом и их сумм с вторым порогом.

В обобщенном виде работа коррелятора-прототипа осуществляется следующим образом. На входы коммутатора 1 сигналов СРНС поступают выборки сигналов СРНС ГЛОНАСС и GPS, формируемые аналого-цифровыми преобразователями блока радиочастотного преобразования приемника сигналов СРНС. В соответствии с командой процессора 2, выдаваемой в регистр 11 управления, коммутатор 1 сигналов СРНС подключает на свой выход сигналы одной из СРНС - ГЛОНАСС или GPS. Сигналы выбранной СРНС поступают на сигнальные входы цифровых смесителей 3 и 4, на опорные входы которых поступают квадратурные сигналы ("SIN" и "COS") опорной частоты с соответствующих выходов цифрового управляемого генератора 5 несущей. Цифровой управляемый генератор 5 несущей обеспечивает формирование квадратурных сигналов промежуточной частоты заданной литеры СРНС ГЛОНАСС, двоичный код которой выдается процессором 2, или промежуточной частоты сигналов СРНС GPS. Цифровые смесители 3 и 4 обеспечивают выделение сигналов заданной литеры СРНС ГЛОНАСС или сигналов спутников СРНС GPS и перенос спектров этих сигналов в основную полосу частот (на нулевую частоту). С выходов цифровых смесителей 3 и 4 сигналы поступают на сигнальные входы блоков 6 и 7 цифровых демодуляторов. На опорные входы блоков 6 и 7 цифровых демодуляторов с первого и второго выходов программируемой линии задержки 10 поступают, соответственно, "точная" ("р") и "смещенная" ("d") копии опорного С/А кода СРНС ГЛОНАСС или GPS. Блоки 6 и 7 цифровых демодуляторов с помощью входящих в их состав цифровых демодуляторов 61, 62 и 71, 72 осуществляют корреляцию принимаемых сигналов с "точной" ("р") и "смещенной" ("d") копиями опорного С/А кода СРНС ГЛОНАСС или GPS. Программируемая линия задержки 10 работает по сигналам, поступающим с выхода генератора 13 опорного кода, формирующего опорные псевдослучайные С/А коды спутников СРНС ГЛОНАСС или GPS. Необходимый для работы генератора 13 сигнал тактовой частоты 1,023 МГц для GPS или 0,511 МГц для ГЛОНАСС подается на его сигнальный вход с выхода цифрового управляемого генератора 12 кода. Выбор вида вырабатываемой псевдослучайной кодовой последовательности и значения тактовой частоты опорного кода осуществляется по командам процессора 2, поступающим через шину обмена данными на генераторы 12 и 13. Результаты корреляции накапливаются в накопительных блоках 8 и 9 в соответствующих накопителях 81, 82 и 91, 92, а именно, накопитель 81 накапливает синфазную компоненту корреляции точной копии сигнала (Ip), накопитель 82 накапливает синфазную компоненту корреляции смещенной копии сигнала (Id), накопитель 91 накапливает квадратурную компоненту корреляции точной копии сигнала (Qp), а накопитель 92 накапливает квадратурную компоненту корреляции смещенной копии сигнала (Qd). Период накопления равен периоду опорного С/А кода, т.е. 1 мс.

Накопленные в накопителях 81, 82, 91, 92 данные (Ip, Qp, Id, Qd) периодически считываются процессором 2, в котором реализуются необходимые алгоритмы обработки сигналов и осуществляется формирование необходимых управляющих команд и данных для осуществления поиска и слежения за сигналом.

В начале процесса поиска процессор 2 исходя из априорной неопределенности временного положения искомого сигнала устанавливает начальную позицию поиска, т.е. задает частоту несущей для цифрового управляемого генератора 5 несущей, частоту кода для цифрового управляемого генератора 12 кода и положение "точной" ("р") и "смещенной" ("d") копий опорного С/А кода СРНС ГЛОНАСС или GPS с помощью регистра 10 управления, а также задает значение порогов для обнаружителя сигнала 14.

Накопленные в накопителях 81, 82, 91, 92 на интервале 1 мс результаты корреляционной обработки Ip, Qp, Id, Qd поступают на сигнальные входы обнаружителя сигнала 14, который осуществляет обнаружение сильного сигнала на первом этапе поиска с помощью своих аппаратных средств. Осуществляется это путем сравнения модулей /Ip/, /Qp/, Ad/, /Qd/ и сумм модулей /Ip/+/Qp/ и /Id/+/Qd/ с заданными порогами. Если в результате сравнений будет выявлено превышение порога, то принимается решение об обнаружении сигнала на данной позиции поиска. Далее осуществляется процедура подтверждения, при завершении которой принимается решение об окончании или продолжении процедуры поиска. Если после обработки всех позиций поиска сигнал не обнаружен, то процесс поиска переходит ко второму этапу - этапу поиска сигнала, реализуемому программными средствами процессора 2 без участия аппаратных средств обнаружителя сигнала 14.

Поиск сигнала на втором этапе осуществляется на тех же позициях, что и на первом этапе. Процессор 2 выдает начальную позицию поиска, т.е. задает частоту несущей для цифрового управляемого генератора 5 несущей, частоту кода для цифрового управляемого генератора 12 кода и положение "точной" ("р") и "смещенной" ("d") копий опорного С/А кода СРНС ГЛОНАСС или GPS с помощью регистра 10 управления. Затем, по истечению 1 мс от начала накопления, процессор 2 считывает информацию со всех накопителей накопительных блоков 8 и 9. Затем осуществляется переход на вторую и последующие позиции поиска. После прохождения всех позиций поиска процессор 2 обрабатывает результаты накоплений, используя заложенный алгоритм, и выносит решение о наличии или отсутствии сигнала на данных позициях.

Таким образом в цифровом корреляторе-прототипе реализуется двухэтапная процедура поиска сигналов - на первом этапе осуществляется поиск сильного сигнала с помощью аппаратных средств обнаружителя сигнала 14, реализующего функцию простого модульного обнаружителя, а на втором этапе (в случае отрицательного результата на первом этапе) осуществляется стандартный поиск сигнала программными средствами процессора 2.

В идеальных условиях при работе с сильными сигналами применение такого цифрового коррелятора дает в приемнике сигналов СРНС выигрыш, по сравнению с аналогами [1]-[6], в части уменьшения времени обнаружения сигнала и уменьшения нагрузки на процессор. В реальных условиях при работе с обычными (достаточно слабыми) сигналами применение такого цифрового коррелятора приводит к увеличению временных затрат на поиск сигнала за счет непроизводительных потерь времени, затрачиваемого на осуществление бесполезного в этом случае первого этапа, без какого-либо уменьшения при этом нагрузки на процессор.

Задачей, на решение которой направлено заявляемое изобретение, является создание цифрового коррелятора приемника сигналов СРНС, в котором задача обнаружения сигнала независимо от его уровня выполняется аппаратными средствами, что позволяет реально разгрузить процессор и использовать его освободившиеся ресурсы для решения дополнительных задач.

Сущность изобретения заключается в следующем. Цифровой коррелятор приемника сигналов СРНС содержит коммутатор сигналов СРНС, сигнальные входы которого образуют сигнальный вход цифрового коррелятора, первый и второй блоки цифровых демодуляторов, каждый из которых содержит группу цифровых демодуляторов, выходы которых образуют группу выходов соответствующего блока цифровых демодуляторов, опорные входы образуют группу опорных входов соответствующего блока цифрового демодулятора, а соединенные между собой сигнальные входы - сигнальный вход соответствующего блока цифровых демодуляторов, первый и второй цифровые смесители, сигнальные входы которых связаны с выходом коммутатора сигналов СРНС, а выходы - с сигнальными входами соответствующих блоков цифровых демодуляторов, первый и второй накопительные блоки, каждый из которых содержит группу накопителей, тактовые входы которых образуют тактовый вход соответствующего накопительного блока, выходы образуют группу выходов соответствующего накопительного блока, а сигнальные входы - группу сигнальных входов соответствующего накопительного блока, связанную с группой выходов соответствующего блока цифровых демодуляторов, обнаружитель сигнала, первая и вторая группы сигнальных входов которого связаны с группами выходов, соответственно, первого и второго накопительных блоков, цифровой управляемый генератор несущей, первый и второй выходы которого связаны с опорными входами, соответственно, первого и второго цифровых смесителей, программируемую линию задержки, выходы которой связаны с группами опорных входов первого и второго блоков цифровых демодуляторов, генератор опорного кода, выход которого связан с сигнальным входом программируемой линии задержки, цифровой управляемый генератор кода, выход которого связан с сигнальным входом генератора опорного кода, регистр управления, выходы которого связаны с управляющими входами программируемой линии задержки, коммутатора сигналов СРНС и генератора опорного кода, а также процессор, связанный через шину обмена данными с цифровым управляемым генератором кода, генератором опорного кода, регистром управления, цифровым управляемым генератором несущей, накопительными блоками и обнаружителем сигнала. При этом тактовые входы накопительных блоков, программируемой линии задержки, цифрового управляемого генератора несущей и цифрового управляемого генератора кода связаны с тактовым входом цифрового коррелятора. В отличие от прототипа, обнаружитель сигнала выполнен в виде квадратурного обнаружителя, реализующего алгоритм вычисления пяти точек шестнадцатиточечного дискретного преобразования Фурье с дополнительными нулями на интервале одной эпохи С/А кода с последующим вычислением модулей результатов преобразования и их некогерентным суммированием и сравнением с переменным порогом, значение которого устанавливается в зависимости от мощности шума и номера некогерентного отсчета, и содержит связанный с процессором через шину обмена данными контроллер, тактовый вход которого связан с тактовым входом цифрового коррелятора, а командный выход - с командным входом генератора опорного кода, мультиплексор, управляющий вход которого связан с соответствующим управляющим выходом контроллера, а первая и вторая группы сигнальных входов, образующие первую и вторую группу сигнальных входов обнаружителя сигнала, связаны с группами выходов соответствующих накопительных блоков, комплексный смеситель, первый и второй сигнальные входы которого связаны с соответствующими выходами мультиплексора, а опорные входы - с соответствующими опорными выходами контроллера, блок когерентного суммирования, первый и второй сигнальные входы которого связаны с соответствующими выходами комплексного смесителя, а управляющий вход - с соответствующим управляющим выходом контроллера, блок вычисления модуля, первый и второй сигнальные входы которого связаны с соответствующими выходами блока когерентного суммирования, а управляющий вход - с соответствующим управляющим выходом контроллера, блок некогерентного суммирования, сигнальный вход которого связан с выходом блока вычисления модуля, а управляющий вход - с соответствующим управляющим выходом контроллера, блок оценки мощности шума, сигнальный вход которого связан с выходом блока вычисления модуля, информационный вход связан с первым выходом блока некогерентного суммирования, управляющий вход связан с соответствующим управляющим выходом контроллера, а выход связан через шину обмена данными с процессором, блок оценки наличия сигнала, сигнальный вход которого связан с вторым выходом блока некогерентного суммирования, выход связан с сигнальным входом контроллера, управляющий вход связан с соответствующим управляющим выходом контроллера, а информационные входы связаны через шину обмена данными с процессором, а также блок определения частотно-временных координат глобального максимума, первый информационный вход которого связан с первым выходом блока некогерентного суммирования, второй информационный вход связан с выходом блока оценки наличия сигнала, управляющий вход связан с соответствующим управляющим выходом контроллера, а выход связан через шину обмена данными с процессором.

В варианте выполнения, имеющем практическое значение, группы накопителей и цифровых демодуляторов в каждом из накопительных блоков и блоков цифровых демодуляторов состоят, соответственно, из К накопителей и К цифровых демодуляторов, где К=16.

Сущность изобретения и возможность его промышленного использования поясняются чертежами и пояснительными материалами, представленными на фиг.1-6, где

на фиг.1 представлена обобщенная структурная схема цифрового коррелятора приемника сигналов СРНС, принятого в качестве прототипа;

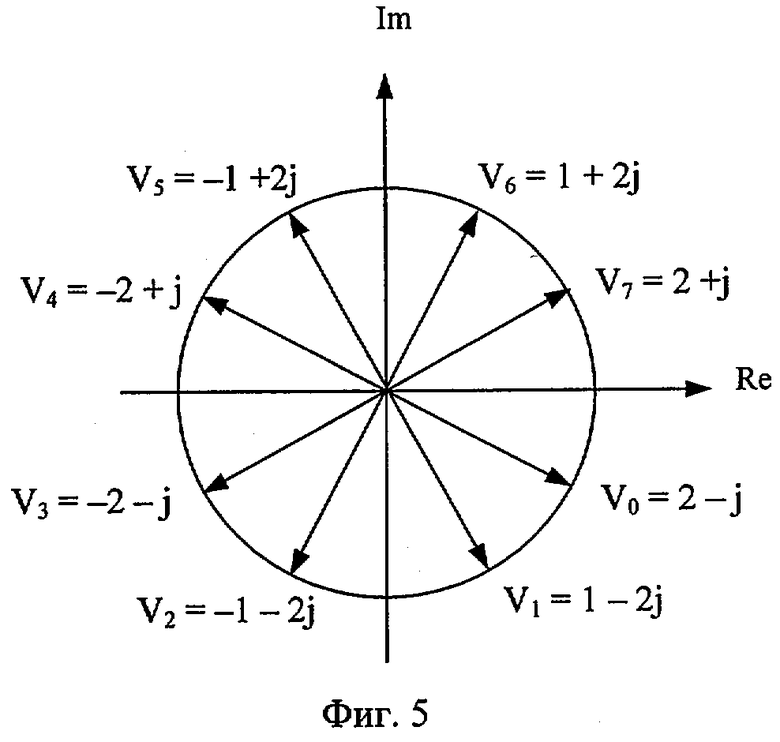

на фиг.2 - обобщенная структурная схема заявляемого цифрового коррелятора приемника сигналов СРНС;

на фиг.3 - обобщенная структурная схема блока оценки мощности шума;

на фиг.4 - обобщенная структурная схема блока оценки наличия сигнала;

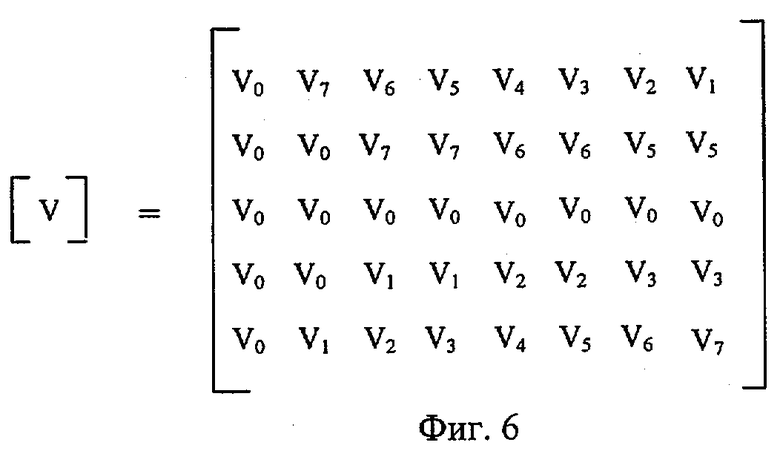

на фиг.5 - графическое изображение набора коэффициентов, используемого в дискретном преобразовании Фурье;

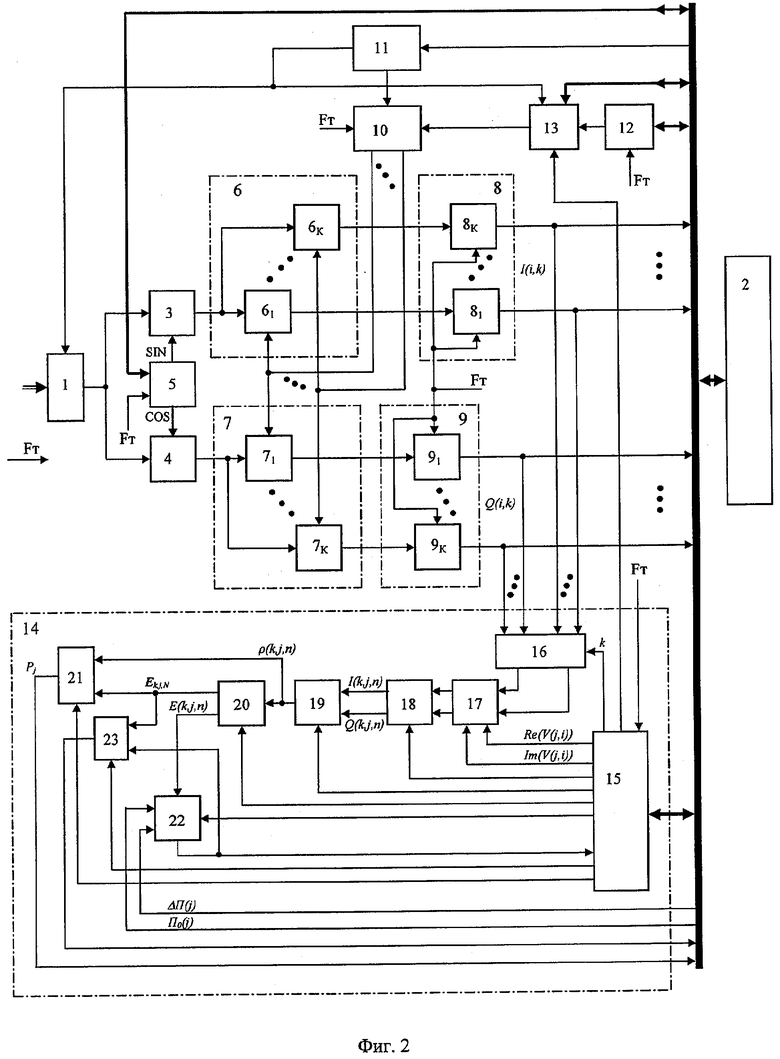

на фиг.6 - матрица коэффициентов, используемых в дискретном преобразовании Фурье.

Заявляемый цифровой коррелятор приемника сигналов СРНС (далее цифровой коррелятор) содержит, см. фиг.2, коммутатор 1 сигналов СРНС, процессор 2, первый 3 и второй 4 цифровые смесители, относящиеся, соответственно, к синфазному и квадратурному каналам обработки, цифровой управляемый генератор 5 несущей, первый 6 и второй 7 блоки цифровых демодуляторов, относящиеся, соответственно, к синфазному и квадратурному каналам обработки, первый 8 и второй 9 накопительные блоки, относящиеся, соответственно, к синфазному и квадратурному каналам обработки, программируемую линию задержки 10, регистр 11 управления, цифровой управляемый генератор 12 кода, генератор 13 опорного кода и обнаружитель сигнала 14.

Блок 6 цифровых демодуляторов содержит группу из К цифровых демодуляторов 61÷6K, блок 7 цифровых демодуляторов содержит группу из К цифровых демодуляторов 71÷7K, накопительный блок 8 содержит группу из К накопителей 81÷8K, а накопительный блок 9 содержит группу из К накопителей 91÷9K, где К=16.

Сигнальные входы цифровых демодуляторов 61÷6K соединены между собой и образуют сигнальный вход блока 6 цифровых демодуляторов, выходы цифровых демодуляторов 61÷6K образуют группу выходов блока 6 цифровых демодуляторов, а опорные входы цифровых демодуляторов 61÷6K образуют группу опорных входов блока 6 цифровых демодуляторов. Сигнальные входы цифровых демодуляторов 71÷7K соединены между собой и образуют сигнальный вход блока 7 цифровых демодуляторов, выходы цифровых демодуляторов 71÷7K образуют группу выходов блока 7 цифровых демодуляторов, а опорные входы цифровых демодуляторов 71÷7K образуют группу опорных входов блока 7 цифровых демодуляторов.

Выходы накопителей 81÷8K образуют группу выходов накопительного блока 8, сигнальные входы накопителей 81÷8K образуют группу сигнальных входов накопительного блока 8, а соединенные между собой тактовые входы накопителей 81÷8K образуют тактовый вход накопительного блока 8. Выходы накопителей 91÷9K образуют группу выходов накопительного блока 9, сигнальные входы накопителей 91÷9K образуют группу сигнальных входов накопительного блока 9, а соединенные между собой тактовые входы накопителей 91÷9K образуют опорный вход накопительного блока 9.

Сигнальные входы коммутатора 1 сигналов СРНС образуют сигнальный вход цифрового коррелятора.

Сигнальные входы цифровых смесителей 3 и 4 связаны с выходом коммутатора 1 сигналов СРНС, а их опорные входы связаны, соответственно, с первым и вторым выходами цифрового управляемого генератора 5 несущей.

Сигнальные входы цифровых демодуляторов 6 и 7 связаны, соответственно, с выходами цифровых смесителей 3 и 4, а группы их выходов связаны, соответственно, с группами входов накопительных блоков 8 и 9.

Группы выходов накопительных блоков 8 и 9 связаны с первой и второй группами сигнальных входов обнаружителя сигналов 14, а также - через шину обмена данными - с процессором 2.

Выход цифрового управляемого генератора 12 кода связан с сигнальным входом генератора 13 опорного кода, выход которого связан с сигнальным входом программируемой линии задержки 10.

Выходы управляемой линии задержки 10 связаны с группами опорных входов блоков 6 и 7 цифровых демодуляторов. Управляющий вход программируемой линии задержки 10 связан с первым выходом регистра 11 управления, второй выход которого связан с управляющими входами коммутатора 1 сигналов СРНС и генератора 13 опорного кода.

Цифровой управляемый генератор 5 несущей, регистр 11 управления, цифровой управляемый генератор 12 кода, генератор 13 опорного кода и обнаружитель сигнала 14 связаны через шину обмена данными с процессором 2.

Тактовые входы цифрового управляемого генератора 5 несущей, накопительных блоков 8 и 9, программируемой линии задержки 10, цифрового управляемого генератора 12 кода и обнаружителя сигнала 14 связаны с тактовым входом цифрового коррелятора.

Обнаружитель сигнала 14 выполнен в виде квадратурного обнаружителя, реализующего алгоритм вычисления пяти точек шестнадцатиточечного дискретного преобразования Фурье с дополнительными нулями на интервале одной эпохи С/А кода с последующим вычислением модулей результатов преобразования и их некогерентным суммированием и сравнением с переменным порогом, значение которого устанавливается в зависимости от мощности шума и номера некогерентного отсчета.

Обнаружитель сигнала 14 содержит контроллер 15, мультиплексор 16, комплексный смеситель 17, блок 18 когерентного суммирования, блок 19 вычисления модуля, блок 20 некогерентного суммирования, блок 21 оценки мощности шума, блок 22 оценки наличия сигнала и блок 23 определения частотно-временных координат глобального максимума.

Контроллер 15 связан через шину обмена данными с процессором 2; тактовый вход контроллера 15, образующий тактовый вход обнаружителя сигнала 14, связан с тактовым входом цифрового коррелятора; командный выход контроллера 15 связан с командным входом генератора 13 опорного кода.

Первая и вторая группы сигнальных входов мультиплексора 16, образующие первую и вторую группу сигнальных входов обнаружителя сигнала, связаны с группами выходов накопительных блоков 8 и 9. Управляющий вход мультиплексора 16 связан с соответствующим управляющим выходом контроллера 15.

Первый и второй сигнальные входы комплексного смесителя 17 связаны с соответствующими выходами мультиплексора 16, а опорные входы - с соответствующими опорными выходами контроллера 15.

Первый и второй сигнальные входы блока 18 когерентного суммирования связаны с соответствующими выходами комплексного смесителя 17, а управляющий вход - с соответствующим управляющим выходом контроллера 15.

Первый и второй сигнальные входы блока 19 вычисления модуля связаны с соответствующими выходами блока 18 когерентного суммирования, а управляющий вход - с соответствующим управляющим выходом контроллера 15.

Сигнальный вход блока 20 некогерентного суммирования связан с выходом блока 19 вычисления модуля, а управляющий вход - с соответствующим управляющим выходом контроллера 15.

Сигнальный вход блока 21 оценки мощности шума связан с выходом блока 19 вычисления модуля, информационный вход связан с первым выходом блока 20 некогерентного суммирования, управляющий вход связан с соответствующим управляющим выходом контроллера 15, а выход связан через шину обмена данными с процессором 2.

Сигнальный вход блока 22 оценки наличия сигнала связан со вторым выходом блока 20 некогерентного суммирования, выход связан с сигнальным входом контроллера 15, управляющий вход связан с соответствующим управляющим выходом контроллера 15, а информационные входы связаны через шину обмена данными с процессором 2.

Первый информационный вход блока 23 определения частотно-временных координат глобального максимума связан с первым выходом блока 20 некогерентного суммирования, второй информационный вход связан с выходом блока 22 оценки наличия сигнала, управляющий вход связан с соответствующим управляющим выходом контроллера 15, а выход связан через шину обмена данными с процессором 2.

В рассматриваемом примере блок 21 оценки мощности шума содержит (фиг.3) блок 24 регистров, состоящий из регистров 241÷24J (J=5), объединенные сигнальные входы которых связаны с выходом сумматора 25, а выходы связаны с соответствующими сигнальными входами мультиплексора 26, а также с соответствующими суммирующими входами блока 27 вычитания, вычитающие входы которого связаны с выходами сумматоров 281÷28J. Входы сумматоров 281÷28J образуют информационный вход блока 21 оценки мощности шума, связанный с первым выходом блока 20 некогерентного суммирования. Первый вход сумматора 25 образует сигнальный вход блока 21 оценки мощности шума, связанный с выходом блока 19 вычисления модуля. Второй вход сумматора 25 связан с выходом мультиплексора 26. Управляющие входы мультиплексора 26 и регистров 241÷24J образуют управляющий вход блока 21 оценки мощности шума, связанный с соответствующим управляющим выходом контроллера 15. Выходы блока 27 вычитания образуют выход блока 21 оценки мощности шума, связанный через шину обмена данными с процессором 2.

В рассматриваемом примере блок 22 оценки наличия сигнала содержит (фиг.4) блок 29 сравнения, выходной регистр 30, блок 31 формирования порога, блок 32 начального значения порога и блок 33 приращения порога. Вход выходного регистра 30 связан с выходом блока 29 сравнения. Выход выходного регистра 30 образует выход блока 22 оценки наличия сигнала, связанный с сигнальным входом контроллера 15 и вторым информационным входом блока 23 определения частотно-временных координат глобального максимума. Сигнальный вход блока 29 сравнения образует сигнальный вход блока 22 оценки наличия сигнала, связанный с вторым выходом блока 20 некогерентного суммирования. Опорный вход блока 29 сравнения связан с выходом блока 31 формирования порога, первый информационный вход которого связан с выходом блока 32 начального значения порога, а второй информационный вход связан с выходом блока 33 приращения порога. Блок 31 формирования порога состоит из регистров 341÷34j (J=5), объединенные сигнальные входы которых связаны с выходом сумматора 35, а выходы связаны с соответствующими сигнальными входами мультиплексора 36, выход которого, образующий выход блока 31 формирования порога, связан с первым входом сумматора 35 и опорным входом блока 29 сравнения. Входы установки начального значения регистров 341÷34J образуют первый информационный вход блока 31 формирования порога, связанный с выходом блока 32 начального значения порога. Второй вход сумматора 35 образует второй информационный вход блока 31 формирования порога, связанный с выходом блока 33 приращения порога. Блок 32 начального значения порога состоит из регистров 371÷37J, объединенные сигнальные входы которых образуют информационный вход блока 32 начального значения порога, а выходы связаны с соответствующими сигнальными входами мультиплексора 38, выход которого связан с первым информационным входом блока 31 формирования порога. Блок 33 приращения порога состоит из регистров 391÷39J, объединенные сигнальные входы которых образуют информационный вход блока 33 приращения порога, а выходы связаны с соответствующими сигнальными входами мультиплексора 40, выход которого связан со вторым информационным входом блока 31 формирования порога. Информационные входы блока 32 начального значения порога и блока 33 приращения порога образуют информационные входы блока 22 оценки наличия сигнала, связанные через шину обмена данными с процессором 2. Управляющие входы регистров 341÷34J, 371÷37J, 391÷39J и мультиплексоров 36, 38, 40 образуют управляющий вход блока 22 оценки наличия сигнала, связанный с соответствующим управляющим выходом контроллера 15.

Цифровой коррелятор имеет два основных режима работы - режим поиска сигнала и режим слежения за сигналом. Режим поиска сигнала характеризуется двумя этапами, на первом из которых осуществляется оценка мощности шума, а на втором - собственно поиск сигнала с использованием переменного порога, значение которого устанавливается в зависимости от результата оценки мощности шума и номера некогерентного отсчета (номера n миллисекундной эпохи С/А кода). Основные особенности осуществления обоих этапов режима поиска сигнала рассматриваются ниже при описании работы блоков 21 оценки мощности шума и 22 оценки наличия сигнала.

В обобщенном виде работа цифрового коррелятора описывается следующим образом. На входы коммутатора 1 сигналов СРНС поступают выборки действительных сигналов СРНС ГЛОНАСС и GPS, формируемые аналого-цифровыми преобразователями блока радиочастотного преобразования приемника сигналов СРНС (на фигурах не показано). В соответствии с командой процессора 2, выдаваемой в регистр 11 управления, коммутатор 1 сигналов СРНС подключает на свой выход сигналы одной из СРНС - ГЛОНАСС или GPS. Сигналы выбранной СРНС поступают на сигнальные входы цифровых смесителей 3 и 4, на опорные входы которых поступают квадратурные сигналы ("SIN" и "COS") опорной частоты с соответствующих выходов цифрового управляемого генератора 5 несущей. Цифровой управляемый генератор 5 несущей обеспечивает формирование квадратурных сигналов промежуточной частоты заданной литеры СРНС ГЛОНАСС, двоичный код которой выдается процессором 2, или промежуточной частоты сигналов СРНС GPS. Цифровые смесители 3 и 4 обеспечивают выделение сигналов заданной литеры СРНС ГЛОНАСС или сигналов спутников СРНС GPS и перенос спектров этих сигналов в основную полосу частот (на нулевую частоту). С выходов цифровых смесителей 3 и 4 сигналы поступают на сигнальные входы блоков 6 и 7 цифровых демодуляторов, т.е. на сигнальные входы цифровых демодуляторов 61÷6K и 71÷7K. На группы опорных входов блоков 6 и 7 цифровых демодуляторов, образованных опорными входами цифровых демодуляторов 61÷6K и 71÷7K, с группы выходов программируемой линии задержки 10 поступают К копий опорного кода (С/А кода СРНС ГЛОНАСС или GPS), смещенные друг относительно друга на заданное время задержки, обычно равное половине длительности символа С/А кода. Блоки 6 и 7 цифровых демодуляторов с помощью входящих в их состав цифровых демодуляторов 61÷6K и 71÷7K осуществляют корреляцию синфазной и квадратурной составляющих обрабатываемых сигналов с указанными К копиями опорного кода. Копии опорного кода формируются на основе сигналов, поступающих с выхода генератора 13 опорного кода, формирующего опорные псевдослучайные С/А коды спутников СРНС ГЛОНАСС или GPS. Необходимый для работы генератора 13 сигнал тактовой частоты 1,023 МГц для GPS или 0,511 МГц для ГЛОНАСС подается на его сигнальный вход с выхода цифрового управляемого генератора 12 кода. Выбор вида вырабатываемой псевдослучайной кодовой последовательности и значения тактовой частоты опорного кода осуществляется по командам процессора 2, поступающим через шину обмена данными на генераторы 12 и 13. Результаты корреляции накапливаются в накопительных блоках 8 и 9 в соответствующих накопителях 81÷8K и 91÷9K на интервалах накопления, равных в режиме поиска сигнала 1/8 эпохи С/А кода (т.е. 1/8 мс), а в режиме слежения за сигналом - длительности эпохи С/А кода (т.е. 1 мс).

Накопленные в накопителях 81÷8K и 91÷9K данные (K синфазных и K квадратурных компонент корреляции) поступают на первую и вторую группы сигнальных входов обнаружителя сигнала 14, а также - через шину обмена данными - в процессор 2, в котором реализуются необходимые алгоритмы обработки сигналов и осуществляется формирование необходимых управляющих команд и данных, используемых при осуществлении поиска (обнаружения) сигнала и последующего слежения за сигналом.

В процессе поиска сигнала процессор 2, исходя из априорной неопределенности частотно-временного положения искомого сигнала, последовательно устанавливает необходимые позиции поиска по частоте несущей и по задержке кода и выдает в контроллер 15 диапазон поиска по задержке (число временных позиций, на которых следует искать сигнал) и длительность интервала некогерентной обработки, определяемого заданным числом N миллисекундных эпох. Установка позиций поиска осуществляется путем задания текущей частоты для цифрового управляемого генератора 5 несущей, частоты кода для цифрового управляемого генератора 12 кода и временного положения копий опорного С/А кода СРНС ГЛОНАСС или GPS с помощью регистра 11 управления, генератора 13 опорного кода и программируемой линии задержки 10. На установленных позициях поиска осуществляется рассмотренная выше корреляционная обработка с формированием на выходах накопительных блоков 8 и 9 К пар квадратурных сигналов I(i, k) и Q(i, k), где i - номер интервала внутри эпохи С/А кода (i=1...8); k - номер канала корреляционной обработки, определяемый номером цифрового демодулятора в группах 61÷6K и 71÷7K (k=1...16).

С периодичностью 0,125 мс (8 кГц) квадратурные сигналы I(i, k) и Q(i, k) поступают, соответственно, на первую и вторую группы сигнальных входов обнаружителя сигнала 14, т.е. на первую и вторую группу сигнальных входов мультиплексора 16. Под действием управляющего сигнала, поступающего с контроллера 15, мультиплексор 16 поочередно пропускает на свои выходы пары квадратурных сигналов, относящиеся к одному номеру канала "k" последовательно переходя от первого номера канала (k=1) к последнему (k=16). Исходя из общего числа каналов K=16 частота выходных сигналов мультиплексора 16 составляет 128 кГц.

С выходов мультиплексора 16 указанные пары квадратурных сигналов поступают на первый и второй сигнальные входы комплексного смесителя 17, на опорные входы которого поступают сигналы Re(V(j, i)) и Im(V(j, i)), определяемые матрицей [V] коэффициентов дискретного преобразования Фурье. Комплексный смеситель 17 осуществляет преобразование квадратурных сигналов путем перемножения их значений на значения коэффициентов Фурье. Каждая пара квадратурных отсчетов каждого из K каналов корреляционной обработки на i-м интервале умножается на вектор-столбец матрицы [V], соответствующей этому интервалу. Результаты этого перемножения далее суммируются в блоке 18 когерентного суммирования, формирующего результирующие сигналы осуществленного дискретного преобразования Фурье для пяти частотных бинов j (от англ. "bin" - элемент дискретизации) на интервале одной (n-й) эпохи С/А кода (1 мс). Работа блока 18 когерентного суммирования происходит под действием управляющих сигналов, поступающих с контроллера 15.

В целях уменьшения аппаратурных затрат и уменьшения энергетических потерь предлагается использовать вариант дискретного преобразования Фурье, являющийся усечением стандартного 16-точечного алгоритма дискретного преобразования Фурье с дополнительными нулями (см. [8] - Л.Рабинер, Б.Гоулд. Теория и применение цифровой обработки сигналов. М., Мир, 1978, с.395, 426), который позволяет получать из исходных сигналов I(i, k) и Q(i, k) результаты для пяти частотных бинов, основываясь на 2-битном наборе коэффициентов Фурье. Этот алгоритм отличается от стандартного 16-точечного алгоритма с дополнительными нулями только используемым набором коэффициентов Фурье [V0÷V7], показанным на фиг.5, и матрицей коэффициентов Фурье [V], показанной на фиг.6.

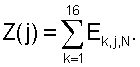

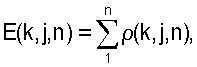

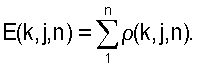

Результаты дискретного преобразования Фурье - выходные сигналы блока 18 когерентного суммирования I(k, j, n) и Q(k, j, n), где n - номер миллисекундной эпохи С/А кода (n=1...255) - поступают на входы блока 19 вычисления модуля, выполняющего функцию определения модуля ρ(k, j, n) квадратурных сигналов I(k, j, n) и Q(k, j, n).

Блок 19 вычисления модуля формирует на своем выходе сигналы ρ(k, j, n), определяющие текущие значения модулей для каждой n-й миллисекундной эпохи С/А кода для каждого j-го частотного бина и каждого k-го канала. В целях уменьшения аппаратурных затрат блок 19 вычисления модуля предлагается выполнить в виде блока, реализующего приближенный алгоритм определения модулей ρ(k, j, n) квадратурных сигналов I(k, j, n) и Q(k, j, n), не требующий операций по извлечению квадратного корня из суммы квадратов слагаемых и обеспечивающий погрешность вычислений не более 4%: ρ=I-I/16+I/64+I/128+Q/4+Q/8+Q/64+Q/128 (для I>Q) (алгоритм Понселе).

С выхода блока 19 вычисления модуля сигналы ρ(k, j, n) поступают на сигнальные входы блока 20 некогерентного суммирования и блока 21 оценки мощности шума.

Работа блока 20 некогерентного суммирования и вид сигналов, формируемых на его первом и втором выходах, зависят от осуществляемого этапа - этапа оценки мощности шума или этапа поиска сигнала.

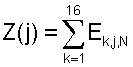

На этапе оценки мощности шума, предваряющем этап поиска сигнала, на каждой новой частотной позиции, задаваемой записью нового значения частоты несущей в цифровой управляемый генератор 5 несущей, блок 20 некогерентного суммирования формирует на своем первом выходе сигналы Еk, j, N, представляющие собой максимальные значения модулей для каждого k-го канала и каждого j-го частотного бина на интервале времени, определяемом заданным числом N миллисекундных эпох. Эти сигналы при осуществлении процедур оценки мощности шума поступают в конце последнего (N-го) цикла некогерентного накопления на информационный вход блока 21 оценки мощности шума, на сигнальный вход которого поступают сигналы ρ(k, j, n) с выхода блока 19 определения модуля.

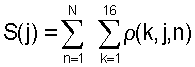

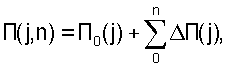

На следующем за этапом оценки мощности шума этапе поиска сигнала блок 20 некогерентного суммирования формирует на своем втором выходе сигналы  представляющие собой нарастающий итог суммирования модулей ρ(k, j, n) по n-м миллисекундным циклам за время некогерентного накопления, определяемое заданным числом N миллисекундных эпох. Эти сигналы при осуществлении процедур поиска и обнаружения полезного сигнала поступают на сигнальный вход блока 22 оценки наличия сигнала, на информационные входы которого поступают вычисленные процессором 2 по результатам оценки мощности шума начальные значения порогов П0(j) и значения их приращений ΔП(j).

представляющие собой нарастающий итог суммирования модулей ρ(k, j, n) по n-м миллисекундным циклам за время некогерентного накопления, определяемое заданным числом N миллисекундных эпох. Эти сигналы при осуществлении процедур поиска и обнаружения полезного сигнала поступают на сигнальный вход блока 22 оценки наличия сигнала, на информационные входы которого поступают вычисленные процессором 2 по результатам оценки мощности шума начальные значения порогов П0(j) и значения их приращений ΔП(j).

Основные особенности этапа оценки мощности шума определяются работой блока 21 оценки мощности шума (фиг.3) и заключаются в следующем.

На информационный вход блока 21 оценки мощности шума на этапе оценки мощности шума с первого выхода блока 20 некогерентного суммирования в конце последнего (N-го) цикла некогерентного накопления поступают сигналы Еk, j, N представляющие собой, как указано выше, максимальные значения модулей для каждого k-го канала и каждого j-го частотного бина на интервале времени, определяемом заданным числом N миллисекундных эпох. Эти сигналы суммируются в блоке 21 оценки мощности шума в сумматорах 281÷28J по всем k каналам для каждого j-го частотного бина. Результаты суммирования  поступают на вычитающие входы блока 27 вычитания.

поступают на вычитающие входы блока 27 вычитания.

На сигнальный вход блока 21 оценки мощности шума, т.е. на первый вход сумматора 25, поступают сигналы ρ(k, j, n), представляющие собой, как указано выше, текущие значения модулей для каждой n-й миллисекундной эпохи С/А кода для каждого j-го частотного бина и k-го канала. Эти сигналы суммируются и накапливаются в регистрах 241÷24J в соответствии со своим частотными бинами на интервале, определяемом заданным числом N миллисекундных эпох. Суммирование осуществляется за счет периодического подключения выходов соответствующих регистров 241÷24J через мультиплексор 26 ко второму входу сумматора 25. Накопленные результаты суммирования  т.e. общие суммы значений модулей ρ(k, j, n) для данного j-го частотного бина, для всех k=16 каналов и всех n=N миллисекундных эпох, в конце последнего (N-го) цикла некогерентного накопления поступают на суммирующие входы блока 27 вычитания, на вычитающие входы которого с выходов сумматоров 281÷28J поступают результаты рассмотренного выше суммирования максимальных значений модулей для всех k=16 каналов

т.e. общие суммы значений модулей ρ(k, j, n) для данного j-го частотного бина, для всех k=16 каналов и всех n=N миллисекундных эпох, в конце последнего (N-го) цикла некогерентного накопления поступают на суммирующие входы блока 27 вычитания, на вычитающие входы которого с выходов сумматоров 281÷28J поступают результаты рассмотренного выше суммирования максимальных значений модулей для всех k=16 каналов

Блок 27 вычитания формирует для каждого частотного бина результаты оценки мощности шума Pj в виде разностей Рj=S(j)-Z(j). Сигналы, определяющие результаты оценки мощности шума, с выхода блока 21 оценки мощности шума через шину обмена данными поступают в процессор 2.

На основании результатов оценки мощности шума процессор 2 вычисляет начальные значения порогов обнаружения и их приращений. Эти данные в виде информационных сигналов П0(j) и ΔП(j) в начале этапа поиска сигнала поступают в блок 22 оценки наличия сигнала.

Основные особенности этапа поиска и обнаружения полезного сигнала определяются работой блока 22 оценки наличия сигнала (фиг.4). Блок 22 реализует усеченную последовательную однопороговую процедуру обнаружения сигнала. Эта процедура заключается в том, что поступающие на сигнальный вход блока 22 сигналы  представляющие собой, как указано выше, нарастающий итог суммирования модулей ρ(k, j, n) по n-м миллисекундным циклам за время некогерентного накопления, определяемое заданным числом N, при каждом значении n сравниваются с нарастающим порогом

представляющие собой, как указано выше, нарастающий итог суммирования модулей ρ(k, j, n) по n-м миллисекундным циклам за время некогерентного накопления, определяемое заданным числом N, при каждом значении n сравниваются с нарастающим порогом  формируемым в блоке 22 на основе входных данных П0(j) и ΔП(j), и по результатам сравнения вырабатывается выходной сигнал, свидетельствующий об обнаружении или отсутствии полезного сигнала. При этом, если при каком-то значении n величины E(k, j, n) для всех каналов k и частотных бинов j оказываются ниже порога, то принимается решение об отсутствии полезного сигнала на данной частотно-временной позиции. Если же хотя бы в одном частотном бине j одного из каналов k величина E(k, j, n) оказывается выше порога, то процесс некогерентного накопления продолжается до момента n=N, при этом фиксируется наличие сигнала в том частотном бине того канала, в котором значение E(k, j, n)≥П(j, N). Указанное сравнение осуществляется с помощью блока 29 сравнения, а хранение сигнала, несущего информацию об обнаружении или отсутствии полезного сигнала в каждом частотном бине каждого канала, осуществляется с помощью выходного регистра 30.

формируемым в блоке 22 на основе входных данных П0(j) и ΔП(j), и по результатам сравнения вырабатывается выходной сигнал, свидетельствующий об обнаружении или отсутствии полезного сигнала. При этом, если при каком-то значении n величины E(k, j, n) для всех каналов k и частотных бинов j оказываются ниже порога, то принимается решение об отсутствии полезного сигнала на данной частотно-временной позиции. Если же хотя бы в одном частотном бине j одного из каналов k величина E(k, j, n) оказывается выше порога, то процесс некогерентного накопления продолжается до момента n=N, при этом фиксируется наличие сигнала в том частотном бине того канала, в котором значение E(k, j, n)≥П(j, N). Указанное сравнение осуществляется с помощью блока 29 сравнения, а хранение сигнала, несущего информацию об обнаружении или отсутствии полезного сигнала в каждом частотном бине каждого канала, осуществляется с помощью выходного регистра 30.

Формирование указанного нарастающего порога  осуществляется следующим образом. Начальные значения порогов П0(j) для каждого j-го частотного бина записываются в соответствующие регистры 371÷37J блока 32 начального значения порога, а значения приращения порогов ΔП0(j) - в соответствующие регистры 391÷39J блока 33 приращения порога. Начальные значения порога, выбираемые мультиплексором 38 для каждого j-го частотного бина, поочередно подаются на первый информационный вход блока 31 формирования порога, где они записываются в соответствующие регистры 341÷34J. Значения приращения порогов, выбираемые мультиплексором 40 для каждого j-го частотного бина, поочередно подаются на второй информационный вход блока 31 формирования порога, т.е. на второй вход сумматора 35. На первый вход сумматора 35 с выхода мультиплексора 36 поочередно поступают текущие значения порогов, хранящиеся в регистрах 341÷34J. В сумматоре 35 осуществляется прибавка приращения к текущему значению порога, после чего новое значение порога записывается в соответствующий регистр 341÷34J. Текущие значения нарастающего порога, определяемые как

осуществляется следующим образом. Начальные значения порогов П0(j) для каждого j-го частотного бина записываются в соответствующие регистры 371÷37J блока 32 начального значения порога, а значения приращения порогов ΔП0(j) - в соответствующие регистры 391÷39J блока 33 приращения порога. Начальные значения порога, выбираемые мультиплексором 38 для каждого j-го частотного бина, поочередно подаются на первый информационный вход блока 31 формирования порога, где они записываются в соответствующие регистры 341÷34J. Значения приращения порогов, выбираемые мультиплексором 40 для каждого j-го частотного бина, поочередно подаются на второй информационный вход блока 31 формирования порога, т.е. на второй вход сумматора 35. На первый вход сумматора 35 с выхода мультиплексора 36 поочередно поступают текущие значения порогов, хранящиеся в регистрах 341÷34J. В сумматоре 35 осуществляется прибавка приращения к текущему значению порога, после чего новое значение порога записывается в соответствующий регистр 341÷34J. Текущие значения нарастающего порога, определяемые как  подаются на опорный вход блока 29 суммирования, на сигнальный вход которого поступают, как указано выше, сигналы

подаются на опорный вход блока 29 суммирования, на сигнальный вход которого поступают, как указано выше, сигналы  Согласованная работа блоков 31, 32 и 33 по формированию нарастающих порогов обеспечивается управляющими сигналами, поступающими с контроллера 15 на управляющий вход блока 22, т.е. на управляющие входы регистров 341÷34J, 371÷37J, 391÷39J и мультиплексоров 36, 38, 40.

Согласованная работа блоков 31, 32 и 33 по формированию нарастающих порогов обеспечивается управляющими сигналами, поступающими с контроллера 15 на управляющий вход блока 22, т.е. на управляющие входы регистров 341÷34J, 371÷37J, 391÷39J и мультиплексоров 36, 38, 40.

При положительном результате поиска формируемый на выходе блока 22 сигнал обнаружения передается на сигнальный вход контроллера 15, который останавливает процесс поиска. При этом в выходном регистре 30 фиксируются номера частотной и временной позиции, на которых обнаружен полезный сигнал, а в блоке 20 некогерентного суммирования для каждого канала и каждой частотной позиции сохраняются последние результаты некогерентного суммирования модулей. Эти данные поступают на информационные входы блока 23 определения частотно-временных координат глобального максимума, который вырабатывает информационные сигналы о частотно-временной позиции этого максимума. Осуществляется это путем попарного сравнения результатов некогерентного накопления для тех частотных бинов (j) и каналов (k), на которых обнаружен сигнал, и информация о которых передается на второй информационный вход блока 23 определения частотно-временных координат глобального максимума с выхода блока 22 оценки наличия сигнала (т.е. с выходного регистра 30). Информационные сигналы, формируемые блоком 23 определения частотно-временных координат глобального максимума, вместе с сообщением об обнаружении сигнала, формируемого контроллером 15, передаются в процессор 2 для перевода цифрового коррелятора в режим слежения за обнаруженным сигналом.

Если же полезный сигнал не обнаружен, то блок 22 оценки наличия сигнала передает в контроллер 15 признак отсутствия сигнала на заданных k×j частотно-временных позициях. В этом случае контроллер 15 выдает в генератор 13 опорного кода команду на задержку опорного кода на K временных позициях, уменьшает на единицу заданный в начале режима поиска диапазон поиска по задержке, приводит в исходное состояние все блоки обнаружителя сигнала 14 и начинает поиск сигнала на той же самой частотной позиции, установленной в цифровом управляемом генераторе 5 несущей (на тех же пяти частотных бинах), но на новых K временных позициях. Если сигнал не будет обнаружен во всем заданном диапазоне поиска по задержке, то контроллер 15 выдает в процессор 2 признак отсутствия сигнала и останавливает работу обнаружителя сигнала 14 до получения от процессора 2 нового задания.

Таким образом, из рассмотренного следует, что заявляемое изобретение технически осуществимо и решает поставленную задачу по созданию цифрового коррелятора приемника сигналов СРНС, в котором задача обнаружения сигнала (независимо от его уровня) выполняется аппаратными средствами, что позволяет реально разгрузить процессор и использовать его освободившиеся ресурсы для решения дополнительных задач. При этом за счет использования большого числа частотно-временных позиций, на которых производится поиск, определяемых произведением J×K, где J=5, K=16, а также за счет обеспечения возможности оценки уровня шума, предоставляющей данные для расчета порогов в процессоре, обеспечивается ускорение поиска и обнаружения сигналов по сравнению с прототипом и аналогами.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОИСКА СИГНАЛОВ СПУТНИКОВ В МНОГОКАНАЛЬНОМ ПРИЕМНИКЕ СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2006 |

|

RU2318221C1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2167431C2 |

| ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С УСТРОЙСТВОМ БЫСТРОГО ПОИСКА НАВИГАЦИОННЫХ СИГНАЛОВ В УСЛОВИЯХ ВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2006 |

|

RU2341898C2 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2001 |

|

RU2205417C2 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

| ИНТЕГРИРОВАННЫЙ ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2146378C1 |

| Многочастотный приемник сигналов Глобальных Навигационных Спутниковых Систем | 2021 |

|

RU2787076C1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР И ПРИЕМНИК НАВИГАЦИОННЫЙ | 2008 |

|

RU2388009C2 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1994 |

|

RU2079148C1 |

Изобретение относится к области средств радионавигации и может быть использовано в цифровых корреляторах приемников сигналов спутниковых радионавигационных систем (СРНС), в частности в цифровых корреляторах приемников сигналов СРНС ГЛОНАСС (Россия) и GPS (США). Технический результат - обеспечение ускорения поиска и обнаружения сигналов. В цифровом корреляторе обнаружение полезного сигнала осуществляется аппаратными средствами, что позволяет разгрузить процессор и использовать его освободившиеся ресурсы для решения дополнительных задач. Цифровой коррелятор содержит коммутатор сигналов СРНС, процессор, цифровые смесители, цифровой управляемый генератор несущей, блоки цифровых демодуляторов, накопительные блоки, программируемую линию задержки, регистр управления, цифровой управляемый генератор кода, генератор опорного кода и обнаружитель сигнала. Обнаружитель сигнала выполнен в виде квадратурного обнаружителя, реализующего алгоритм вычисления пяти точек шестнадцатиточечного дискретного преобразования Фурье с дополнительными нулями на интервале одной эпохи С/А кода с последующим вычислением модулей результатов преобразования и их некогерентным суммированием и сравнением с переменным порогом, значение которого устанавливается в зависимости от мощности шума и номера некогерентного отсчета. Обнаружитель сигнала содержит контроллер, мультиплексор, комплексный смеситель, блок когерентного суммирования, блок вычисления модуля, блок некогерентного суммирования, блок оценки мощности шума, блок оценки наличия сигнала и блок определения частотно-временных координат глобального максимума. 1 з.п. ф-лы, 6 ил.

| Постоянная литейная форма | 1981 |

|

SU1063536A1 |

| ЦИФРОВОЙ ГЕНЕРАТОР ДЛЯ ЦИФРОВЫХ СЛЕДЯЩИХ СИСТЕМ КОРРЕЛЯЦИОННОЙ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2180125C1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| БЛОК ПРИЕМНИКА СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ С ВНЕШНЕЙ СИНХРОНИЗАЦИЕЙ | 2003 |

|

RU2250578C1 |

| ИНТЕГРИРОВАННЫЙ ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2146378C1 |

| US 5399984, A, 21.03.1995. | |||

Авторы

Даты

2007-11-10—Публикация

2006-04-04—Подача