Изобретение относится к вычислительной технике, в частности к системам управления распределением данных в информационной сети Государственной автоматизированной системы (ГАС) “Выборы”.

Особенность решаемой технической задачи заключается в том, что при проведении каждой избирательной кампании система управления распределением данных должна выполнять функции, определяемые видом избирательной кампании (референдум, выборы на должность, выборы депутатов, отзыв) и ролью Избирательных комиссий в указанных кампаниях. При этом система управления распределением данных в информационной сети ГАС “Выборы” должна обеспечить согласованное функционирование всех объектов системы за счет передачи и приема различных видов сообщений, автоматического обобщения отдельных видов информации, поступающих от нижестоящих избирательных комиссий. Все эти требования должны быть реализованы в подсистеме автоматизации избирательных процессов.

Для определенности будем рассматривать систему распределения данных в информационной сети ГАС “Выборы на головном объекте системы, который представляет Центральная избирательная комиссия (Центризбирком), а в качестве объектов - источников информации - объекты избирательных комиссий субъектов Российской Федерации (ИКСРФ).

Известны системы, которые могли бы быть использованы для решения поставленной задачи (1, 2).

Первая из известных систем содержит блоки приема и хранения данных, соединенные с блоками управления и обработки данных, блоки поиска и селекции, подключенные к блокам хранения данных и отображения, синхронизирующие входы которых соединены с выходами блока управления (1).

Существенный недостаток данной системы состоит в невозможности решения задачи обновления данных, хранимых в памяти в виде соответствующих документов одновременно с решением задачи выдачи содержания этих документов пользователям в реальном масштабе времени.

Известна и другая система формирования объектов с различными объектными указателями для доступа к набору объектов структуры данных, представляющая собой многозадачную вычислительную систему, содержащую центральный процессор и блоки памяти, подключенные к центральному процессору, блоки обработки данных, содержащие регистры, триггеры и элементы И, ИЛИ, и блоки выдачи данных, соединенные с блоками памяти, центральным процессором и блоками обработки структур данных (2).

Последнее из перечисленных выше технических решений наиболее близко к описываемому.

Его недостаток заключается в невысокой надежности защиты данных от несанкционированного доступа пользователей, что приводит к утечке конфиденциальной информации, функционирующей в системе управления распределением данных.

Цель изобретения - повышение надежности защиты данных путем исключения несанкционированного доступа пользователей к документам, функционирующим в системе.

Поставленная цель достигается тем, что в известную систему, содержащую первый регистр, информационный вход которого является первым информационным входом системы, синхронизирующий вход подключен к выходу первого элемента И, один вход которого является первым синхронизирующим входом системы, а соответствующий выход первого регистра соединен с информационным входом первого блока памяти, первый селектор адреса, информационный вход которого подключен к соответствующему выходу первого регистра, синхронизирующий вход соединен с выходом первого элемента И, второй регистр, информационный вход которого соединен с информационным выходом первого селектора адреса, синхронизирующий выход которого подключен к синхронизирующему входу второго регистра, элементы ИЛИ первой группы, одни входы которых соединены с соответствующим выходом второго регистра, другие входы подключены к выходам соответствующих элементов И первой группы, одни из входов которых являются первым адресным входом системы, а выходы элементов ИЛИ первой группы соединены с адресным входом первого блока памяти, вход управления записью которого подключен к выходу первого элемента задержки, являющемуся первым синхронизирующим выходом системы, вход управления считыванием соединен с выходом второго элемента И, а выход первого блока памяти является первым информационным выходом системы, второй элемент задержки, вход которого соединен с выходом первого элемента задержки, а выход подключен к установочным входам первого и второго регистров и к входу третьего элемента задержки, выход которого соединен с одним входом второго элемента И, выход которого подключен к входу четвертого элемента задержки и к другим входами элементов И первой группы, третий регистр, информационные входы которого являются вторым информационным входом системы, а синхронизирующий вход является вторым синхронизирующим входом системы, первый триггер, единичный вход которого является третьим синхронизирующим входом системы, установочный вход подключен к выходу четвертого элемента задержки, прямой выход первого триггера соединен с другим входом второго элемента И, а инверсный выход подключен к другому входу первого элемента И, пятый элемент задержки, выход которого соединен с входом шестого элемента задержки, элемент ИЛИ, выход которого подключен к установочным входам второго триггера и третьего регистра, третий элемент И, один вход которого соединен с инверсным выходом второго триггера, а другой является четвертым синхронизирующим входом системы, второй блок памяти, адресный вход которого соединен с выходами элементов ИЛИ второй группы, информационный вход является третьим информационным входом системы, а выход подключен к одним входам элементов И блока элементов, выходы которых являются группами информационных выходов системы, введены второй селектор адреса, информационный вход которого соединен с одним выходом третьего регистра, синхронизирующий вход подключен к второму синхронизирующему входу системы, четвертый регистр, информационный вход которого соединен с информационным выходом второго селектора адреса, синхронизирующий выход которого подключен к синхронизирующему входу четвертого регистра, установочный вход которого соединен с выходом элемента ИЛИ, первый компаратор, информационные входы которого соединены с другим выходом третьего регистра и с первым выходом четвертого регистра, синхронизирующий вход первого компаратора подключен к синхронизирующему выходу второго селектора адреса, а один выход подключен к одному входу элемента ИЛИ, второй компаратор, информационные входы которого также соединены с другим выходом третьего регистра и с вторым выходом четвертого регистра, синхронизирующий вход подключен к другому выходу первого компаратора, при этом первый выход второго компаратора соединен с другим входом элемента ИЛИ, а второй выход является вторым синхронизирующим выходом системы, дешифратор, входы которого соединены с третьим выходом четвертого регистра, элементы И второй группы, одни входы которых подключены к четвертому выходу четвертого регистра, другие входы соединены с выходом пятого элемента задержки и с прямым выходом второго триггера, а выходы подключены к одним входам элементов ИЛИ второй группы, элементы И третьей группы, одни входы которых являются вторым адресным входом системы, другие соединены с инверсным выходом второго триггера и с выходом третьего элемента И, а выходы подключены к другим входам элементов ИЛИ второй группы, седьмой элемент задержки, вход которого соединен с выходом третьего элемента И, а выход подключен к входу управления записью второго блока памяти, вход управления считыванием которого соединен с выходом шестого элемента задержки и с другими входами элементов И блока элементов, третьи входы которых подключены к соответствующим выходам дешифратора, и элементы И четвертой группы, одни входы которых соединены с другим выходом третьего регистра, другие входы подключены к второму выходу второго компаратора, а выходы являются вторым информационным выходом системы, при этом второй выход второго компаратора соединен с входом пятого элемента задержки и с единичным входом второго триггера.

Сущность изобретения поясняется чертежами, где на фиг.1 представлена структурная схема устройства, а на фиг.2 - структурная схема селектора адреса.

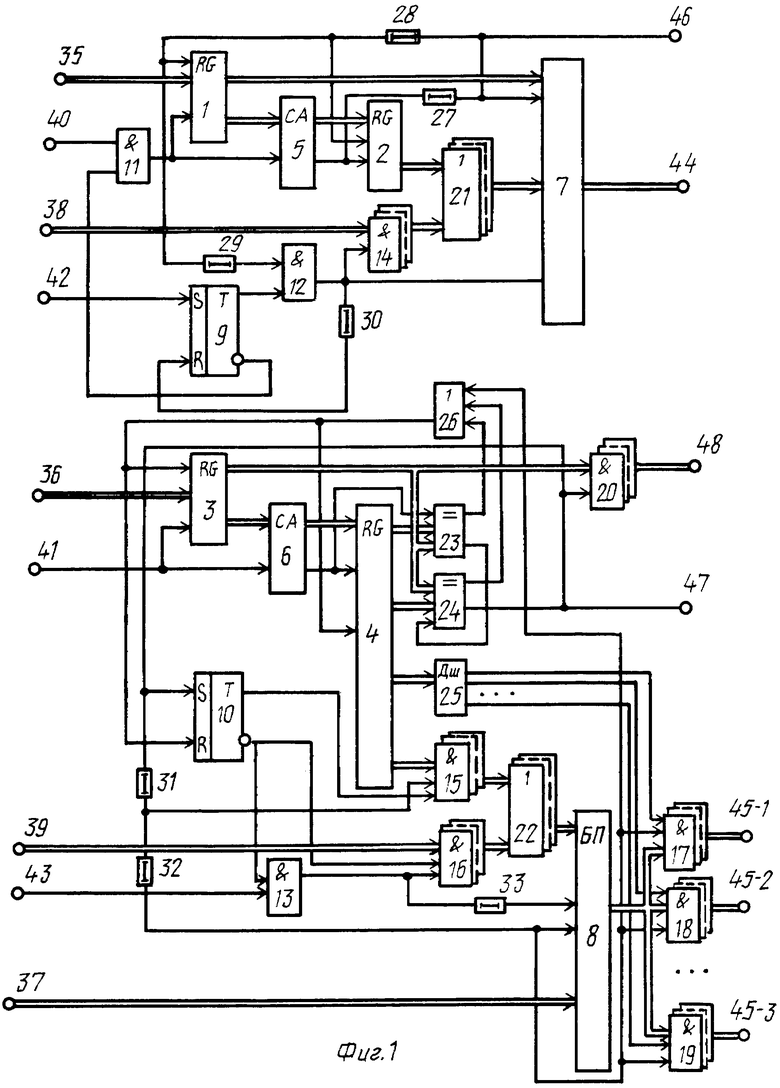

Система (фиг.1) содержит первый 1, второй 2, третий 3 и четвертый 4 регистры, первый 5 и второй 6 селекторы адреса, первый 7 и второй 8 блоки памяти, первый 9 и второй 10 триггеры, первый 11, второй 12 и третий 13 элементы И, первую 14, вторую 15 и третью 16 группы элементов И, блок групп 17, 18 и 19 элементов И, четвертую 20 группу элементов И, первую 21 и вторую 22 группы элементов ИЛИ, первый 23 и второй 24 компараторы, дешифратор 25, элемент 26 ИЛИ, первый 27, второй 28, третий 29, четвертый 30, пятый 31, шестой 32 и седьмой 33 элементы задержки.

На фиг.1 также показаны первый 35, второй 36 и третий 37 информационные входы системы, первый 38 и второй 39 адресные входы системы, первый 40, второй 41, третий 42 и четвертый 43 синхронизирующие входы системы, первый 44 информационный выход системы, выходы 45-1, 45-2, 45-3 группы информационных выходов системы, первый 46 и второй 47 синхронизирующие выходы системы, и второй 48 информационный выход системы.

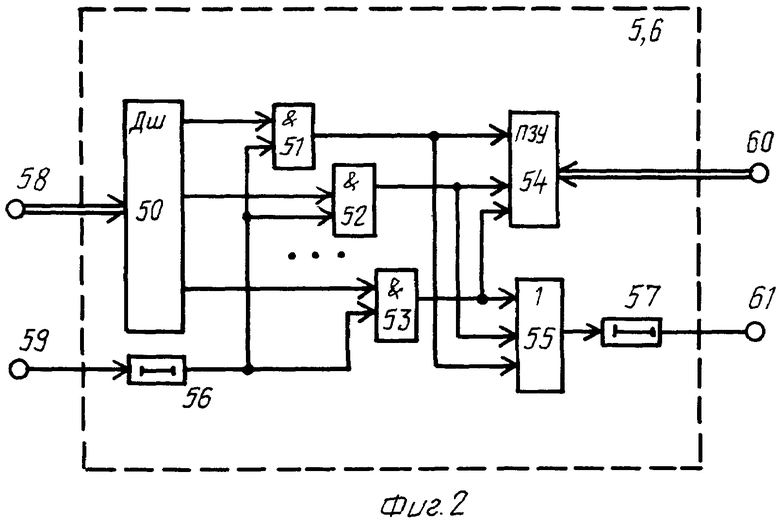

Селектор 5, 6 адреса (фиг.2) содержит дешифратор 50, первый 51, второй 52 и третий 53 элементы И, блок 54 памяти, выполненный в виде постоянного запоминающего устройства, элемент 55 ИЛИ, первый 56 и второй 57 элементы задержки.

На фиг.2 также показаны информационный 58 и синхронизирующий 59 входы селектора адреса и информационный 60 и синхронизирующий 61 выходы селектора адреса.

Все узлы и элементы системы выполнены на стандартных потенциально-импульсных элементах.

Система работает следующим образом.

На информационный вход 35 системы по тракту передачи данных последовательно поступают сообщения (кодограммы) от Избирательных комиссий субъектов Российской Федерации о ходе голосования избирателей в соответствующих субъектах РФ.

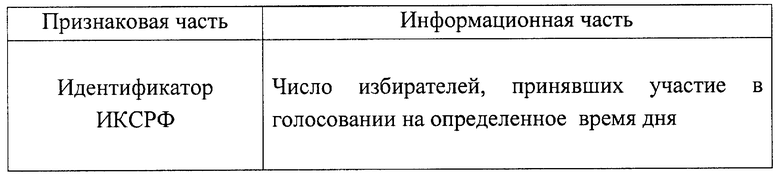

Кодограммы содержат признаковую и информационную части.

Структура кодограммы имеет следующий вид:

Признаковая часть сообщения содержит идентификатор ИКСРФ, приславшего кодограмму, а информационная часть содержит сведения о числе избирателей данного региона, принявших участие в голосовании, и время подведения предварительных итогов.

Код кодограммы с входа 35 заносится в регистр 1 синхронизирующим импульсом с входа 40, который проходит на синхронизирующий вход регистра 1 через элемент 11 И, открытый по второму входу высоким потенциалом с инверсного выхода триггера 9 режима, находящегося в исходном состоянии.

Дешифратор 50 селектора 5 определяет признак принимаемого сообщения, выдавая на один их своих выходов высокий потенциал. Для определенности положим, что высокий потенциал поступил на один вход элемента 51 И.

Параллельно с этим синхронизирующий импульс с выхода элемента 11 И поступает на вход 59 селектора 5, где задерживается элементом 56 на время срабатывания дешифратора 50, и далее опрашивает состояния элементов 51-53 И. Учитывая то обстоятельство, что открытым по одному входу будет только элемент 51 И, то пройдя этот элемент И, синхроимпульс поступает, во-первых, на вход считывания фиксированной ячейки памяти постоянного запоминающего устройства 54, где хранится начальный адрес той зоны памяти блока 7, куда необходимо записать информацию, принятую регистром 1. Во-вторых, тот же импульс считывания на выходе элемента 55 ИЛИ задерживается элементом задержки 57 на время считывания содержимого фиксированной ячейки ПЗУ и затем поступает на синхронизирующий вход регистра 2, фиксируя в нем код адреса зоны памяти.

В-третьих, этот же импульс после задержки элементом 27 на время занесения информации в регистр 2 поступает на вход записи блока 7, записывая информационную часть кодограммы сообщения с информационного выхода регистра 1 по адресу, который с выхода регистра 2 через группу элементов 21 ИЛИ подается на адресный вход блока 7 памяти.

Выход 44 блока 7 памяти соединен с сервером информационной системы (на чертеже не показан), который по сигналу прерывания с выхода 46 после очередного занесения содержимого регистра 1 в блок 7, устанавливает на адресном входе 38 адрес зоны памяти, откуда должна быть считана одна из пришедших кодограмм, и выдает сигнал приема данных на единичный вход триггера 9. Триггер 9, переходя в единичное состояние, закрывает элемент 11 И на время приема кодограммы сервером и открывает элемент 12 И.

Сигнал прерывания сервера с выхода элемента 27 задерживается элементом 28 на время подготовки сервера к приему данных и далее поступает на установочные входы регистров 1 и 2, возвращая их в исходное состояние, и далее после задержки элементом 29 на время установки регистров 1, 2 в исходное состояние поступает на опрос состояния элемента 12 И. Поскольку к этому моменту времени элемент 12 И будет открыт, то импульс с выхода элемента 12 И через элементы 14 И группы и элементы 21 ИЛИ группы установит на адресном входе блока 7 адрес ячейки считывания и осуществит считывание данных через выход 44. После этого тем же импульсом, задержанным элементом задержки 30 на время считывания данных, триггер 9 возвращается в исходное состояние, и система вновь готова к приему очередной кодограммы.

Считанные с блока 7 данные используются сервером в качестве входных данных функциональных задач, решаемых в информационной системе клиент-сервер. По мере решения этих задач полученные результаты в виде соответствующих справок выдаются сервером на информационный вход 37 устройства и далее на информационный вход блока памяти 8.

Должностные лица Избиркома (назовем их пользователями системы), отслеживающие ход избирательных процессов, могут получать обработанные сервером данные только в рамках отведенных им полномочий.

Для этого каждый из них на своем пульте управления (на чертеже не показаны) набирает код идентификатора той справки, которую он хотел бы получить. Код идентификатора справки с входа 36 поступает на часть информационных входов регистра 3, на другую часть информационных входов которого постоянно подан (конструктивно “зашит”) код идентификатора пользователя, который конструктивно скрыт от пользователя, и последний не имеет к нему доступа.

После нажатия пользователем клавиши “Выдать”, на вход 42 поступает синхронизирующий импульс, который заносит в переменную часть регистра 3 код идентификатора справки, который с выхода регистра 3 поступает на вход селектора адреса 6.

Дешифратор 50 селектора 6 расшифровывает код идентификатора пользователя, выдавая на один их своих выходов высокий потенциал. Для определенности положим, что высокий потенциал поступил на один вход элемента 52 И. Параллельно с этим синхронизирующий импульс с входа 42 поступает на вход 59 селектора 6, где задерживается элементом 56 на время срабатывания дешифратора 50, и далее опрашивает состояния элементов 51-53 И. Учитывая то обстоятельство, что открытым по одному входу будет только элемент 52 И, то, пройдя этот элемент И, синхроимпульс поступает, во-первых, на вход считывания фиксированной ячейки памяти постоянного запоминающего устройства 54, где хранится адрес рабочего места пользователя и диапазон идентификаторов справок, которые вправе получить должностное лицо, работающее за данным рабочим местом.

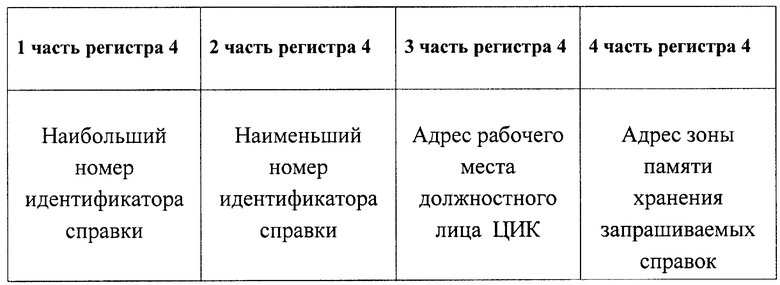

Структура кодограммы имеет следующий вид:

Во-вторых, тот же импульс считывания на выходе элемента 55 ИЛИ задерживается элементом задержки 57 на время считывания содержимого фиксированной ячейки ПЗУ и затем поступает на синхронизирующий вход регистра 4, фиксируя в нем код адреса зоны памяти и диапазон идентификаторов справок, представленный высшим и низшим по номеру идентификаторами.

Наибольший номер идентификатора справки с выхода регистра 4 поступает на одни входы компаратора 23, а наименьший номер - на вход компаратора 24. На другие входы компараторов 23 и 24 с выхода регистра 3 поступает идентификационный номер справки, которую затребовало должностное лицо.

Импульс с выхода 61 селектора 6 поступает на синхронизирующий вход компаратора 23. При этом, если номер требуемой справки больше максимального номера, установленного для этого пользователя, то на выходе “не сравнения” компаратора 23 появляется сигнал, который через элемент 26 ИЛИ проходит на установочный вход регистра 3 и сбрасывает переменную часть этого регистра в исходное состояние, блокируя тем самым выдачу справки.

Если же номер требуемой справки будет равен или меньше максимального, то сигнал появляется на выходе “сравнение” компаратора 23, откуда поступает на синхронизирующий вход компаратора 24, сравнивающего запрашиваемый номер с минимальным по величине номером, доступным данному пользователю. Если запрашиваемый номер больше или равен минимальному, то на выходе “сравнение” компаратора 24 появляется синхронизирующий сигнал, который, во-первых, поступает через выход 47 на вход прерывания сервера в качестве сигнала запроса справки, во-вторых, он поступает на одни входы соответствующих элементов 20 И, на другие входы которых подается код идентификатора справки, и переписывает последний на вход сервера через выход 45.

В третьих, этот же импульс поступает на единичный вход триггера 10, устанавливая его в единичное состояние, при котором он открывает по одному входу элементы 15 И группы, через которые код адреса зоны памяти хранения справки тем же импульсом, задержанным элементом 31, подключается к адресному входу блока 8 памяти. После чего импульсом, задержанным элементом задержки 32 и поступающим на вход считывания блока 8, запрашиваемые данные считываются через соответствующую группу элементов 17-19 и один из выходов 48 на рабочее место должностного лица.

Если же триггер 10 находится в исходном состоянии, то инверсным потенциалом с прямого выхода триггера он блокирует подключение адреса зоны памяти через элементы 15 И к блоку 8. В этом режиме высоким потенциалом с инверсного выхода открыт элемент 13 И и элементы 16 И группы, которые подключают к адресному входу блока 8 адрес зоны памяти выдаваемый сервером на вход 39, а синхронизирующий импульс сервера с входа 43 проходит элемент 13 И и подключает адрес зоны памяти с входа 39 через элементы 16 И группы и элементы 22 ИЛИ группы. Тем же импульсом, задержанным элементом 33 на время установки адреса, осуществляется запись справки, подготовленной сервером по запросу пользователя.

Таким образом, введение новых узлов и блоков и новых конструктивных связей позволило существенно повысить надежность защиты данных системы от несанкционированного использования путем исключения возможности несанкционированного доступа к данным даже со стороны пользователей системы.

Источники информации

1. Патент США №0505651, М. кл. G 06 F 13/40, 13/38, 1992.

2. Патент США №05129083, М. кл. G 06 F 12/00, 15/40, 1992 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РАСПРЕДЕЛЕНИЕМ ДАННЫХ В ИНФОРМАЦИОННОЙ СЕТИ КЛИЕНТ-СЕРВЕР | 2001 |

|

RU2218595C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2276806C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ПОГРАНИЧНОГО КОНТРОЛЯ | 2006 |

|

RU2316811C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ АВТОМАТИЗИРОВАННОЙ СИСТЕМЫ "ГОСУДАРСТВЕННЫЙ РЕГИСТР НАСЕЛЕНИЯ" | 2003 |

|

RU2246130C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРЕДЪЯВЛЕНИЕМ ИНФОРМАЦИИ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248605C2 |

| СИСТЕМА УПРАВЛЕНИЯ ВЫБОРКОЙ И ОБРАБОТКОЙ ДАННЫХ ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2277721C1 |

| АНАЛИТИЧЕСКАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2005 |

|

RU2287186C1 |

| СПРАВОЧНАЯ СИСТЕМА ИНФОРМАЦИОННО-МАРКЕТИНГОВОГО ЦЕНТРА | 2003 |

|

RU2259584C2 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ИДЕНТИФИКАЦИИ ДАННЫХ ПОДПИСНЫХ ЛИСТОВ ИЗБИРАТЕЛЕЙ ГАС "ВЫБОРЫ" | 2005 |

|

RU2279710C1 |

Изобретение относится к вычислительной технике, в частности к системам управления распределения данных в информационной сети Государственной автоматизированной системы “Выборы”. Техническим результатом является повышение надежности защиты данных в системе путем исключения возможности несанкционированного доступа пользователей системы к распределяемым данным. Устройство содержит регистры, блоки памяти, селекторы адреса, компараторы, триггеры, элементы И, элементы ИЛИ, дешифратор, элементы задержки. 2 ил., 2 табл.

Система управления распределением данных в информационной сети ГАС “Выборы”, содержащая первый регистр, информационный вход которого является первым информационным входом системы, синхронизирующий вход подключен к выходу первого элемента И, один вход которого является первым синхронизирующим входом системы, а соответствующий выход первого регистра соединен с информационным входом первого блока памяти, первый селектор адреса, информационный вход которого подключен к соответствующему выходу первого регистра, синхронизирующий вход соединен с выходом первого элемента И, второй регистр, информационный вход которого соединен с информационным выходом первого селектора адреса, синхронизирующий выход которого подключен к синхронизирующему входу второго регистра, элементы ИЛИ первой группы, одни входы которых соединены с соответствующим выходом второго регистра, другие входы подключены к выходам соответствующих элементов И первой группы, одни из входов которых являются первым адресным входом системы, а выходы элементов ИЛИ первой группы соединены с адресным входом первого блока памяти, вход управления записью которого подключен к выходу первого элемента задержки, являющемуся первым синхронизирующим выходом системы, вход управления считыванием соединен с выходом второго элемента И, а выход первого блока памяти является первым информационным выходом системы, второй элемент задержки, вход которого соединен с выходом первого элемента задержки, а выход подключен к установочным входам первого и второго регистров и к входу третьего элемента задержки, выход которого соединен с одним входом второго элемента И, выход которого подключен к входу четвертого элемента задержки и к другим входам элементов И первой группы, третий регистр, информационные входы которого являются вторым информационным входом системы, а синхронизирующий вход является вторым синхронизирующим входом системы, первый триггер, единичный вход которого является третьим синхронизирующим входом системы, установочный вход подключен к выходу четвертого элемента задержки, прямой выход первого триггера соединен с другим входом второго элемента И, а инверсный выход подключен к другому входу первого элемента И, пятый элемент задержки, выход которого соединен с входом шестого элемента задержки, элемент ИЛИ, выход которого подключен к установочным входам второго триггера и третьего регистра, третий элемент И, один вход которого соединен с инверсным выходом второго триггера, а другой является четвертым синхронизирующим входом системы, второй блок памяти, адресный вход которого соединен с выходами элементов ИЛИ второй группы, информационный вход является третьим информационным входом системы, а выход подключен к одним входам элементов И блока элементов, выходы которых являются группами информационных выходов системы, отличающаяся тем, что она содержит второй селектор адреса, информационный вход которого соединен с одним выходом третьего регистра, синхронизирующий вход подключен к второму синхронизирующему входу системы, четвертый регистр, информационный вход которого соединен с информационным выходом второго селектора адреса, синхронизирующий выход которого подключен к синхронизирующему входу четвертого регистра, установочный вход которого соединен с выходом элемента ИЛИ, первый компаратор, информационные входы которого соединены с другим выходом третьего регистра и с первым выходом четвертого регистра, синхронизирующий вход первого компаратора подключен к синхронизирующему выходу второго селектора адреса, а один выход подключен к одному входу элемента ИЛИ, второй компаратор, информационные входы которого также соединены с другим выходом третьего регистра и с вторым выходом четвертого регистра, синхронизирующий вход подключен к другому выходу первого компаратора, при этом первый выход второго компаратора соединен с другим входом элемента ИЛИ, а второй выход является вторым синхронизирующим выходом системы, дешифратор, входы которого соединены с третьим выходом четвертого регистра, элементы И второй группы, одни входы которых подключены к четвертому выходу четвертого регистра, другие входы соединены с выходом пятого элемента задержки и с прямым выходом второго триггера, а выходы подключены к одним входам элементов ИЛИ второй группы, элементы И третьей группы, одни входы которых являются вторым адресным входом системы, другие соединены с инверсным выходом второго триггера и с выходом третьего элемента И, а выходы подключены к другим входам элементов ИЛИ второй группы, седьмой элемент задержки, вход которого соединен с выходом третьего элемента И, а выход подключен к входу управления записью второго блока памяти, вход управления считыванием которого соединен с выходом шестого элемента задержки и с другими входами элементов И блока элементов, третьи входы которых подключены к соответствующим выходам дешифратора, и элементы И четвертой группы, одни входы которых соединены с другим выходом третьего регистра, другие входы подключены к второму выходу второго компаратора, а выходы являются вторым информационным выходом системы, при этом второй выход второго компаратора соединен с входом пятого элемента задержки и с единичным входом второго триггера.

| US 5129083 C1, 07.07.1992 | |||

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| RU 94018467 A1, 20.07.1996 | |||

| Устройство буферной памяти | 1990 |

|

SU1805475A1 |

Авторы

Даты

2004-10-27—Публикация

2003-02-17—Подача