Изобретение относится к вычислительной технике и может быть использовано в отказоустойчивых вычислительных системах.

Известно устройство вызова интерпретированных программ, содержащее два триггера, запоминающее устройство, регистр и два элемента И (Сигналов В.И. Об одном подходе к расширению систем команд однокристального микропроцессора. Управляющие системы и машины, N 4, 1985, с.31-33).

Недостатками такого устройства являются узкие область применения и класс решаемых задач, так как оно может быть использовано для интерпретации команд, отсутствующих в системе команд данного микропроцессора, и не может менять режимы интерпретации в процессе работы микропроцессорной системы, что необходимо в отказоустойчивых системах.

Известно также устройство, содержащее дешифратор, четыре блока постоянной памяти, адресную матрицу, накопительную матрицу, элемент ИЛИ, шинные формирователи, инвертор, группу инверторов (Шевкопляс Б.В. Микропроцессорные структуры, М. Радио и связь, 1986, с.214-215, рис.10.7).

Недостатками такого устройства являются узкие область применения и класс решаемых задач, так как оно позволяет лишь заменять неправильные коды команд на правильные (ячейку на ячейку) и не способно обеспечить замену отказавшей команды на эквивалентные последовательности команд произвольной длины, не содержащие кодов отказавшей команды (а такая возможность вследствие избыточности системы команд имеется почти всегда).

Наиболее близким по технической сущности к предлагаемому является устройство управления памятью, содержащее дешифратор, шинный формирователь, три блока постоянной памяти, два счетчика, два регистра, триггер, схему сравнения, четыре элемента ИЛИ, восемь элементов И, одновибратор, элемент задержки, мультиплексор, причем выходы всех блоков памяти, шинного формирователя, информационные входы первого и второго счетчиков, второго регистра и первый информационный вход мультиплексора подключены к информационному входу-выходу устройства, информационные входы первого регистра, дешифратора, второй информационный вход мультиплексора, адресные входы первого и второго блоков памяти подключены к адресному входу устройства, третий вход первого элемента ИЛИ, третий вход восьмого элемента И и четвертый вход шестого элемента И подключены к входу выборки команды устройства, третий вход второго элемента ИЛИ, входы установки в "0" первого и второго регистров и первого счетчика подключены к входу начальной установки устройства, второй вход первого элемента ИЛИ, вторые входы первого, второго и третьего элемента И подключены к входу записи устройства, первый вход первого элемента ИЛИ подключен к входу чтения устройства, выход первого элемента ИЛИ подключен к входу разрешения дешифратора, второй, третий и четвертый выходы которого подключены соответственно к первым входам первого, второго и третьего элементов И, первый выход дешифратора подключен к входу разрешения обращения второго блока постоянной памяти, выход первого элемента И -- к входу синхронизации второго регистра, выход второго элемента И к входу синхронизации первого счетчика, пятый выход дешифратора к входу разрешения шинного формирователя, шестой выход дешифратора к первым входам четвертого и пятого элементов И, второй вход четвертого элемента И и инверсный вход пятого элемента И к выходу триггера, выход четвертого элемента И к входу разрешения обращения третьего блока памяти, выход пятого элемента И к входу разрешения обращения первого блока памяти, седьмой выход дешифратора к первому входу второго элемента ИЛИ, восьмой выход дешифратора к входу установки в "0" второго счетчика, синхровход которого подключен к выходу третьего элемента И, шестой выход дешифратора к первым входам шестого, седьмого и восьмого элементов И, второй вход шестого элемента И к выходу третьего элемента ИЛИ, третий вход шестого элемента И к входу режима частичной реконфигурации устройства, выход шестого элемента И к первому входу четвертого элемента ИЛИ второй вход седьмого элемента И к входу режима полной реконфигурации устройства, выход седьмого элемента И к второму входу четвертого элемента ИЛИ, второй вход восьмого элемента И подключен к входу режима замещения информации устройства, а выход к третьему входу четвертого элемента ИЛИ, выход которого подключен к стробирующему входу схемы сравнения, выход схемы сравнения подключен к синхровходам триггера и первого регистра, выход которого подключен к информационному входу шинного формирователя, выход признака окончания считывания данных третьего блока памяти к входу элемента задержки, выход которого подключен к входу одновибратора, выход одновибратора подключен к второму входу второго элемента ИЛИ, выход которого подключен к входу установки в "0" триггера, информационный вход которого подключен к входу логической "1" устройства, а выход к вычитающему входу второго счетчика, выходы которого подключены к входам третьего элемента ИЛИ, второй информационный вход мультиплексора подключен к адресному входу устройства, адресный вход мультиплексора к входу задания типа замещаемой информации устройства, выход мультиплексора к первому информационному входу схемы сравнения, второй информационный вход которой подключен к выходу второго регистра, выход первого счетчика к адресному входу третьего блока памяти, вход разрешения обращения которого подключен к счетному входу первого счетчика, вход разрешения счета которого подключен к входу разрешения изменения адреса замещаемой информации устройства (авт.св. СССР N 1679489, кл. G 06 F 12/00, 1989).

Недостатком прототипа являются большие объемы постоянной памяти, необходимые для организации замены отказавшей команды на эквивалентные последовательности оставшихся команд, записанные во втором блоке памяти, велико время выполнения этих замен, т.е. снижается быстродействие вычислительных систем (ВС) в целом, что может сделать невозможным использование известного устройства в многопроцессорных ВС или в управляющих ВС, работающих в реальном масштабе времени. Количество различных команд, привлекаемых для программной замены отказавшей команды, также значительно, что существенно снижает возможности использования прототипа в отказоустойчивых ВС, поскольку для множественных отказов системы команд алгоритмов эквивалентных замен чаще всего просто не существует.

Целью изобретения является сокращение объемов памяти и временных затрат на алгоритмическую реконфи- гурацию.

Цель достигается тем, что в устpойство управления памятью, содержащее дешифратор, шинный формирователь, три блока постоянной памяти, два счетчика, два регистра, триггер, схему сравнения, четыре элемента ИЛИ, восемь элементов И, одновибратор, элемент задержки, мультиплексор, причем выходы третьего блока памяти, шинного формирователя, информационные входы первого и второго счетчиков, второго регистра подключены к информационному входу-выходу устройства, информационные входы первого регистра, дешифратора, второй информационный вход мультиплексора, адресные входы первого и второго блоков памяти подключены к адресному входу устройства, третий вход первого элемента ИЛИ, третий вход восьмого элемента И и четвертый вход шестого элемента И подключены к входу выборки команды устройства, третий вход второго элемента ИЛИ, входы установки в "0" первого и второго регистров и первого счетчика подключены к входу начальной установки устройства, второй вход первого элемента ИЛИ, вторые входы первого, второго и третьего элемента И подключены к входу записи устройства, первый вход первого элемента ИЛИ подключен к входу чтения устройства, выход первого элемента ИЛИ подключен к входу разрешения дешифратора, второй, третий и четвертый выходы которого подключены соответственно к первым входам первого, второго и третьего элементов И, а первый выход дешифратора подключен к входу разрешения обращения второго блока постоянной памяти, выход первого элемента И подключен к входу синхронизации второго регистра, выход второго элемента И к входу синхронизации первого счетчика, пятый выход дешифратора к входу разрешения шинного формирователя, шестой выход дешифратора к первым входам четвертого и пятого элементов И, второй вход четвертого элемента И и инверсный вход пятого элемента И к выходу триггера, выход четвертого элемента И к входу разрешения обращения третьего блока памяти, выход пятого элемента И к входу разрешения обращения первого блока памяти, седьмой выход дешифратора к первому входу блока второго элемента ИЛИ, восьмой выход дешифратора к входу установки в "0" второго счетчика, синхровход которого подключен к выходу третьего элемента И, шестой выход дешифратора к первым входам шестого, седьмого и восьмого элементов И, второй вход шестого элемента И к выходу третьего элемента ИЛИ, третий вход шестого элемента И к входу режима частичной реконфигурации устройства, выход шестого элемента И подключен к первому входу четвертого элемента ИЛИ, второй вход седьмого элемента И к входу режима полной реконфигурации устройства, выход седьмого элемента И к второму входу четвертого элемента ИЛИ, второй вход восьмого элемента И подключен к входу режима замещения информации устройства, а выход к третьему входу четвертого элемента ИЛИ, выход которого подключен к стробирующему входу схемы сравнения, выход схемы сравнения подключен к синхровходам триггера и первого регистра, выход которого подключен к информационному входу шинного формирователя, выход признака окончания считывания данных третьего блока памяти подключен к входу элемента задержки, выход которых подключен к входу одновибратора, выход одновибратора подключен к второму входу второго элемента ИЛИ, выход которого подключен к входу установки в "0" триггера, информационный вход которого подключен к входу логической "1" устройства, а выход к вычитающему входу второго счетчика, выходы которого подключены к входам третьего элемента ИЛИ, адресный вход мультиплексора подключен к входу задания типа замещаемой информации устройства, выход мультиплексора к первому информационному входу сравнения, второй информационный вход которой подключен к выходу второго регистра, выход первого счетчика к адресному входу третьего блока памяти, вход разрешения обращения которого подключен к счетному входу первого счетчика, вход разрешения счета которого подключен к входу разрешения изменения адреса замещаемой информации устройства, введены счетчик, два регистра, группа регистров, группа мультиплексоров, сумматор, элемент НЕ, два блока постоянной памяти, четыре шинных формирователя, одновибратор, элемент ИЛИ-НЕ, три элемента ИЛИ, демультиплексор, группа элементов задержки, три элемента задержки, дешифратор, шесть элементов И, причем вход режима замещения информации подключен к первому входу элемента ИЛИ-НЕ, второй вход которого и первый вход девятого элемента И подключены к входу режима частичной реконфигурации, инверсный вход девятого элемента И подключен к выходу третьего элемента ИЛИ, выход элемента ИЛИ-НЕ подключен к первому входу седьмого элемента ИЛИ, к второму входу которого подключен выход девятого элемента И, выход седьмого элемента ИЛИ подключен к входу элемента НЕ и к входу разрешения второго шинного формирователя, информационный вход которого и первый вход мультиплексора подключены к выходу первого блока памяти, выход элемента НЕ подключен к первым входам десятого и двенадцатого элементов И и к входу разрешения второго дешифратора, вход режима полной реконфигурации устройства подключен к третьему инверсному входу одиннадцатого элемента И и к первому инверсному входу четырнадцатого элемента И, второй вход которого, вторые инверсные входы двенадцатого, тринадцатого элементов И и второй вход пятого элемента ИЛИ подключены к выходу второго одновибратора, выход четырнадцатого элемента И подключен к входу разрешения третьего шинного формирователя, информационный вход которого подключен к выходу третьего регистра, выход третьего шинного формирователя подключен к адресному входу первого блока памяти, выходы второго, четвертого и пятого шинных формирователей подключены к информационному входу-выходу устройства, выход двенадцатого элемента И подключен к входу разрешения четвертого шинного формирователя, информационный вход которого подключен к первому выходу демультиплексора, второй выход которого подключен к информационному входу четвертого регистра, входы установки в "0" третьего и четвертого регистров и первый вход пятого элемента ИЛИ подключены к входу начальной установки устройства, вход задания типа замещаемой информации устройства подключен к второму инверсному входу одиннадцатого элемента И, первый вход которого вход разрешения обращения пятого блока памяти, вход второго элемента задержки и адресный вход демультиплексора подключены к выходу схемы сравнения, выход одиннадцатого элемента И подключен к входу синхронизации четвертого регистра, выходы которого подключены к соответствующим информационным входам всех мультиплексоров группы (т.е. i-ый выход четвертого регистра подключен к i-ым информационным входам всех мультиплексоров группы, i= ; где k количество информационных участков в формате команды, используемых под операнды), информационный вход нулевого регистра группы и нулевые информационные входы мультиплексоров группы подключены соответственно к группе информационных выходов второго блока памяти (т.е. информационный вход нулевого регистра группы подключен к нулевому выходу группы, а нулевой информационный вход i-го мультиплексора группы подключен к i-му информационному выходу группы второго блока памяти), адресные входы мультиплексоров группы подключены к соответствующим выходам четвертого блока памяти, выходы мультиплексоров группы подключены к информационным входам соответствующих регистров группы (т. е. выход i-го мультиплексора группы подключен к информационному входу i-го регистра группы), выходы всех регистров группы подключены соответственно к группе информационных входов пятого шинного формирователя (т.е. выход нулевого регистра группы подключен к нулевому входу группы, а выход i-го регистра группы подключен к i-му входу группы информационных входов пятого шинного формирователя), первый выход первого дешифратора подключен к вторым входам шестого элемента ИЛИ и десятого элемента И, к входам синхронизации всех регистров группы и к первому входу тринадцатого элемента И, выход которого подключен к входу разрешения пятого шинного формирователя, выход признака окончания считывания данных второго блока памяти подключен к входу третьего элемента задержки, выход которого подключен к входу второго одновибратора, выход пятого элемента ИЛИ подключен к входу начальной установки третьего счетчика, к счетному входу которого подключен выход десятого элемента И, выход первого элемента И подключен к первому входу шестого элемента ИЛИ, выход которого подключен к входу четвертого элемента задержки, выход которого подключен к входу разрешения обращения четвертого блока памяти, к второму адресному входу которого подключен выход третьего счетчика, выход второго регистра подключен к первому адресному входу четвертого блока памяти и к информационному входу второго дешифратора, выход которого подключен к адресному входу пятого блока памяти, выход которого подключен к второму входу сумматора, к первому входу которого подключен выход первого регистра, выход сумматора подключен к информационному входу третьего регистра, синхронизирующий вход которого подключен к выходу второго элемента задержки, выход мультиплексора подключен также к входу группы элементов задержки, выход которых подключен к информационному входу демультиплексора.

; где k количество информационных участков в формате команды, используемых под операнды), информационный вход нулевого регистра группы и нулевые информационные входы мультиплексоров группы подключены соответственно к группе информационных выходов второго блока памяти (т.е. информационный вход нулевого регистра группы подключен к нулевому выходу группы, а нулевой информационный вход i-го мультиплексора группы подключен к i-му информационному выходу группы второго блока памяти), адресные входы мультиплексоров группы подключены к соответствующим выходам четвертого блока памяти, выходы мультиплексоров группы подключены к информационным входам соответствующих регистров группы (т. е. выход i-го мультиплексора группы подключен к информационному входу i-го регистра группы), выходы всех регистров группы подключены соответственно к группе информационных входов пятого шинного формирователя (т.е. выход нулевого регистра группы подключен к нулевому входу группы, а выход i-го регистра группы подключен к i-му входу группы информационных входов пятого шинного формирователя), первый выход первого дешифратора подключен к вторым входам шестого элемента ИЛИ и десятого элемента И, к входам синхронизации всех регистров группы и к первому входу тринадцатого элемента И, выход которого подключен к входу разрешения пятого шинного формирователя, выход признака окончания считывания данных второго блока памяти подключен к входу третьего элемента задержки, выход которого подключен к входу второго одновибратора, выход пятого элемента ИЛИ подключен к входу начальной установки третьего счетчика, к счетному входу которого подключен выход десятого элемента И, выход первого элемента И подключен к первому входу шестого элемента ИЛИ, выход которого подключен к входу четвертого элемента задержки, выход которого подключен к входу разрешения обращения четвертого блока памяти, к второму адресному входу которого подключен выход третьего счетчика, выход второго регистра подключен к первому адресному входу четвертого блока памяти и к информационному входу второго дешифратора, выход которого подключен к адресному входу пятого блока памяти, выход которого подключен к второму входу сумматора, к первому входу которого подключен выход первого регистра, выход сумматора подключен к информационному входу третьего регистра, синхронизирующий вход которого подключен к выходу второго элемента задержки, выход мультиплексора подключен также к входу группы элементов задержки, выход которых подключен к информационному входу демультиплексора.

Сущность изобретения заключается в сокращении объемов памяти и временных затрат на алгоритмическую реконфигурацию за счет введения режима алгоритмической реконфигурации по шаблону. Суть нового введенного режима заключается в настройке устройства на анализ считываемых из первого блока постоянной памяти кодов команд, которые признаны неисправными в результате самопроверки внешнего процессора; в исключении считывания во внешний процессор неисправной команды из первого блока памяти в результате перевода выхода второго шинного формирователя в состояние высокого импеданса в условиях обнаружения отказов типа неправильное выполнение отдельных команд и в организации считывания в этом случае исправных команд во внешний процессор из первого блока памяти через первый мультиплексор, демультиплексор и четвертый шинный формирователь; в установке триггера при обнаружении на информационном входе-выходе кода этой команды, который блокирует первый блок постоянной памяти и подключает третий блок постоянной памяти; в записи в первый регистр адреса, на котором возникла реконфигурация команды, а в четвертый регистр самой отказавшей команды; в считывании из третьего блока постоянной памяти соответствующей команды безусловного перехода, которая выполняется внешним процессором, причем адрес требуемой команды определяется настройкой; в обнулении триггера по окончании считывания внешним процессором команды безусловного перехода с целью восстановления возможности чтения операндов из первого блока постоянной памяти; в считывании в режиме алгоритмической реконфигурации из второго блока памяти шаблона программы (состоящего из шаблонов отдельных команд) эквивалентной замены отказавшей команды и синтезе на его основе (с использованием содержимого четвертого регистра) искомой программы эквивалентной замены, выполняемой внешним процессором; в управлении на каждом шаге этого синтеза группой мультиплексоров в соответствии с управляющими кодами четвертого блока памяти для формирования очередной команды программы эквивалентной замены отказавшей команды; в вычислении в сумматоре продвинутого адреса отказавшей команды (т.е. адреса, по которому после завершения эквивалентной замены будет продолжено считывание из первого блока постоянной памяти) и в выдаче его после завершения эквивалентной замены отказавшей команды в режиме алгоритмической реконфигурации на адресный вход первого блока памяти.

Сущность изобретения реализуется следующей совокупностью конструктивных признаков новых элементов и связей, определяющих соответствие заявляемого технического решения критерию "новизна".

Введение третьего счетчика и соответствующих его связей позволяет в режиме алгоритмической реконфигурации по шаблону адресовать четвертый блок памяти с целью выборки шаблонов команд программы эквивалентной замены отказавшей команды.

Введение третьего регистра и соответствующих ему связей позволяет в новом введенном режиме осуществлять хранение продвинутого адреса отказавшей команды и выдачу его на адресный вход первого блока памяти для продолжения работы по основной программе.

Введение четвертого регистра и соответствующих ему связей позволяет в новом введенном режиме осуществлять хранение отказавшей команды и использование ее информационных участков для заполнения шаблонов команд.

Введение группы регистров и соответствующих им связей позволяет в новом введенном режиме осуществлять хранение команд программы эквивалентной замены на каждом шаге синтеза, а также выдачу их во внешний процессор через пятый шинный формирователь.

Введение группы мультиплексоров и соответствующих им связей позволяет в новом введенном режиме осуществлять заполнение шаблонов команд программы эквивалентной замены необходимыми информационными участками отказавшей команды на основе коммутации своих информационных входов в соответствии с управляющими кодами из четвертого блока памяти.

Введение сумматора и соответствующих ему связей позволяет в новом введенном режиме на основе адреса отказавшей команды вычислять продвинутый адрес.

Введение элемента НЕ и соответствующих ему связей позволяет управлять двенадцатым элементом И и входом управления второго дешифратора в условиях обнаружения отказов типа неправильного выполнения отдельных команд.

Введение четвертого блока памяти и соответствующих ему связей позволяет в соответствии с кодом отказавшей команды и значением третьего счетчика управлять группой мультиплексоров в новом введенном режиме в целях заполнения шаблона необходимыми информационными участками отказавшей команды.

Введение пятого блока памяти и соответствующих ему связей позволяет сумматору в новом введенном режиме вычислять продвинутый адрес за счет выдачи ему в качестве второго слагаемого необходимой константы.

Введение второго шинного формирователя и соответствующих ему связей позволяет исключить считывание во внешний процессор неисправных команд, когда обнаружен отказ типа неправильного выполнения отдельных команд.

Введение третьего шинного формирователя и соответствующих ему связей позволяет в новом введенном режиме по окончании эквивалентной замены адресовать первый блок постоянной памяти подвинутым адресом в целях возвращения в основную программу.

Введение четвертого шинного формирователя и соответствующих ему связей позволяет в новом введенном режиме считывать во внешний процессор из первого блока памяти исправные команды в условиях обнаружения отказов типа неправильного выполнения отдельных команд.

Введение пятого шинного формирователя и соответствующих ему связей позволяет в новом введенном режиме считывать во внешний процессор программу эквивалентной замены отказавшей команды, синтезирован- ную на основе шаблона внесением необходимой информации из отказавшей команды.

Введение второго одновибратора и соответствующих ему связей позволяет в новом введенном режиме управлять третьим шинным формирователем для выдачи на адресный вход первого блока памяти продвинутого адреса и обнулять третий счетчик по окончании эквивалентной замены отказавшей команды.

Введение элемента ИЛИ-НЕ и соответствующих ему связей позволяет управлять седьмым элементом ИЛИ во всех режимах работы, кроме настройки.

Введение пятого элемента ИЛИ и соответствующих ему связей позволяет обнулять третий счетчик как после подачи питания на устройство, так и при реализации нового введенного режима.

Введение шестого элемента ИЛИ и соответствующих ему связей позволяет управлять четвертым блоком памяти для обеспечения выдачи им на адресные входы группы мультиплексоров управляющих кодов в целях организации нового введенного режима.

Введение седьмого элемента ИЛИ и соответствующих ему связей позволяет управлять вторым шинным формирователем в целях исключения считывания во внешний процессор неисправной команды из первого блока памяти в условиях обнаружения отказов типа неправильное выполнение отдельных команд.

Введение демультиплексора и соответствующих ему связей позволяет в условиях обнаружения отказов типа неправильное выполнение отдельных команд обеспечить выдачу в четвертый шинный формирователь исправных команд из первого блока памяти, а также запись в четвертый регистр неисправной команды.

Введение группы элементов задержки и соответствующих им связей позволяет выдавать информацию с выхода мультиплексора на информационный вход демультиплексора с задержкой, достаточной для срабатывания схемы сравнения при считывании неисправной команды из первого блока памяти и коммутации (в связи с этим) демультиплексора в условиях обнаружения отказов типа неправильное выполнение отдельных команд.

Введение второго элемента задержки и соответствующих ему связей позволяет управлять записью в третий регистр продвинутого адреса отказавшей команды (используемого в новом введенном режиме) после завершения сумматором вычислений в условиях обнаружения отказов типа неправильное выполнение отдельных команд.

Введение третьего элемента задержки и соответствующих ему связей позволяет управлять вторым одновибратором после надежного считывания из второго блока памяти всего шаблона и завершения синтеза устройством программы эквивалентной замены отказавшей команды в новом введенном режиме.

Введение четвертого элемента задержки и соответствующих ему связей позволяет управлять четвертым блоком памяти на выдачу очередных управляющих кодов на адресные входы группы мультиплексоров после надежного срабатывания третьего счетчика в новом введенном режиме.

Введение второго дешифратора и соответствующих ему связей позволяет в соответствии с кодом неисправной команды адресовать пятый блок памяти в условиях обнаружения отказов типа неправильное выполнение отдельных команд. Без этого дешифратора в блоке пришлось бы задействовать количество ячеек, равное числу возможных команд.

Введение девятого элемента И и соответствующих ему связей позволяет управлять седьмым элементом ИЛИ в режиме частичной алгоритмической реконфигурации.

Введение десятого элемента И и соответствующих ему связей позволяет управлять счетным входом третьего счетчика в новом введенном режиме.

Введение одиннадцатого элемента И и соответствующих ему связей позволяет управлять четвертым регистром для обеспечения записи неисправной команды из демуль- типлексора в новом введенном режиме.

Введение двенадцатого элемента И и соответствующих ему связей позволяет управлять четвертым шинным формирователем для обеспечения считывания во внешний процессор исправной команды в условиях обнаружения отказов типа неправильное выполнение отдельных команд.

Введение тринадцатого элемента И и соответствующих ему связей позволяет управлять пятым шинным формирователем для обеспечения пошагового считывания во внешний процессор из группы регистров команд программы эквивалентной замены, синтезированной в новом введенном режиме.

Введение четырнадцатого элемента И и соответствующих ему связей позволяет управлять третьим шинным формирователем для обеспечения в новом введенном режиме считывания на адресный вход первого блока постоянной памяти продвинутого адреса после завершения синтеза программы эквивалентной замены.

Введение элемента НЕ и соответствующих ему связей позволяет управлять десятым и двенадцатым элементами И и вторым дешифратором в условиях обнаружения отказов типа неправильное выполнение отдельных команд.

Введение новых связей для первого блока памяти позволяет в условиях обнаружения отказов типа неправильное выполнение отдельных команд исключить считыва- ние неисправной команды во внешний процессор, а также обеспечивает автоматическое возвращение в основную программу по завершении эквивалентной замены отказавшей команды.

Введение новых связей для второго блока памяти позволяет обеспечивать новый введенный режим необходимыми шаблонами программ эквивалентных замен отказавших команд, а также управлять третьим элементом задержки по окончании считывания шаблона.

Введение новых связей для первого регистра позволяет использовать адрес отказавшей команды для вычисления в сумматоре продвинутого адреса, используемого по завершении нового введенного режима.

Введение новых связей для второго регистра позволяет в новом введенном режиме адресовать шестой блок памяти в целях выбора соответствующего набора управляющих кодов и управлять вторым дешифратором.

Введение новых связей для схемы сравнения позволяет управлять пятым блоком памяти, вторым элементом задержки, одиннадцатым элементом И и демультиплексором в новом введенном режиме.

Введение новых связей для третьего элемента ИЛИ позволяет управлять девятым элементом И в режиме частичной алгоритмической реконфигурации.

Введение новых связей для мультиплексора позволяет организовать выдачу всей информации из первого блока памяти на вход группы элементов задержки в условиях обнаружения отказов типа неправильное выполнение отдельных команд.

Таким образом, предлагаемое техническое решение соответствует критерию "изобретательский уровень", поскольку в известных устройствах аналоге и прототипе в условиях обнаружения отказов типа неправильное выполнение отдельных команд при осуществлении замены отказавшей команды на эквивалентные последовательности из числа оставшихся не достигается сокращение объемов памяти и временных затрат на выполнение режима алгоритмической реконфигурации вследствие отсутствия указанной выше совокупности конструктивных признаков.

При использовании предлагаемого устройства достигается цель изобретения, состоящая в сокращении объемов памяти и временных затрат на выполнение режима алгоритмической реконфигурации, тем самым расширяются возможности применения предлагаемого устройства в отказоустойчивых ВС.

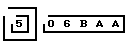

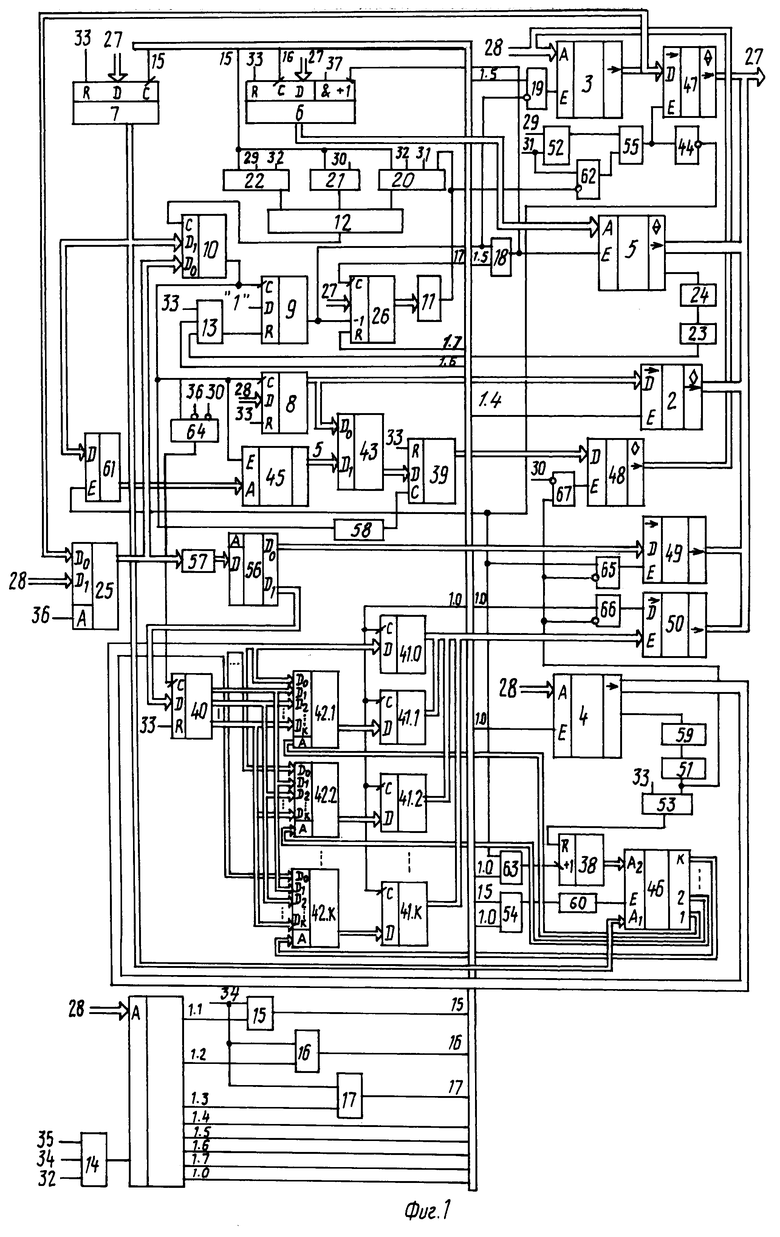

На фиг.1 изображена функциональная схема предлагаемого устройства управления памятью; на фиг.2 временная диаграмма его работы в режиме алгоритмической реконфигурации по шаблону.

Устройство управления памятью содержит первый дешифратор 1, содержащий выходы 1.0-1.7, первый шинный формирователь 2, три блока 3-5 постоянной памяти, первый счетчик 6, два регистра 7, 8, триггер 9, схему 10 сравнения, четыре элемента ИЛИ 11-14, восемь элементов И 15-22, первый одновибратор 23, первый элемент 24 задержки, мультиплексор 25, второй счетчик 26, информационный вход-выход 27, адресный вход 28, вход 29 режима замещения информации, вход 30 режима полной реконфигурации, вход 31 режима частичной реконфигурации, вход 32 выборки команды, вход 33 начальной установки, вход 34 записи, вход 35 чтения, вход 36 задания типа замещаемой информации, вход 37 разрешения изменения адреса замещаемой информации устройства, третий счетчик 38, два регистра 39, 40, группу регистров 41.0-41.k, группу мультиплексоров 42.1-42. k, сумматор 43, элемент НЕ 44, два блока 45, 46 постоянной памяти, четыре шинных формирователя 47-50, второй одновибратор 51, элемент ИЛИ-НЕ 52, три элемента ИЛИ 53-55, демультиплексор 56, группу элементов 57 задержки, три элемента 58-60 задержки, второй дешифратор 61, шесть элементов И 62-67.

Выходы третьего блока 5 памяти, первого 2, второго 47, четвертого 49 и пятого 50 шинных формирователей, информационные входы первого 6 и второго 26 счетчиков, второго регистра 7 подключены к информационному входу-выходу 27 устройства, выход третьего шинного формирователя 48 подключен к адресному входу первого блока 3 памяти. Информационные входы первого регистра 8, дешифратора 1, второй информационный вход D1мультиплексора 25, адресные входы первого 3 и второго 4 блоков памяти подключены к адресному входу 28 устройства. Третий вход первого элемента ИЛИ 14, третий вход восьмого элемента И 22 и четвертый вход шестого элемента И 20 подключены к входу 32 выборки команды устройства. Третий вход второго элемента ИЛИ 13, первый вход пятого элемента ИЛИ 53, входы установки в "0" регистров 7, 8, 39, 40 и первого счетчика 6 подключены к входу 33 начальной установки устройства. Второй вход первого элемента ИЛИ 14, вторые входы первого 15, второго 16 и третьего 17 элементов И подключены к входу 34 записи устройства. Первый вход первого элемента ИЛИ 14 подключен к входу 35 чтения устройства, выход первого элемента ИЛИ 14 подключен к входу разрешения дешифратора 1, второй 1.1, третий 1.2 и четвертый 1.3 выходы которого подключены соответственно к первым входам первого 15, второго 16 и третьего 17 элементов И. Выход первого элемента И 15 подключен к входу синхронизации второго регистра 7 и к первому входу шестого элемента ИЛИ 54, выход второго элемента И 16 подключен к входу синхронизации первого счетчика 6, пятый выход 1.4 дешифратора 1 к входу разрешения первого шинного формирователя 2, шестой выход 1.5 дешифратора 1 к первым входам четвертого 18 и пятого 19 элементов И и к первым входам шестого 20, седьмого 21 и восьмого 22 элементов И. Второй вход четвертого элемента И 18 и инверсный вход пятого элемента И 19 подключены к выходу триггера 9, выход четвертого элемента И 18 к входу разрешения обращения третьего блока 5 памяти, выход пятого элемента И 19 к входу разрешения обращения первого блока 3 памяти, седьмой выход 1.6 дешифратора 1 к первому входу второго элемента ИЛИ 13, восьмой выход 1.7 дешифратора 1 к входу установки в "0" второго счетчика 26, синхровход которого подключен к выходу третьего элемента И 17. Второй вход шестого элемента И 20 подключен к выходу третьего элемента ИЛИ 11, третий вход шестого элемента И 20 к входу 31 режима частичной реконфигурации устройства, выход шестого элемента И 20 к первому входу четвертого элемента ИЛИ 12, второй вход седьмого элемента И 21 к входу 30 режима полной реконфигурации устройства, выход седьмого элемента И 21 к второму входу четвертого элемента ИЛИ 12, второй вход восьмого элемента И 22 к входу 29 режима замещения информации устройства, а выход к третьему входу четвертого элемента ИЛИ 12, выход которого подключен к стробирующему входу схемы 10 сравнения. Выход схемы сравнения подключен к первому входу одиннадцатого элемента И 64, входу разрешения обращения пятого блока 45 памяти, входу второго элемента 58 задержки, а также к синхровходам триггера 9 и первого регистра 8. Выход признака окончания считывания данных третьего блока 5 памяти подключен к входу первого элемента 24 задержки, выход которого подключен к входу первого одновибратора 23. Выход одновибратора 23 подключен к второму входу второго элемента ИЛИ 13, выход которого подключен к входу установки в "0" триггера 9. Информационный вход последнего подключен к входу логической "1" устройства, а выход к вычитающему входу второго счетчика 26, выходы которого подключены к входам третьего элемента ИЛИ 11. Второй информационный вход мультиплексора 25 подключен к адресному входу 28 устройства, адресный вход мультиплексора 25 к входу 36 задания типа замещаемой информации устройства, выход мультиплексора 25 к первому информационному входу Doсхемы 10 сравнения, второй информационный вход которой подключен к выходу второго регистра 7. Выход первого счетчика 6 подключен к адресному входу третьего блока 5 памяти, вход разрешения обращения которого подключен к счетному входу первого счетчика 6. Вход разрешения счета счетчика 6 подключен к входу 37 разрешения изменения адреса замещаемой информации устройства, вход 29 режима замещения информации подключен к первому входу элемента ИЛИ-НЕ 52, второй вход которого и первый вход девятого элемента И 62 подключены к входу 31 режима частичной реконфигурации. Инверсный вход девятого элемента И 62 подключен к выходу третьего элемента ИЛИ 11, выход элемента ИЛИ-НЕ 52 подключен к первому входу седьмого элемента ИЛИ 55, к второму входу которого подключен выход девятого элемента И 62. Выход седьмого элемента ИЛИ 55 подключен к входу элемента НЕ 44 и к входу разрешения второго шинного формирователя 47, информационный вход которого и первый вход мультиплексора 25 подключены к выходу первого блока 3 памяти. Выход элемента НЕ 44 подключен к первым входам десятого 63 и двенадцатого 65 элементов И и к входу разрешения второго дешифратора 61. Вход 30 режима полной реконфигурации устройства подключен к третьему инверсному входу одиннадцатого элемента И 64 и к первому инверсному входу четырнадцатого элемента И 67, второй вход которого, вторые инверсные входы двенадцатого 65, тринадцатого 66 элементов И и второй вход пятого элемента ИЛИ 53 подключены к выходу второго одновибратора 51. Выход четырнадцатого элемента И 67 подключен к входу разрешения третьего шинного формирователя 48, информационный вход которого подключен к выходу третьего регистра 39. Выход третьего шинного формирователя подключен к адресному входу первого блока 3 памяти. Выходы второго 47, четвертого 49 и пятого 50 шинных формирователей подключены к информационному входу-выходу 27 устройства. Выход двенадцатого элемента И 65 подключен к входу разрешения четвертого шинного формирователя 49, информационный вход которого подключен к первому выходу демультиплексора 56. Второй выход последнего подключен к информационному входу четвертого регистра 40. Вход 36 задания типа замещаемой информации устройства подключен к второму инверсному входу одиннадцатого элемента И 64, выход которого подключен к входу синхронизации четвертого регистра 40. Выходы регистра 40 подключены к соответствующим информационным входам всех мультиплексоров 42.1-42.k группы (т.е. i-й выход четвертого регистра 40 подключен к i-м информационным входам всех мультиплексоров 42.1-42. k группы, i= , где k количество информационных участков в формате команды, используемых под операнды). Информационный вход нулевого регистра 41.0 группы и нулевые информационные входы мультиплексоров 41.1-42. k группы подключены соответственно к группе информационных выходов второго блока 4 памяти (т. е. информационный вход нулевого регистра 41.0 группы подключен к нулевому выходу группы, а нулевой информационный вход i-го мультиплексора 41. i группы подключен к i-му информационному выходу группы второго блока 4 памяти). Адресные входы мультиплексоров 42.1-42.k группы подключены к соответствующим выходам четвертого блока 46 памяти, выходы мультиплексоров 42.1-42.k группы подключены к информационным входам соответствующих регистров 41.1-41.k группы (т.е. выход i-го мультиплексора 42.1-42. k группы подключен к информационному входу i-го регистра 41.1-41.k группы). Выходы всех регистров 41.0-41.k группы подключены соответственно к группе информационных входов пятого шинного формирователя 50 (т.е. выход нулевого регистра 41.0 группы подключен к нулевому входу группы, а выход i-го регистра 41.1 группы подключен к i-му входу группы информационных входов пятого шинного формирователя 50). Первый выход 1.0 первого дешифратора 1 подключен к входу разрешения обращения второго блока 4 памяти, к вторым входам шестого 54 и десятого 63 элементов И, к входам синхронизации всех регистров 41.0-41.k группы и к первому входу тринадцатого элемента И 66, выход которого подключен к входу разрешения пятого шинного формирователя 50. Выход признака окончания считывания данных второго блока 4 памяти подключен к входу третьего элемента 59 задержки, выход которого подключен к входу второго одновибратора 51. Выход пятого элемента ИЛИ 53 подключен к входу начальной установки третьего счетчика 38, к счетному входу которого подключен выход десятого элемента И 63. Выход шестого элемента ИЛИ 54 подключен к входу четвертого элемента 60 задержки, выход которого подключен к входу разрешения обращения четвертого блока 46 памяти, к второму адресному входу которого подключен выход третьего счетчика 38. Выход второго регистра 7 подключен к первому адресному входу четвертого блока 46 памяти и к информационному входу второго дешифратора 61, выход которого подключен к адресному входу пятого блока 45 памяти. Выход блока 45 подключен к второму входу сумматора 43, к первому входу которого подключен выход первого регистра 8. Выход сумматора 43 подключен к информационному входу третьего регистра 39, синхронизирующий вход которого подключен к выходу второго элемента 58 задержки. Выход мультиплексора 25 подключен также к входу группы элементов 57 задержки, выход которых подключен к информационному входу демультиплексора 56.

, где k количество информационных участков в формате команды, используемых под операнды). Информационный вход нулевого регистра 41.0 группы и нулевые информационные входы мультиплексоров 41.1-42. k группы подключены соответственно к группе информационных выходов второго блока 4 памяти (т. е. информационный вход нулевого регистра 41.0 группы подключен к нулевому выходу группы, а нулевой информационный вход i-го мультиплексора 41. i группы подключен к i-му информационному выходу группы второго блока 4 памяти). Адресные входы мультиплексоров 42.1-42.k группы подключены к соответствующим выходам четвертого блока 46 памяти, выходы мультиплексоров 42.1-42.k группы подключены к информационным входам соответствующих регистров 41.1-41.k группы (т.е. выход i-го мультиплексора 42.1-42. k группы подключен к информационному входу i-го регистра 41.1-41.k группы). Выходы всех регистров 41.0-41.k группы подключены соответственно к группе информационных входов пятого шинного формирователя 50 (т.е. выход нулевого регистра 41.0 группы подключен к нулевому входу группы, а выход i-го регистра 41.1 группы подключен к i-му входу группы информационных входов пятого шинного формирователя 50). Первый выход 1.0 первого дешифратора 1 подключен к входу разрешения обращения второго блока 4 памяти, к вторым входам шестого 54 и десятого 63 элементов И, к входам синхронизации всех регистров 41.0-41.k группы и к первому входу тринадцатого элемента И 66, выход которого подключен к входу разрешения пятого шинного формирователя 50. Выход признака окончания считывания данных второго блока 4 памяти подключен к входу третьего элемента 59 задержки, выход которого подключен к входу второго одновибратора 51. Выход пятого элемента ИЛИ 53 подключен к входу начальной установки третьего счетчика 38, к счетному входу которого подключен выход десятого элемента И 63. Выход шестого элемента ИЛИ 54 подключен к входу четвертого элемента 60 задержки, выход которого подключен к входу разрешения обращения четвертого блока 46 памяти, к второму адресному входу которого подключен выход третьего счетчика 38. Выход второго регистра 7 подключен к первому адресному входу четвертого блока 46 памяти и к информационному входу второго дешифратора 61, выход которого подключен к адресному входу пятого блока 45 памяти. Выход блока 45 подключен к второму входу сумматора 43, к первому входу которого подключен выход первого регистра 8. Выход сумматора 43 подключен к информационному входу третьего регистра 39, синхронизирующий вход которого подключен к выходу второго элемента 58 задержки. Выход мультиплексора 25 подключен также к входу группы элементов 57 задержки, выход которых подключен к информационному входу демультиплексора 56.

Дешифратор 1 предназначен для управления 6 блоками 3, 4, 5, 46 памяти, шинными формирователями 2, 50, регистрами 7, 8, группой регистров 41.0-41.k и счетчиками 6, 26, 38. Дешифратор 1 дешифрирует адрес, установленный на адресных входах 28 в том случае, если активирован выход элемента ИЛИ 14, возбуждающий вход разрешения дешифратора 1. Если на входах 28 установлены адреса счетчика 6, регистров 7, 8, то возбуждаются соответствующие выходы 1.1, 1.2, 1.3 дешифратора. Если на входах 28 установлен адрес шинного формирователя 2, то возбуждается выход 1.4 дешифратора 1. Если на входах 28 установлены адреса ячеек памяти блока 3, то возбуждается выход 1.5 дешифратора 1. Если на входах 28 установлены адреса ячеек блока 4 памяти, то возбуждается выход 1.0 дешифратора 1. Для управления обнулением триггера 9 и счетчика 26 на входах должны быть установлены адреса, возбуждающие соответствующие выходы 1.6, 1.7 дешифратора 1. Дешифратор может быть реализован, например, на стандартных интегральных микросхемах 155ИДЗ.

Шинный формирователь 2 предназначен для буферирования выходов регистра 8. Внешний процессор обращается к шинному формирователю 2 как к ячейке памяти с фиксированным адресом, при этом возбуждается выход 1.4 дешифратора 1 (безразлично в режиме записи или чтения) и информация с выходов регистра 8 поступает на вход-выход 27 и затем во внешний процессор. Иначе выход шинного формирователя 2 находится в высокимпедансном состоянии и не влияет на передачу информации по входу-выходу 27. Шинный формирователь 2 может быть реализован, например, на стандартных интегральных микросхемах 589АП16.

Блок 3 постоянной памяти предназначен для хранения основных программ работы внешнего процессора, составленных из полного перечня его команд на языке машинных кодов. Команды и данные в соответствии с адресами ячеек на входе 28 считываются из блока 3 на вход-выход 27 через шинный формирователь 47 или (в условиях обнаружения отказа типа неправильное выполнение отдельных команд) через мультиплексор 25, демультиплексор 56 и шинный формирователь 49 с задержкой, определяемой группой элементов 57 задержки, причем вход разрешения активизируется выходом элемента И 19. В противном случае выход блока 3 находится в высокоимпедансном состоянии и не влияет на передачу информации по входу-выходу 27. Блок 3 постоянной памяти может быть реализован, например, на стандартных интегральных микросхемах 556РТ5, буферированных шинными формирователями 589АП16 по входам.

Блок 4 постоянной памяти предназначен для хранения шаблонов алгоритмических эквивалентов команд внешнего процессора, составленных из условий усеченности полной системы команд в результате отказов. Обращение к блоку 4 происходит при возбуждении выхода 1.0 дешифратора 1. Блок 4 постоянной памяти реализуется аналогично блоку 3.

Блок 5 постоянной памяти предназначен для хранения информации, которой необходимо заменить информацию в блоке 3, либо команд безусловного перехода (задаются счетчиком 6) на шаблоны алгоритмических эквивалентов. При выборе последнего слова команды безусловного перехода возбуждается отдельный выход блока 5. При неактивировании входа разрешения блока 5 его выход находится в высокоимпедансном состоянии и не влияет на передачу информации по входу-выходу 27. Блок 5 постоянной памяти также реализуется аналогично блоку 3. Частота синхронизации внешнего процессора такова, что запись информации из блока 3 через элементы предлагаемого устройства по шине данных во внутренние регистры процессора происходит после момента возможного срабатывания триггера 9 и переключения на считывание информации из блока 5, т.е. процессор "не заметит" подмены неисправной команды, находящейся в блоке 3, на команду безусловного перехода, находящуюся в блоке 5.

Счетчик 6 предназначен для хранения кода адреса информации, записанной в блоке 5. Этот код записывается с входа-выхода 27 по импульсу на выходе элемента И 16. Состояние счетчика 6 изменяется задним фронтом импульса на выходе элемента И 18 для обеспечения адресации команды перехода, состоящей из нескольких слов. Счетчик 6 может быть реализован, например, на стандартных интегральных микросхемах 155ИЕ7. Для реализации управления счетным входом по входу 37 необходим элемент И, подключенный выходом к счетному входу.

Регистр 7 предназначен для хранения кода адреса или кода команды, на которых производится либо замена информации информацией из блока 5, либо выполняется режим алгоритмической реконфигурации по шаблону из блока 4. Хранящийся код команды осуществляет адресацию блока 46 (выбирается соответствующий шаблон программы эквивалентной замены), а через дешифратор 61 адресацию блока 45 (выбирается константа для вычисления продвинутого адреса). Информация в регистр 7 записывается с входа-выхода 27 по импульсу на выходе элемента И 15.

Регистр 8 предназначен для хранения адреса, на котором происходит алгоритмическая реконфигурация либо замена информации, которая записывается с входа 28 по переднему фронту импульса на выходе схемы 10 сравнения. Регистры 7, 8 могут быть реализованы, например, на стандартных интегральных микросхемах 155ИР13.

Триггер 9 предназначен для управления счетчиком 26 и элементами И 18, 19. Триггер может быть обнулен сигналом с выхода элемента ИЛИ 13, а устанавливается передним фронтом импульса на выходе схемы 10 сравнения, так как на информационный вход триггера подается сигнал логической "1". Возбужденный выход триггера 9 блокирует элемент И19. Триггер может быть реализован, например, на стандартных интегральных микросхемах 155ТМ2.

Схема 10 сравнения предназначена для сравнения информации на выходе мультиплексора 25 и регистра 7 для управления триггером 9, регистром 8, элементом И 64, блоком 45 памяти, демультиплексором 56 и элементом 58 задержки. Схема 10 сравнения стробируется выходом элемента ИЛИ 12. Она может быть реализована, например, на стандартных интегральных микросхемах 553СП1.

Элемент ИЛИ 11 предназначен для управления элементом И 20 и блокирования элемента И 62. Его выход активирован, если код, записанный в счетчике 26, отличен от нуля.

Элемент ИЛИ 12 предназначен для управления входом синхронизации схемы 10 сравнения в том случае, если на выходах хотя бы одного из элементов И20, 21, 22 имеется логическая "1".

Элемент ИЛИ 13 предназначен для обнуления триггера 9 либо сигналом начального сброса с входа 33, либо выходом одновибратора 23, либо выходом 1.6 дешифратора 1.

Элемент ИЛИ 14 предназначен для управления дешифратором 1 в том случае, если активирован один из управляющих сигналов 35 чтения, 34 записи, 32 выборки команды. В этом случае дешифратор 1 дешифрирует адрес на входе 28.

Элемент И 15 предназначен для формирования импульса записи информации в регистр 7 и управления через элемент ИЛИ 54 элементом 60 задержки, если возбужден выход 1.1 дешифратора 1 и вход 34 записи.

Элемент И 16 предназначен для управления записью информации в счетчик 6 в том случае, если возбужден выход 1.2 дешифратора 1 и вход 34 записи.

Элемент И 17 предназначен для управления записью информации в счетчик 26 в том случае, если возбужден выход 1.3 дешифратора 1 и вход 34 записи.

Элемент И 18 предназначен для управления входом разрешения блока 5 и счетным входом счетчика 6 в том случае, если возбужден выход 1.5 дешифратора 1 и установлен триггер 9.

Элемент И 19 предназначен для управления входом разрешения блока 3 в том случае, если возбужден выход 1.5 дешифратора 1 и не установлен триггер 9.

Элемент И 20 предназначен для управления элементом ИЛИ 12 в том случае, если возбуждены выход 1.5 дешифратора 1, выход элемента ИЛИ 11, вход 31 режима частичной реконфигурации и вход 32 выборки команды.

Элемент И 21 предназначен для управления элементом ИЛИ 12 в том случае, если возбуждены выход 1.5 дешифратора 1 и вход 30 режима полной реконфигурации.

Элемент И 22 предназначен для управления элементом ИЛИ 12 в том случае, если возбуждены выход 1.5 дешифратора 1, вход 29 режима замещения информации и вход 32 выборки команды.

Одновибратор 23 предназначен для формирования импульса сброса триггера 9 по окончании выборки из блока 5 команды безусловного перехода на шаблоны алгоритмических эквивалентов блока 4 либо на заменяемую информацию. Одновибратор 23 может быть реализован, например, на стандартных интегральных микросхемах 155АГ1.

Элемент 24 задержки предназначен для задержки сигнала управления одновибратором 23 с отдельного выхода блока 5 на период времени, необходимый для надежного считывания информации из блока 5 во внешний процессор.

Мультиплексор 25 предназначен для подключения к входу Do-схемы 10 сравнения либо выхода блок 3, либо адресного входа 28 в зависимости от значения сигнала на входе 36 задания типа замещаемой информации (если на входе логическая "1", подключается адресный вход 28). Мультиплексор 25 осуществляет также выдачу информации на вход группы элементов 57 задержки. Он может быть реализован, например, на стандартных интегральных микросхемах 155КП1.

Счетчик 26 предназначен для управления элементом ИЛИ 11 путем вычитания единицы из числа, записанного в него при настройке, всякий раз, когда обнуляется триггер 9, что необходимо для задания необходимого количества алгоритмических реконфигураций. Запись информации в счетчик 26 осуществляется с входа-выхода 27 по сигналу на выходе элемента И 17. Обнуляется счетчик 26 при возбуждении выхода 1.7 дешифратора 1. Счетчик может быть реализован, например, на стандартных интегральных микросхемах 155ИЕ7.

Информационный вход-выход 27 предназначен для подключения шины данных внешнего процессора. Внешний процессор считывает данные и команды с входа-выхода 27 по собственным синхросигналам, частота следования которых такова, что запись информации в его внутренние регистры происходит с задержкой, учитывающей возможное срабатывание триггера 9 и переключение блоков 3 и 5 памяти. Поэтому внешний процессор "не заметит" подмены информации.

Адресный вход 28 предназначен для подключения шины адреса внешнего процессора.

Вход 29 режима замещения информации предназначен для перевода выхода шинного формирователя 47 в состояние высокого импеданса и для управления элементом И 22, где используется для задания режима алгоритмической реконфигурации по коду команды, либо при замене по коду команды, когда активирован вход 32.

Вход 30 режима полной реконфигурации предназначен для блокирования элементов И 64, 67, а также для управления элементом И 21 либо для задания режима алгоритмической реконфигурации, либо при замене информации как по коду команды или операнда, так и по адресу.

Вход 31 режима частичной реконфигурации предназначен для управления элементом И 20, для задания режима частичной алгоритмической реконфигурации, а также для перевода в состояние высокого импеданса выхода шинного формирователя 47 или активирования его при появлении логического "0" на выходе элемента ИЛИ 11. Входы 29, 30, 31 возбуждаются унитарно: в каждом из возможных режимов возбужден только один из них.

Вход 32 выборки команды предназначен для сигнализации о цикле выборки команды внешнего процессора. Он подключается к соответствующему разряду шины управления процессора (например, для процессора 580ИК80 это коньюнкция разрядов 5, 7 регистра слова состояния).

Вход 33 начальной установки предназначен для обнуления триггера 9 регистров 7, 8, 39, 40 и счетчиков 6, 38. Он может быть подключен к разряду "Начальный сброс" шины управления процессора.

Вход 34 записи предназначен для подключения разряда записи в ячейку памяти шины управления внешнего процессора. Вход 35 чтения предназначен для подключения разряда чтения ячейки памяти шины управления внешнего процессора.

Вход 36 задания типа замещаемой информации предназначен для управления мультиплексором 25, а также для блокирования элемента И 64. При невозбуждении входа 36 на входы мультиплексора 25 подключается информационный вход-выход 27.

Вход 37 разрешения изменения адреса замещаемой информации устройства предназначен для блокировки счетного входа счетчика 6 в том случае, если нет необходимости изменения его состояния (фиксированная замена информации по адресу или по коду), в этом случае вход 37 обнулен.

Счетчик 38 предназначен для адресации блока 46 памяти в режиме алгоритмической реконфигурации по шаблону. Очередное увеличение содержимого счетчика осуществляется задним фронтом сигнала с выхода элемента И 63, а обнуление -сигналом с выхода элемента ИЛИ 53. Счетчик 38 может быть реализован, например, на стандартных интегральных микросхемах 155ИЕ7.

Регистр 39 предназначен для хранения продвинутого адреса отказавшей команды, записываемого с выхода сумматора 43 по сигналу с выхода элемента 58 задержки.

Регистр 40 предназначен для хранения содержимого отказавшей команды, для которой выполняется режим алгоритмической реконфигурации по шаблону. Информация в регистр 40 записывается с выхода D1демультиплексора 56 по переднему фронту сигнала с выхода элемента И 64. Регистры 39, 40 могут быть реализованы, например, на стандартных интегральных микросхемах 155ИР13.

Группа регистров 41.0-41.k предназначена для хранения получаемых команд на каждом шаге синтеза программы эквивалентной замены отказавшей команды в режиме алгоритмической реконфигурации по шаблону. Информация в группу регистров 41.0-41.k записывается по переднему фронту сигнала с выхода 1.0 дешифратора 1. При этом на каждом шаге синтеза в регистр 41.0 записывается код очередной команды (первые разряды соответствующего шаблона команды) из блока 4, а в регистры 41.1-41.k соответственно информационные участки синтезируемой команды с выходов мультиплексоров 42.1-42.k. Группа регистров 41.1-41.k может быть реализована, например, на стандартных интегральных микросхемах 155ИР13.

Группа мультиплексоров 42.1-42.k предназначена для подключения к информационным входам группы регистров 41.1-41.k либо соответствующих выходов 1-k блока 4 (на фиг.1 не указаны), либо соответствующих выходов 1-k регистра 40 в зависимости от управляющего кода на выходах 1-k блока 46 (причем адресный вход i-го мультиплексора группы подключен к i-му выходу блока 46, i= . Группа мультиплексоров 42.1-42.k может быть реализована, например, на стандартных интегральных микросхемах 155КП1.

. Группа мультиплексоров 42.1-42.k может быть реализована, например, на стандартных интегральных микросхемах 155КП1.

Сумматор 43 предназначен для вычисления продвинутого адреса отказавшей команды (адрес отказавшей команды на вход Do сумматора поступает из регистра 8), для которой выполняется режим алгоритмической реконфигурации по шаблону, посредством увеличения содержимого регистра 8 на значение константы, поступающей на вход D1 сумматора из блока 45. Сумматор 43 может быть реализован, например, на стандартных интегральных микросхемах 155ИМ1.

Элемент НЕ 44 предназначен для управления входом разрешения дешифратора 61 и первыми входами элементов И 63, 65 в том случае, если не активирован выход элемента ИЛИ 55.

Блок 45 постоянной памяти предназначен для хранения констант, необходимых для вычисления продвинутого адреса отказавших команд. Количество хранимых констант определяется количеством (в данной ВС) различных по длине форматов команд. Выбор необходимой константы зависит от того, какой выход дешифратора 61 возбужден, так как каждому выходу дешифратора соответствует одна ячейка памяти в блоке 45 (на фиг.1 выходы дешифратора 61 указаны шиной). Считывание выбранной константы на вход D1сумматора 43 осуществляется по сигналу с выхода схемы 10 сравнения на входе разрешения обращения блока 45. Блок 45 может быть реализован, например, на стандартных интегральных микросхемах 556РТ5, буферированных шинными формирователями 589АП16 по входам.

Блок 46 постоянной памяти предназначен для хранения наборов кодов, обеспечивающих управление группой мультиплек- соров 42.1-42.k в режиме алгоритмической реконфигурации по шаблону. В блоке 46 используется принцип двойной адресации. По адресному входу А1 в соответствии с кодом отказавшей команды с выхода регистра 7 осуществляется выбор последовательности управляющих кодов, выбор каждого набора внутри которой осуществляется по адресному входу А2 счетчиком 38. Считывание управляющих кодов с выходом 1-k блока 46 соответственно на адресные входы мультиплексоров 42.1-42.k осуществляется по сигналу с выхода элемента 60 задержки, который возбуждает вход разрешения обращения блока 46. Блок 46 может быть реализован, например, на стандартных интегральных микросхемах 556РТ5, буферированных шинными формирователями 589АП16 по входам.

Шинный формирователь 47 предназначен для буферирования выходов блока 3 постоянной памяти. Он обеспечивает считывание информации из блока 3 на вход-выход 27 в случае активирования входа разрешения сигналом логической "1"с выхода элемента ИЛИ 55. Иначе выход шинного формирователя находится в высокоимпедансном состоянии и не влияет на передачу информации по входу-выходу 27. Шинный формирователь 47 реализуется аналогично шинному формирователю 2.

Шинный формирователь 48 предназначен для буферирования выходов регистра 39. Он обеспечивает считывание информации из регистра 39 на адресный вход блока 3 в случае активирования входа разрешения сигналом логической "1" с выхода элемента И 67. Иначе выход шинного формирователя находится в высокоимпедансном состоянии и не влияет на передачу информации по адресному входу 28. Шинный формирователь 48 реализуется также аналогично шинному формирователю 2.

Шинный формирователь 49 предназначен для буферирования выходов демультиплексора 56. Он обеспечивает считывание информации с выхода Doдемультиплексора 56 на вход-выход 27 в случае активирования входа разрешения сигналом логической "1" с выхода элемента И 65. Иначе выход шинного формирователя находится в высокоимпедансном состоянии и не влияет на передачу информации по входу-выходу 27. Шинный формирователь 49 реализуется также аналогично шинному формирователю 2.

Шинный формирователь 50 предназначен для буферирования выходов группы регистров 41.0-41.k, эти выходы подключены соответственно к его 1-k (на фиг. 1 указаны шиной) информационным входам. Он обеспечивает считывание информации на вход-выход 27 в случае активирования входа разрешения сигналом логической "1" с выхода элемента И 66. Иначе выход шинного формирователя находится в высокоимпедансном состоянии и не влияет на передачу информации по входу-выходу 27. Шинный формирователь 50 также реализуется аналогично шинному формирователю 2.

Одновибратор 51 предназначен для управления элементами ИЛИ 53 и И 67 при появлении сигнала логической "1" на выходе элемента 59 задержки, при этом одновибратор 51 также блокирует элементы И 65, 66, удерживая выходы шинных формирователей 49, 50 в состоянии высокого импеданса. Одновибратор 51 реализуется аналогично одновибратору 23.

Элемент ИЛИ-НЕ 52 предназначен для управления элементом ИЛИ 55 в том случае, если активированы вход 29 режима замещения информации и вход 31 режима частичной реконфигурации устройства.

Элемент ИЛИ 53 предназначен для обнуления счетчика 38 либо сигналом начального сброса с входа 33, либо выходом одновибратора 51.

Элемент ИЛИ 54 предназначен для управления элементом 60 задержки в том случае, если возбужден выход 1.0 дешифратора 1 или выход элемента И 15.

Элемент ИЛИ 55 предназначен для управления входом разрешения шинного формирователя 47 в том случае, если возбужден выход элемента ИЛИ-НЕ 52 или выход элемента И 62.

Демультиплексор 56 предназначен для подключения выхода группы элементов задержки либо к информационному входу шинного формирователя 49, либо к информационному входу регистра 40 в зависимости от значения сигнала на выходе схемы 10 сравнения (если на выходе логическая "1", то вход демультиплексора 56 подключается к информационному входу регистра 40). Демультиплексор 56 может быть реализован, например, на стандартных интегральных микросхемах 155ИД3.

Группа элементов 57 задержки (на фиг.1 обозначена одним элементом) предназначена для задержки информации, поступающей с выхода мультиплексора 25 на вход демультиплексора 56 на период времени, необходимый для срабатывания схемы 10 сравнения и коммутации (в связи с этим) демультиплексора 56.

Элемент 58 задержки предназначен для задержки сигнала с выхода схемы 10 сравнения на вход синхронизации регистра 39 на период времени, необходимый для завершения вычислений в сумматоре 43.

Элемент 59 задержки предназначен для задержки сигнала управления одновибратором 51 с отдельного выхода блока 4 на период времени, необходимый для надежного считывания шаблона из блока 4, завершения формирования на его основе программы эквивалентной замены отказавшей команды.

Элемент 60 задержки предназначен для задержки сигнала с выхода элемента ИЛИ 54 на вход разрешения обращения блока 46 памяти на период времени, необходимый для надежного срабатывания счетчика 38.

Дешифратор 61 предназначен для управления блоком 45 памяти. Он дешифрирует информацию, записанную в регистре 7, в том случае, если активирован выход элемента НЕ 44, возбуждающий вход разрешения дешифратора 61. Количество выходов дешифратора соответствует количеству ячеек в блоке 45. В зависимости от кода команды, записанного в регистре 7, возбуждается выход дешифратора 61, активизирующий ячейку блока 45, где записана соответствующая этому коду константа. Дешифратор 61 может быть реализован, например, на стандартных интегральных микросхемах 155ИД3.

Элемент И 62 предназначен для управления элементом ИЛИ 55 в том случае, если возбужден вход 31 режима частичной реконфигурации и не активирован выход элемента ИЛИ 11.

Элемент И 63 предназначен для управления счетным входом счетчика 38 в том случае, если возбуждены вход элемента НЕ 44 и выход 1.0 дешифратора 1.

Элемент И 64 предназначен для управления записью информации в регистр 40 в том случае, если возбужден выход схемы 10 сравнения и не активированы вход 30 режима полной реконфигурации и вход 36 задания типа замещаемой информации.

Элемент И 65 предназначен для управления входом разрешения шинного формирователя 49 в том случае, если возбужден выход элемента НЕ 44 и не активирован выход одновибратора 51.

Элемент И 66 предназначен для управления входом разрешения шинного формирователя 50 в том случае, если возбужден выход 1.0 дешифратора 1 и не активирован выход одновибратора 51.

Элемент И 67 предназначен для управления входом разрешения шинного формирователя 48 в том случае, если возбужден выход одновибратора 51 и не активирован выход 30 режима полной реконфигурации.

Устройство работает следующим образом.

Режим настройки. В этом режиме внешняя ЭВМ записывает в регистр 7 и счетчики 6,26 настроечную информацию. Предварительно перед записью информации по входу 38 производится обнуление счетчика 6, регистра 7, триггера 9 через элемент ИЛИ 13 и счетчика 38 через элемент ИЛИ 53. При этом по входу-выходу 27 поступает слово информации, а на адресных входах устанавливается адрес ячейки памяти, т.е. адрес регистра 7. Так как в этом случае возбуждается вход 34 устройства, то активируется выход элемента ИЛИ 14, возбуждается вход разрешения дешифратора 1, его выход 1.1 и соответственно выход элемента И 15, что приводит к записи в регистр 7 кода команды, требующей алгоритмической реконфигурации, а также к выдаче на адресные входы группы мультиплексоров 42.1-42. k управляющих наборов с выходов 1-k соответственно блока 46 (на первый адресный вход которого подается код команды с регистра 7, а на второй нулевое значение с выхода счетчика 38), поскольку логическая "1" на выходе элемента И 15 через элемент ИЛИ 54 и элемент 60 задержки разрешает выдачу информации, необходимой для режима алгоритмической реконфигурации по шаблону.

Аналогично происходит запись информации в счетчик 6, куда записывается адрес команды перехода на заданный вариант алгоритмической конфигурации, при этом возбуждается выход 1.2дешифратора 1 и выход элемента И 16. Информация записывается с входа-выхода 27. В счетчик 26 может быть записан код количества повторений заданной команды, при которых необходима алгоритмическая реконфигурация. При этом аналогично выше описанному возбуждается выход 1.3 дешифратора 1, выход элемента И 17 и информация записывается по входам данных счетчика 26 с входа-выхода 27 по синхроимпульсу с выхода элемента И 17.

Режим замены информации в ячейке. В этом режиме на входы 30, 37 подается логическая "1". Информация, загруженная в регистр 7, в этом случае имеет смысл адреса ячейки, в которой информация подлежит замене, причем код адреса новой информации записан в счетчик 6. Счетчик 26 в этом режиме не используется. На вход 36 подается логическая "1" и вход 28 подключается к схеме 10 сравнения. Информация с выхода мультиплексора 25 поступает также на демультиплексор 56, с которого (в зависимости от сигнала на его адресном входе) она подается либо на шинный формирователь 49, либо на регистр 40, но в этом режиме эти элементы не используются, поскольку на входе синхронизации регистра 40 установлен нулевой сигнал с выхода элемента И 64, а на входе разрешения шинного формирователя 49 нулевой сигнал с выхода 1.0 дешифратора 1. Входы 29, 31, 32 обнулены, единичный сигнал с выхода элемента ИЛИ-НЕ 52 через элемент ИЛИ 55 возбуждает вход управления шинного формирователя 47, обеспечивая внешней ЭВМ считывание (с входа-выхода 27) и выполнение программы, записанной в блоке 3 постоянной памяти. При этом возбуждаются вход 35 или 32, поэтому на адресах ячеек блока 3 возбуждается выход 1.5 дешифратора 1 и, так как триггер 9 пока обнулен, то выход элемента И 19 возбуждает вход выборки блока 3, из которого в соответствии с адресами, установленными на входе 28, через шинный формирователь 47 считывается либо команда, либо данные на вход-выход 27. Если считывается информация по адресу, заданному в регистре 7, то возбужден выход элемента И 21 (возбуждены вход 30 и выход 1.5 дешифратора 1), поэтому через элемент ИЛИ 12 возбуждается вход управления схемы 10 сравнения. Активируется выход схемы сравнения (информация в регистре 7 равна информации на входе 28, поступающей через мультиплексор 25), поэтому устанавливается триггер 9, так как его информационный вход подключен к входу логической "1" устройства, в регистр 8 записывается адрес, установленный на входе 28. Изменяется и состояние счетчика 26, однако в этом режиме он не используется. Выход триггера 9 через элемент И 19 блокирует чтение информации из блока 3 и подключает блок 5 через элемент И 18, чем обеспечивается замена информации по заданному адресу. В блоке 5 один информационный выход предназначен для сброса триггера 9 после такой замены, что и происходит с задержкой, определяемой элементом 24 (необходима для надежного считывания замененной информации), одновибратором 23, который через элемент ИЛИ 13 обнуляет триггер 9. Изменяется состояние счетчика 6. При следующей установке триггера 9 из блока 5 считана информация из очередной ячейки. Следовательно, заменяемая информация может меняться в ходе вычислительного процесса. Иначе необходимо установить на входе логический "0", блокирующий прохождение счетных импульсов.

Аналогично прототипу в этом режиме может осуществляться замена не только по адресам, но и по данным. В этом случае вход 36 не активируется (выход мультиплексора 25 подключен к входу Do), а в регистр 7 записывается код, который необходимо заменить на другой, записанный в блоке 5. Для замены только данных на вход 29 управления подается логическая "1", на выходе элемента ИЛИ-НЕ 52 появляется логический "0", который через элемент ИЛИ 55 переводит выход шинного формирователя 47 в состояние высокого импеданса (на выходе элемента И 62 логический "0"), т.е. исключает считывание информации из блока 3 непосредственно на вход-выход 27. Логическая "1" с выхода элемента НЕ 44 через элемент И 65 активирует вход разрешения шинного формирователя 49 (на выходе одновибратора 51 логический "0"). Теперь информация с выхода блока 3 на вход-выход 27 поступает через мультиплексор 25, демультиплексор 56 и шинный формирователь 49. Аналогично вышеописанному при считывании кода, установленного в регистре 7, возбуждается выход схемы 10 сравнения, устанавливается триггер 9 и из блока 5 считывается всякий раз другая необходимая информация с учетом изменения состояния счетчика 6, если необходимо. Адреса, записываемые в регистр 8, могут использоваться для отладки с целью проверки работы устройства, причем они считываются из регистра 8 программно: возбуждается выход 1.4 дешифратора 1 (регистр 8 через шинный формирователь 2 программно доступен как ячейка памяти для чтения), возбуждается вход управления шинного формирователя 2 и адрес из регистра 8 поступает на вход-выход 27.

Режим полной алгоритмической реконфигурации. В этом режиме устройство обеспечивает выдачу на входы-выходы 27 кодов команд безусловного перехода для замены команд, которые не могут быть выполнены внешним процессором в связи с некоторым частичным отказом его технических средств (это может быть идентифицировано самим процессором по результатам, например, его самопроверки) на их алгоритмические эквиваленты, составленные и оставшихся команд. В отличие от прототипа в блоке 4 записаны не целиком программы эквивалентных замен, а только их шаблоны (состоящие из шаблонов команд), на основании которых предлагаемое устройство за счет использования операндов отказавшей команды и формирует полноценные замены отказавших команд. Это позволяет существенно сократить эти программы, а следовательно, потребные объемы памяти и время выполнения эквивалентных замен.

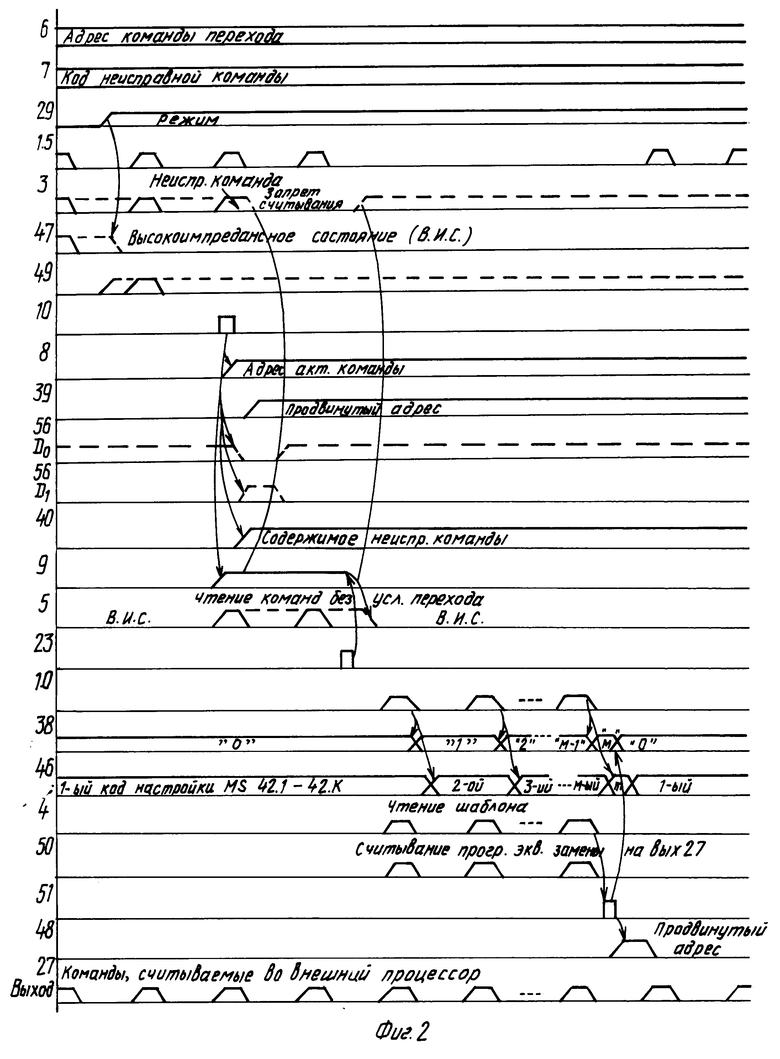

В регистре 7 записан код команды, подлежащей замене, в счетчике 6 соответствующий этому коду адрес команды безусловного перехода на начало алгоритмического эквивалента шаблона, записанного в блоке 4. На входы 29, 37 управления подается логическая "1", на входы 30, 31, 36 логические "0". Причем подача логических уровней на входы управления может быть осуществлена, например, внешним процессором путем вывода кода на некоторый внешний регистр (не указан на фиг.1) либо, например, подачей требуемых уровней напряжения жестко. Логический "0" с выхода элемента ИЛИ-НЕ 52 через элемент ИЛИ 55 (на выходе элемента И 62 также логический "0") переводит выход шинного формирователя 47 в состояние высокого импеданса, а сигнал с выхода элемента НЕ 44 активизирует входы управления дешифратора 61 через элемент И 65 шинного формирователя 49, а также первый вход элемента И 63. В результате перевода в состояние высокого импеданса шинного формирователя 47 и активирования выхода шинного формирователя 49 устройство в течение всего режима исключает считывание во внешний процессор по входу-выходу 27 неисправной команды (прототипом не обеспечивалось), осуществляя проверку на схеме 10 сравнения (поскольку входы D1 и Do схемы сравнения подключены соответственно к выходам регистра 7 и мультиплексора 25) всей информации, считываемой из блока 3, на предмет совпадения с кодом команды, записанным в регистре 7. В случае несовпадения информация из блока 3 на вход-выход 27 поступает через мультиплексор 25, группу элементов 57 задержки, демультиплексор 56 и шинный формирователь 49. Выходы блоков 2, 5, 47, 50 находятся в высокоимпедансном состоянии и не влияют на передачу информации по входу-выходы 27. Логическая "1" на управляющем входе дешифратора 61 разрешает осуществить в нем декодирование кода команды из регистра 7. В результате возбуждается выход дешифратора 61, соответствующий формату отказавшей команды (на фиг.1 выходы дешифратора 1 указаны шиной), и в блоке 45 осуществляется выбор ячейки памяти, из которой будет проведено считывание константы, необходимой для вычисления продвинутого адреса (адреса ячейки памяти блока 3, следующей за той, откуда была считана неисправная команда). Процесс вычисления продвинутого адреса заключается в увеличении адреса отказавшей команды на длину (в байтах) этой отказавшей команды (поскольку информация в основной памятиЭВМ располагается последовательно единым массивом), что осуществляется сум- матором 43. Количество необходимых ячеек в блоке 45 определяется количеством различных форматов команд, используемых в ВС. Так, например, для процессора БИ 0210 ЕС ЭВМ (БИ 0210 Техническое описание ЦЕ 3.031.041 ТО1 1987), где используются команды и данные разрядности 16 и 32, достаточно двух ячеек памяти (в памяти блока 45 будут константы 2 и 4).