Изобретение относится к цифровой вычислительной технике, в частности к устройствам для сопряжения процессоров с памятью. Оно может быть использовано для построения системы с быстродействующей памятью.

Цель изобретения - повышение производительности устройства за счет обеспечения автоматического перехода на работу резерва блока памяти при отказе ячейки блока памяти.

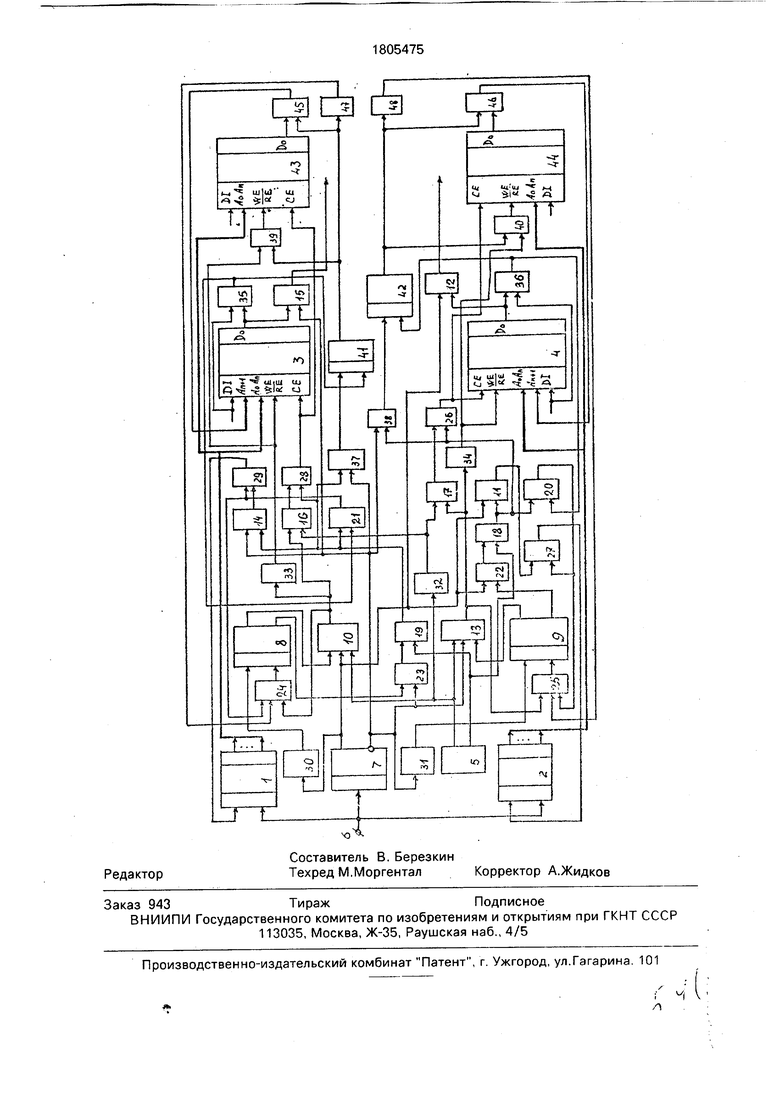

На чертеже представлена блок-схема устройства блока памяти.

Устройство содержит счетчики 1 и 2 адреса, блоки 3 и 4 памяти, генератор 5 импульсов, вход 6 запуска устройства, триггеры 7, 8 и 9, элементы 10,...21, элементы ИЛИ 22,...29, формирователи 30 и 31 коротких импульсов, элементы задержки 32, 33 и 34, схемы сравнения 35, 36. Кроме этого, устройство содержит элементы И 37,..., 40 , счетчики 41 и 42 импульсов, блоки 43 и 44

памяти, элементы ИЛИ 45 и 46 и формирователи 47 и 48 коротких импульсов.

Устройство работает следующим образом.

Информация, подлежащая записи по входу 1 в блоки 3, 4 памяти, привязывается к сигналу запуска по входу 6 и при необходимости может быть синхронизирована импульсами частоты записи, поступающими с первого выхода генератора 5 (не показан).

Сигнал запуска по входу 6 используется также для синхронизации счетчиков 1 и 2. Сигнал на единичном выходе триггера 7 соответствует режиму записи для блока 3 и режиму считывания для блока 4, а сигнал на инверсном выходе триггера 7 соответствует режиму считывания блока 3 и режиму записи для блока 4.

В момент установки счетчиков 1 и 2 и триггера 7 сигналом запуска по входу 6 срабатывания по фронту сигнала с выхода триггера 7 формирователь 30. импульсный

fe

00

о ел

Јь ч4

СП

сигнал с выхода которого принудительно устанавливает триггер 8 в единичное состояние.

В режиме записи информации для блоков 3 и 4 частоты записи с генератора 3 поступают через соответственно открытые элементы И 10 и 13. При этом команда записи для каждого блока памяти разбивается на два канала: управление по входу Запись-считывание и по йходу Выборка кристалла. Для блока 3 команда записи в виде импульсной Частоты записи проходит через элементы 33 и 32 задержки, причем время срабатывания элемента 32 задержки больше времени срабатывания элемента 33 задержки, в результате чего обеспечивается задержка управления по входу Выборка кристалла по отношению к входу Запись-считывание в момент прихода импульса частоты записи с выхода генератора 3. По окончании импульса частоты записи элемент И 16 закрывается, в результате срабатывает элемент задержки 33, время срабатывания которого равно времени срабатывания элементов И 16 и ИЛИ 28, следовательно, исчезновение сигналов управления по входам запись- считывание и Выборка кристалла происходит одновременно. Одновременно по спаду импульса на выходе И 10 устанавливается в О триггер 8, в результате чего закрывается элемент 1/1 10 и разрешается работа элемента И 19, который пропускает импульс частоты считывания с второго выхода генератора 5. Этот импульс проходит через элемент ИЛИ 28 на вход Выборка кристалла блока 3, в результате чего происходит считывание информации, которая только что была записана в блок 3, так как адрес ячейки записи не изменился, а записываемая информация еще хранится на 1- м входе блока 3. Считываемая информация с блока 3 поступает на схему 35 сравнения и сравнивается с информацией на 1-м входе. В случае совпадения информации сигналом с выхода схемы 35 сравнения открывается элемент И 21, и импульс частоты считывания поступает через элемент ИЛИ 29 на вход счетчика 1. Исчезновение импульса частоты считывания изменяет состояние счетчика 1, что соответствует изменению адреса в блоке 3.

Одновременно сигнал с выхода элемент И 21 через элемент ИЛИ 24 устанавливает в 1 триггер 8, открывая элемент И 10 для прохождения импульсов частоты записи по новому адресу в блоке 3.

Отсутствие сигнала сравнения на выходе схемы 35 сравнения в момент записи информации указывает не неисправность блока 3, при этом счетчик 41 подсчитывает

определенное количество импульсов считывания для уверенного обращения к блоку 3, после чего на его выходе появляется единичный сигнал, который через элемент ИЛИ

45 подключает резерв блока 3, а через формирователь 47 переводит триггер 8 в единичное положение через элемент ИЛИ 24, позволяя произвести запись информации в резерв блока 3 памяти по цепи: элемент И

ю, элемент 16 И и ИЛИ 28 - на вход Выборка кристалла, одновременно через элемент И 39 сигнал с выхода счетчика 41 импульсов позволяет по адресу отказавшей ячейки блока 3 записать единичный уровень

5 сигнала в блок 43 памяти, т.к. на его вход 1 подключен источник постоянного напряжения (не показан). Правильность записи информации в резерв блока 3 подтверждается сигналом на выходе 35 сравнения, этот сиг0 нал сбрасывает счетчик 41 и производит смену адреса в счетчике 1 по цепи элементов И 21 и ИЛИ 29.

В режиме считывания для блока 3 импульсы частоты считывания с другого выхо5 да генератора 5 проходит через открытый элемент И 19 с сигналом нулевого выхода триггера 7 через элемент ИЛИ 23, при этом счетчик 1 срабатывает от импульсов частоты считывания через открытый элемент И

0 14. При выборе адреса неисправной ячейки на выходе блока 43 памяти появляется единичный сигнал, который через элемент ИЛИ 45 включает резерв блока 3, выдавая из него записанную информацию, далее при

5 смене адреса продолжает работать блок 3 памяти.

Формула изобретения Устройство буферной памяти, содержащее два блока памяти, два счетчика адреса,

0 три триггера, генератор импульсов, три элемента задержки, двенадцать элементов И, восемь элементов ИЛИ, два формирователя коротких импульсов и две схемы сравнения, причем вход синхронизации

5 первого триггера является входом запуска устройства и соединен с входами сброса первого и второго счетчика адреса, выходы разрядов первого и второго счетчиков адреса соединены с младшими разрядами

0 адресных входов первого и второго блоков памяти соответственно, прямой выход первого триггера соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом генератора им5 пульсов и первым входом второго элемента И, выход первого элемента И соединен с первым входом третьего элемента И и через первый элемент задержки - с входом чтения-записи первого блока памяти, выход второго элемента И - с первым входом четвертого элемента И и через второй элемент задержки - с входом чтения-записи второго блока памяти, первый выход генератора импульсов соединен через третий элемент задержки с вторыми входами третьего и четвертого элементов И, выходы которых соединены с первыми входами первого и второго элементов ИЛИ соответственно, выходы которых соединены с входами Выборка кристалла первого и второго блоков памяти соответственно, второй выход генератора импульсов соединен с первыми входами пятого и шестого элементов И, выходы которых соединены с вторыми входами первого и второго элементов ИЛИ соответственно, прямой и инверсный выходы первого триггера соединены через первый и второй формирователи коротких импульсов с входами установки в 1 второго и третьего триггеров соответственно, инверсный выход первого триггера соединен с вторым входом второго элемента И, прямые выходы второго и третьего триггеров соединены с третьими входами первого и второго элементов И соответственно, выходы которых соединены с первыми входами третьего и четвертого элементов ИЛИ, выходы которых соединены с входами установки второго и третьего триггеров соответственно, прямой и инверсный выходы первого триггера соединены с первыми входами пятого и шестого элементов ИЛИ соответственно, вторые входы которых соединены с инверсными выходами третьего и второго триггеров соответственно, выходы пятого и шестого элементов ИЛИ соединены с вторыми входами шестого и пятого элементов И соответственно, выход пятого элемента И -с первыми входами седьмого и восьмого элементов И, выход шестого элемента И - с первыми входами девятого и десятого элементов И, прямой и инверсный выходы первого триггера - с вторыми входами десятого и восьмого элементов И соответственно, выходы восьмого и десятого элементов И - с первыми входами седьмого и восьмого элементов ИЛИ соответственно, выход седьмого элементов И - с вторыми входами третьего и седьмого элементов ИЛИ, выход девятого элемента И - с вторыми входами четвертого и восьмого элементов ИЛИ, выходы седьмого и восьмого элементов ИЛИ - со счетными входами первого и второго счетчиков адреса соответственно, выходы первой и второй схем сравнения - с вторыми входами седьмого и девятого элементов И соответственно, информационные входы первого и второго блоков памяти явлуются первым и вторым информационными; входами устройства и

соединены с первыми входами первой и второй схем сравнения соответственно, выход первого блока памяти соединен с вторым входом первой схемы сравнения и

первым входом одиннадцатого элемента И, выход второго блока памяти - с вторым входом второй схемы сравнения и первым входом двенадцатого элемента И, прямой и инверсный выходы первого триггера - с вто0 рыми входами двенадцатого и одиннадцатого элементов И соответственно, выходы одиннадцатого и двенадцатого элементов И являются первым и вторым информационными выходами устройства соответственно,

5 отличающееся тем, что, с целью повышения производительности устройства за счет обеспечения автоматического перехода на работу резерва блока памяти при отказе ячейки блока памяти, в него вве0 дены четыре элемента И. два счетчика импульсов, два блока памяти, два элемента ИЛИ и два формирователя коротких импульсов, при этом первые входы тринадцатого и четырнадцатого элементов И подключены к

5 выходам пятого и шестого элементов И соответственно, их вторые входы - к инверсному выходу первого триггера, а выходы - к счетным входам первого и второго счетчиков импульсов соответственно, установочные

0 входы которых соответственно подключены к выходам первой и второй схем сравнения, выход первого счетчика импульсов соединен с входом третьего формирователя коротких импульсов и первыми входами

5 пятнадцатого элемента И и девятого элемента ИЛИ, выход второго счетчика импульсов - с входом четвертого формирователя коротких импульсов и первыми входами шестнадцатого элемента И и десятого эле0 мента ИЛИ, вторые входы пятнадцатого и шестнадцатого элементов И подключены соответственно к выходам первого и второго элементов задержки, а их выходы соединены с входами Запись-считывание третьего

5 и четвертого блоков памяти соответственно, входы Выборка кристаллов которых подключены соответственно к выходам первого и второго элементов ИЛИ, адресные входы третьего и четвертого блоков памяти под0 ключены соответственно к выходам первого и второго счетчиков адреса, выходы третьего и четвертого блоков памяти соединены с вторыми входами девятого и десятого элементов ИЛИ соответственно, выходы кото5 рых соединены с входами старших разрядов первого и второго блоков памяти соответственно, а выходы третьего и четвертого формирователей коротких импульсов - с третьими входами третьего и четвертого элементов ИЛИ соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство буферной памяти | 1987 |

|

SU1494010A1 |

| Устройство для управления доступом к памяти | 1986 |

|

SU1376089A1 |

| Устройство для обнаружения ошибок в блоках интегральной оперативной памяти | 1988 |

|

SU1605281A1 |

| Устройство буферной памяти | 1987 |

|

SU1418723A1 |

| Устройство для контроля оперативной памяти | 1991 |

|

SU1833919A1 |

| Устройство для контроля хода программы | 1986 |

|

SU1328819A2 |

| Дискретная линия задержки | 1980 |

|

SU961123A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство задержки импульсов | 1981 |

|

SU1019611A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

Изобретение относится к цифровой вычислительной технике. Цель изобретения - повышение производительности устройства за счет обеспечения автоматического перехода на работу резерва блока памяти при отказе ячейки блока памяти. Устройство содержит счетчики адреса, блоки памяти, генератор импульсов, вход запуска устройства, триггеры, элементы И, элементы ИЛИ, схемы сравнения, элементы задержки, формирователи коротких импульсов, счетчики импульсов, блоки памяти. При выборе адреса неисправной ячейки на выходе блока памяти появляется единичный сигнал, который через элемент ИЛИ включает резерв блока памяти, выдавая из него записанную информацию, далее при смене адреса продолжает работать блок памяти. 1 ил.

| Устройство буферной памяти | 1987 |

|

SU1494010A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-30—Публикация

1990-08-29—Подача