Изобретение относится к автоматике, вычислительной технике, в частности, к электроизмерительной технике.

Известен способ интегрирования периодического аналогового напряжения на основе использования пассивного RC или RL интегратора (см. Атабеков Г.И. Основы теории цепей. М.: Энергия, 1969. - С.206). Его недостатком является наличие погрешностей вследствие приближенного выполнения операции интегрирования входного напряжения.

Известны также способы интегрирования, сводящиеся, по сути, к операции суммирования импульсов (см. патент №2131128 Россия). Их недостатком является методическая погрешность из-за замены операции интегрирования операцией суммирования.

Известен также способ интегрирования напряжения на основе активного интегратора, например, с использованием операционного усилителя (см. Хоровиц П., Хилл У. Искусство схемотехники. - М.: Мир, 1983. - T.1. - С.207-208). Использование в таком способе интегрирования активного интегратора позволяет существенно снизить методическую погрешность, но его недостатком является наличие погрешностей от интегрирования входных токов и напряжения смещения используемого активного элемента, например операционного усилителя.

Наиболее близким к предлагаемому является способ интегрирования периодического напряжения на основе активного интегратора, в котором время интегрирования разбивается на такты, в течение части из них производят интегрирование входного сигнала, а в течение других осуществляют коррекцию смещения нулевого уровня (см. Гутников B.C. Интегральная электроника в измерительных устройствах. - Л.: Энергоатомиздат, 1988. - С.256-258), который выбран в качестве прототипа. Такой способ позволяет снизить погрешность от интегрирования входных токов и напряжения смещения используемого активного элемента, например операционного усилителя. Но его недостатком является увеличение методических погрешностей интегрирования вследствие потери информации в течение тактов коррекции нулевого уровня, поскольку источник входного напряжения при этом отключается от входа интегратора.

Технический результат - повышение точности интегрирования напряжения.

Указанный технический результат достигается тем, что в известном способе интегрирования периодического напряжения, включающем выполнение операции интегрирования с использованием активного аналогового интегратора (ААИ) и разбиения процесса интегрирования на N (где N - число четное) тактов, включающих рабочие такты и такты коррекции смещения нулевого уровня, особенность заключается в том, что процесс интегрирования дополнительно разбивают на два равных по длительности цикла, кратных периоду входного напряжения, так, что количество тактов в каждом цикле равно N/2, причем в течение первого цикла рабочими являются нечетные такты, а тактами коррекции - четные, а в течение второго цикла - наоборот: рабочими являются четные такты, а тактами коррекции - нечетные.

Проведенный анализ уровня техники позволил установить, что заявителем не обнаружено аналога, характеризующегося признаками, тождественными всем признакам заявленного изобретения, а определение из перечня аналогов прототипа позволило выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном способе, изложенных в формуле изобретения. Следовательно, заявляемое изобретение соответствует условию “новизна”.

Для проверки соответствия заявленного изобретения условию “изобретательский уровень” заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного способа. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, поскольку из уровня техники, определенного заявителем, не выявлено влияние предусматриваемых существенными признаками заявленного изобретения преобразований на достижение технического результата. Следовательно, заявленное изобретение соответствует условию “изобретательский уровень”.

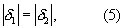

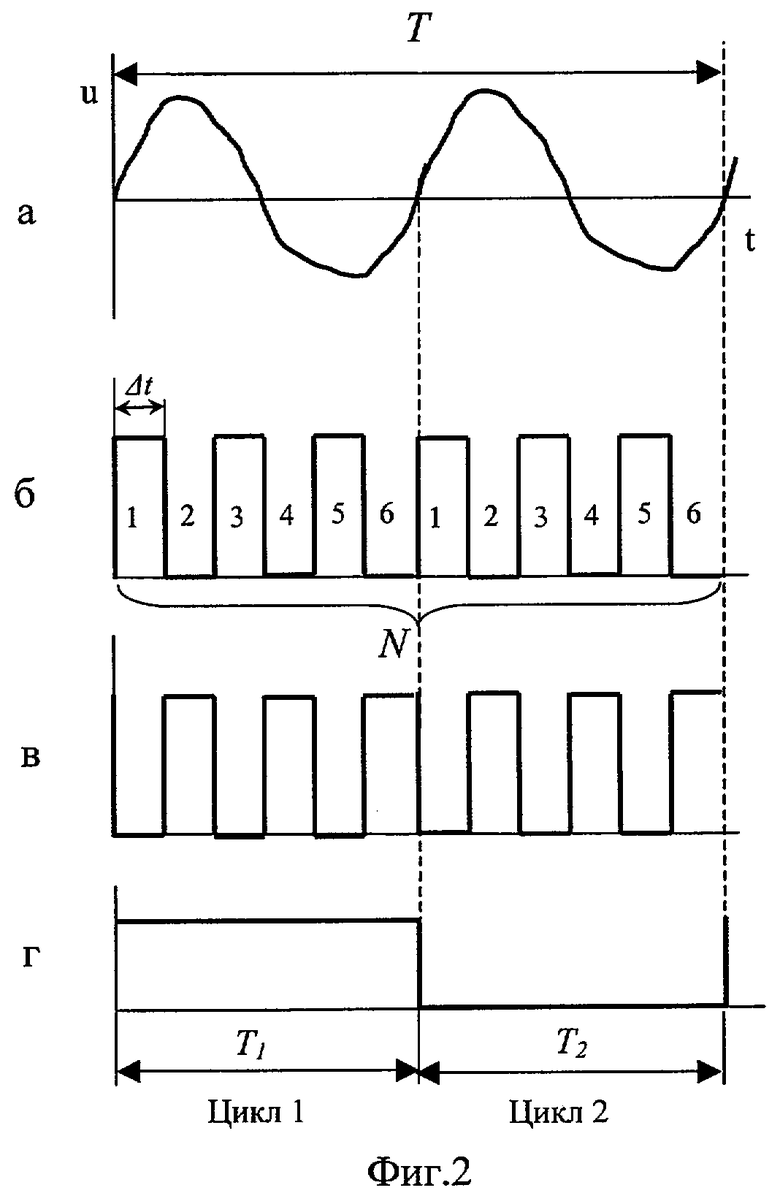

На фиг.1 приведена структурная схема, а на фиг.2 - временные диаграммы, поясняющие предлагаемый способ.

Сущность предлагаемого решения заключается в следующем.

Процесс интегрирования периодического напряжения (фиг.2а) источника 1 с помощью генератора тактовых импульсов (ГТИ) 2 (фиг.1) разбивается на четное число N интервалов (фиг.2б), причем на его инвертирующем выходе импульсы находятся в противофазе (фиг.2в). С помощью формирователя 3 (фиг.1) процесс интегрирования дополнительно разбивается на два цикла, кратных периоду входного напряжения, (например, каждый цикл по длительности может быть равен периоду входного напряжения, что показано на фиг.2г), каждый из которых включает N/2 тактовых импульса. Формирователь 3 может быть выполнен на основе триггера Шмидта (преобразователя входного напряжения в прямоугольные импульсы) и делителя частоты прямоугольных импульсов. Формирователь имеет также инвертирующий выход.

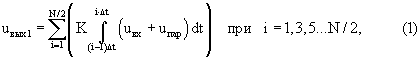

Импульсы с прямых выходов ГТИ 2 и формирователя 3 подаются на логическую ячейку И 4 (фиг.1), поэтому ключ 5 замыкается в течение нечетных номеров (i=1,3,...) импульсов ГТИ 2 (эти импульсы подаются на вход управления ключа 5 с выхода логической ячейки ИЛИ 6), поэтому за время первого цикла (фиг.2г) производится интегрирование входного напряжения с помощью активного аналогового интегратора (ААИ) 7 в течение нечетных импульсов ГТИ 2:

где uвх - входное напряжение; uпар - паразитное напряжение, обусловленное напряжением смещения и входными токами активного элемента ААИ 7; К - коэффициент пропорциональности; Δt - длительность импульса ГТИ 2 (фиг.2б).

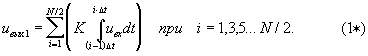

В течение четных номеров (i=2,4,...) ключ 5 разомкнут и интегрирования входного напряжения не происходит, поэтому имеется возможность осуществления коррекции ААИ 7 с помощью известных методов, основанных на измерении паразитного напряжения и введения соответствующего корректирующего напряжения. Таким образом, за суммарное время нечетных тактов будет происходить интегрирование только входного напряжения:

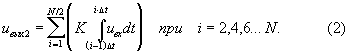

Импульсы с инверсных выходов ГТИ 2 и формирователя 3 подаются на логическую ячейку И 8 (фиг.1), поэтому во втором цикле ключ 5 замыкается в течение четных номеров (i=2,4,...) (фиг.2б) импульсов ГТИ 2 (эти импульсы также подаются на вход управления ключа 5 с выхода логической ячейки ИЛИ 6). Аналогично вышесказанному, в нечетные интервалы времени можно осуществить коррекцию ААИ 7, поэтому в итоге его выходное напряжение ААИ 5 описывается выражением:

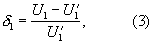

Поскольку интегрирование в обоих циклах производится в течение неполного времени, то следует ожидать появления методических погрешностей интегрирования. Анализ показывает, что относительная погрешность интегрирования в первом цикле

где U1 - результат интегрирования согласно выражению (1*); U′1 - результат “идеального” интегрирования за все время первого цикла t1 (фиг.2г), имеет знак “+”, а относительная погрешность интегрирования во втором цикле

где U2 - результат интегрирования согласно выражению (2); U′2 - результат “идеального” интегрирования за все время второго цикла Т2, имеет знак “-”, причем

поэтому за все время интегрирования Т (фиг.2а) методическая погрешность интегрирования будет равна нулю.

Вышеизложенное свидетельствует, что для заявленного способа в том виде, как он охарактеризован в формуле изобретения, подтверждена возможность его осуществления с помощью описанных в заявке средств и методов, а также - достижения предусмотренного технического результата.

Следовательно, заявленное изобретение соответствует условию “промышленная применимость”.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ВЫБОРОЧНОГО ИНТЕРВАЛЬНОГО ИНТЕГРИРОВАНИЯ НАПРЯЖЕНИЯ | 2002 |

|

RU2218599C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ | 2012 |

|

RU2521305C2 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2004 |

|

RU2256184C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2013 |

|

RU2550591C1 |

| СПОСОБ ИНТЕРВАЛЬНОГО ИНТЕГРИРОВАНИЯ НАПРЯЖЕНИЙ | 2013 |

|

RU2540850C2 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2291559C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЧАСТОТУ ИМПУЛЬСОВ | 2015 |

|

RU2602351C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВЫБОРКИ МГНОВЕННОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2003 |

|

RU2230376C1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

Изобретение относится к автоматике, вычислительной технике, в частности к электроизмерительной технике. Техническим результатом является повышение точности интегрирования. Способ заключается в разбиении процесса интегрирования на N тактов, включающих рабочие такты и такты коррекции смещения нулевого уровня, и дополнительном разбиении процесса интегрирования на два равных по длительности цикла, кратных периоду входного напряжения так, что количество тактов в каждом цикле равно N/2, при этом в течение первого цикла рабочими являются нечетные такты, а тактами коррекции - четные, в течение второго цикла рабочими являются четные такты, а тактами коррекции - нечетные. 2 ил.

Способ интегрирования периодического напряжения, включающий выполнение операции интегрирования с использованием активного аналогового интегратора и разбиения процесса интегрирования на N тактов (где N - число четное), включающих рабочие такты и такты коррекции смещения нулевого уровня, отличающийся тем, что процесс интегрирования дополнительно разбивают на два равных по длительности цикла, кратных периоду входного напряжения, так, что количество тактов в каждом цикле равно N/2, причем в течение первого цикла рабочими являются нечетные такты, а тактами коррекции - четные, а в течение второго цикла наоборот - рабочими являются четные такты, а тактами коррекции - нечетные.

| ГУТНИКОВ В.С | |||

| Интегральная электроника в измерительных устройствах | |||

| - Л.: Энергоатомиздат, 1988, с.256-258 | |||

| ИНТЕГРАТОР ПЕРИОДИЧЕСКИХ НАПРЯЖЕНИЙ | 1999 |

|

RU2149448C1 |

| УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2001 |

|

RU2182361C1 |

| Устройство для испытания легкоплавких предохранительных пробок паровых котлов | 1929 |

|

SU13846A1 |

| Способ двухтактового интегрирования | 1977 |

|

SU635497A1 |

| Способ интегрирования электрических сигналов | 1973 |

|

SU465594A1 |

| Устройство для защиты забойного пространства от падающих кусков | 1988 |

|

SU1603020A1 |

| US 4734598 А, 29.03.1988. | |||

Авторы

Даты

2005-02-27—Публикация

2003-11-11—Подача