Изобретение относится к способу управления фазами заряда и разряда опорного конденсатора носителя данных с блоком обработки данных, причем опорный конденсатор связан с входом питающего напряжения блока обработки данных, при этом способ включает этапы:

- отсоединения блока обработки данных и опорного конденсатора от потенциала питания,

- осуществления вычислительных операций в блоке обработки данных и

- соединения опорного конденсатора с напряжением питания и тем самым заряда опорного конденсатора.

В основе этого способа лежит тот факт, что блоки обработки данных, которые обрабатывают данные секретного ключа, должны быть выполнены таким образом, чтобы во время вычисления на основе потребления тока невозможно было сделать никаких выводов относительно данных ключа. В особенности, тем самым должна быть предотвращена возможность применения известных методов простого анализа мощности (SPA - Simple Power Analysis) и дифференциального анализа мощности (DPA – Differential Power Analysis). За счет буферизации напряжения питания вычислительного средства во время вычислительного цикла обеспечивается скрытие профиля потребления тока вычислительным устройством в процессе выполнения критически важных вычислительных операций. Однако в общем случае по уровню разряда опорного конденсатора можно выяснить, какова была активность в блоке обработки данных в течение времени буферизации. Существует опасность того, что на основе последующего тока подзаряда, который зависит от предшествующего уровня разряда опорного конденсатора, можно получить выводы относительно обрабатываемых секретных данных или, в необходимом случае, относительно специализированной алгоритмической обработки.

Задача настоящего изобретения состоит в том, чтобы обеспечить буферизацию блока обработки данных с использованием опорного конденсатора таким образом, чтобы при подзаряде опорного конденсатора невозможно было сделать никаких выводов о потреблении тока в течение вычислительного цикла. Кроме того, необходимо создать схемное устройство для осуществления способа.

Указанная задача, в отношении способа, решается в способе вышеупомянутого типа, который отличается тем, что перед зарядом опорного конденсатора производится разряд опорного конденсатора до предварительно заданного напряжения постоянным током.

Что касается устройства, указанная задача решается схемным устройством, содержащим опорный конденсатор, который имеет возможность разряда через подключаемый источник постоянного тока, причем опорный конденсатор имеет возможность соединения с потенциалом питания, компаратор, первый вход которого имеет возможность соединения с опорным конденсатором, и ко второму входу которого приложено эталонное напряжение, блок управления, который связан с выходом конденсатора, при этом с помощью блока управления осуществляется управление переключателем для соединения опорного конденсатора с потенциалом питания, а также переключателем для подключения источника постоянного тока.

За счет разряда опорного конденсатора до предварительно определенного напряжения заряд, накапливаемый в процессе заряда конденсатора, всегда является одинаковым. Поэтому уже невозможно сделать выводов относительно состояния заряда опорного конденсатора после вычислительного цикла.

Особенно предпочтительным является то, что разряд опорного конденсатора до заданного напряжения осуществляется постоянным током, так как следует исходить из того, что в схемном устройстве, которое детектирует достижение предварительно заданного напряжения, имеется время запаздывания. За это время опорный конденсатор разряжается дальше. Если разряд осуществляется не постоянным током, то напряжение опорного конденсатора по окончании фазы разряда вновь является зависимым от уровня разряда после завершения проведения вычислительных операций, хотя и во много меньшей степени, чем в способе или соответственно в схемном устройстве согласно уровню техники. В предпочтительном варианте осуществления схемного устройства разряд может быть реализован постоянным током с помощью схемы зеркального отображения тока.

Кроме того, предпочтительно, если разряд опорного конденсатора производится через последовательно соединенные сопротивление и транзистор, причем тем самым образуется делитель напряжения, который может устанавливаться таким образом, чтобы напряжение, снимаемое с точки между транзистором и сопротивлением, могло сравниваться с определенным напряжением эталона запрещенной полосы.

Изобретение поясняется далее на примере выполнения со ссылками на чертежи, на которых показано следующее:

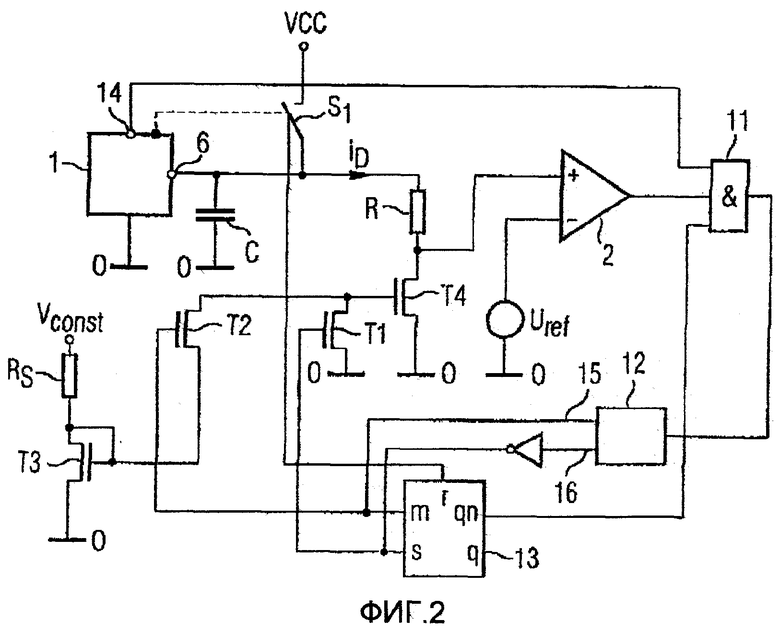

фиг.1 – первое схематичное представление схемного устройства, соответствующего изобретению, и

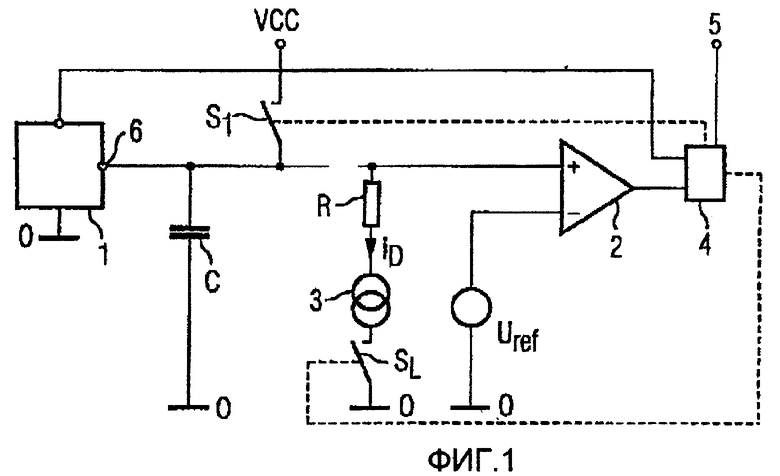

фиг.2 – второе более конкретное выполнение схемного устройства, соответствующего изобретению.

На фиг.1 представлена принципиальная схема устройства, посредством которого может быть осуществлен способ, соответствующий изобретению. Блок 1 обработки данных соединен с питающим напряжением VCC не непосредственно, а вход 6 питающего напряжения имеет возможность отсоединения от питающего напряжения посредством первого переключателя S1. Кроме того, с входом 6 питающего напряжения соединен опорный конденсатор С. Когда первый переключатель S1 разомкнут, питающее напряжение для блока 1 обработки данных обеспечивается опорным конденсатором С. Рабочий интервал, в течение которого блок 1 обработки данных может получать питание посредством опорного конденсатора С, зависит от емкости конденсатора С, а также от потребления тока блоком 1 обработки данных. Целью данного устройства является то, чтобы при проведении критически важных, т.е. релевантных с точки зрения защищенности вычислительных операций в блоке 1 обработки данных, развязать этот блок от питающего напряжения, чтобы предотвратить возможность несанкционированного получения выводов касательно секретного ключа на основе потребления тока всей схемы с блоком 1 обработки данных. Если, однако, по окончании проведения вычислительных операций переключатель S1 снова замыкается, то конденсатор вновь заряжается, при этом на основе тока заряда по-прежнему можно распознать, какой заряд конденсатора С потребовался для проведения защищенных вычислительных операций.

Чтобы предотвратить такую возможность, конденсатор С разряжается до определенного значения напряжения и только после этого вновь заряжается до номинального напряжения. Потенциальная возможность для этого могла бы состоять в том, чтобы конденсатор С разряжать до постоянного напряжения, генерированного соответствующей схемой. Это в общем случае означало бы, что источник постоянного напряжения переключается на емкостную нагрузку. Однако поскольку источник постоянного тока на практике не идеален и запитывается от питающего напряжения, то и при таком решении наблюдается питающий ток, зависимый от уровня напряжения конденсатора С. Тем самым такая схема не пригодна для того, чтобы полностью скрывать потребление тока во время осуществления секретных вычислительных операций.

В соответствии с изобретением конденсатор С, в противоположность описанному выше, разряжается через источник 3 постоянного тока до тех пор, пока напряжение на конденсаторе С не достигнет предварительно определенного нижнего граничного значения. После этого цепь разряда прерывается посредством переключателя S2, и замыкается переключатель S1, чтобы тем самым обеспечить повторный заряд конденсатора С. Определение нижнего граничного значения напряжения осуществляется посредством компаратора 2, который сравнивает напряжение на конденсаторе С с эталонным напряжением Uref. На выходе компаратора 2 подключен блок 4 управления, который осуществляет управление переключателем S1 и S2. Блок 4 управления сам управляется от блока 1 обработки данных перед началом и после окончания проведения секретной вычислительной операции. Тем самым указывается, когда переключатель S1 должен размыкаться, чтобы снабжение питанием блока 1 обработки данных производилось через опорный конденсатор С, и когда должен осуществляться процесс разряда, т.е. замыкание переключателя S2. Конец процесса разряда определяется самостоятельно посредством компаратора, и тем самым устанавливается момент времени для размыкания переключателя S2 и замыкания переключателя S1. Кроме того, блок 4 управления может управляться посредством дополнительного входа 5, например, через дополнительную схему, которая определяет начальные условия.

При разряде конденсатора через сопротивление R напряжение на конденсаторе, без использования дополнительных мер, спадает согласно e-функции. Когда, как в схеме по фиг.1, компаратор 2 в этих условиях установит, что достигнуто нижнее предварительно заданное напряжение конденсатора, то проходит еще некоторое время, прежде чем переключатель S2 разомкнется. В течение этого времени конденсатор С продолжает разряжаться. Хотя время запаздывания компаратора 2 и переключателя S2 всегда одинаково, однако так как напряжение на конденсаторе С спадает согласно е-функции, то действительное конечное напряжение конденсатора С все еще зависит от его предшествующего уровня заряда.

Поэтому разряд в соответствующем изобретению варианте выполнения происходит с использованием постоянного тока, что обеспечивается источником 3 постоянного тока, так что хотя в течение времени запаздывания компаратора 2 и переключателя S2 напряжение на конденсаторе С продолжает падать, однако его конечное значение не зависит от предшествующего состояния заряда.

На фиг.2 показан конкретный вариант выполнения соответствующего изобретению схемного устройства со схемой зеркального отображения тока для реализации источника постоянного тока и устройством, состоящим из схемы “И” 11, двухфазного генератора 12 и триггерной схемы 13 для реализации блока управления. Вход 6 питающего напряжения блока 1 обработки данных, как в примере выполнения по фиг.1, связан с питающим напряжением VCC. Также предусмотрен опорный конденсатор С, посредством которого обеспечивается питание блока 1 обработки данных, когда переключатель S1 разомкнут. В отличие от фиг.1, неинвертирующий вход компаратора 2 связан не непосредственно с конденсатором С или входом 6 питающего напряжения, а напряжение снимается с точки между сопротивлением R и последовательно включенным транзистором Т4. Разряд конденсатора С осуществляется, таким образом, через сопротивление R и транзистор Т4, которые в процессе разряда образуют делитель напряжения. Выбор точки съема напряжения между сопротивлением R и транзистором Т4 объясняется тем, что сравнение напряжения компаратором 2 должно производиться с эталонным напряжением Uref, и это эталонное напряжение Uref должно вырабатываться посредством эталона запрещенной полосы. Напряжение эталона запрещенной полосы в типовом случае составляет примерно 1,203 В, в то время как напряжение, до которого конденсатор должен разрядиться, в наиболее благоприятном случае составляет 2,0 В. Поэтому должен предусматриваться делитель напряжения, состоящий из сопротивления R и транзистора Т4, чтобы на сопротивлении падало напряжение, примерно равное 0,8 В. Если бы напряжение снималось непосредственно с конденсатора С, то сравнение с эталоном запрещенной полосы было бы невозможным.

Источник постоянного тока реализуется посредством схемы зеркального отображения тока с сопротивлением Rs и транзистором Т3 в опорной ветви, а также с транзистором Т4. В опорной ветви сопротивление Rs включено последовательно с транзистором Т3 и находится между постоянным напряжением Vkonst и опорным потенциалом 0. Посредством величины сопротивления Rs и постоянного напряжения Vkonst тем самым устанавливается, какой ток протекает в опорной ветви. Посредством этого также определяется, какой ток может протекать через транзистор Т4. Через транзистор Т1, который включен между управляющим выводом транзистора Т4 и опорным потенциалом, включен транзистор Т4. Посредством транзистора Т2, который включен между управляющим выводом транзистора Т3 и управляющим выводом транзистора Т4, зеркальное отображение тока может включаться и выключаться.

Если конденсатор находится не на своем нижнем уровне напряжения, то результатом сравнения компаратора 2 является сигнал высокого логического уровня. Когда переключатель S1 размыкается, триггерная схема сбрасывается, и на инвертирующем выходе qn триггерной схемы 13 имеется высокий логический уровень. Если теперь дополнительно от блока 1 обработки данных сигнализируется, что релевантные с точки зрения защиты вычислительные операции завершены, и конденсатор может разряжаться, то выход 14 блока 1 обработки данных находится на высоком логическом уровне, и этот сигнал прикладывается в качестве третьего входного сигнала к схеме “И” 11. Тем самым уровень напряжения на выходе схемы “И” 11 переходит на высокий логический уровень, и затем вводится процесс разряда. Посредством двухфазного генератора 12 из выходного сигнала схемы “И” 11 генерируются два задержанных во времени сигнала 16 и 15. Сначала посредством сигнала 16 отпирается транзистор Т1, так что транзистор Т4 может перейти в проводящее состояние. Вторым сигналом 15 переключается транзистор Т2, так что схема зеркального отображения тока активизируется и отображает ток через сопротивление Rs в ветвь разряда. Так как ток iD разряда постоянный, то на сопротивлении R падает постоянное напряжение, которое в этом варианте осуществления установлено на 0,8 В. При первоначальном напряжении 2,4 В на конденсаторе С и падении напряжения 0,8 В на сопротивлении R, на неинвертирующем входе компаратора 2 приложено теперь напряжение 1,6 В, в то время как эталонное напряжение Uref составляет 1,2 В. Только при разряде конденсатора до напряжения 2 В напряжение на неинвертирующем входе компаратора 2 становится меньше, чем напряжение на инвертирующем входе. В этот момент происходит падение выходного сигнала компаратора 2, и за счет этого сигнала низкого логического уровня на входе схемы “И” 11 ее выход также переходит на низкий логический уровень. Затем транзистор Т1 переключается в проводящее состояние, так что транзистор Т4 разряда запирается, и разряд конденсатора С заканчивается. После замыкания переключателя S1 конденсатор С может вновь заряжаться.

Разумеется, для подобного функционирования возможны различные выполнения схемного устройства, и если только в них предусматривается, что опорный конденсатор С разряжается постоянным током iD, то такие схемы входят в объем изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМНЫЙ УЗЕЛ И СПОСОБ КОНТРОЛЯ МИКРОКОНТРОЛЛЕРА НА ОСНОВЕ СТОРОЖЕВОГО НАПРЯЖЕНИЯ | 2016 |

|

RU2697027C1 |

| УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ЭНЕРГИИ И ГЕНЕРАТОР ЭНЕРГИИ, СОДЕРЖАЩИЙ ТАКОЕ УСТРОЙСТВО | 2019 |

|

RU2780813C2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОЧЕНЬ МАЛЫХ ЕМКОСТЕЙ И ЕГО ПРИМЕНЕНИЕ | 1999 |

|

RU2216027C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЕМКОСТНОГО ОБНАРУЖЕНИЯ ОБЪЕКТОВ | 2008 |

|

RU2486530C2 |

| СЕНСОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ | 1990 |

|

RU2067354C1 |

| УСТРОЙСТВО ДЛЯ ЗАРЯДКИ БАТАРЕЙ | 2007 |

|

RU2448402C2 |

| СХЕМНЫЙ УЗЕЛ ДЛЯ ОТКЛЮЧАЕМОЙ ОКОНЕЧНОЙ НАГРУЗКИ ЛИНИИ ПОСЛЕДОВАТЕЛЬНОЙ ШИНЫ | 2016 |

|

RU2701382C1 |

| УСТРОЙСТВО И СПОСОБ ВОЗБУЖДЕНИЯ ДЛЯ ВОЗБУЖДЕНИЯ НАГРУЗКИ, В ЧАСТНОСТИ, БЛОКА СВЕТОДИОДОВ | 2012 |

|

RU2589734C2 |

| ДАТЧИК УРОВНЯ ЧЕРНИЛ И ОТНОСЯЩИЕСЯ К НЕМУ СПОСОБЫ | 2011 |

|

RU2561029C1 |

| БЛОК УПРАВЛЕНИЯ И СПОСОБ ДЛЯ ПРИВЕДЕНИЯ В ДЕЙСТВИЕ СРЕДСТВ БЕЗОПАСНОСТИ, А ТАКЖЕ ДАТЧИК ДЛЯ ВЫДАЧИ СИГНАЛА АВАРИЙНОЙ СИТУАЦИИ | 2008 |

|

RU2527742C2 |

Изобретение относится к способу управления фазами заряда и разряда опорного конденсатора (К) (С) носителя данных, причем опорный К (С) перед зарядом разряжается только до предварительно определенного уровня напряжения. Технический результат заключается в предотвращении возможности несанкционированного доступа к информации на основе потребления тока блоком обработки данных. Разряд К (С) осуществляется постоянным током (iD), что не позволяет распознать, каким было состояние заряда К (С) перед разрядом. Благодаря этому невозможно сделать выводов о токах, протекающих в блоке (1) обработки данных в процессе выполнения релевантных для обеспечения защиты вычислительных операций. В предпочтительном варианте выполнения устройства источник (3) постоянного тока образован схемой зеркального отображения тока, и посредством компаратора (2) напряжение на опорном К (С) сравнивается с эталоном запрещенной полосы напряжения разряда. 2 н. и 2 з.п. ф-лы, 2 ил.

| DE 19850293 A1, 04.05.2000 | |||

| Рамочный фильтр-пресс | 1941 |

|

SU63827A1 |

| DE 19911673 A1, 14.09.2000 | |||

| ПАРОПРОНИЦАЕМАЯ ВСТАВКА ДЛЯ ПРЕДМЕТОВ ОДЕЖДЫ И АКСЕССУАРОВ, ПРЕДМЕТ ОДЕЖДЫ И АКСЕССУАРЫ С УПОМЯНУТОЙ ВСТАВКОЙ | 2018 |

|

RU2776410C2 |

| КАРТА СО ВСТРОЕННОЙ МИКРОСХЕМОЙ | 1996 |

|

RU2142648C1 |

| КАРТОЧКА С ВСТРОЕННЫМ МИКРОПРОЦЕССОРОМ | 1997 |

|

RU2154859C2 |

Авторы

Даты

2005-05-10—Публикация

2001-11-06—Подача