Изобретение относится к карточке с встроенным микропроцессором, содержащей корпус карточки и размещенную внутри корпуса карточки полупроводниковую интегральную схему, в которой интегрально выполнены управляющая схема и электрически связанное с управляющей схемой полупроводниковое запоминающее устройство, при этом управляющая схема снабжается питающим напряжением, создаваемым схемой питающего напряжения, и тактовым сигналом, создаваемым расположенной отдельно от управляющей схемы схемой тактовых сигналов, при этом питающее напряжение имеет рабочее значение, находящееся внутри заданных пределов рабочего питающего напряжения, и подаваемым тактовой сигнал имеет рабочую величину тактовой частоты, находящуюся внутри заданных пределов рабочей тактовой частоты.

Возможности использования выполненных как правило в формате чековых карточек карточек с встроенным микропроцессором стали чрезвычайно многосторонними на основе их функциональной гибкости и продолжают увеличиваться с повышением скорости обработки данных и емкости памяти имеющихся интегральных схем. Наряду с типичными в настоящее время областями применения таких карточек с встроенным микропроцессором в виде карточек медицинского страхования, карточек учета рабочего времени при скользящем графике, телефонных карточек, в будущем открываются новые возможности применения, в частности для выполнения электронных платежных операций, для контроля за доступом к ЭВМ, для защищенных банков данных и т.д. При использовании микроконтроллеров в карточках с встроенным микропроцессором необходимо в большинстве случаев выполнять очень высокие требования безопасности для эффективного предотвращения несанкционированного доступа к закрытым данным владельца карточки или манипулирования с денежными суммами. Поэтому в известные до настоящего времени карточки с встроенным микропроцессором включают элементы защиты, которые относительно их принципа действия можно разделить на пассивные и активные защитные механизмы и которые описаны, например, в справочнике с названием "Карточки с встроенным микропроцессором", издательство Карл Ханзер Ферлаг, 1995, страницы 208 - 213.

Пассивные механизмы защиты в основном базируются на технологии изготовления полупроводников. Например, для проверки интегральных микросхем во время изготовления полупроводников и для выполнения всех внутренних проверочных программ все микроконтроллеры имеют так называемый режим проверки, в котором полупроводниковые схемы можно проверять еще на подложке или в модуле. Этот режим проверки позволяет производить такие входы в память, которые в последующем строго запрещены, так что переключение с режима проверки в режим пользования должно быть выполнено необратимым. Это осуществляют как правило с помощью поликремниевых предохранителей в интегральной схеме. Кроме того, известно располагать внутренние шины в интегральной схеме, которые соединяют процессор с тремя различными видами памяти: постоянной памятью, электрически стираемой программируемой постоянной памятью и оперативной памятью, не выходящими наружу и тем самым без возможности контактирования без применения очень трудоемких способов, с помощью кодированного расположения отдельных проводников шин располагать их в запутанном и многократно измененном положении. Таким образом, нет возможности для несанкционированного подслушивания адресной шины, шины данных и управляющей шины микроконтроллера или влияния на них и тем самым считывания содержания памяти. Кроме того, размещение полупроводниковой памяти не в самых верхних и тем самым в самых легкодоступных слоях, а в нижних кремниевых слоях предотвращает, соответственно, затрудняет считывание содержания постоянной памяти бит за битом с помощью оптического микроскопа. Другую опасность представляет анализ электрических потенциалов в интегральной схеме во время ее работы. При достаточно высокой частоте сканирования имеется возможность измерять потенциалы заряда, т.е. напряжения, на очень небольших участках интегральной схемы и таким образом делать выводы о содержании полупроводниковой памяти с произвольным доступом (RAM) во время работы и тем самым получать возможность получения закрытых данных владельца карточки. Это может быть в определенной степени предотвращено с помощью дополнительного слоя металлизации над соответствующими ячейками памяти. Если такой металлический слой удалить, например, химическим способом, то интегральная схема больше не может работать, так как металлизированный слой необходим для правильной работы интегральной схемы в качестве электрического проводника для подачи напряжения.

Кроме того, известны активные механизмы защиты для карточек с встроенным микропроцессором, которые предотвращают несанкционированный доступ к данным. Например, может быть предусмотрена сенсорная схема, которая посредством измерения сопротивления или емкости устанавливает присутствие на кремниевом кристалле пассивированного слоя, нанесенного на поверхность кристалла и предназначенного для предотвращения окисления, который необходимо удалить для проведения манипуляций с интегральной схемой. Если пассивированного слоя больше нет или он поврежден, то включается режим прерывания в программном обеспечении интегральной схемы или вся интегральная схема отключается от аппаратных средств, так что надежно предотвращаются все динамические анализы. Кроме того, известно предусматривать в микроконтроллере карточки с встроенным микропроцессором схему слежения за напряжением, которая обеспечивает надежное отключение блока, если напряжение становится выше или ниже верхней, соответственно, нижней границы рабочего напряжения. Тем самым обеспечивается для программного обеспечения надежность того, что невозможна работа в пограничных областях, в которых интегральная схема не является полностью работоспособной. Другое чувствительное устройство, работающее частично на распознавании напряжения, обеспечивает так называемое распознавание включение питания. Эта также присутствующая в интегральной схеме функция распознавания включения питания независимо от сигнала сброса обеспечивает то, что интегральная схема при включении всегда переводится в определенную область. Кроме того, известно выполнять в микропроцессоре функциональную группу для обнаружения недостаточной частоты. Она предотвращает недопустимое снижение приложенной тактовой частоты. Снабжение карточки с встроенным микропроцессором тактовым сигналом происходит как правило извне, так что внутренняя скорость вычислений определяется полностью извне. Тем самым существует теоретически возможность управления работой микроконтроллера извне в режиме отдельных шагов. Это приводило бы к возможности несанкционированного анализа прежде всего посредством измерения потребления тока и электрических потенциалов в интегральной схеме.

Карточка с встроенным микропроцессором согласно ограничительной части пункта 1 формулы изобретения известна, например, из DE-A-4 328753. Для предотвращения несанкционированного доступа к закрытому коду в качестве защитной меры предусмотрен счетчик, который определяет количество несанкционированных доступов к закрытому коду и при превышении предельного значения полностью блокирует карточку с встроенным микропроцессором.

Из EP-A-О 481881 известна карточка с встроенным микропроцессором с электрически стираемой программируемой постоянной памятью и центральным процессором, которые снабжены защитными детекторами для определения ненормальных рабочих и окружающих состоянии. Детекторы соединены с регистром RS, информационное содержание которого в случае логической единицы управляет переключением на подпрограмму центрального процессора, которая прерывает работу центрального процессора.

Из NL-A-8 903111 известна карточка с встроенным микропроцессором с постоянной памятью и детекторами, с помощью которых карточка с встроенным микропроцессором приводится в негодность в качестве реакции на не санкционированную карточкой попытку доступа к постоянной памяти. Постоянная память представляет собой статическую память с произвольной выборкой (SRAM). Карточка с встроенным микропроцессором имеет переключатель с первым положением и со вторым положением, при этом детекторы при обнаружении несанкционированной попытки доступа переводят переключатель из первого положения во второе положение для приведения в негодность карточки с встроенным микропроцессором.

Все известные до настоящего времени защитные меры для предотвращения несанкционированного доступа к закрытым данным карточки с встроенным микропроцессором имеет общим то, что после приведения в действие соответствующей меры защиты карточка с встроенным микропроцессором становится в целом неработоспособной.

В основе изобретения лежит задача создать активное защитное устройство для карточки с встроенным микропроцессором согласно уровню техники, соответственно, усовершенствовать так, чтобы можно было исключить опасность несанкционированного доступа к информационному содержанию ячеек памяти расположенного внутри карточки полупроводникового запоминающего устройства с произвольным доступом, при одновременном оставлении работоспособными схемных компонентов карточки с встроенным микропроцессором, не затронутых несанкционированным доступом.

Указанный результат достигается тем, что карточка с встроенным микропроцессором, содержащая корпус карточки и размещенную внутри корпуса карточки полупроводниковую интегральную схему, в которой интегрально выполнены управляющая схема и электрически связанное с управляющей схемой полупроводниковое запоминающее устройство, при этом управляющая схема снабжается питающим напряжением, создаваемым схемой питающего напряжения, и тактовым сигналом, создаваемым расположенной отдельно от управляющей схемы схемой тактовых сигналов, при этом управляющая схема соединена с сенсорной схемой, которая регистрирует отклонение разрешенного рабочего состояния управляющей схемы и/или других схемных компонентов полупроводниковой интегральной схемы, в соответствии с изобретением дополнительно содержит включенную за сенсорной схемой систему запуска, которая при наличии неразрешенного рабочего состояния управляющей схемы и/или других схемных компонентов создает сигнал сброса и независимо от снабжения управляющей схемы тактовым сигналом выдает сигнал сброса в полупроводниковое запоминающее устройство на стирание информационного содержания всех ячеек памяти полупроводникового запоминающего устройства.

При этом сенсорная схема предпочтительно соединена со схемами обеспечения управляющей схемы тактовым сигналом и/или питающим напряжением и регистрирует отклонение питающего напряжения от рабочего напряжения и/или отклонение тактовой частоты от рабочей тактовой частоты, и при наличии отклонения рабочего питающего напряжения и/или рабочей тактовой частоты создает сигнал сброса.

Кроме того, сенсорная схема предпочтительно имеет схему детектирования напряжения, которая регистрирует превышение питающего напряжения заданного верхнего, соответственно, понижение ниже заданного нижнего предельного значения рабочего напряжения.

А также сенсорная схема предпочтительно имеет схему детектирования частоты, которая регистрирует превышение тактовой частоты заданного верхнего, соответственно, понижение ниже заданного нижнего предельного значения рабочей тактовой частоты.

При этом управляющая схема предпочтительно представляет собой схему микропроцессора интегрально выполненной в полупроводниковой интегральной схеме схемы микроконтроллера, которая наряду с полупроводниковым запоминающим устройством содержит другие функциональные блоки, в частности полупроводниковую постоянную память и/или электрически стираемую программируемую постоянную память.

Кроме того, в заявленной карточке с встроенным микропроцессором предпочтительно предусмотрено, что одновременно со стиранием информационного содержания ячеек памяти полупроводникового запоминающего устройства стирается также информационное содержание соединенного с управляющей схемой регистра или аккумулятора.

Таким образом, согласно изобретению, при любом отклонении разрешенного рабочего состояния размещенной в карточке с встроенным микропроцессором управляющей схемы и/или других схемных компонентов автоматически происходит мгновенное стирание имеющего значение для безопасности или относящегося к личности владельца информационного содержания. Отклонение от разрешенного рабочего состояния управляющей схемы может быть вызвано, например, несанкционированным доступом или несанкционированной манипуляцией схемными компонентами карточки с встроенным микропроцессором, например, при попытке считывания закрытых данных с помощью несанкционированного входа. За счет отклонения от разрешенного рабочего состояния такая попытка манипулирования автоматически распознается и запускается автоматическое стирание, в частности, всего закрытого информационного содержания. Такое информационное содержание временно запоминается, например, в связанной электрически с управляющей схемой полупроводниковой памяти с произвольным доступом, а также, например, в приданном управляющей схеме регистре памяти, например, в так называемом специальном регистре, или в аккумуляторе. Таким образом, создаваемый сенсорной схемой при отклонении от разрешенного рабочего состояния сигнал запуска управляет не только стиранием соответствующей информации в полупроводниковой памяти с произвольным доступом (RAM), но также стиранием информационного содержания других запоминающих и регистровых устройств, в которых по меньшей мере временно запоминаются такие данные, через которые можно выйти на закрытую информацию.

Существенное преимущество изобретения состоит в том, что в случае возникновения неразрешенного рабочего состояния способность работы других схемных компонентов, не затронутых попыткой манипулирования, в частности самой управляющей схемы, сохраняется. Таким образом могут еще обрабатываться информационные сигналы после выявления попытки манипулирования. Например, может еще происходить передача данных на находящийся в соединении с карточкой с встроенным микропроцессором терминал, и может быть выдана команда на блокирование карточки с выдачей соответственных персональных данных.

В особенно просто реализуемом схемном решении может быть предусмотрено, что после обнаружения неразрешенного рабочего состояния автоматически происходит полное стирание информационного содержания. Это может быть осуществлено, предпочтительно, посредством выдачи сигнала сброса всем соответствующим ячейкам памяти и регистрам полупроводникового запоминающего устройства.

В предпочтительном варианте выполнения изобретения предусмотрено, что сенсорная схема соединена со схемами обеспечения управляющей схемы тактовым сигналом и/или питающим напряжением и распознает отклонение питающего напряжения от рабочего напряжения и/или отклонение подаваемой тактовой частоты от рабочей тактовой частоты, и при наличии отклонения рабочего напряжения и/или рабочей тактовой частоты создает сигнал запуска, который подается на включенную за сенсорной схемой и соединенную с полупроводниковым запоминающим устройством схему запуска, которая в качестве реакции на сигнал запуска управляет по меньшей мере частичным стиранием информационного содержания полупроводникового запоминающего устройства.

В частности, предусмотренная в карточке с встроенным микропроцессором и служащая для временного запоминания персональных данных полупроводниковая память с произвольным доступом (RAM)* представляет собой в некотором смысле слабое место выполненного в полупроводниковой интегральной схеме микроконтроллера, так как ее ячейки памяти содержат закрытую информацию в упорядоченном виде, которую можно считать при несанкционированном доступе с помощью относительно просто выполняемых мер. Благодаря изобретению, при попытке несанкционированного считывания информационного содержания посредством манипулирования с рабочим напряжением или частотой автоматически вызывается мгновенное стирание ячеек памяти. С помощью этой меры по меньшей мере значительно затрудняется несанкционированное считывание полупроводниковой памяти, в которой в рабочем состоянии временно запоминается закрытая информация, соответственно, коды. Тем самым становится в частности невозможным переводить полупроводниковую интегральную схему в неразрешенное рабочее состояние, для того, чтобы затем спокойно, "квазистатически" считывать информационное содержание, которое удерживает полупроводниковая память, пока не отключено рабочее напряжение.

В предпочтительном варианте выполнения изобретения может быть предусмотрено, что включенная после сенсорной схемы схема запуска выдает сигнал сброса на полупроводниковую память для стирания информационного содержания всех ячеек памяти полупроводниковой памяти с произвольным доступом. При этом может быть в частности предусмотрено, что управление по меньшей мере частичным стиранием информационного содержания ячеек памяти полупроводниковой памяти с произвольным доступом происходит с помощью включенной после сенсорной схемы схемы запуска независимо от подаваемого на управляющую схему тактового сигнала. При этом во всех четырех возможных случаях, в которых сенсорная схема создает сигнал запуска, запускается стирание всей полупроводниковой памяти с произвольным доступом, которое происходит асинхронно независимо от подачи тактового сигнала на управляющую схему, с целью обеспечения того, что сенсорная схема и схема запуска исправно работают также при полном отключении тактового сигнала.

Другие преимущества, признаки и целесообразности изобретения следуют из последующего описания примера выполнения с помощью чертежей, на которых изображено:

фиг. 1 - схематичный вид сверху карточки с встроенным микропроцессором; и

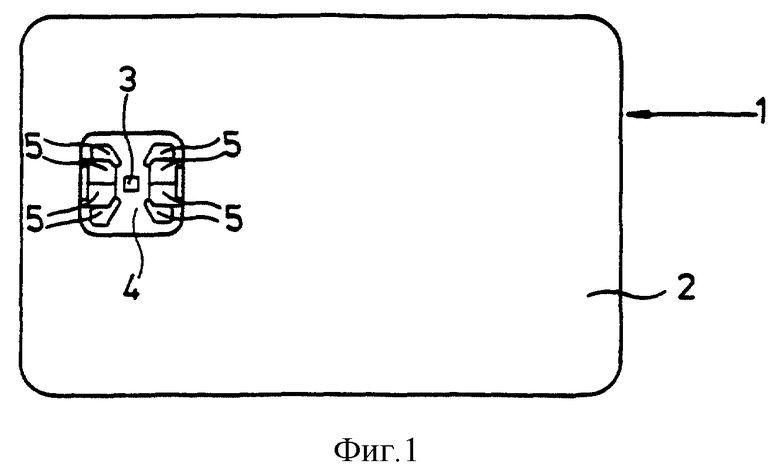

фиг. 2 - схематичный вид - электронных схемных компонентов, предусмотренных в размещенной в корпусе карточки полупроводниковой интегральной схеме.

На фиг. 1 показана карточка 1 с встроенным микропроцессором, содержащая корпус 2 карточки и размешенную внутри корпуса 2 карточки полупроводниковую интегральную схему 3, которая выполнена в качестве составной части предварительно изготовленного модуля 4 микропроцессора, на поверхности которого распоюжены металлические контактные элементы 5 для подвода энергии и передачи данных наружу. Вместо карточки с встроенным микропроцессором, снабженной контактами, карточка с встроенным микропроцессором согласно изобретению может представлять собой также бесконтактную карточку.

На фиг. 2 показаны наиболее важные функциональные схемные компоненты выполненной в полупроводниковой интегральной схеме 3 схемы микроконтроллера 6, которая является центральной составной частью карточки 1 с встроенным микропроцессором. Показана управляющая схема, соответственно, схема микропроцессора 7 и три различных полупроводниковых запоминающих устройства, в частности полупроводниковая память с произвольным доступом (RAM) 8, постоянная память (ROM) 9, а также электрически стираемая программируемая постоянная память (EEPROM) 10. В постоянной памяти 9 карточки 1 с встроенным микропроцессором расположено большинство рабочих системных программ, а также различные функции тестирования и диагностики. Эти программы вводятся изготовителем при производстве полупроводниковой интегральной схемы 3. По сравнению с постоянной памятью и с памятью с произвольным доступом технически более сложная электрически стираемая программируемая постоянная память 10 используется в карточке 1 с встроенным микропроцессором для всей информации и программ, которые и любом момент времени должны быть один раз изменены или стерты. В смысле функционирования электрически стираемая программируемая постоянная память соответствует винчестерскому диску персонального компьютера, так как данные остаются сохраненными также без подвода питания и могут быть при потребности изменены. Память 8 с произвольным доступом представляет собой память карточки 1 с встроенным микропроцессором, в которую во время одного сеанса можно как угодно часто заносить и изменять данные. Таким образом, в отношение возможных обращений память 8 с произвольным доступом не имеет таких ограничений, как электрически стираемая программируемая постоянная память 10. Для сохранения данных память 8 с произвольным доступом нуждается в питающем напряжении. Если питающее напряжение не подается или если оно отключается на короткое время, то содержание памяти 8 с произвольным доступом не является больше определенным. Память 8 с произвольным доступом состоит из множества транзисторов, которые включены так, что они работают как бистабильные триггеры. При этом состояние схемы репрезентирует содержание памяти в один бит в памяти 8 с произвольным доступом. Используемая в карточке 1 с встроенным микропроцессором память 8 с произвольным доступом является статической памятью, т.е. содержание памяти не должно периодически обновляться. Тем самым память 8 с произвольным доступом не зависит от внешнего тактового сигнала в отличие от динамической памяти с произвольным доступом. Использование статической памяти 8 с произвольным доступом важно еще и потому, что должно быть возможным останавливать подачу тактового сигнала в карточку с встроенным микропроцессором в так называемом ждущем режиме, что было бы невозможным в динамической памяти с произвольным доступом. Используемый в карточке 1 с встроенным микропроцессором микропроцессор 7 представляет собой известный тип процессора, набор команд которого ориентируется, например, на архитектуру Интел 8051 и может быть частично дополнен другими командами. Для питания напряжением схемных компонентов схемы микроконтроллера 6 предусмотрена схема 12 питающего напряжения, питаемая извне через вводы GND (масса) и Vcc (питающее напряжение) контактов 5 карточки 1 с встроенным микропроцессором, которая поставляет рабочее напряжение, величина которого находится в заданных пределах рабочего напряжения, например, 3 -5 B + 10%. Кроме того, предусмотрена изображенная схематично вводом Clk (такт) схема 13 снабжения тактовым сигналом, которая снабжает микропроцессор 7 тактовым сигналом, необходимым для определенном временной последовательности выполнения команд и определяющим скорость вычислений схемы микроконтроллера 6, который имеет величину рабочей частоты, находящейся в заданных пределах рабочей тактовой частоты, например, между 1 и 5 МГц, в будущем около 7.5 МГц, 10 МГц. По отношению к схеме микропроцессора 7 тактовый сигнал задается отдельной от него и схематично изображенной схемой 13 снабжения тактовым сигналом, так что внутренняя скорость вычислений полностью определяется извне. Тем самым существует теоретически возможность управления схемой микроконтроллера 6 извне в режиме отдельных шагов, что может создавать возможность несанкционированного анализа, прежде всего посредством измерения потребления тока и электрического потенциала в полупроводниковой интегральной схеме 3. Согласно изобретению предусмотрена сенсорная схема 14, соединенная с подаваемым тактовым сигналом и/или питаемым напряжением управляющей схемы 7, которая со стороны входа через проводники 15 и 16 регистрирует подаваемые непосредственно на управляющую схему 7 тактовый сигнал и/или питающее напряжение, и при наличии отклонения от рабочего напряжения и/или от тактовой частоты создает сигнал запуска, который по проводнику 17 подается на схему 18 запуска, включенную после сенсорной схемы 14 и соединенную с полупроводниковой памятью 8, которая в качестве реакции на сигнал запуска управляет по меньшей мере частичным стиранием информационного содержания ячеек 19 памяти полупроводниковой памяти 6. При этом сенсорная схема 14 содержит, с одной стороны, схему 20 детектирования напряжения, которая регистрирует нахождение питающего напряжения выше или ниже заданных верхнего, соответственно, нижнего предельного значения рабочего напряжения, и с другой стороны, схему 21 детектирования частоты, которая регистрирует нахождение частоты тактового сигнала выше или ниже заданных верхнего, соответственно, нижнего предельного значения рабочей тактовой частоты. Соединенная проводником 22 с полупроводниковой памятью 8 схема 18 запуска создает в качестве реакции на поставляемый сенсорной схемой 14 сигнал запуска, предпочтительно, сигнал сброса, на основании которого стирается информационное содержание всех ячеек 19 памяти полупроводниковой памяти 8. Этот сигнал сброса сознается независимо от подводимого через ввод 23 контакта 5 внешнего сигнала RST. Одновременно со стиранием информационного содержания ячеек памяти полупроводниковой памяти с произвольным доступом может быть стерто согласно изобретению также информационное содержание входящего в управляющую схему, схематично показанного на фиг. 2 регистра или аккумулятора 11.

Изобретение относится к вычислительной технике и может использоваться при медицинском страховании, учете рабочего времени в скользящем графике, телефонии и т. д. Техническим результатом является повышение защищенности карточки со встроенным микропроцессором от несанкционированного доступа при одновременном оставлении работоспособными схемных компонентов упомянутой карточки, не затронутых несанкционированным доступом. Для этого карточка содержит управляющую схему, полупроводниковое запоминающее устройство, схему питающего напряжения, схему тактовых сигналов, сенсорную схему, схему запуска. 5 з.п.ф-лы, 2 ил.

| DE 4328753 A1, 03.03.1994 | |||

| Электропривод с центробежным регулятором скорости | 1969 |

|

SU475716A1 |

| Генератор строчной развертки | 1973 |

|

SU467497A1 |

| US 3740530 A, 19.06.1973 | |||

| US 4199100 A, 22.04.1980 | |||

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПЛАТЕЖЕЙ С ПОМОЩЬЮ ЭЛЕКТРОННОЙ КАРТОЧКИ | 1993 |

|

RU2035067C1 |

| АБОНЕНТСКАЯ КАРТОЧКА | 1990 |

|

RU2011225C1 |

Авторы

Даты

2000-08-20—Публикация

1997-03-04—Подача