Изобретение относится к области радиоизмерений и предназначено для оценки нелинейных искажений, вносимых трактами обработки или усиления низкочастотных сигналов, например звуковых.

Прототипом заявляемого устройства является устройство, содержащее генератор случайного сигнала, полосовой фильтр, фильтр нижних частот и вольтметр, вход которого соединен с выходом фильтра нижних частот, вход которого является тестовым входом устройства, тестовым выходом которого служит выход полосового фильтра, вход которого соединен с выходом генератора случайного сигнала [Сырицо А. Измерение нелинейных искажений на шумовом сигнале. - Радио, 1999 г., №4, стр.29-31].

Принцип действия измерителя-прототипа заключается в подаче на вход тестируемого узла (например, усилителя) случайного сигнала в ограниченной полосе частот, а затем измерении уровня сигнала на выходе усилителя вне полосы частот входного тестового сигнала. Поскольку результатом интермодуляционных искажений являются и составляющие с комбинационными частотами, выходящими за пределы полосы частот входного сигнала, то по отношению напряжения этих составляющих к напряжению входного сигнала судят об уровне интермодуляционных искажений. Причем в качестве интермодуляционных составляющих берется только часть сигнала, расположенная в низкочастотной области спектра выходного искаженного сигнала, выделенная фильтром нижних частот. При этом другие комбинационные составляющие, находящиеся как в полосе частот входного сигнала, так и выше нее, не учитываются. Безусловно, такой подход, отличаясь простотой аппаратурной реализации, не обеспечивает высокой точности измерений и не позволяет судить о реальном уровне вносимых искажений по всему диапазону рабочих частот тестируемого усилителя.

Технический результат, достигаемый при использовании настоящего изобретения, состоит в повышении точности оценки уровня шумовой интермодуляции, вызванной нелинейной характеристикой тестируемого узла.

Технический результат достигается тем, что в измеритель уровня шумовой интермодуляции, содержащий генератор случайного сигнала и полосовой фильтр, вход которого соединен с выходом генератора случайного сигнала, выход полосового фильтра является тестовым выходом измерителя, согласно изобретению введены мультиплексор, коррелятор, блок сравнения и блок управления, вход которого является входом запуска измерителя, тестовым входом которого служит первый информационный вход мультиплексора, второй информационный вход которого соединен с выходом полосового фильтра, выход мультиплексора соединен с информационным входом коррелятора, выход которого соединен с информационным входом блока сравнения, выход которого является информационным выходом измерителя, адресный вход мультиплексора, тактовый и обнуляющий входы коррелятора, а также входы управления блоком сравнения соединены с соответствующими выходами блока управления, адресный выход которого соединен с единой адресной шиной коррелятора и блока сравнения.

Блок сравнения может быть выполнен в виде устройства, вычисляющего среднее значение модуля разности сравниваемых величин, в виде устройства, вычисляющего среднеквадратичное значение разности сравниваемых величин, в виде устройства, вычисляющего среднее отношение сравниваемых величин.

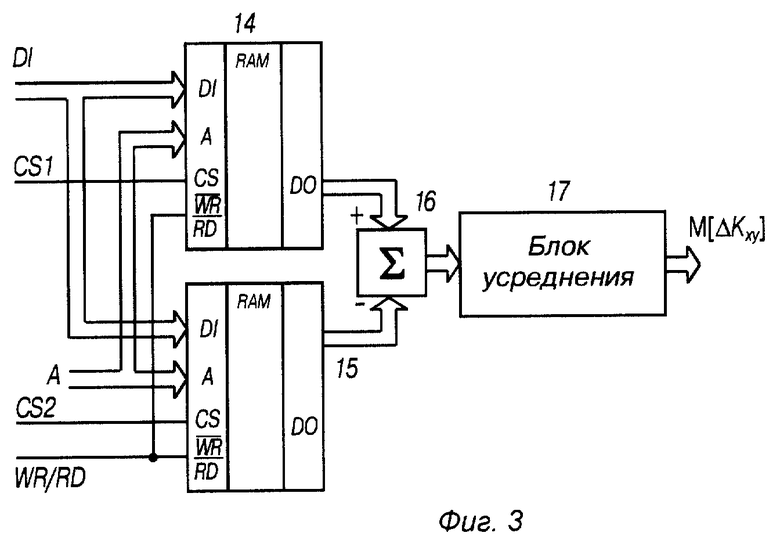

Кроме того блок сравнения, выполненный как устройство, вычисляющее среднее значение модуля разности сравниваемых величин, может содержать два оперативных запоминающих устройства, блок вычитания и блок усреднения, выход которого является выходом блока сравнения, адресным входом которого служат объединенные адресные входы оперативных запоминающих устройств, информационные входы которых также объединены и служат информационным входом блока сравнения, информационные выходы первого и второго оперативных запоминающих устройств подключены соответственно к первому и второму входам блока вычитания, выход которого соединен со входом блока усреднения, объединенные входы управления записью оперативных запоминающих устройств служат первым управляющим входом блока сравнения, вторым и третьим управляющими входами которого являются входы выбора кристалла соответственно первого и второго оперативного запоминающего устройства.

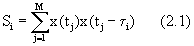

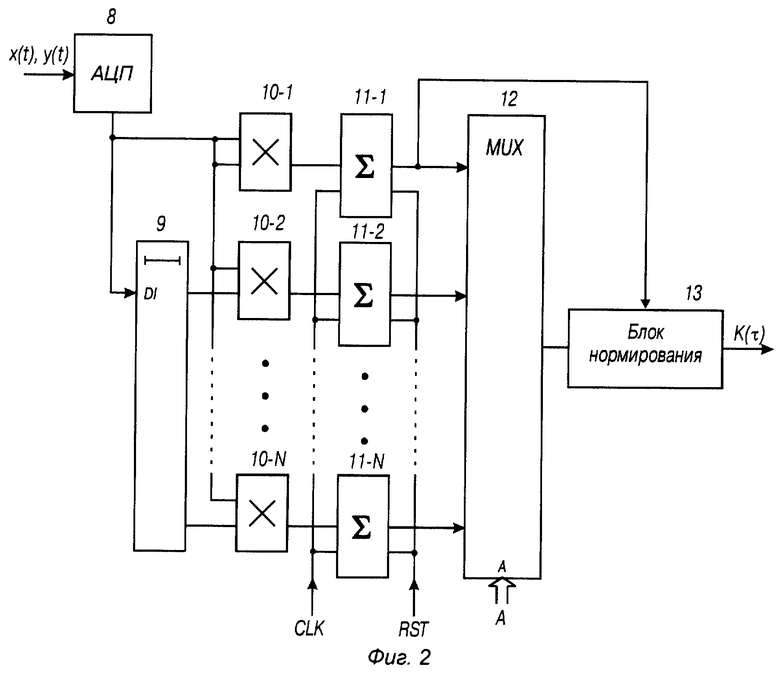

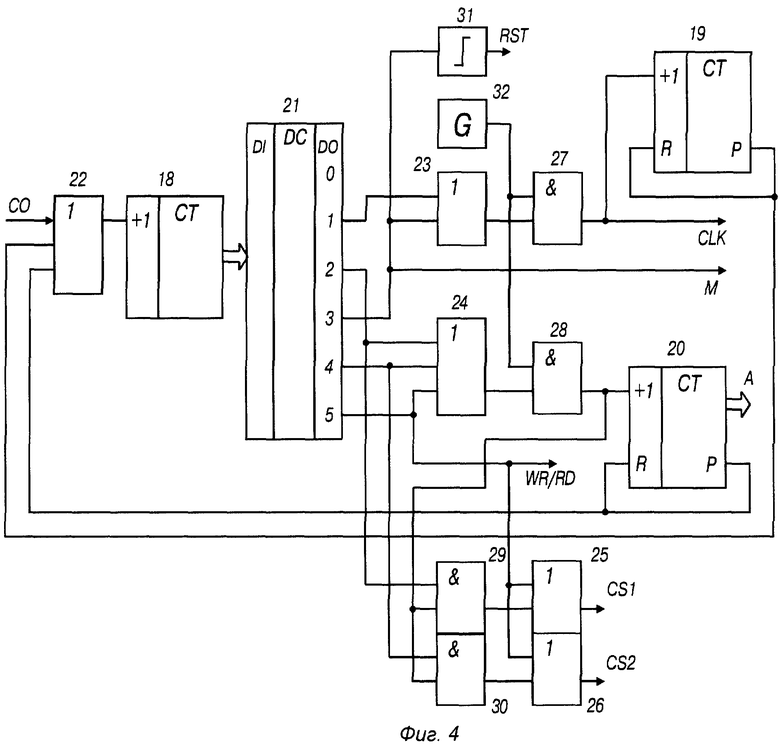

Сущность изобретения поясняется графическим материалом. На фиг.1 показана функциональная схема измерителя уровня шумовой интермодуляции с подключенным тестируемым усилителем. На фиг.2 приведена функциональная схема одного из вариантов реализации коррелятора. На фиг.3 приведена функциональная схема одного из вариантов реализации блока сравнения. На фиг.4 приведена функциональная схема одного из вариантов реализации блока управления.

Функциональная схема измерителя по фиг.1 содержит генератор 1 случайного сигнала, полосовой фильтр 2 (ПФ), аналоговый мультиплексор 3, коррелятор 4, блок 5 сравнения, блок 6 управления и тестируемый усилитель 7 с подключенной нагрузкой RL. Выход генератора 1 соединен со входом ПФ2, к входу которого подключен вход тестируемого усилителя 7, выход которого соединен с первым информационным входом мультиплексора 3, второй информационный вход которого соединен с выходом ПФ2, выход мультиплексора 3 соединен с информационным входом коррелятора 4, выход которого соединен с информационным входом блока 5 сравнения, выход которого является информационным выходом измерителя, адресный вход мультиплексора 3 соединен с выходом М (Mode) блока 6 управления, тактовый и обнуляющий входы коррелятора 4 соединены соответственно с выходами CLK и RST блока 6, первый, второй и третий входы управления блока 5 сравнения соединены соответственно с выходами WR/RD, CS1 и CS2 блока 6, адресный выход А которого соединен с единой адресной шиной коррелятора 4 и блока 5 сравнения, вход блока 6 управления служит входом СО запуска измерителя.

Функциональная схема коррелятора 4 (фиг.2) содержит аналого-цифровой преобразователь (АЦП) 8, линию 9 задержки, группу 10 умножителей, группу 11 накапливающих сумматоров, мультиплексор 12 и блок 13 нормирования, выход которого является выходом К(τ) коррелятора 4, входом которого служит информационный вход АЦП 8, выход которого соединен со входом линии 9 задержки и объединенными первыми входами умножителей 10, выходы которых подключены к информационным входам соответствующих накапливающих сумматоров из группы 11, выходы которых подключены к соответствующим информационным входам мультиплексора 12, выход которого соединен с первым входом блока 13 нормирования, второй вход которого соединен с выходом накапливающего сумматора 11-1, тактовые входы сумматоров 11 объединены и составляют тактовый вход CLK коррелятора 4, обнуляющие входы сумматоров 11 также объединены и составляют обнуляющий вход RST коррелятора 4, второй вход умножителя 10-1 объединен с первым, а вторые входы умножителей 10-2 - 10-N подключены к соответствующим выходам многоотводной линии 9 задержки, адресный вход мультиплексора 12 составляет адресную шину коррелятора 4. Блок 13 нормирования физически может быть выполнен в виде блока деления, при этом первый вход блока 13 является входом делимого, а второй вход - входом делителя.

Блок 5 сравнения (фиг.3) содержит оперативные запоминающие устройства (ОЗУ) 14 и 15, блок 16 вычитания и блок 17 усреднения. Выходы ОЗУ 14 и 15 подключены к соответствующим входам блока 16 вычитания, выход которого соединен со входом блока 17 усреднения, выход которого является выходом блока 5 сравнения, информационным входом DI которого служат объединенные информационные входы ОЗУ 14, 15, объединенные входы управления записью WR/RD которых служат первым управляющим входом блока 5, вторым CS1 и третьим CS2 управляющими входами которого являются входы CS ОЗУ 14 и 15 соответственно, адресные входы ОЗУ 14, 15 объединены и составляют адресную шину блока 5 сравнения.

Блок 6 управления (фиг.4) содержит счетчики 18, 19, 20, дешифратор 21, элементы ИЛИ 22, 23, 24, 25, 26, элементы И 27, 28, 29, 30, одновибратор 31 и генератор 32 тактовых импульсов. Разрядные выходы счетчика 18 соединены с соответствующими разрядными входами дешифратора 21, первый выход которого соединен с первым входом элемента ИЛИ 23, второй выход соединен с объединенными первыми входами элементов ИЛИ 24 и И 29, третий выход соединен со вторым входом элемента ИЛИ 23, четвертый выход соединен со вторым входом элемента ИЛИ 24 и первым входом элемента И 30, пятый выход соединен с объединенными третьим входом элемента ИЛИ 24, первым входом элемента ИЛИ 25, первым входом элемента ИЛИ 26, вторые входы элементов И 29, 30 объединены и подключены к выходу элемента И 28, первый вход которого объединен с первым входом элемента И 27 и подключен к выходу генератора 32 тактовых импульсов, вторые входы элементов И 27, 28 подключены к выходам элементов ИЛИ 23, 24 соответственно, выходы элементов И 27, 28 подключены к счетным входам счетчиков 19, 20 соответственно, выходы переносов счетчиков 19 и 20 подключены к первому и второму входам элемента ИЛИ 22 соответственно, обнуляющий вход счетчика 19 соединен с выходом переноса указанного счетчика, обнуляющий вход счетчика 20 соединен с выходом переноса указанного счетчика, счетный вход счетчика 18 соединен с выходом элемента ИЛИ 22, третий выход которого является входом СО запуска блока 6 управления, обнуляющим выходом RST которого служит выход одновибратора 31, вход которого соединен с третьим выходом дешифратора 21, третий выход дешифратора 21 служит режимным выходом М блока 6 и предназначен для соединения с адресным входом мультиплексора 3, адресным выходом А блока 6 является многоразрядный информационный выход счетчика 20, тактовым выходом CLK блока 6 служит выход элемента И 27, выходом WR/RD управления записью служит пятый выход дешифратора 21, выходами CS1 и CS2 служат выходы элементов ИЛИ 25, 26 соответственно, причем второй вход элемента ИЛИ 25 соединен с выходом элемента И 29, а второй вход элемента ИЛИ 26 соединен с выходом элемента И 30.

В основе функционирования измерителя уровня шумовой интермодуляции (фиг.1) лежит алгоритм, состоящий в сравнении автокорреляционных функций входного и выходного сигналов. Учитывая, что нелинейное преобразование случайных сигналов меняет их статистические свойства, то задача оценки объема продуктов нелинейных искажений может быть сведена к оценке степени изменения автокорреляционной функции случайного сигнала, прошедшего нелинейные цепи. С позиций спектрального подхода это означает, что с расширением спектра выходного сигнала вследствие появления результатов интермодуляции изменяется и отвечающая этому спектру автокорреляционная функция, так как энергетический спектр и автокорреляционная функция жестко связаны преобразованием Фурье.

Используемый в качестве тестового случайный сигнал со сплошным спектром вырабатывается генератором 1; на вход тестируемого усилителя 7 сигнал подается в узком диапазоне частот после полосового фильтра 2 (например, в полосе, составляющей 10-30% от полосы рабочих частот усилителя). Процесс измерений складывается из трех основных этапов. На первом этапе вычисляется нормированная автокорреляционная функция Куу(τ) выходного сигнала тестируемого усилителя, на втором этапе - нормируемая автокорреляционная функция Кхх(τ) входного сигнала с выхода ПФ2. На третьем этапе полученные величины Куу(τ) и Кхх(τ) сравниваются.

По запускающему импульсу на входе СО (фиг.1) - начало I этапа - в корреляторе 4 начинается вычисление функции Kyy(τ), так как на информационный вход коррелятора 4 поступает сигнал y(t) через первый вход мультиплексора 3, а блок 6 управления в ответ на импульс СО выдает пакет тактовых импульсов, тактирующих коррелятор, количество которых определяет длительность интервала наблюдения Т. По истечении времени Т блок 6 прекращает подачу тактовых импульсов и переходит к управлению передачей в блок 5 сравнения результатов вычисления Куу(τ). Для этого блок 6 управления начинает перебор адресов на единой адресной шине А, обращаясь последовательно к ячейкам памяти коррелятора 4, в каждой из которых содержится одна ордината функции Kyy(τ). Одновременно происходит обращение и к ячейкам памяти в блоке 5 сравнения, куда переписываются вычисленные значения Куу(τ). По окончании передачи информации из коррелятора 4 в блок 5 память коррелятора 4 обнуляется и возобновляется его тактирование, что означает начало II этапа. Кроме того на режимном выходе М устанавливается логическая единица, приводящая к коммутации на выход мультиплексора 3 сигнала x(t) с выхода ПФ2. На данном этапе вычисляется функция Кхх(τ). Завершается второй этап, так же как и первый, передачей оценки Кхх(τ) в память блока 5 сравнения, после чего измеритель переходит к этапу сравнения нормированных автокорреляционных функций (III этап).

Сравнение функций Куу(τi) и Кхх(τi) в примере, проиллюстрированном схемой по фиг.3, происходит путем вычисления среднего отклонения

где N - число вычисляемых ординат;

τi - дискретно вводимая линией 9 задержка.

При максимально возможном сходстве процессов x(t) и y(t), когда x(t)=ky(t) (k - постоянный коэффициент), величина М[ΔКху] будет равна 0. С увеличением степени отличия входного и выходного сигналов будет расти и среднее значение разности М[ΔКху] их автокорреляционных функций. Таким образом при функционировании блока 5 сравнения согласно алгоритму (1) количественным показателем уровня шумовой интермодуляции следует считать величину М[ΔКху].

В качестве коррелятора 4 может быть использовано устройство параллельного типа (но не обязательно) (фиг.2), содержащее N каналов обработки (по числу вычисляемых ординат). Принцип действия подобных устройств общеизвестен и состоит в формировании N задержанных на время τi=(i-1)Δτ сигналов (Δτ - дискрет задержки), затем перемножении сигнала x(tj)(у(tj)) на сигнал x(tj-τi)(y(tj-τi)) и вычислении N сумм вида

или

где tj=t0+jΔt(j=1,2,...M);

t0 - начальный момент времени;

Δt - период дискретизации сигналов x(t), y(t) в АЦП 8.

М - количество отсчетов в выборке за время Т.

Для получения ординат нормированной автокорреляционной функции сумму Si следует разделить на аналогичную величину при нулевой задержке (τ1=0), то есть вычислить отношение

для различных значений τi, (для функции Kyy(τi) необходимо выполнить те же операции с заменой x(t) на y(t)). Суммы вида (2), которые используются в (3), формируются на выходах накапливающих сумматоров 11-1 - 11-N. Для коммутации каждого значения Si на вход блока 13 нормирования служит мультиплексор 12, управляемый по единой адресной шине блоком 6. В процессе перебора адресов на выходе блока 13 последовательно появляются значения Kyy(τi) (Kxx(τi)) для всех i. Поскольку в блоке 13 нормирование результатов происходит за счет деления сумм Si без их предварительного усреднения, то блок 13 может быть упрощен до уровня блока деления.

Назначение блока 5 сравнения (фиг.3) - это вычисление выражения (1), для чего необходимо выполнить две основные операции: получить модуль разности для различных τi и усреднить полученные значения. Вычисление модуля разности |Куу(τi)-Кхх(τi)| происходит в блоке 16 вычитания. Блок 17 усреднения может состоять из накапливающего сумматора и устройства деления на постоянную величину N, вход накапливающего сумматора при этом является входом блока усреднения, выходом которого служит выход устройства деления, вход которого соединен с выходом накапливающего сумматора.

При работе блока 5 сравнения, на первом этапе активизируется ОЗУ 14, для этого блок 6 управления подает импульсы CS1 на соответствующий вход ОЗУ 14. На втором этапе блок 6 прекращает подачу импульсов CS1 и начинает подавать импульсы CS2 для выбора ОЗУ 15. В результате значения функции Куу(τi) записываются в ОЗУ 14, а функции Kxx(τi) в ОЗУ 15. На этапе сравнения ОЗУ 14, 15 переводятся в режим чтения, для этого блок 6 управления формирует логические уровни: (WR/RD)=1, CS1=CS2=1; на адресной шине А происходит последовательный перебор адресов ОЗУ и извлекаемые данные потактно поступают в блок 16 вычитания, а далее в блок 17 усреднения.

Для управления работой вышеописанных узлов служит выделенный блок 6 управления (фиг.4), принцип действия которого состоит в следующем.

В исходном состоянии вся последовательная логика блока 6 обнулена. Запускается блок 6 управления коротким импульсом по входу СО, в ответ на что счетчик 18 команд устанавливает на своих разрядных выходах код, соответствующий десятичной единице (на младшем разряде логическая единица, на остальных - нули). При этом на выходе DO1 дешифратора 21 появляется логическая единица (на остальных выходах DO - нули), это приводит к тому, что на выход CLK блока 6 начинают поступать тактовые импульсы, служащие для управления коррелятором 4. Время наблюдения Т, в течение которого на выходе CLK действуют тактовые импульсы, отсчитывается счетчиком 19, коэффициент пересчета которого выбирается таким образом, чтобы на выходе Р переноса появился импульс после отсчета М тактовых импульсов (см. формулу (2)). По импульсу переноса счетчик 19 обнуляется, счетчик 18 инкрементирует свое содержимое, на выходах дешифратора 21 устанавливается распределение DO2=1, DO0=DO1=DО3=DO4=DO5=0 и тактовые импульсы на выход CLK перестают поступать. При DO2=1 запускается адресный счетчик 20, который после перебора заданного объема адресов на шине А (количество адресов должно быть не меньше количества каналов N коррелятора 4), обнуляется и далее импульс с выхода переноса счетчика 20 воздействует на счетный вход счетчика 18 команд, в результате чего на выходах дешифратора 21 устанавливаются логические уровни DO3=1, DO0=DO1=DO2=DO4=DO5=0. С положительным перепадом напряжения на выходе DО3 дешифратора 21 формируется импульс обнуления (выход RST), который вырабатывается одновибратором 31, срабатывающим только по положительным фронтам. Импульс обнуления подается в коррелятор 4, обнуляет там накапливающие сумматоры 11 и это следует считать окончанием первого и началом второго этапа.

На втором этапе измерений блок 6 так же как и ранее выдает на выход CLK пакет тактовых импульсов, после чего (при DO4=1) включается адресный счетчик 20 для обращения к памяти коррелятора 4 и блока 5 сравнения. На данном этапе формируются импульсы CS2 выбора ОЗУ 15, в ячейки которого записываются ординаты функции Kxx(τi). Далее с импульсом переноса на выходе счетчика 20 код на выходе счетчика 18 наращивается на единицу младшего разряда и на выходах дешифратора 21 устанавливаются следующие уровни DO0=DO1=DO2=DO3=DO4=0, DO5=1. При DO5=1 блок 6 управления переходит в режим управления измерителем на третьем этапе. Этот этап характеризуется тем, что (WR/RD)=CS1=CS2=1, а следовательно, ОЗУ 14, 15 переводятся в режим чтения и счетчик 20 последовательно выдает на адресную шину адреса, по которым из ОЗУ 14, 15 извлекаются операнды для получения результата вида (1). С появлением импульса переноса на выходе счетчика 20 он обнуляется, а на выходах DO дешифратора 21 устанавливаются низкие логические уровни: блок 6 управления отработал заданный цикл и готов к следующему, для чего на вход СО следует подать запускающий импульс. Отметим также, что каждый очередной цикл измерений следует начинать с обнуления накапливающих сумматоров, входящих как в состав коррелятора 4, так и в блок 17 усреднения, а также с обнуления счетчика 18.

Сравнение оценок автокорреляционных функций Kyy(τi) и Кхх(τi) можно производить не только вычисляя среднее отклонение (1), но и другими способами, например, путем нахождения отношения Кyy(τi)/Кхх(τi) и др. В каждом из случаев используется соответствующая выбранному алгоритму структура блока 5 сравнения. Неизменным для всех случаев остается лишь то, что для оценки уровня шумовой интермодуляции необходимо выяснить как сильно отличаются автокорреляционные функции сигналов до и после нелинейного преобразования. Причем, как это видно из вышеописанного, при сравнении автокорреляционных функций, в отличие от прототипа, учитывается весь спектр частот, появившихся в результате интермодуляции составляющих входного шумового сигнала, что и позволяет повысить как информативность оценки, так и точность выявления объема вносимых искажений. Заметим, что под шумовым сигналом в данном случае подразумевается случайный сигнал с равномерным сплошным спектром по крайней мере в полосе частот пропускания фильтра 2 (или близкий к нему по спектральным свойствам процесс, например псевдослучайный).

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

| ИЗМЕРИТЕЛЬ УРОВНЯ ШУМОВОЙ ИНТЕРМОДУЛЯЦИИ | 2003 |

|

RU2244938C2 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР | 2002 |

|

RU2227321C2 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| ДВУХКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393492C2 |

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2002 |

|

RU2229156C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| ДИСКРИМИНАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2002 |

|

RU2234729C2 |

Изобретение относится к области радиоизмерений и предназначено для оценки нелинейных искажений вносимых трактами обработки или усиления низкочастотных сигналов, например звуковых. В основе функционирования устройства лежит алгоритм, состоящий в сравнении автокорреляционных функций случайных входного и выходного сигналов. Таким образом задача оценки объема вносимых интермодуляционных искажений сводится к оценке степени изменения автокорреляционной функции сигнала, прошедшего нелинейные цепи. Измеритель при этом содержит генератор случайного сигнала, полосовой фильтр, мультиплексор, коррелятор, блок сравнения и блок управления. Технический результат – повышение точности оценки уровня шумовой интермодуляции, вызванной нелинейной характеристикой тестируемого узла. 4 з.п.ф-лы, 4 ил.

| Устройство для наблюдения и измерения комбинационных и интермодуляционных составляющих сигнала в частотных каналах радиоприемника | 1980 |

|

SU938204A1 |

| Измеритель шумов | 1990 |

|

SU1723535A1 |

| RU 2002102159 A1, 27.07.2003 | |||

| JP 2002040068 А1, 06.02.2002 | |||

| WO 9739597 А1, 23.10.1997. | |||

Авторы

Даты

2005-05-20—Публикация

2003-11-18—Подача