Изобретение относится к специализированным вычислительным средствам и служит для сравнительного анализа случайных процессов, разнесенных во времени.

Известен корреляционный анализатор, построенный по классической схеме параллельного корреляционного анализа и содержащий первый и второй входные блоки, линию задержки, n перемножителей, n усреднителей и дисплей, причем первые входы n перемножителей объединены и подключены к выходу первого входного блока, а вторые входы n перемножителей подключены к соответствующим n отводам линии задержки, включая отвод с нулевой задержкой, вход которой соединен с выходом второго входного блока, входами устройства являются входы входных блоков, выходы n перемножителей подключены к соответствующим входам дисплея через n усреднителей [Мирский Г.Я. Электронные измерения. - М.: Радио и связь, 1986, с.291, рис.8.12].

Принцип действия коррелятора-аналога требует одновременного присутствия на двух его входах исследуемых сигналов. Таким образом, проводить сравнительный анализ сигналов, действующих в различные интервалы времени, при помощи данного устройства не представляется возможным, что и относится к недостатку устройства.

Наиболее близким по технической сущности к предлагаемому анализатору является корреляционный анализатор, содержащий два коррелятора, блок вычитания, блок регулируемой задержки, блок постоянной задержки, усилитель и два управляемых фильтра, причем выходы первого и второго корреляторов соединены с соответствующими входами блока вычитания, выход которого через усилитель соединен с управляющим входом блока регулируемой задержки, выход которого непосредственно и через блок постоянной задержки соответственно соединен с первыми входами первого и второго корреляторов, вторые входы которых соединены с выходом первого управляемого фильтра, выход второго управляемого фильтра соединен с информационным входом блока регулируемой задержки, информационные входы первого и второго управляемых фильтров являются соответственно первым и вторым входами устройства, управляющие входы первого и второго управляемых фильтров объединены и подключены к выходу усилителя [А.с. СССР №1101837. Опубл. в Б.И., 1984 г., №25].

Несмотря на то, что в состав анализатора-прототипа входят два независимых коррелятора, общая структура анализатора не позволяет проводить сравнительный анализ сигналов, действующих не одновременно, так как не предусмотрена возможность запоминания информации о ранее действующем сигнале.

Недостаток корреляционного анализатора-прототипа заключается в отсутствии функциональной возможности совместной обработки сигналов, действующих в различные моменты времени, с целью определения степени их подобия.

Технический результат, достигаемый при использовании настоящего изобретения, состоит в возможности количественного определения степени подобия сигналов, действующих в различные моменты времени.

Технический результат достигается тем, что в известный корреляционный анализатор, содержащий коррелятор и блок вычитания, первый вход которого соединен с выходом коррелятора, согласно изобретению введены блок памяти, блок усреднения и блок управления, причем второй вход блока вычитания соединен с выходом блока памяти, информационный вход которого подключен к выходу коррелятора, адресный вход которого объединен с адресным входом блока памяти и подключен к адресному выходу блока управления, стробирующий выход которого подключен к стробирующему входу коррелятора, информационный вход которого является информационным входом анализатора, выходом которого является выход блока усреднения, информационный вход которого соединен с выходом блока вычитания, а тактовый вход соединен с соответствующим выходом блока управления, обнуляющий вход которого объединен с обнуляющими входами коррелятора и блока усреднения и является обнуляющим входом анализатора, первым и вторым управляющими входами которого служат соответствующие входы блока управления, входы управления блока памяти соединены с соответствующими выходами блока управления.

Сущность изобретения поясняется функциональными схемами и временными диаграммами.

На фиг.1 приведена функциональная схема корреляционного анализатора; на фиг.2 - временные диаграммы, иллюстрирующие работу анализатора; на фиг.3 - функциональная схема блока управления (пример исполнения).

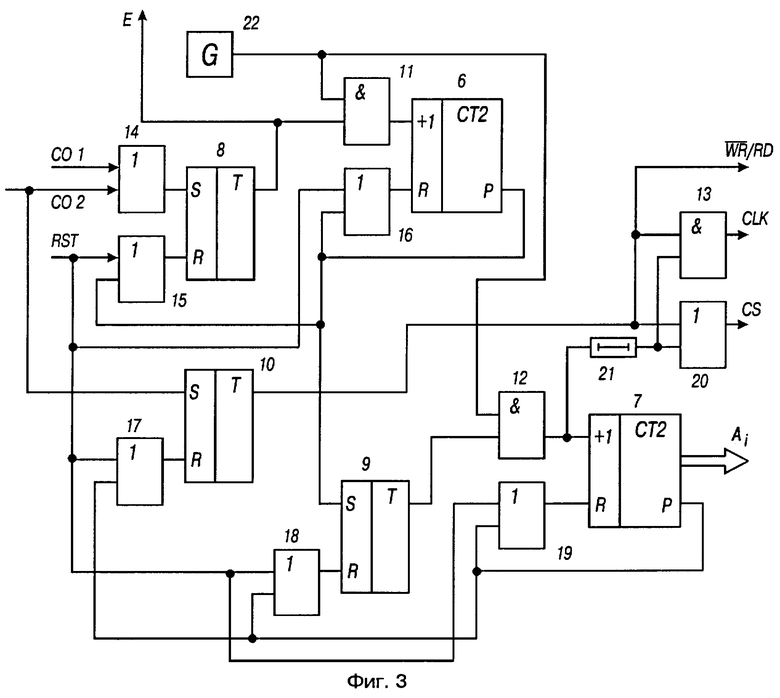

Корреляционный анализатор на фиг.1 содержит коррелятор 1, блок 2 вычитания, блок 3 памяти, представленный в виде ОЗУ, блок 4 усреднения и блок 5 управления. Первый и второй входы блока 2 вычитания соединены соответственно с информационными выходами коррелятора 1 и ОЗУ 3 соответственно, информационный вход ОЗУ 3 подключен к выходу коррелятора 1, адресный вход которого объединен с адресным входом ОЗУ 3 и подключен к адресному выходу блока 5 управления, стробирующий выход которого подключен к стробирующему входу Е коррелятора 1, информационный вход которого является информационным входом X, Y анализатора, выходом которого является выход блока 4 усреднения, информационный вход которого соединен с выходом блока 2 вычитания, а тактовый вход CLK соединен с соответствующим выходом блока 5 управления, обнуляющий вход RST которого соединен обнуляющими входами RST коррелятора 1 и блока 4 усреднения и является обнуляющим входом RST анализатора, первым С01 и вторым С02 управляющими входами которого служат соответствующие входы блока 5 управления, входы управления CS и  ОЗУ 3 соединены с соответствующими выходами блока 5 управления.

ОЗУ 3 соединены с соответствующими выходами блока 5 управления.

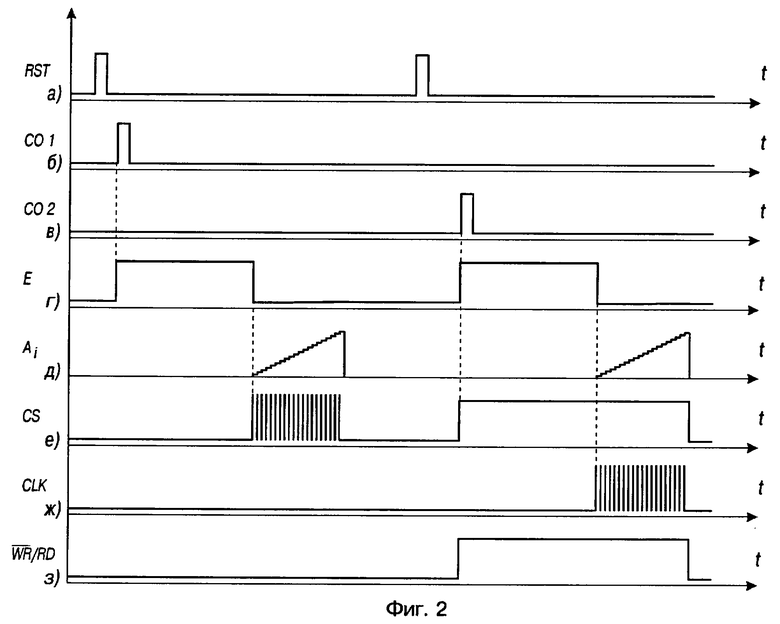

Временные диаграммы (фиг.2) содержат импульсы RST обнуления анализатора (фиг.2а); первый С01 и второй С02 импульсы управления анализатором (соответственно фиг.2б и фиг.2в); стробирующие импульсы Е на входе коррелятора 1 (фиг.2г); текущий адресный код Аi на адресных входах DA коррелятора 1 и ОЗУ 3 (фиг.2д); импульсы CS выбора ОЗУ 3 (фиг.2е); тактовые импульсы CLK на тактовом входе блока 4 усреднения (фиг.2ж); импульс  чтения ОЗУ 3 (фиг.2з).

чтения ОЗУ 3 (фиг.2з).

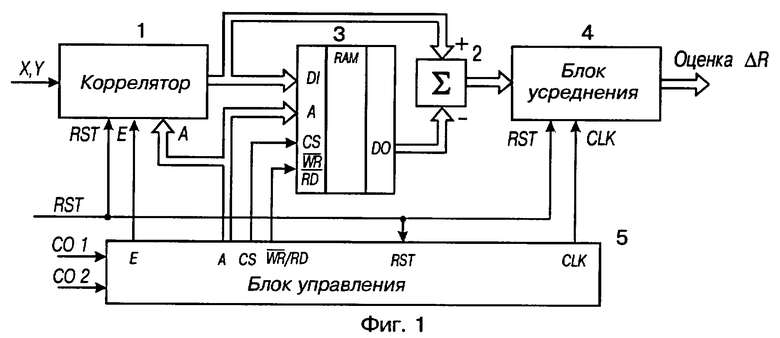

Блок 3 управления (фиг.3) содержит счетчики 6 и 7, триггеры 8, 9 и 10, элементы 2И 11, 12 и 13, элементы 2ИЛИ 14, 15, 16, 17, 18, 19 и 20, элемент 21 задержки и генератор 22 тактовых импульсов. Первый и второй входы элемента 2ИЛИ 14 являются соответственно первым С01 и вторым С02 управляющими входами блока 5, обнуляющим входом RST которого служат объединенные первые входы элементов 2ИЛИ 15, 16, 17, 18 и 19, выходы которых подключены к обнуляющим входам триггера 8, счетчика 6, триггера 10, триггера 9, счетчика 7 соответственно, вторые входы элементов 2ИЛИ 15 и 16 объединены и подключены к выходу переполнения счетчика 6, вторые входы элементов 2ИЛИ 17, 18 и 19 объединены и подключены к выходу переполнения счетчика 7, разрядные выходы которого являются адресным выходом А блока 5 управления, стробирующим выходом Е которого является выход триггера 8, соединенный с первым входом элемента 2И 11, второй вход которого объединен с первым входом элемента 2И 12 и подключен к выходу генератора 22 тактовых импульсов, выходы элементов 2И 11 и 12 подключены к суммирующим входам соответственно счетчиков 6 и 7, выход переполнения счетчика 6 соединен с входом установки в единицу триггера 9, выход которого соединен с вторым входом элемента 2ИЛИ 12, к выходу которого подключен вход элемента 21 задержки, выход которого соединен с объединенными первыми входами элементов 2ИЛИ 20 и 2 И 13, вторые входы которых также объединены и подключены к выходу триггера 10, вход установки в единицу которого объединен с вторым входом элемента 2ИЛИ 14, выход которого соединен с входом установки в единицу триггера 8, выход триггера 10 и выход элемента 2ИЛИ 20 являются соответственно выходами  и CS блока 5 управления, тактовым выходом CLK которого является выход элемента 2И 13. Принцип действия корреляционного анализатора основан на поочередном вычислении автокорреляционных функций RXX(τi) и RYY(τi) соответственно сигналов X(t) и Y(t), стационарных и эргодических, действующих в различные моменты времени, запоминании и затем сравнении полученных значений. Первая из вычисленных функций запоминается в специально выделенном под нее блоке памяти и может храниться достаточно долго (в реальных пределах) до появления второго сигнала. Следовательно, временные ограничения на относительный сдвиг процессов Х(t) и Y(t) в практических задачах могут вообще отсутствовать, а теоретически определяются максимально возможным временем хранения информации без разрушения в конкретно используемых запоминающих структурах. Вторая автокорреляционная функция, в процессе анализа извлекается непосредственно из ячеек памяти (накапливающих сумматоров, например) самого коррелятора.

и CS блока 5 управления, тактовым выходом CLK которого является выход элемента 2И 13. Принцип действия корреляционного анализатора основан на поочередном вычислении автокорреляционных функций RXX(τi) и RYY(τi) соответственно сигналов X(t) и Y(t), стационарных и эргодических, действующих в различные моменты времени, запоминании и затем сравнении полученных значений. Первая из вычисленных функций запоминается в специально выделенном под нее блоке памяти и может храниться достаточно долго (в реальных пределах) до появления второго сигнала. Следовательно, временные ограничения на относительный сдвиг процессов Х(t) и Y(t) в практических задачах могут вообще отсутствовать, а теоретически определяются максимально возможным временем хранения информации без разрушения в конкретно используемых запоминающих структурах. Вторая автокорреляционная функция, в процессе анализа извлекается непосредственно из ячеек памяти (накапливающих сумматоров, например) самого коррелятора.

Началу вычислительных операций в анализаторе (фиг.1) предшествует обнуление всей последовательной логики коррелятора 1, блока 4 усреднения и блока 5 управления, для чего на вход RST подают обнуляющий импульс (фиг.2а). С началом действия на информационном входе X, Y анализатора первого сигнала Х(t) анализатор запускают, для чего на первый управляющий вход С01 подают импульс запуска (фиг.2б). В ответ блок 5 управления выдает строб-импульс (фиг.2в), длительность которого определяет длительность интервала наблюдения, в течение которого коррелятор 1 проводит усреднения, необходимые для вычисления автокорреляционной функции RXX. По окончании интервала наблюдения на общей адресной шине устройства начинается последовательный перебор адресов (фиг.2д), необходимый для записи в ОЗУ 3 вычисленных значений ординат автокорреляционной функции RXX(τi), (i - номер ординаты, i=0,1,...N, τI=iΔτ, Δτ - дискрет задержки). Таким образом, выставляемые по вызову адресного кода на выходной информационной шине коррелятора вычисленные значения RXX(τi) поочередно поступают на информационный вход ОЗУ 3, которые и записываются в память последнего под действием специально формируемых разрешающих импульсов CS (фиг.2е), момент формирования которых несколько сдвигается во времени в сторону запаздывания относительно момента смены адреса. Управление режимом, в котором находится ОЗУ 3, осуществляется по входу  - низкий логический уровень на указанном входе переводит ОЗУ в режим записи (фиг. 2з). После перезаписи данных из коррелятора 1 в ОЗУ 3 анализатор повторно обнуляют (фиг.2а) для очистки содержимого накопительных счетчиков коррелятора 1, после чего устройство переходит в режим ожидания второго сигнала Y(t).

- низкий логический уровень на указанном входе переводит ОЗУ в режим записи (фиг. 2з). После перезаписи данных из коррелятора 1 в ОЗУ 3 анализатор повторно обнуляют (фиг.2а) для очистки содержимого накопительных счетчиков коррелятора 1, после чего устройство переходит в режим ожидания второго сигнала Y(t).

При появлении на входе X, Y сигнала Y(t) на второй управляющий вход С02 подают запускающий импульс, в связи с чем коррелятор 1 начинает процесс вычисления автокорреляционной функции RYY(τi). Одновременно со вторым запуском анализатора блок 5 управления выдает импульс  чтения ОЗУ 3 (фиг.2з), который переводит ОЗУ 3 в режим, допускающий чтение на все оставшееся время данного цикла анализа.

чтения ОЗУ 3 (фиг.2з), который переводит ОЗУ 3 в режим, допускающий чтение на все оставшееся время данного цикла анализа.

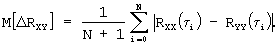

По окончании второго стробирующего импульса Е (фиг.2г), когда коррелятором 1 подготовлены значения ординат автокорреляционной функции RYY(τi), на адресной шине вновь начинается формирование адресного кода Аi. При этом ОЗУ 3 комбинацией импульсов CS и  (фиг.2е, з) переводится в режим чтения и передачи информации на выход, то есть на вход блока 2 вычитания, на другой вход которого синхронно поступает информация непосредственно с выхода коррелятора 1. Таким образом, в каждом i-м такте в соответствии с вызываемым адресом на входах блока 2 вычитания будут присутствовать значения ординат RXX(τi) и RYY(τi): первые - извлекаемые из ячеек ОЗУ 3,а вторые - из коррелятора 1. Формируемая потактно разность |RXX(τi) - RYY(τi)| направляется в блок 4 усреднения, где происходит вычисление среднего отклонения M[ΔRXY]:

(фиг.2е, з) переводится в режим чтения и передачи информации на выход, то есть на вход блока 2 вычитания, на другой вход которого синхронно поступает информация непосредственно с выхода коррелятора 1. Таким образом, в каждом i-м такте в соответствии с вызываемым адресом на входах блока 2 вычитания будут присутствовать значения ординат RXX(τi) и RYY(τi): первые - извлекаемые из ячеек ОЗУ 3,а вторые - из коррелятора 1. Формируемая потактно разность |RXX(τi) - RYY(τi)| направляется в блок 4 усреднения, где происходит вычисление среднего отклонения M[ΔRXY]:

Из последнего выражения несложно видеть, что степень сходства процессов X(t) и Y(t) в заявленном устройстве определяют путем определения, насколько мало среднее значение М[ΔRXY] разности их автокорреляционных функций. Разумеется, в идеальном случае абсолютному равенству вычисленных значений RXX(τi) и RYY(τi) будет соответствовать равенство нулю и их среднего отклонения: М[ΔRXY]=0.

Относительно реализованного в анализаторе метода отметим, что поскольку автокорреляционные функции сигналов тесно связаны с их энергетическими спектрами при помощи преобразований Фурье, то по степени их равенства можно судить и о степени сходства энергетических спектров, то есть по полученному значению М[ΔRXY]. Добавим также, что при τi=0 автокорреляционная функция процесса численно равна дисперсии: RXX(0)=σ2. Дисперсия же σ2, в свою очередь, равна средней мощности процесса, в данном случае процесса Х(t). Следовательно, структура анализатора 1 по фиг.1 позволяет вычислять и разность средних мощностей процессов Х(t) и Y(t). Для этого достаточно зафиксировать на выходе блока 2 вычитания значение разности |RXX(τi) и RYY(τi)| при τI=0.

Рассмотрим далее некоторые особенности конкретного исполнения отдельных блоков заявленного анализатора (фиг.1).

Структура анализатора разработана в том предположении, что коррелятор 1 - многоканальное устройство параллельного вычисления корреляционной функции R(τi), где i - число каналов определяется заданным числом вычисляемых ординат, а полученные значения ординат могут храниться в накапливающих сумматорах-усреднителях или в счетчиках-накопителях. Подача на выход коррелятора выбранного значения R(τi) осуществляется путем мультиплексирования данных, содержащихся в сумматорах устройства. Управление передачей указанных данных на выход осуществляют по адресной шине А коррелятора 1 путем установки кода, значение которого соответствует адресу вызываемой ординаты R(τi). Из вышеизложенного следует обязательное требование к структурной схеме коррелятора 1: в устройстве должен содержаться (N+1)-канальный мультиплексор, канальные входы которого соединены с информационными выходами канальных накапливающих сумматоров-усреднителей, а адресный вход мультиплексора представляет собой адресный вход коррелятора.

Блок 4 усреднения в заявляемом корреляционном анализаторе может быть выполнен в виде последовательно включенных накапливающего сумматора и устройства деления на постоянный коэффициент N+1. В качестве последнего устройства может быть применено ППЗУ с заранее записанными значениями возможных результатов деления, то есть реализуется аппаратно-табличный способ выполнения арифметических операций. По входу CLK предусматривается тактирование внутренних регистров накапливающего сумматора.

Пример конкретной реализации блока 5 управления показан на фиг.3.

Блок 5 управления работает следующим образом.

После обнуления всех триггеров и счетчиков блока 5 на вход С01 подают первый запускающий импульс (фиг.2б) - признак наличия первого сигнала Х(t). По фронту указанного импульса триггер 8 переходит в состояние высокого логического уровня на выходе, передавая соответствующий уровень (фиг.2г) на стробирующий выход Е блока 5 и, кроме того, дает команду на счет счетчику 6. Последний отсчитывает время, отводимое коррелятору 1 на наблюдение и накопление данных: дальняя по времени граница интервала наблюдения определяется моментом появления импульса переполнения на выходе Р указанного счетчика. В связи с чем триггер 8 переходит в исходное состояние, счет останавливается, а триггер 9 переводится в состояние высокого логического уровня, на суммирующий вход счетчика 7 разрешается прохождение тактовых импульсов и начинается процесс формирования текущего адреса Аi (фиг.2д), используемого на данном этапе для поадресной записи информации в ОЗУ 3. С некоторой задержкой во времени смена адресного кода сопровождается появлениями импульсов CS, разрешающих работу ОЗУ 3. Указанные импульсы проходят через элемент 21 задержки на выход элемента 2ИЛИ 20. Время задержки выбирают исходя из требований по временному распределению сигналов конкретной микросхемы ОЗУ. После формирования кода последнего адреса счетчик 7 обнуляется, триггер 9 переходит в исходное состояние и блок 5 управления завершает цикл формирования управляющих воздействий.

Следующий цикл начинается с поступлением второго запускающего импульса на вход С01 (фиг.2в). При этом алгоритм работы блока 5 управления сохраняется прежним, как и было описано выше, за тем исключением, что триггер 10 переходит в единичное состояние и, как следствие, устанавливается высокий логический уровень на выходах  и CS блока 5 - ОЗУ 3 переводится в режим чтения, а также после окончания действия строб-импульса на выход CLK блока 5 подаются тактовые импульсы для управления блоком 4 усреднения.

и CS блока 5 - ОЗУ 3 переводится в режим чтения, а также после окончания действия строб-импульса на выход CLK блока 5 подаются тактовые импульсы для управления блоком 4 усреднения.

Из описания принципа действия анализатора и особенностей его схемотехнического исполнения видно, что для взаимной обработки сигналов, сдвинутых на достаточно большие промежутки времени и не перекрывающихся между собой, не обязательно применять сложные компенсирующие линии задержки. Теоретически линия задержки способна устранить любые временные рассогласования и, таким образом, позволяет использовать корреляторы классического типа. Однако при этом существенно увеличивается как стоимость всего устройства в целом, так и его аппаратурный объем. Аппаратурный объем же заявленного анализатора инвариантен по отношению к временным сдвигам исследуемых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

| КОРРЕЛЯЦИОННОЕ УСТРОЙСТВО | 2002 |

|

RU2229156C2 |

| ИЗМЕРИТЕЛЬ УРОВНЯ ШУМОВОЙ ИНТЕРМОДУЛЯЦИИ | 2003 |

|

RU2252425C2 |

| ДИСКРИМИНАТОР СЛУЧАЙНЫХ СИГНАЛОВ | 2002 |

|

RU2234729C2 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| ИЗМЕРИТЕЛЬ УРОВНЯ ШУМОВОЙ ИНТЕРМОДУЛЯЦИИ | 2003 |

|

RU2244938C2 |

| ДВУХКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393492C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

Изобретение относится к области вычислительной техники и может быть использовано для анализа случайных процессов. Техническим результатом является расширение функциональных возможностей. Анализатор содержит коррелятор, блок вычитания, блок памяти, блок усреднения и блок управления. 3 ил.

Корреляционный анализатор, содержащий коррелятор и блок вычитания, первый вход которого соединен с выходом коррелятора, отличающийся тем, что в него введены блок памяти, блок усреднения и блок управления, причем второй вход блока вычитания соединен с выходом блока памяти, информационный вход которого подключен к выходу коррелятора, адресный вход которого объединен с адресным входом блока памяти и подключен к адресному выходу блока управления, стробирующий выход которого подключен к стробирующему входу коррелятора, информационный вход которого является информационным входом анализатора, выходом которого является выход блока усреднения, информационный вход которого соединен с выходом блока вычитания, а тактовый вход соединен с соответствующим выходом блока управления, обнуляющий вход которого объединен с обнуляющими входами коррелятора и блока усреднения и является обнуляющим входом анализатора, первым и вторым управляющими входами которого служат соответствующие входы блока управления, входы управления блока памяти соединены с соответствующими выходами блока управления.

| Корреляционное устройство для определения времени задержки | 1983 |

|

SU1101837A1 |

| Электронные измерения | |||

| - М: Радио и связь, 1986, с.291.RU 2037198 C1, 09.06.1995.RU 94036198 A1, 20.07.1996.WO 99/24916 A1, 20.05.1999.US 5931893 А, 03.08.1999. | |||

Авторы

Даты

2004-04-20—Публикация

2002-07-17—Подача