Настоящее изобретение относится, в целом, к системе связи, в которой используется многоуровневая модуляция/демодуляция, и, в частности, к способу и устройству для переупорядочения битового потока последовательности кодового слова перед модуляцией и упорядочения выхода демодулятора в виде исходной последовательности кодового слова.

В системе IMT-2000 (International Mobile Telecommunication-2000) или в системе UMTS (Universal Mobile Telecommunication System), в обычной системе мобильной связи МДКР (множественного доступа с кодовым разделением), для повышения эффективности использования спектра, применяется многоуровневая модуляция-демодуляция. Под “многоуровневой модуляцией” будем понимать схемы модуляции 8ФМн (8-кратная фазовая манипуляция), 16КАМ (16-кратная квадратурная амплитудная модуляция) и 64КАМ, т.е. 2m-кратную модуляцию более высокого уровня, чем схема модуляции КФМн (квадратурная фазовая манипуляция). При генерации модулированных битов с использованием многоуровневой модуляции, биты, образующие каждый модулированный бит, различаются по надежности. Различие в надежности приводит к различию в средней частоте битовых ошибок для соответствующих битов.

При этом, когда в качестве канального кодера используется кодер, образованный совокупностью системных кодеров, например, турбо-кодер, биты кодового слова, выдаваемые системными кодерами, попадают либо в систематическую часть, поток битов с более высоким приоритетом (важностью), либо в четностную часть, поток битов с более низким приоритетом. В случае, когда одна информационная последовательность поступает на совокупность образующих кодеров, снижение частоты битовых ошибок для битов, принадлежащих систематической части битов кодового слова, может приводить к снижению средней частоты битовых ошибок и средней частоты пакетных ошибок информационной последовательности, выдаваемой канальным декодером. Таким образом, когда биты кодового слова, принадлежащие систематической части с более высоким приоритетом, имеют безусловно более высокую надежность, чем биты кодового слова, принадлежащие четностной части с более низким приоритетом, можно ожидать улучшения характеристики частоты генерации ошибок в информационной последовательности, генерируемой после декодирования.

Итак, задачей настоящего изобретения является способ и устройство для перестановки битов последовательности кодового слова, выдаваемой канальным кодером, осуществляемой до модуляции в системе связи, где применяется многоуровневая модуляция, позволяющей размещать биты, принадлежащие систематической части с более высоким приоритетом, в битовых позициях модулированного бита, имеющих более высокую надежность.

Другой задачей настоящего изобретения является способ и устройство для перестановки битов последовательности кодового слова, выдаваемой канальным кодером, осуществляемой до модуляции в системе связи, где применяется многоуровневая модуляция, позволяющей размещать биты, принадлежащие систематической части с более высоким приоритетом, в битовых позициях модулированного бита, имеющих более высокую надежность, и размещать демодулированные биты в порядке исходной последовательности кодового слова.

Еще одной задачей настоящего изобретения является способ и устройство для снижения средней частоты битовой ошибки и средней частоты пакетной ошибки информационной последовательности, генерируемой после декодирования, в системе связи.

Для решения вышеозначенных и других задач предусмотрены способ и устройство для отображения потока битов, выдаваемого кодером, в поток битов для 2m-кратной модуляции. Способ и устройство предусматривают деление потока битов, выдаваемого кодером, на первый период и второй период. Первый период содержит биты с более высоким приоритетом в потоке битов, выдаваемом кодером, а второй период содержит биты с более низким приоритетом. Способ и устройство предусматривают отображение битов, принадлежащих первому периоду, в битовые позиции с более высокой надежностью в потоке из m битов, представляющем каждый из битов для 2m-кратной модуляции, и отображение битов, принадлежащих второму периоду, в битовые позиции с более низкой надежностью в потоке из m битов.

Вышеозначенные и другие задачи, признаки и преимущества настоящего изобретения явствуют из нижеследующего подробного описания, приведенного в сочетании с прилагаемыми чертежами, на которых:

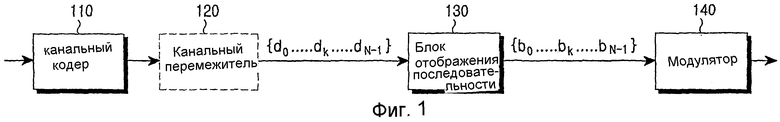

фиг.1 - схема передающего устройства, содержащего блок отображения последовательности для переупорядочения последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

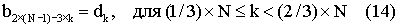

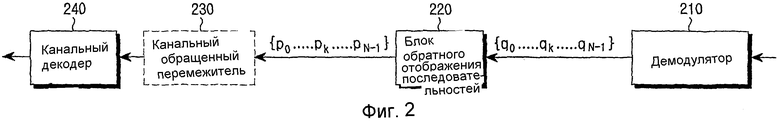

фиг.2 - схема приемного устройства, содержащего блок обратного отображения последовательности, согласно варианту осуществления настоящего изобретения;

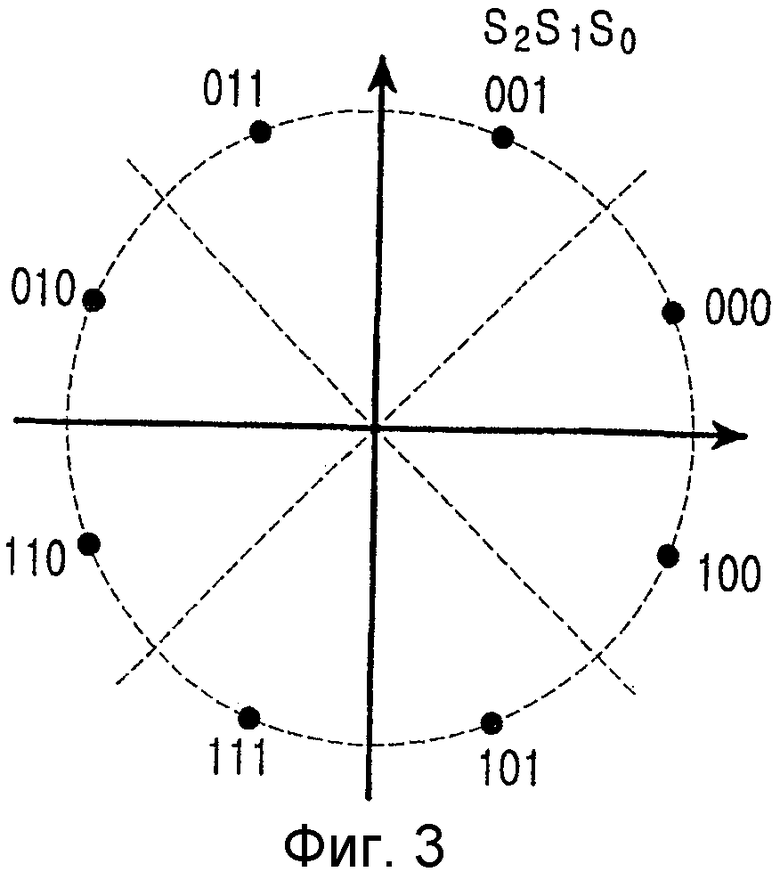

фиг.3 - диаграмма группировки сигналов для схемы модуляции 8ФМн (8-кратная фазовая манипуляция);

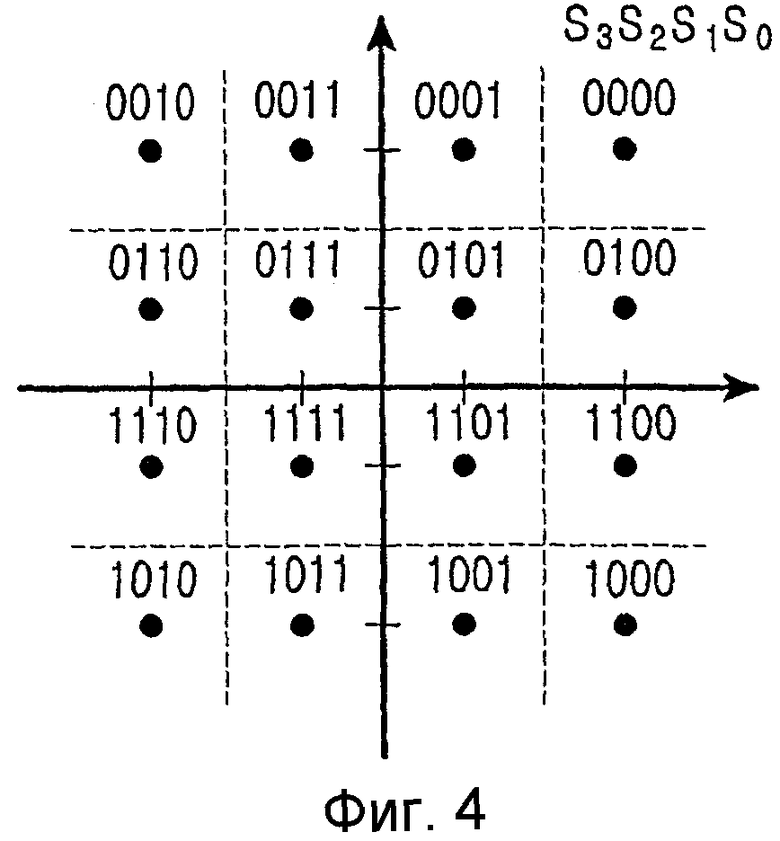

фиг.4 - диаграмма группировки сигналов для схемы модуляции 16КАМ (16-кратная квадратурная амплитудная модуляция);

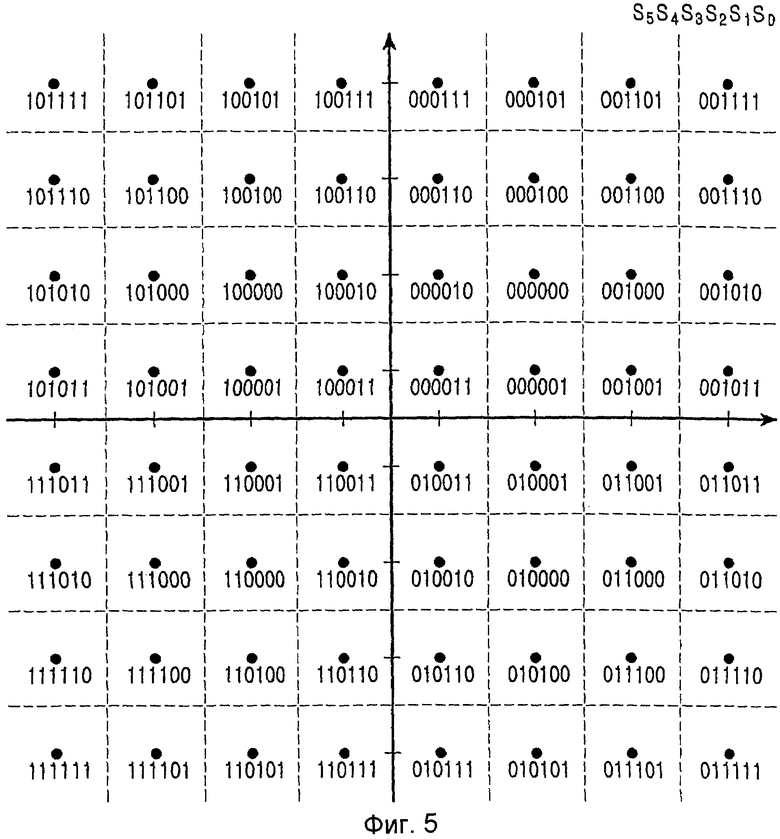

фиг.5 - диаграмма группировки сигналов для схемы модуляции 64 КАМ (64-кратная квадратурная амплитудная модуляция);

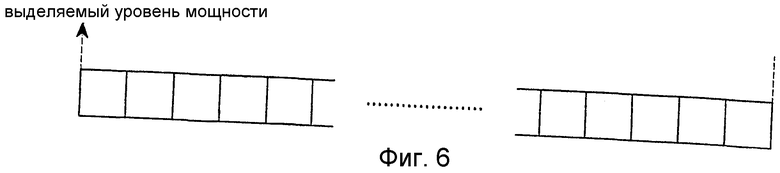

фиг.6 - схема однородного распределения мощности в последовательности кодового слова;

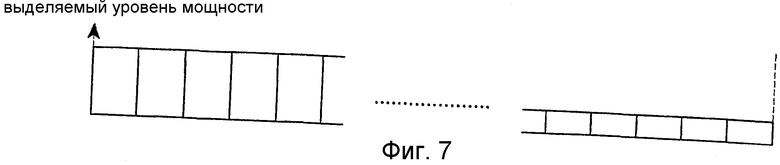

фиг.7 - схема распределения мощности в последовательности кодового слова, когда более высокий уровень мощности соответствует ее головной части;

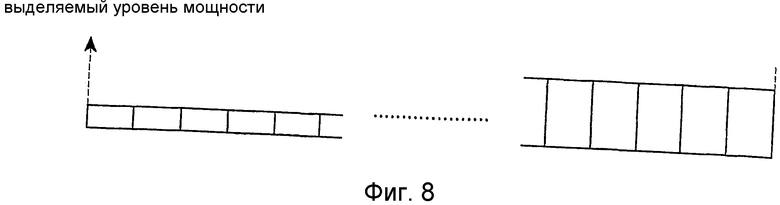

фиг.8 - схема распределения мощности в последовательности кодового слова, когда более высокий уровень мощности соответствует ее хвостовой части;

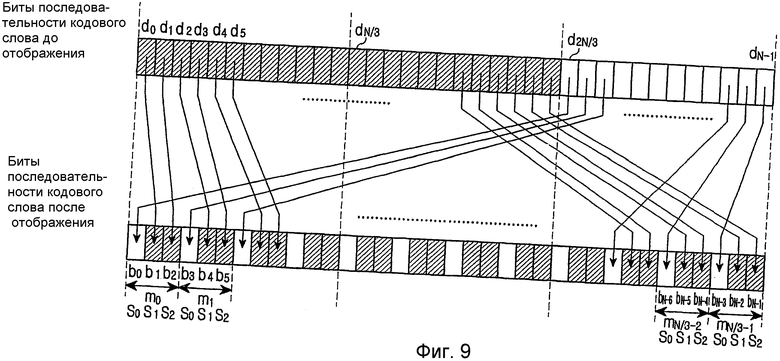

фиг.9 - операция перестановки битов, соответствующая схеме модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

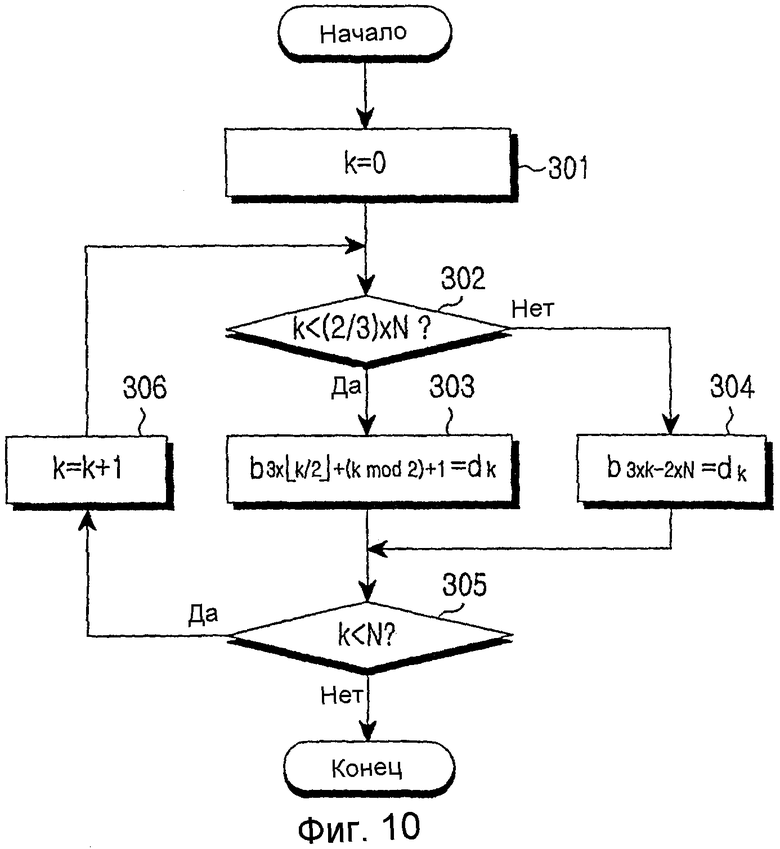

фиг.10 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

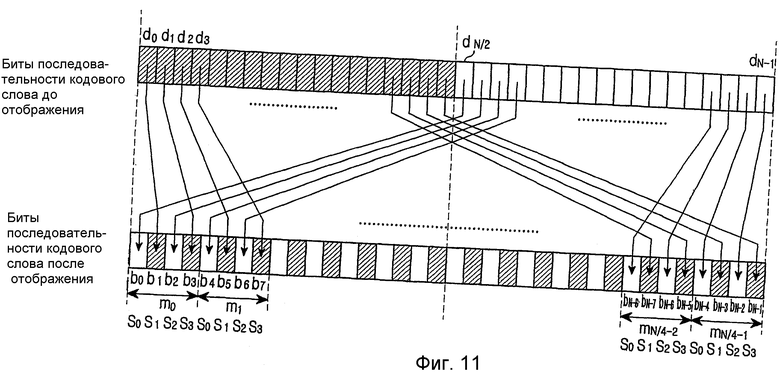

фиг.11 - операция перестановки битов, соответствующая схеме модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

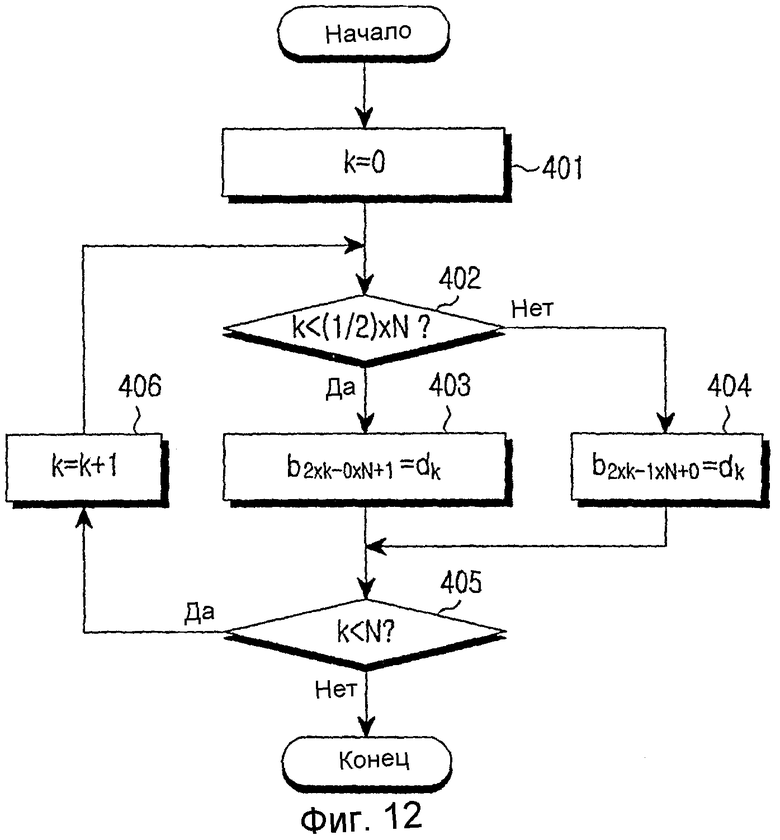

фиг.12 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

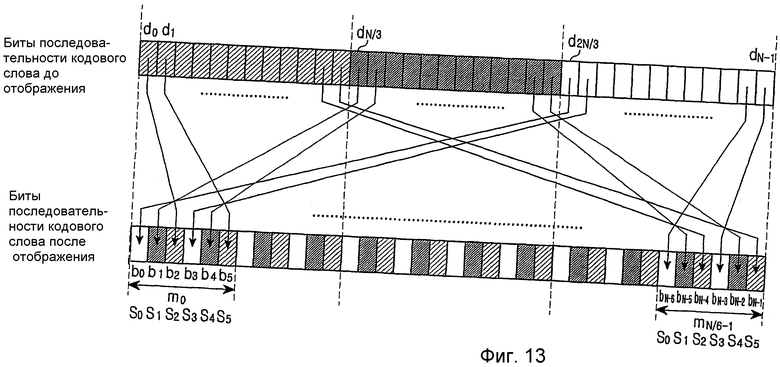

фиг.13 - операция перестановки битов, соответствующая схеме модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

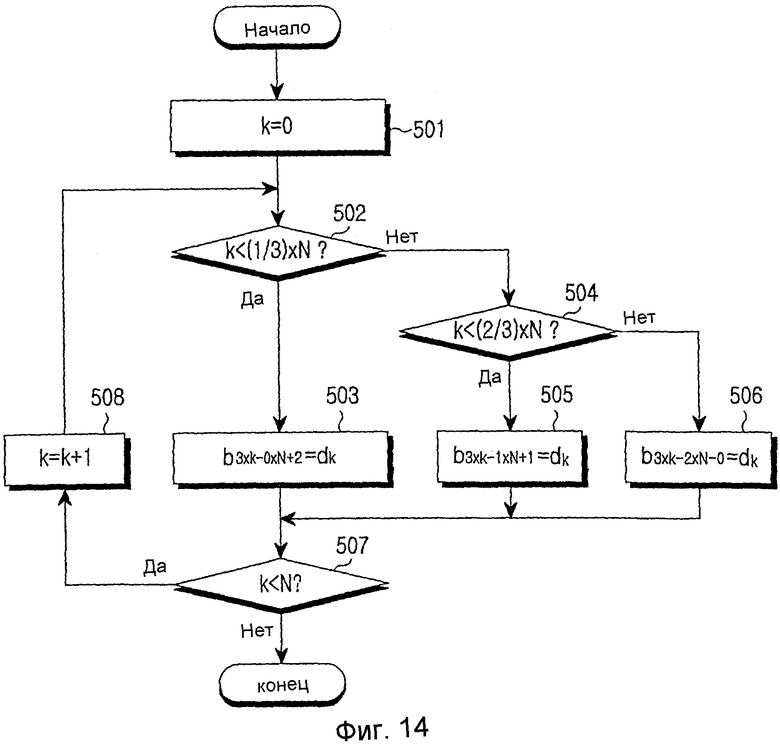

фиг.14 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

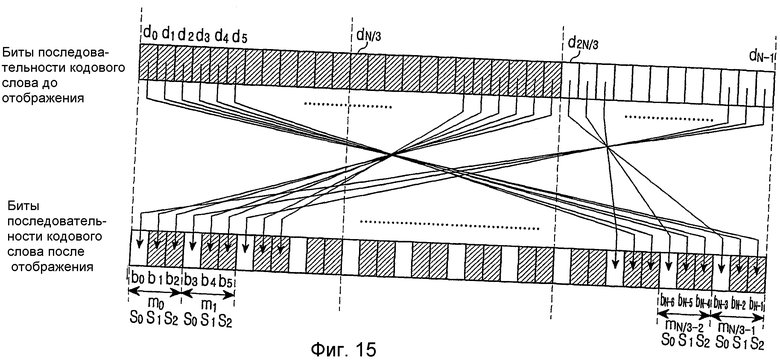

фиг.15 - операция перестановки битов, соответствующая схеме модуляции 8ФМн, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

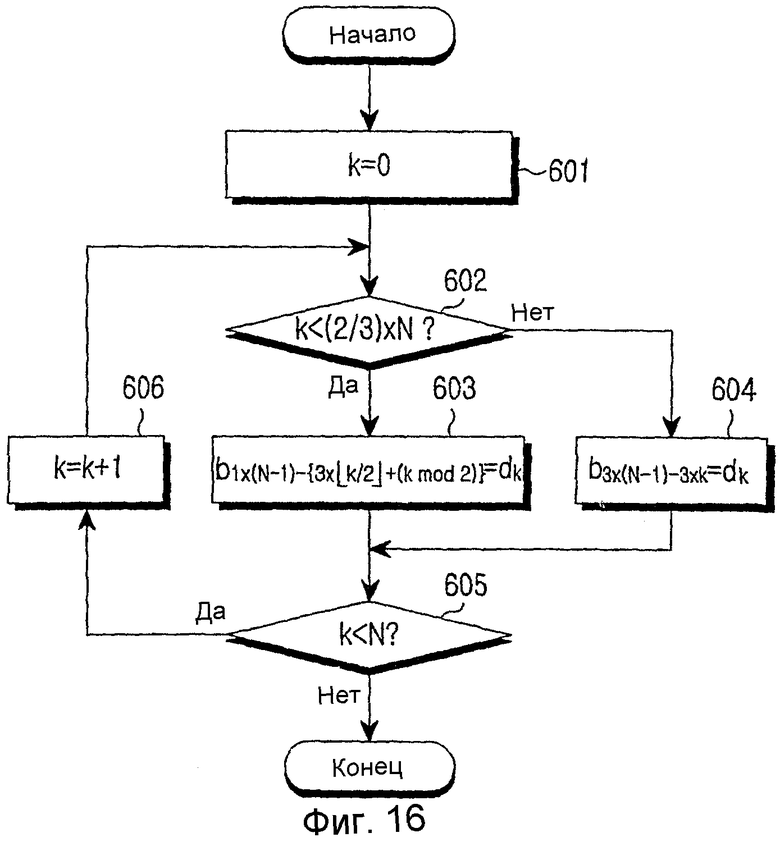

фиг.16 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

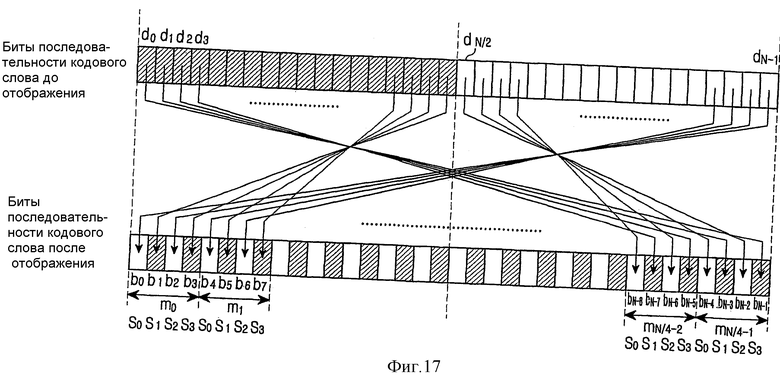

фиг.17 - операция перестановки битов, соответствующая схеме модуляции 16КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

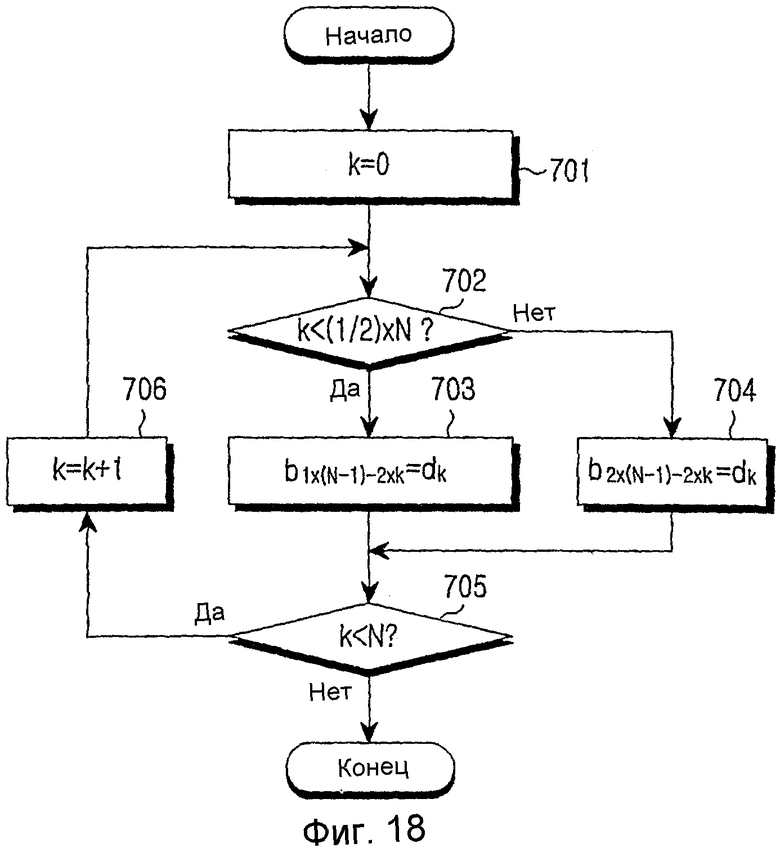

фиг.18 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

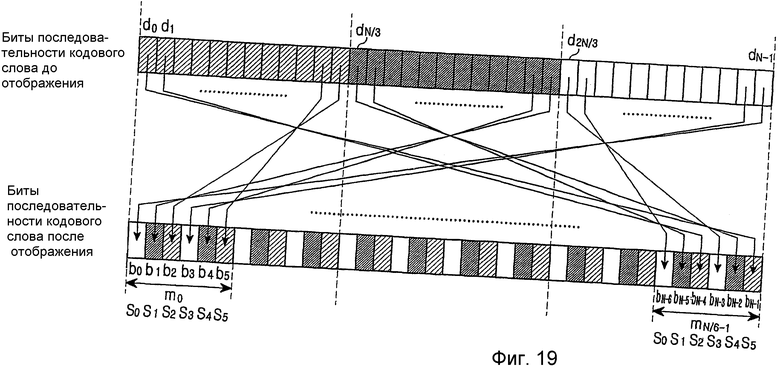

фиг.19 - операция перестановки битов, соответствующая схеме модуляции 64КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

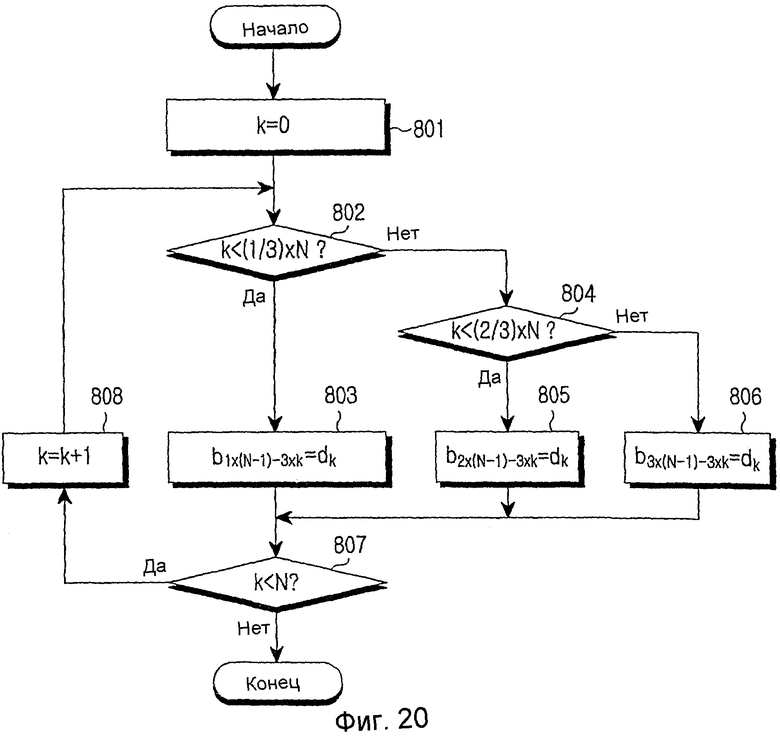

фиг.20 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

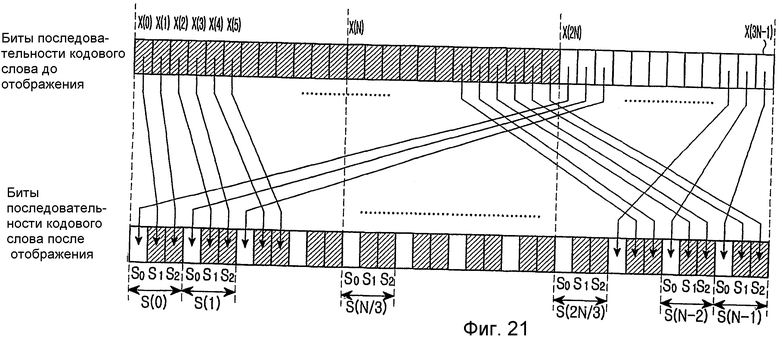

фиг.21 - операция перестановки битов, соответствующая схеме модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

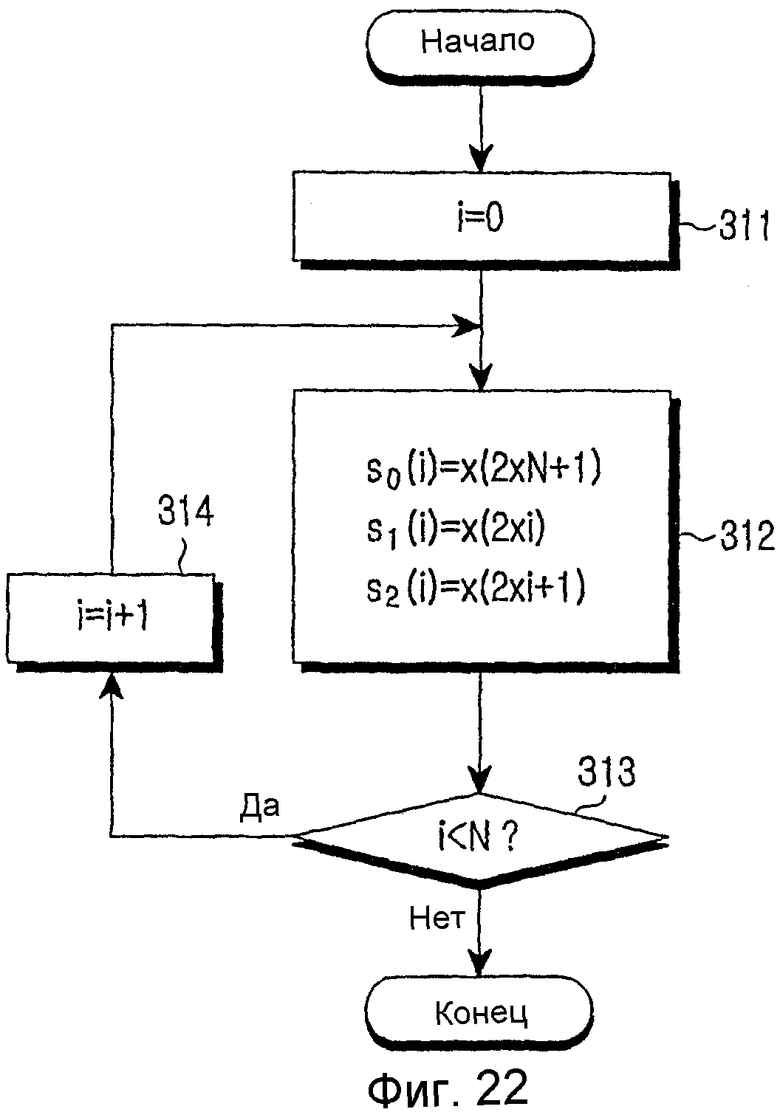

фиг.22 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

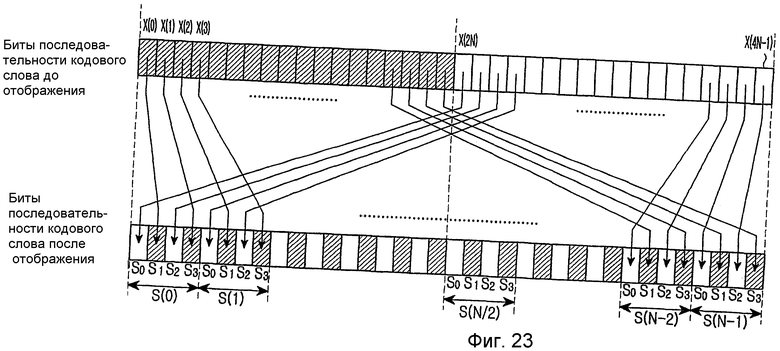

фиг.23 - операция перестановки битов, соответствующая схеме модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

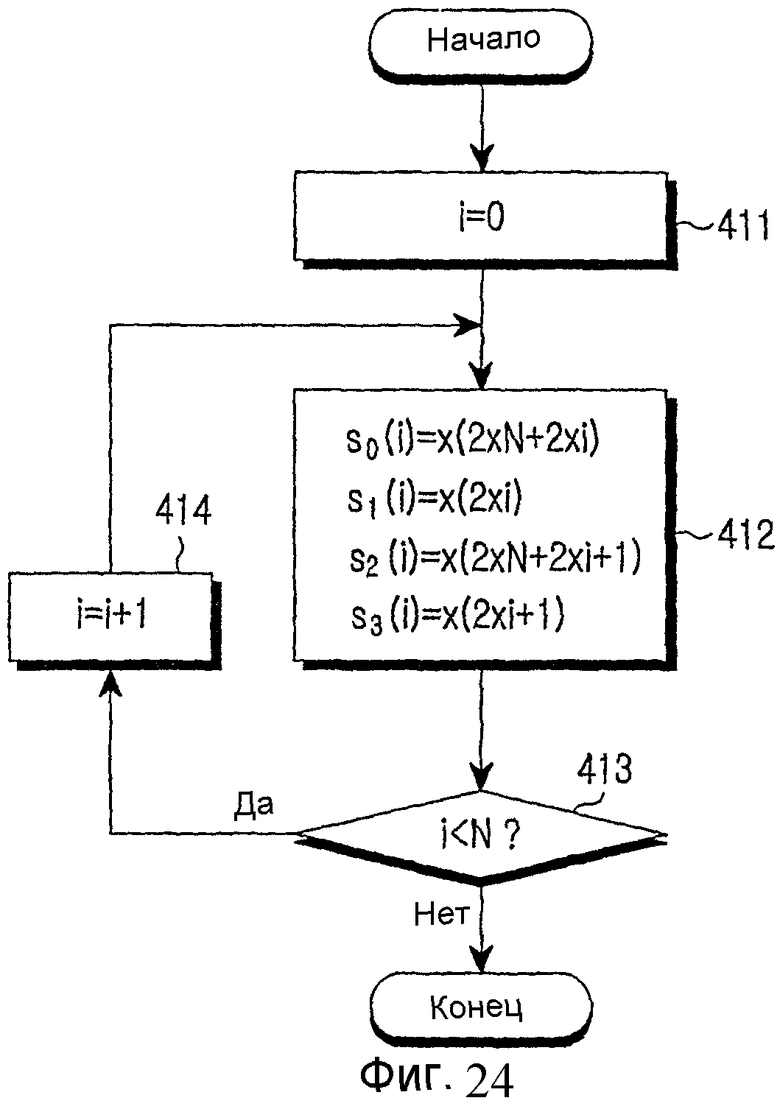

фиг.24 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

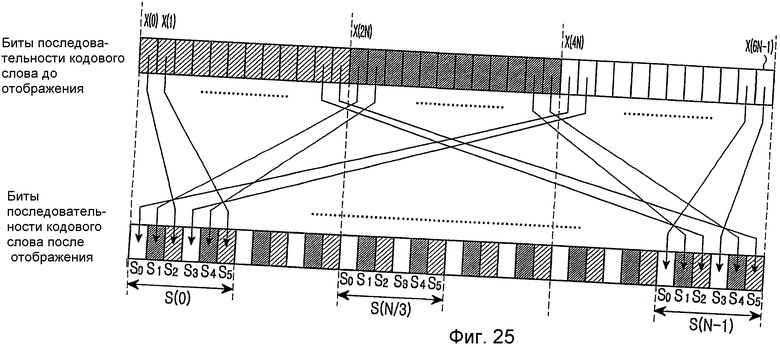

фиг.25 - операция перестановки битов, соответствующая схеме модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

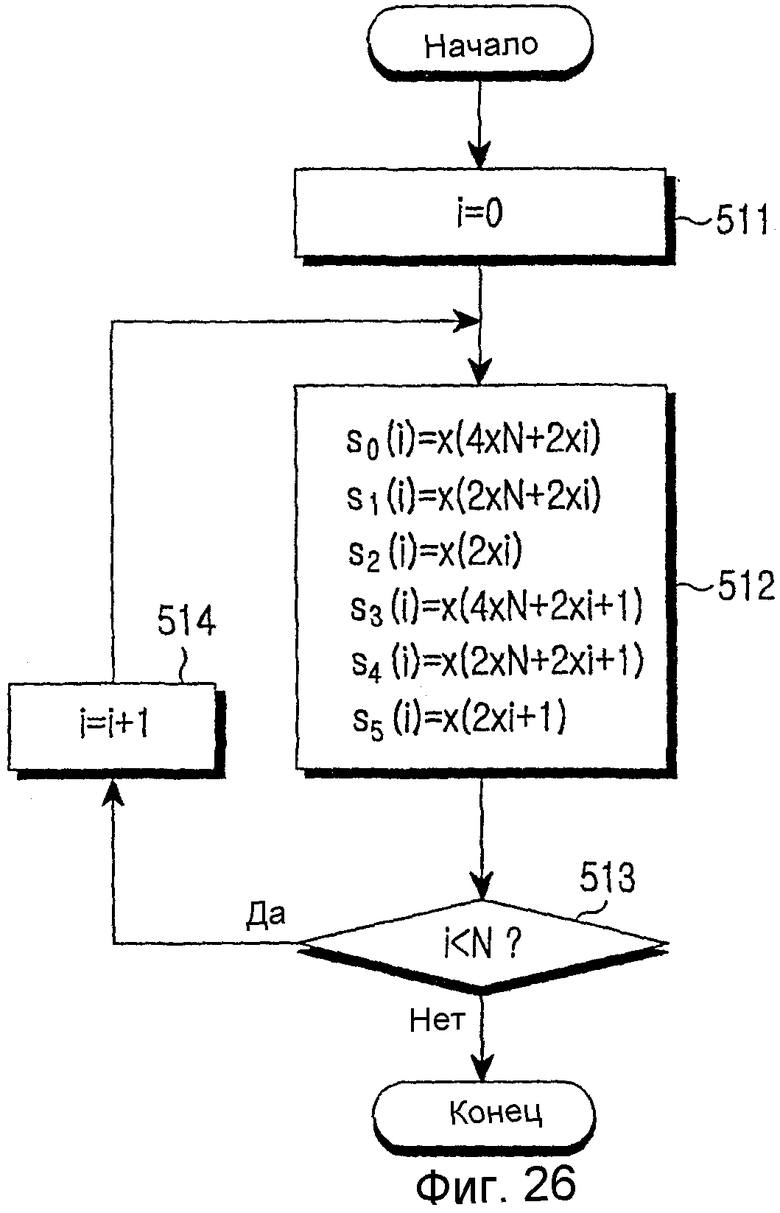

фиг.26 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

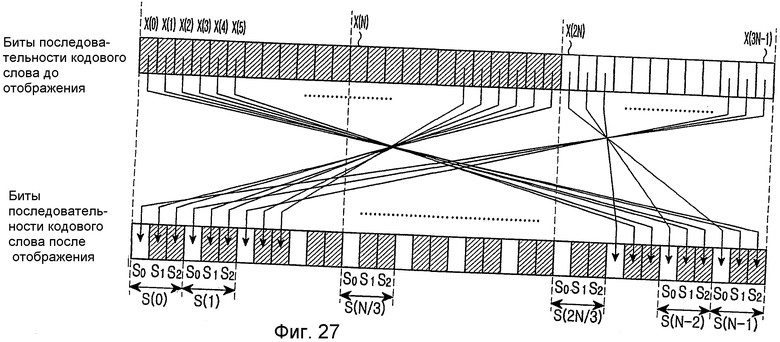

фиг.27 - операция перестановки битов, соответствующая схеме модуляции 8ФМн, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

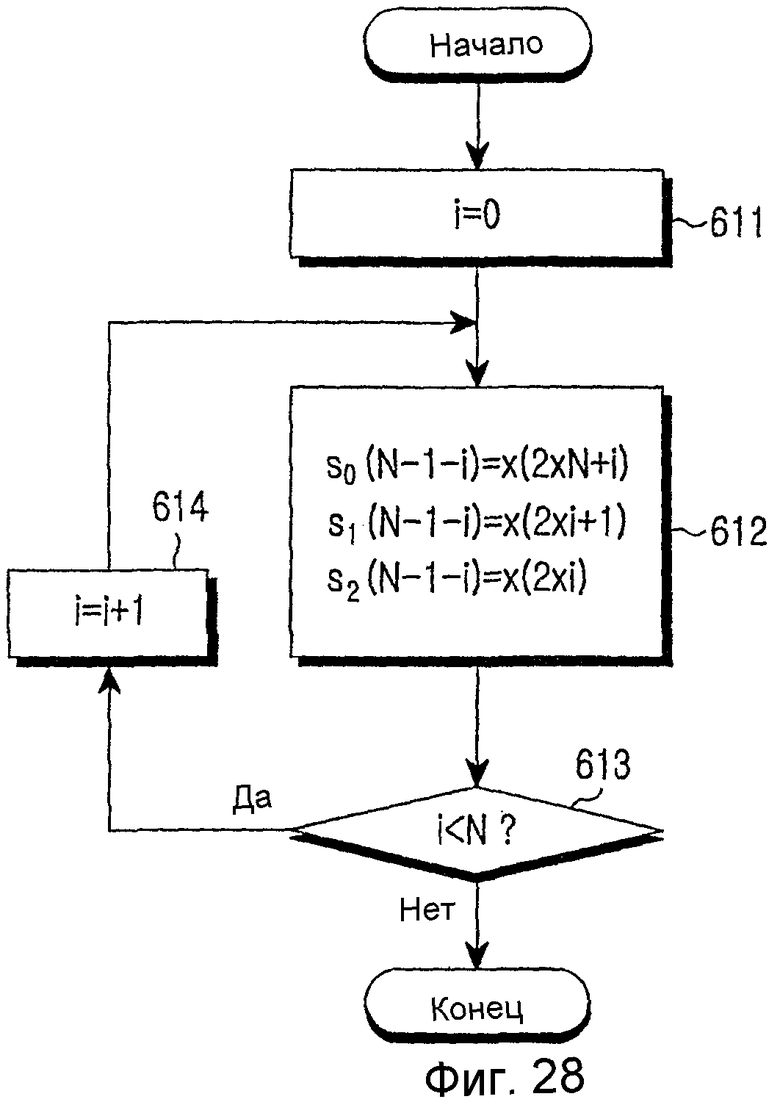

фиг.28 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

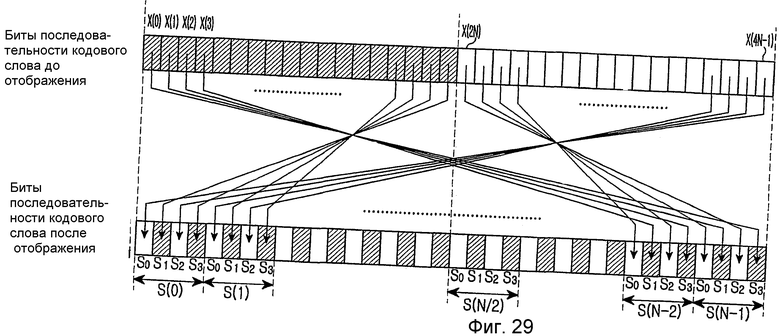

фиг.29 - операция перестановки битов, соответствующая схеме модуляции 16КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

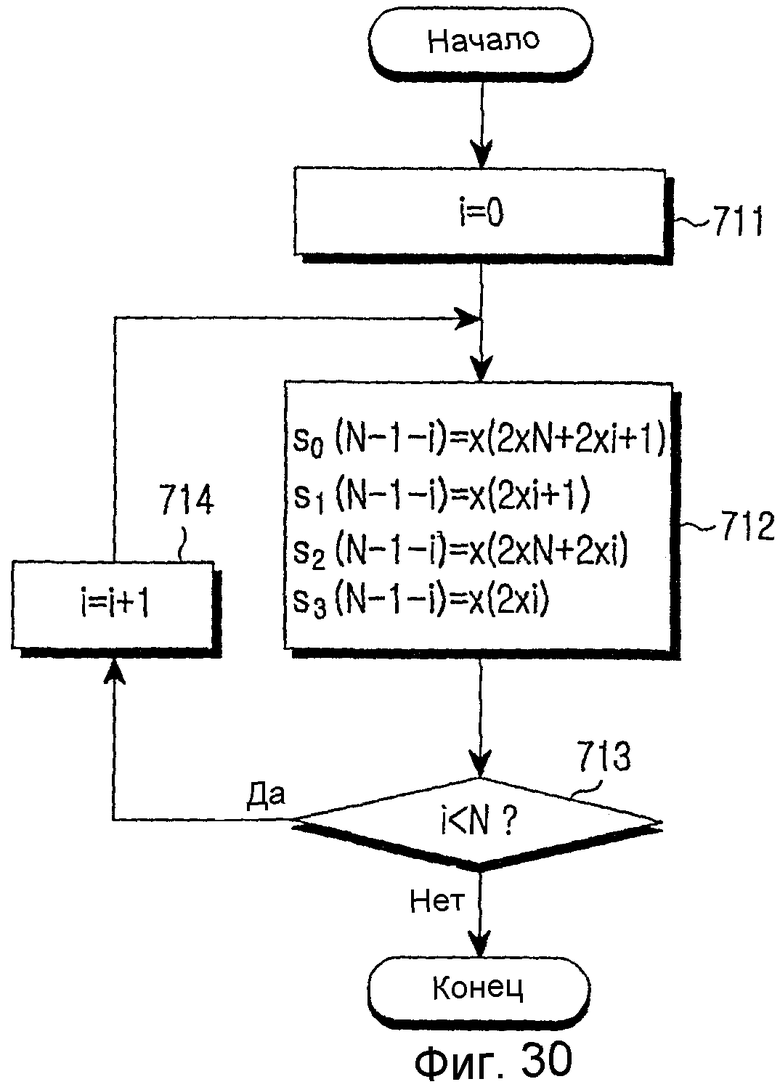

фиг.30 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

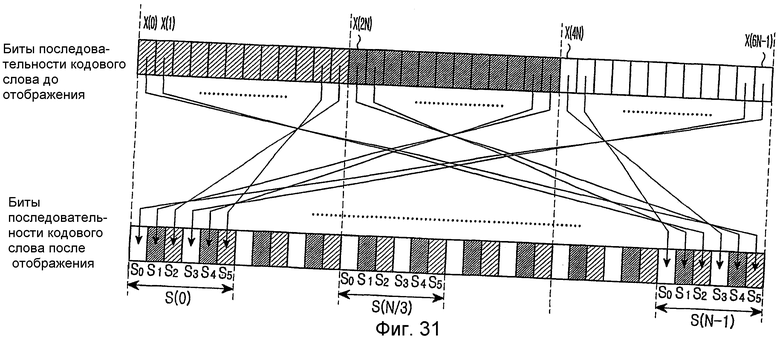

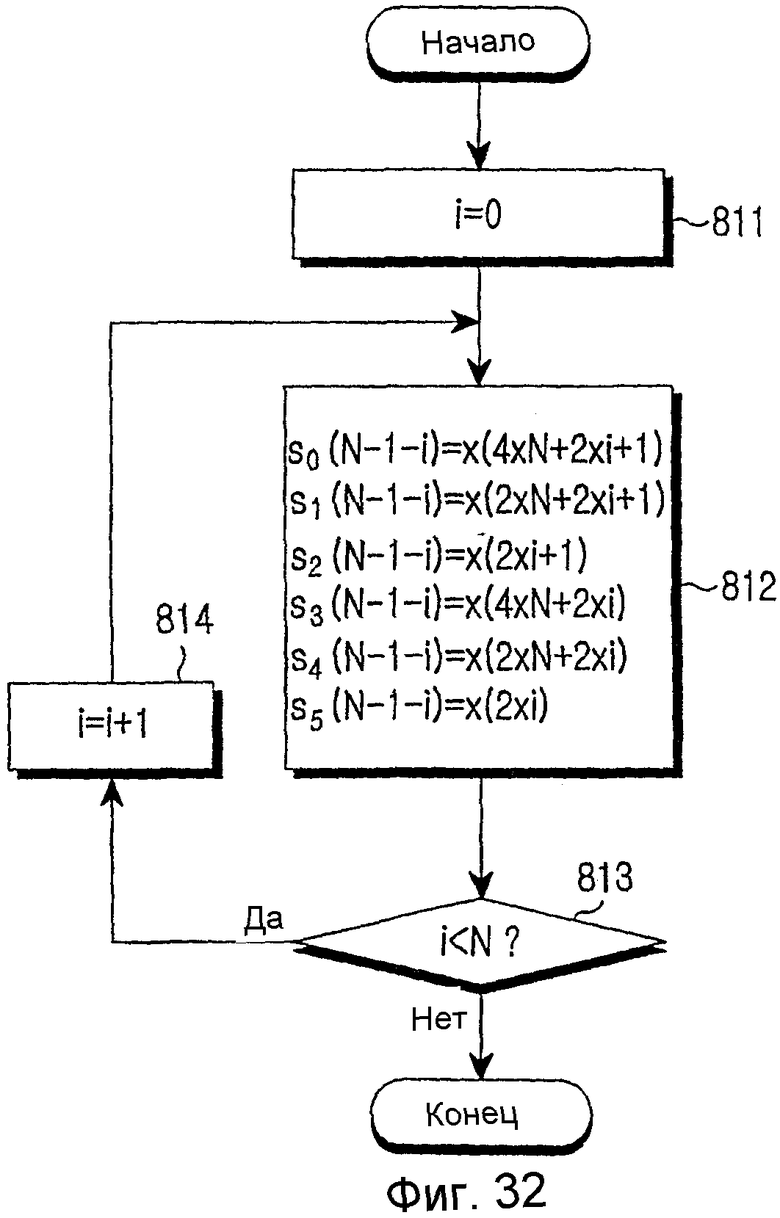

фиг.31 - операция перестановки битов, соответствующая схеме модуляции 64КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

фиг.32 - процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения;

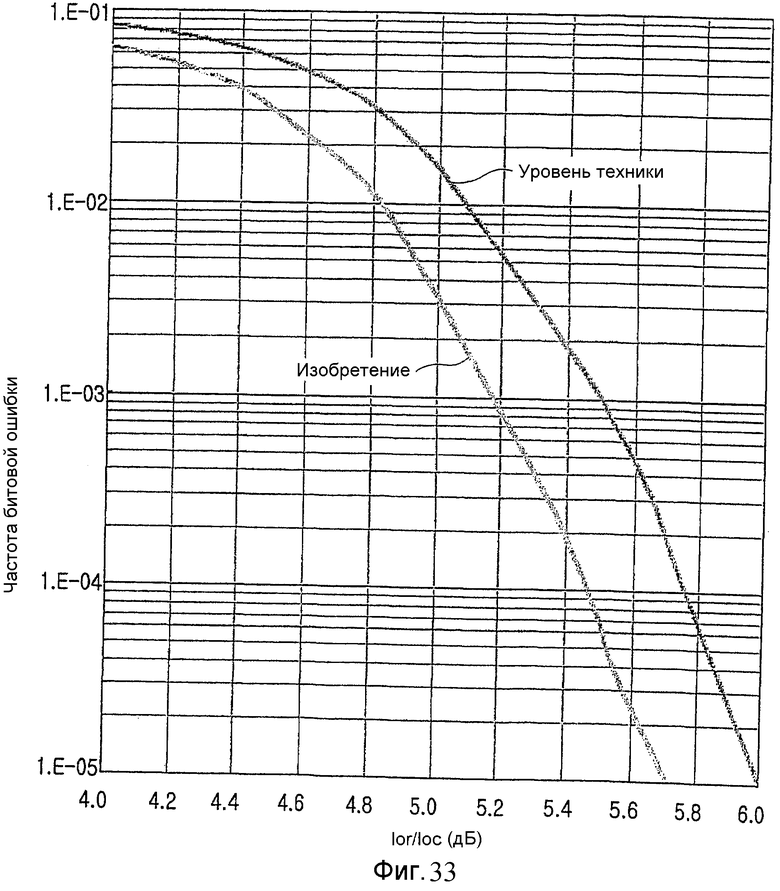

фиг.33 - характеристика средней частоты битовых ошибок, обеспечиваемая настоящим изобретением, в сравнении с той же характеристикой для уровня техники, применительно к схеме модуляции 8ФМн в случае однородного распределения мощности в последовательности кодового слова;

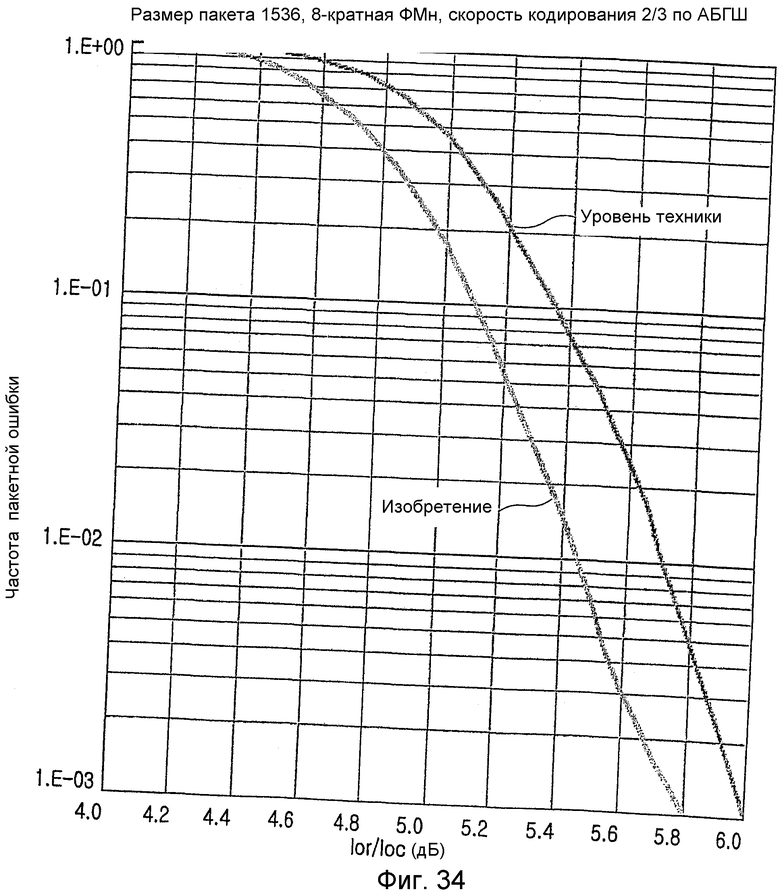

фиг.34 - характеристика средней частоты пакетных ошибок, обеспечиваемая настоящим изобретением, в сравнении с той же характеристикой для уровня техники, применительно к схеме модуляции 8ФМн в случае однородного распределения мощности в последовательности кодового слова;

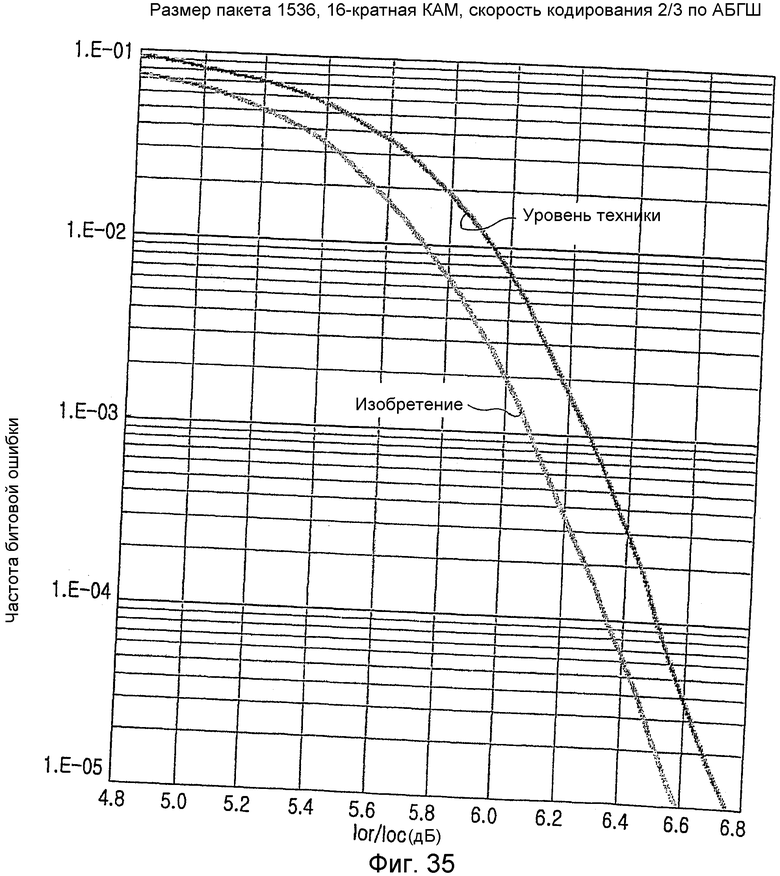

фиг.35 - характеристика средней частоты битовых ошибок, обеспечиваемая настоящим изобретением, в сравнении с той же характеристикой для уровня техники, применительно к схеме модуляции 16КАМ в случае однородного распределения мощности в последовательности кодового слова;

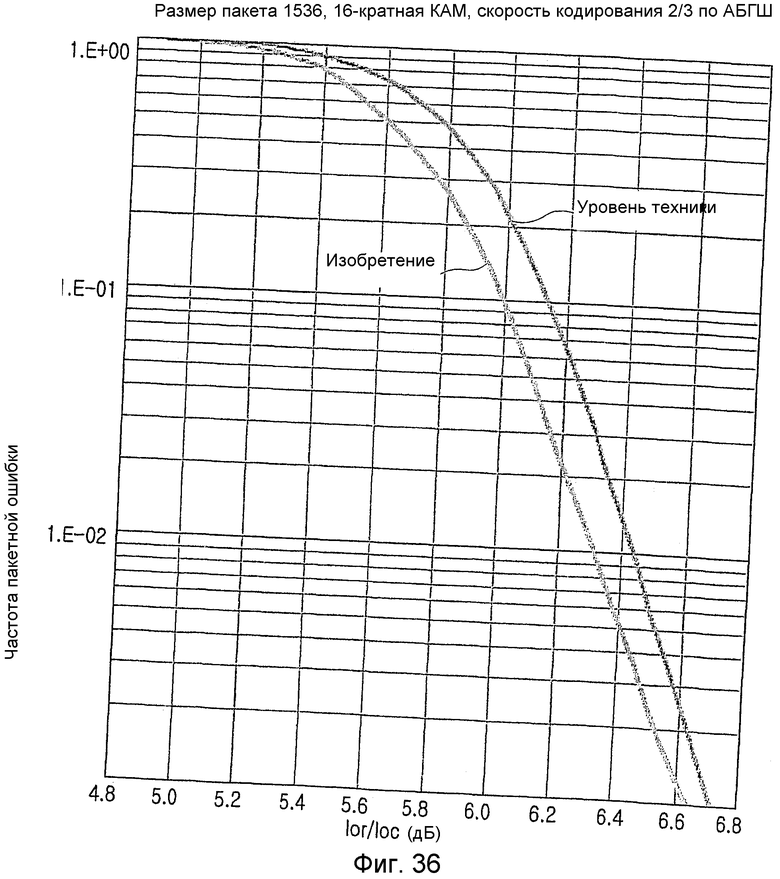

фиг.36 - характеристика средней частоты пакетных ошибок, обеспечиваемая настоящим изобретением, в сравнении с той же характеристикой для уровня техники, применительно к схеме модуляции 16КАМ в случае однородного распределения мощности в последовательности кодового слова.

Предпочтительный вариант осуществления настоящего изобретения описан ниже со ссылкой на прилагаемые чертежи. В нижеследующем описании, общеизвестные функции и конструкции не описаны подробно, чтобы не затемнять изобретение несущественными деталями.

Настоящее изобретение предусматривает (1) способ перестановки битов последовательности кодового слова, выдаваемой канальным кодером, до осуществления модуляции в системе связи, где используется многоуровневая модуляция/демодуляция, а именно, 8ФМн, 16КАМ и 64КАМ, имеющая более высокий уровень модуляции, чем КФМн, в результате чего биты с более высокой надежностью, а именно, биты, принадлежащие систематической части, размещаются в позициях с более высокой надежностью среди битов, образующих модулированный бит, (2) способ размещения выходных значений демодулятора в исходных положениях последовательности кодового слова и (3) устройство для осуществления способов. Если, после канального кодера, канальный перемежитель не используется, или, если, несмотря на использование канального перемежителя, перемеженную последовательность можно разделить на систематическую часть с более высоким приоритетом и четностную часть с более низким приоритетом, то настоящее изобретение позволяет улучшить характеристики системы с применением способа перестановки выходных битов канального кодера или канального перемежителя перед модуляцией, за счет различия в надежности между битами в схеме многоуровневой модуляции/демодуляции, и с применением способа размещения выходных значений демодулятора в исходных позициях перед декодированием канала или снятием перемежения канала. Прежде всего, обратимся к описанию передающего устройства, осуществляющего переупорядочение последовательности кодового слова согласно варианту осуществления настоящего изобретения, и приемного устройства, соответствующего передающему устройству. Затем, рассмотрим операцию переупорядочения последовательности кодового слова согласно различным вариантам осуществления настоящего изобретения. Операция переупорядочения последовательности кодового слова описана в двух аспектах. Варианты осуществления А-1, А-2, А-3, В-1, В-2 и В-3, отвечающие первому аспекту, иллюстрируют операцию переупорядочения последовательности кодового слова применительно к последовательностям кодового слова. Варианты осуществления С-1, С-2, С-3, D-1, D-2 и D-3, отвечающие второму аспекту, иллюстрируют операцию переупорядочения последовательности кодового слова применительно к модулированным битам. В основе описания вариантов осуществления, отвечающих первому аспекту, лежит предположение о том, что последовательность кодового слова состоит из N битов, а в основе описания вариантов осуществления, отвечающих второму аспекту, лежит предположение о том, что количество модулированных битов равно N. Хотя операция переупорядочения последовательности кодового слова, отвечающая настоящему изобретению, описана в двух разных аспектах, следует заметить, что обе операции, по существу, одинаковы. Наконец, мы проанализируем, каким образом операция переупорядочения последовательности кодового слова, отвечающая настоящему изобретению, улучшает характеристики системы связи.

На фиг.1 изображена конструкция передающего устройства, в состав которого входит блок отображения последовательности, осуществляющий переупорядочение последовательности кодового слова, согласно настоящему изобретению. Согласно фиг.1, канальный кодер 110 кодирует входной информационный битовый поток и выдает последовательность кодового слова, состоящую из совокупности битовых потоков. В качестве канального кодера 110 можно использовать, например, турбо-кодер. Канальный перемежитель 120 перемежает последовательность кодового слова, выдаваемую канальным кодером 110, и выдает перемеженную последовательность кодового слова. Блок 130 отображения последовательности, именно тот элемент, который отвечает настоящему изобретению, переупорядочивает последовательность кодового слова согласно различным вариантам осуществления настоящего изобретения, подготавливая ее к модуляции. Модулятор 140 модулирует последовательность кодового слова, переупорядоченную блоком 130 отображения последовательности, согласно соответствующей схеме модуляции, и генерирует модулированные биты. Модулятор 140 представляет собой многоуровневый модулятор, работающий по схеме многоуровневой (2m-кратной) модуляции, например, 8ФМн, 16КАМ и 64КАМ. Операция переупорядочения последовательности кодового слова, выполняемая блоком 130 отображения последовательности, может зависеть от того, по какой схеме модуляции работает модулятор 140. Таким образом, блок 130 отображения последовательности осуществляет операцию переупорядочения последовательности кодового слова в соответствии с одной из схем модуляции, 8ФМн, 16КАМ и 64КАМ, используемой модулятором 140.

На фиг.2 показана конструкция приемного устройства, в состав которого входит блок обратного отображения последовательности, отвечающий варианту осуществления настоящего изобретения. Приемное устройство, соответствующее передающему устройству, изображенному на фиг. 1, содержит элементы, соответствующие элементам передающего устройства и осуществляющие операции, обратные по отношению к операциям соответствующих элементов передатчика.

Согласно фиг.2, демодулятор 210, элемент, соответствующий модулятору 140, демодулирует поступающую информацию и выводит демодулированный бит. Блок 220 обратного отображения последовательности, элемент, соответствующий блоку 130 отображения последовательности, размещает демодулированный бит, поступивший от демодулятора 210, в том порядке, в каком он был размещен в исходной последовательности кодового слова до того, как она была подвергнута перестановке блоком 130 отображения последовательности. Канальный обращенный перемежитель 230, элемент, соответствующий канальному перемежителю 120, снимает перемежение последовательности кодового слова, поступившей от блока 220 обратного отображения последовательности. Канальный декодер 240, элемент, соответствующий канальному кодеру 110, декодирует выходной сигнал канального обращенного перемежителя 230. В качестве канального декодера 240 можно использовать турбо-декодер.

Прежде чем перейти к подробному описанию настоящего изобретения, рассмотрим, как блок 130 отображения последовательности, отвечающий настоящему изобретению, отображает (или группирует) входную последовательность кодового слова в соответствии со схемой модуляции. Последовательность кодового слова может поступать на блок 130 отображения последовательности либо непосредственно от канального кодера 110, изображенного на фиг.1, либо, в перемеженном виде, от канального перемежителя 120, стоящего после канального кодера 110, что также показано на фиг.1. Поэтому, используемый здесь термин “последовательность кодового слова” означает последовательность кодового слова, выдаваемую канальным кодером 110, или последовательность кодового слова, перемеженную канальным перемежителем 120 после того, как она была закодирована канальным кодером 110.

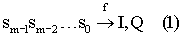

В процессе модуляции, последовательность кодового слова, выдаваемая канальным кодером 110, делится на совокупности из m битов, каждая из которых группируется в ту или иную точку сигнала среди M=2m точек сигнала согласно, например, правилу кодирования Грея. Это можно выразить как

В уравнении (1), si (i=0,1,... ,m-1) представляет (i+1)-й бит последовательности кодового слова, выдаваемой канальным кодером, группируемый в один модулированный бит. Что касается I и Q, то они представляют синфазную и квадратурную составляющие соответствующего модулированного бита, соответственно. В случае схемы модуляции 8ФМн, m=3. В случае схем модуляции 16КАМ и 64КАМ, m=4 и 6, соответственно.

В многоуровневой схеме модуляции, биты, составляющие один модулированный бит, отличаются друг от друга надежностью. Дело в том, что вероятность ошибки, обусловленной сменой какого-либо битового значения модулированного бита, сгруппированного в той или иной позиции на плоскости I-Q, вызванной шумом, в зависимости от расстояния до позиции поврежденного модулированного бита, оказывается различной. В силу этого феномена, разные биты имеют разные значения ЛОП (логарифмического отношения правдоподобия), что приводит к ухудшению характеристик канального декодера, который рассчитан на прием мягких значений битов, имеющих одинаковую частоту битовой ошибки.

В схеме модуляции 8ФМн, 2 из 3 битов, составляющих один модулированный бит, обладает одинаковой надежностью, тогда как оставшийся один бит имеет более низкую надежность, чем другие биты. Например, в случае применения диаграммы группировки сигнала для 8ФМн, изображенной на фиг.3, второй бит s1 и третий бит s2 из 3 битов имеют более высокую надежность, чем первый бит s0. В схеме модуляции 16КАМ, 2 из 4 битов, составляющих один модулированный бит, обладают более высокой надежностью по сравнению с оставшимися 2 битами. Например, в случае применения диаграммы группировки сигнала для 16КАМ, изображенной на фиг.4, второй бит s1 и четвертый бит s3 из 4 битов имеют более высокую надежность, чем первый бит s0 и третий бит s2. В схеме модуляции 64КАМ, 6 битов попарно различаются надежностью. Например, в случае применения диаграммы группировки сигнала для 64КАМ, изображенной на фиг.5, третий бит s2 и шестой бит s5 из 6 битов имеют более высокую надежность, чем второй бит s1 и пятый бит s4, а первый бит s0 и четвертый бит s3 имеют более низкую надежность. Однако, какие именно битовые позиции отличаются надежностью, может зависеть от применяемой диаграммы группировки сигнала.

Прежде всего, опишем операцию перестановки битов последовательности кодового слова, выдаваемой канальным кодером или канальным перемежителем, перед модуляцией.

Принцип изобретения

Фундаментальный принцип переупорядочения, отвечающий настоящему изобретению, состоит в таком переупорядочении последовательности кодового слова, выдаваемой канальным кодером или канальным перемежителем, при котором максимально возможное количество битов с более высоким приоритетом, например, биты кодового слова, принадлежащие систематической части, размещались бы в битовых позициях модулированного бита, обладающей более высокой надежностью. В рамках сформулированного выше принципа, перестановку битов последовательности кодового слова до генерации модулированного бита можно осуществлять по-разному в зависимости от распределения мощности в последовательности кодового слова.

Варианты осуществления, отвечающие первому аспекту

Операция перестановки битов, согласно вариантам осуществления изобретения, описана по отдельности для случая однородного распределения мощности в последовательности кодового слова и для другого случая, когда головная часть и хвостовая часть последовательности кодового слова различаются уровнем мощности. Кроме того, каждый случай отдельно описан для 8ФМн, 16КАМ и 64КАМ. В нижеследующем описании операции перестановки битов, будем предполагать, что одна последовательность кодового слова состоит из N битов, причем N в схеме модуляции 8ФМн кратно 3, в схеме модуляции 16КАМ - кратно 4 и в схеме модуляции 64КАМ - кратно 6. Представим, последовательность кодового слова до переупорядочения как {d0,d1,... ,dk,... ,dN-2,dN-1}, и представим последовательность кодового слова после переупорядочения как {b0,b1,... ,bk,... ,bN-2,bN-1}. Кроме того, предположим, что последовательность кодового слова до переупорядочения, т.е. выходная последовательность кодового слова канального кодера или канального перемежителя размещается в порядке систематической части и четностной части. Если последовательность кодового слова не размещена в порядке систематической части и четностной части, то для достижения этого упорядочения сначала нужна прямая предварительная обработка.

А. Однородное распределение мощности в последовательности кодового слова

В случае однородного распределения мощности в последовательности кодового слова, улучшить характеристику системы, а именно, снизить частоту пакетных ошибок можно, применив принцип сохранного переупорядочения. Случай однородного распределения мощности в последовательности кодового слова показан на фиг.6.

Вариант осуществления А-1 (для схемы модуляции 8ФМн)

Согласно вышесказанному, 2 из 3 битов, образующих один 8ФМн-модулированный бит, имеют более высокую надежность, чем оставшийся 1 бит. В случае использования диаграммы группировки, изображенной на фиг.3, второй бит s1 и третий бит s2 имеют более высокую надежность, чем первый бит s0. При этом, блок 130 отображения последовательности, изображенный на фиг.1, осуществляет следующую операцию переупорядочения выходной кодовой последовательности канального кодера или канального перемежителя перед модуляцией.

1. Для битов из первого периода, блок 130 отображения последовательности последовательно отображает биты с первого по {(2/3)× N}-й в позиции второго бита s1 и третьего бита s2 в каждом из (N/3) модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности последовательно отображает оставшиеся биты с {(2/3)× N+1}-го по N-й в позицию первого бита s0 в каждом из (N/3) модулированных битов.

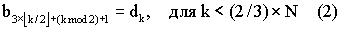

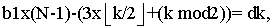

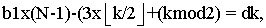

Эти процессы обобщены в уравнениях (2) и (3). На фиг.9 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

В уравнениях (2) и (3), ‘A mod B’ обозначает остаток от деления А на В, а  обозначает максимальное целое число, меньшее Х.

обозначает максимальное целое число, меньшее Х.

На фиг.9 показана операция перестановки битов для схемы модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Согласно фиг.9, последовательность кодового слова, представляющая собой N-битовый поток, делится на первый период и второй период. Первый период это промежуток между первым битом d0 и {(2/3)× N}-м битом d2N/3-1 последовательности кодового слова, а второй период это промежуток между {(2/3)× N+1}-м битом d2N/3 и N-м битом dN-1 последовательности кодового слова. В данном случае, модулированный бит состоит из 3 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N/3.

Первый бит d0 в первом периоде последовательности кодового слова отображается во вторую битовую позицию m0,s1 (т.е. b1) первого модулированного бита, и второй бит d1 в первом периоде последовательности кодового слова отображается в третью битовую позицию m0,s2 (т.е. b2) первого модулированного бита. Третий бит d2 в первом периоде отображается во вторую битовую позицию m1,s1 (т.е. b4) второго модулированного бита, и четвертый бит d3 в первом периоде отображается в третью битовую позицию m1,s2 (т.е. b5) второго модулированного бита. {(2/3)× N-1}-й бит d2N/3-2 в первом периоде отображается во вторую битовую позицию mN/3-1,s1 (т.е. bN-2) (N/3)-го модулированного бита, последнего модулированного бита, и {(2/3)× N}-й бит d2N/3-1, последний бит в первом периоде отображается в третью битовую позицию mN/3-1,s2 (т.е. bN-1) последнего модулированного бита.

{(2/3)× N+1}-й бит d2N/3, первый бит во втором периоде, отображается в первую битовую позицию m0,s0 (т.е. b0) первого модулированного бита, и {(2/3)× N+2}-й бит d2N/3+1, второй бит во втором периоде, отображается в первую битовую позицию m1,s0 второго модулированного бита. (N-1)-й бит dN-2 во втором периоде отображается в первую битовую позицию mN/3-2,s0 (т.е. bN-6) {N/3-1}-го модулированного бита, и N-й бит dN-1, последний бит во втором периоде, отображается в первую битовую позицию mN/3-1,s0 (т.е. bN-3) (N/3)-го модулированного бита, последнего модулированного бита.

На фиг.10 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.10, на этапе 301, блок 130 отображения последовательности присваивает величине k значение нуль (k=0). На этапе 302, блок 130 отображения последовательности определяет, меньше ли k значения {(2/3)× N}. Если k меньше, чем {(2/3)× N}, то блок 130 отображения последовательности осуществляет операцию этапа 303. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 304. На этапе 303, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (2). На этапе 304, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (3). Операции этапов 303 и 304 осуществляются повторно, пока на этапе 305 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 305 определено, что k меньше N, то блок 130 отображения последовательности увеличивает k на 1 на этапе 306, после чего возвращается к этапу 302.

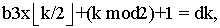

Вариант осуществления А-2 (для схемы модуляции 16КАМ)

Согласно вышесказанному, 2 из 4 битов, образующих один 16КАМ-модулированный бит, имеют более высокую надежность, чем оставшиеся 2 бита. В случае использования диаграммы группировки сигнала, изображенной на фиг.4, второй бит s1 и четвертый бит s3 имеют более высокую надежность, чем первый бит s0 и третий бит s2. При этом, блок 130 отображения последовательности осуществляет следующую операцию переупорядочения выходной последовательности кодового слова канального кодера или канального перемежителя до модуляции.

1. Для битов из первого периода, блок 130 отображения последовательности последовательно отображает биты с первого по {(1/2)× N}-й в позиции второго бита s1 и четвертого бита s3 в каждом из (N/4) модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности последовательно отображает оставшиеся биты с {(1/2)× N+1}-го по N-й в позиции первого бита s0 и третьего бита s2 в каждом из (N/4) модулированных битов.

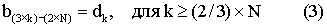

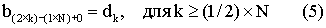

Эти процессы обобщены в уравнениях (4) и (5). На фиг.11 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

На фиг.11 показана операция перестановки битов для схемы модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Согласно фиг.11, последовательность кодового слова, представляющая собой N-битовый поток, делится на первый период и второй период. Первый период это промежуток между первым битом d0 и {(1/2)× N}-м битом dN/2-1 последовательности кодового слова, а второй период это промежуток между {(1/2)× N+1}-м битом dN/2 и N-м битом dN-1 последовательности кодового слова. В данном случае, модулированный бит состоит из 4 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N/4.

Первый бит d0 в первом периоде последовательности кодового слова отображается во вторую битовую позицию m0,s1 (т.е. b1) первого модулированного бита, и второй бит d1 в первом периоде отображается в четвертую битовую позицию m0,s3 (т.е. b3) первого модулированного бита. Третий бит d2 в первом периоде отображается во вторую битовую позицию m1,s1 (т.е. b5) второго модулированного бита, и четвертый бит d3 в первом периоде отображается в четвертую битовую позицию m1,s3 (т.е. b7) второго модулированного бита. {(1/2)× N-1}-й бит dN/2-2 в первом периоде отображается во вторую битовую позицию mN/4-1,s1 (т.е. bN-3) (N/4)-го модулированного бита, последнего модулированного бита, и {(1/2)× N}-й бит dN/2-1, последний бит в первом периоде отображается в четвертую битовую позицию mN/4-1,s3 (т.е. bN-1) последнего модулированного бита.

{(1/2)× N+1}-й бит dN/2, первый бит во втором периоде последовательности кодового слова, отображается в первую битовую позицию m0,s0 (т.е. b0) первого модулированного бита, и {(1/2)× N+2}-й бит dN/2+1, второй бит во втором периоде, отображается в третью битовую позицию m0,s2 (т.е. b2) первого модулированного бита. (N-1)-й бит dN-2 во втором периоде отображается в первую битовую позицию mN/4-1,s0 (т.е. bN-4) {N/4}-го модулированного бита, последнего модулированного бита, и N-й бит dN-1, последний бит во втором периоде, отображается в третью битовую позицию mN/4-1,s2 (т.е. bN-2) (N/4)-го модулированного бита.

На фиг.12 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.12, на этапе 401, блок 130 отображения последовательности присваивает величине k значение нуль (k=0). На этапе 402, блок 130 отображения последовательности определяет, меньше ли k значения {(1/2)× N}. Если k меньше, чем {(1/2)× N}, то блок 130 отображения последовательности осуществляет операцию этапа 403. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 404. На этапе 403, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (4). На этапе 404, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (5). Операции этапов 403 и 404 осуществляются повторно, пока на этапе 405 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 405 определено, что k меньше N, то блок 130 отображения последовательности увеличивает k на 1 на этапе 406, после чего возвращается к этапу 402.

Вариант осуществления А-3 (для схемы модуляции 64КАМ)

Согласно вышесказанному, 2 из 6 битов, образующих один 64КАМ-модулированный бит, имеют более высокую надежность, чем оставшиеся 2 пары битов. В случае использования диаграммы группировки сигнала, изображенной на фиг.5, третий бит s2 и шестой бит s5 имеют более высокую надежность, чем второй бит s1 и пятый бит s4, а первый бит s0 и четвертый бит s3 имеют более низкую надежность. При этом, блок 130 отображения последовательности осуществляет следующую операцию переупорядочения выходной последовательности кодового слова канального кодера или канального перемежителя до модуляции.

1. Для битов из первого периода, блок 130 отображения последовательности последовательно отображает биты с первого по {(1/3)× N}-й в позиции третьего бита s2 и шестого бита s5 в каждом из (N/6) модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности последовательно отображает биты с {(1/3)× N+1}-го по {(2/3)× N}-й в позиции второго бита s1 и пятого бита s4 в каждом из (N/6) модулированных битов.

3. Для битов из третьего периода, блок 130 отображения последовательности последовательно отображает оставшиеся биты с {(2/3)× N+1}-го по N-й в позиции первого бита s0 и четвертого бита s3 в каждом из (N/6) модулированных битов.

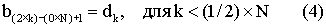

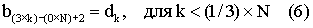

Эти процессы обобщены в уравнениях с (6) по (8). На фиг.13 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

На фиг.13 показана операция перестановки битов для схемы модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Согласно фиг.13, последовательность кодового слова, представляющая собой N-битовый поток, делится на первый период, второй период и третий период. Первый период это промежуток между первым битом d0 и {(1/3)× N}-м битом dN/3-1 последовательности кодового слова. Второй период это промежуток между {(1/3)× N+1}-м битом dN/3 и {(2/3)× N}-м битом d2N/3-1 последовательности кодового слова. Третий период это промежуток между {(2/3)× N+1}-м битом d2N/3 и N-м битом dN-1 последовательности кодового слова. В данном случае, модулированный бит состоит из 6 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N/6.

Первый бит d0 в первом периоде последовательности кодового слова отображается в третью битовую позицию m0,s2 (т.е. b2) первого модулированного бита, и второй бит d1 в первом периоде отображается в шестую битовую позицию m0,s5 (т.е. b5) первого модулированного бита. Третий бит d2 в первом периоде отображается в третью битовую позицию m1,s2 (т.е. b8) второго модулированного бита, и четвертый бит d3 в первом периоде отображается в шестую битовую позицию m1,s5 (т.е. b11) второго модулированного бита. {(1/3)× N-1}-й бит dN/3-2 в первом периоде отображается в третью битовую позицию mN/6-1,s2 (т.е. bN-4) (N/6)-го модулированного бита, последнего модулированного бита, и {(1/3)× N}-й бит dN/3-1, последний бит в первом периоде, отображается в шестую битовую позицию mN/6-1,s5 (т.е. bN-1) последнего модулированного бита.

{(1/3)× N+1}-й бит dN/3, первый бит во втором периоде последовательности кодового слова, отображается во вторую битовую позицию m0,s1 (т.е. b1) первого модулированного бита, и {(1/3)× N+2}-й бит dN/3+1, второй бит во втором периоде, отображается в пятую битовую позицию m0,s4 (т.е. b4) первого модулированного бита. {(2/3)× N-1}-й бит d2N/3-2 во втором периоде последовательности кодового слова отображается во вторую битовую позицию mN/6-1,s1 (т.е. bN-5) (N/6)-го модулированного бита, последнего модулированного бита, и {(2/3)× N}-й бит d2N/3-1, последний бит во втором периоде, отображается в пятую битовую позицию mN/6-1,s4 (т.е. bN-2) последнего модулированного бита.

{(2/3)× N+1}-й бит d2N/3, первый бит в третьем периоде последовательности кодового слова, отображается в первую битовую позицию m0,s0 (т.е. b0) первого модулированного бита, и {(2/3)× N+2}-й бит d2N/3+1, второй бит в третьем периоде, отображается в четвертую битовую позицию b0,s3 первого модулированного бита. (N-1)-й бит dN-2 в третьем периоде последовательности кодового слова отображается в первую битовую позицию mN/6-1,s0 (т.е. bN-6) {N/6}-го модулированного бита, последнего модулированного бита, и N-й бит dN-1, последний бит в четвертом периоде, отображается в третью битовую позицию mN/6-1,s3 (т.е. bN-3) последнего модулированного бита.

На фиг.14 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.14, на этапе 501, блок 130 отображения последовательности присваивает величине k значение нуль (k=0). На этапе 502, блок 130 отображения последовательности определяет, меньше ли k значения {(1/3)× N}. Если k меньше, чем {(1/3)× N}, то блок 130 отображения последовательности осуществляет операцию этапа 503. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 504. На этапе 504, блок 130 отображения последовательности определяет, меньше ли k значения {(2/3)× N}. Если k больше или равно {(1/3)× N} и меньше {(2/3× N}, то блок 130 отображения последовательности осуществляет операцию этапа 505. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 506. На этапе 503, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (6). На этапе 505, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (7). На этапе 506, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (8). Операции этапов 503, 505 и 506 осуществляются повторно, пока на этапе 507 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 507 определено, что k меньше N, то блок 130 отображения последовательности увеличивает k на 1 на этапе 508, после чего возвращается к этапу 502.

В. Головной части и хвостовой части последовательности кодового слова выделены разные уровни мощности

В случае неоднородного распределения мощности в последовательности кодового слова, можно отдельно рассмотреть следующие два варианта.

В первом варианте, головная часть последовательности кодового слова получает более высокий уровень мощности, а хвостовая часть последовательности кодового слова получает более низкий уровень мощности. Такое распределение мощности проиллюстрировано на фиг.7. В этом случае, переупорядочение выходных битов канального кодера или канального перемежителя происходит так же, как описано выше применительно к однородному распределению мощности в последовательности кодового слова. Дело в том, что, когда неоднородное распределение мощности в последовательности кодового слова неизбежно, для улучшения характеристик системы связи, более высокий уровень мощности предпочтительно выделять систематической части, а более низкий уровень мощности - четностной части.

Во втором варианте, напротив, головная часть последовательности кодового слова получает более низкий уровень мощности, а хвостовая часть последовательности кодового слова - более высокий уровень мощности. Такое распределение мощности проиллюстрировано на фиг.8. В этом случае, способ перестановки битов, используемый при однородном распределении мощности в последовательности кодового слова, необходимо модифицировать, поскольку улучшение характеристики имеет место, когда более высокий уровень мощности имеет систематическая часть, а не четностная часть. Таким образом, чтобы обеспечить более высокий уровень мощности систематической части, определенную часть последовательности кодового слова необходимо разместить в битовых позициях с одинаковой надежностью в порядке, обратном тому, который используется в вышеописанных случаях. Опишем операцию, производимую в этом случае, применительно к соответствующим схемам модуляции.

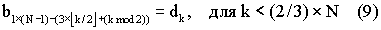

Вариант осуществления В-1 (для схемы модуляции 8ФМн)

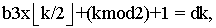

1. Для битов из первого периода, блок 130 отображения последовательности отображает, в обратном порядке, биты с первого по {(2/3)× N}-й в позиции третьего бита s2 и второго бита s1 в каждом из (N/3) модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности отображает, в обратном порядке, оставшиеся биты с {(2/3)× N+1}-го по N-й в позицию первого бита s0 в каждом из (N/3) модулированных битов.

Эти процессы обобщены в уравнениях (9) и (10). На фиг.15 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

На фиг.15 показана операция перестановки битов для схемы модуляции 8ФМн, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Согласно фиг.15, последовательность кодового слова, представляющая собой N-битовый поток, делится на первый период и второй период. Первый период это промежуток между первым битом d0 и {(2/3)× N}-м битом d2N/3-1 последовательности кодового слова, а второй период это промежуток между {(2/3)× N+1}-м битом d2N/3 и N-м битом dN-1 последовательности кодового слова. В данном случае, модулированный бит состоит из 3 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N/3.

Первый бит d0 в первом периоде последовательности кодового слова отображается в третью битовую позицию mN/3-1,s2 (т.е. bN-1) (N/3)-го модулированного бита, последнего модулированного бита, и второй бит d1 в первом периоде последовательности кодового слова отображается во вторую битовую позицию mN/3-1,s1 (т.е. bN-2) последнего модулированного бита. Третий бит d2 в первом периоде отображается в третью битовую позицию mN/3-2,s2 (т.е. bN-4) {(N/3)-1}-го модулированного бита, и четвертый бит d3 в первом периоде отображается во вторую битовую позицию mN/3-2,s1 (т.е. bN-5) {(N/3)-1}-го модулированного бита. {(2/3)× N-1}-й бит d2N/3-2 в первом периоде отображается в третью битовую позицию m0,s2 (т.е. b2) первого модулированного бита, и {(2/3)× N}-й бит d2N/3-1, последний бит в первом периоде отображается во вторую битовую позицию m0,s1 (т.е. b1) первого модулированного бита.

{(2/3)× N+1}-й бит d2N/3, первый бит во втором периоде последовательности кодового слова, отображается в первую битовую позицию mN/3-1,s0 (т.е. bN-3) (N/3)-го модулированного бита, последнего модулированного бита, и {(2/3)× N+2}-й бит d2N/3+1, второй бит во втором периоде, отображается в первую битовую позицию mN/3-2,s0 (т.е. bN-6) {(N/3)-1}-го модулированного бита. (N-1)-й бит dN-2 во втором периоде отображается в первую битовую позицию m1,s0 (т.е. b3) второго модулированного бита, и N-й бит dN-1, последний бит во втором периоде, отображается в первую битовую позицию m0,s0 (т.е. b0) первого модулированного бита.

На фиг.16 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.16, на этапе 601, блок 130 отображения последовательности присваивает величине k значение нуль (k=0). На этапе 602, блок 130 отображения последовательности определяет, меньше ли k значения {(2/3)× N}. Если k меньше, чем {(2/3)× N}, то блок 130 отображения последовательности осуществляет операцию этапа 603. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 604. На этапе 603, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (9). На этапе 604, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (10). Операции этапов 603 и 604 осуществляются повторно, пока на этапе 605 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 605 определено, что k меньше N, то блок 130 отображения последовательности увеличивает k на 1 на этапе 606, после чего возвращается к этапу 602.

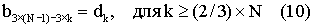

Вариант осуществления В-2 (для схемы модуляции 16КАМ)

1. Блок 130 отображения последовательности располагает выходную последовательность кодового слова канального кодера или канального перемежителя в порядке систематической части и четностной части.

2. Для битов из первого периода, блок 130 отображения последовательности отображает, в обратном порядке, биты с первого по {(1/2)× N}-й в позиции четвертого бита s3 и второго бита s1 в каждом из (N/4) модулированных битов.

3. Для битов из второго периода, блок 130 отображения последовательности отображает, в обратном порядке, оставшиеся биты с {(1/2)× N+1}-го по N-й в позиции третьего бита s2 и первого бита s0 в каждом из (N/4) модулированных битов.

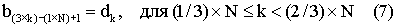

Эти процессы обобщены в уравнениях (11) и (12). На фиг.17 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

На фиг.17 показана операция перестановки битов для схемы модуляции 16КАМ, при условии, что более высокий уровень мощности выделяется хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Согласно фиг.17, последовательность кодового слова, представляющая собой N-битовый поток, делится на первый период и второй период. Первый период это промежуток между первым битом d0 и {(1/2)× N}-м битом dN/2-1 последовательности кодового слова, а второй период это промежуток между {(1/2)× N+1}-м битом dN/2 и N-м битом dN-1 последовательности кодового слова. В данном случае, модулированный бит состоит из 4 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N/4.

Первый бит d0 в первом периоде последовательности кодового слова отображается в четвертую битовую позицию mN/4-1,s3 (т.е. bN-1) (N/4)-го модулированного бита, последнего модулированного бита, и второй бит d1 в первом периоде последовательности кодового слова отображается во вторую битовую позицию mN/4-1,s1 (т.е. bN-3) последнего модулированного бита. Третий бит d2 в первом периоде отображается в четвертую битовую позицию mN/4-2,s3 (т.е. bN-5) {(N/4)-1}-го модулированного бита, и четвертый бит d3 в первом периоде отображается во вторую битовую позицию mN/4-2,s1 (т.е. bN-7) {(N/4)-1}-го модулированного бита. {(1/2)× N-1}-й бит dN/2-2 в первом периоде отображается в четвертую битовую позицию m0,s3 (т.е. b3) первого модулированного бита, и {(1/2)× N}-й бит dN/2-1, последний бит в первом периоде, отображается во вторую битовую позицию m0,s1 (т.е. b1) первого модулированного бита.

{(1/2)× N+1}-й бит dN/2, первый бит во втором периоде последовательности кодового слова, отображается в третью битовую позицию mN/4-1,s2 (т.е. bN-2) (N/4)-го модулированного бита, последнего модулированного бита, и {(1/2)× N+2}-й бит dN/2+1, второй бит во втором периоде, отображается в первую битовую позицию mN/4-1,s0 (т.е. bN-4) последнего модулированного бита. (N-1)-й бит dN-2 во втором периоде отображается в третью битовую позицию m0,s2 (т.е. b2) первого модулированного бита, и N-й бит dN-1, последний бит во втором периоде, отображается в первую битовую позицию m0,s0 (т.е. b0) первого модулированного бита.

На фиг.18 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения.

Согласно фиг.18, на этапе 701, блок 130 отображения последовательности присваивает величине k значение нуль (k=0). На этапе 702, блок 130 отображения последовательности определяет, меньше ли k значения {(1/2)× N}. Если k меньше, чем {(1/2)× N}, то блок 130 отображения последовательности осуществляет операцию этапа 703. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 704. На этапе 703, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (11). На этапе 704, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (12). Операции этапов 703 и 704 осуществляются повторно, пока на этапе 705 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 705 определено, что k меньше N, то блок 130 отображения последовательности увеличивает k на 1 на этапе 706, после чего возвращается к этапу 702.

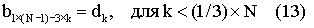

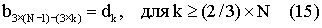

Вариант осуществления В-3 (для схемы модуляции 64КАМ)

1. Для битов из первого периода, блок 130 отображения последовательности отображает, в обратном порядке, биты с первого по {(1/3)× N}-й в позиции шестого бита s5 и третьего бита s2 в каждом из (N/6) модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности отображает, в обратном порядке, биты с {(1/3)× N+1}-го по {(2/3)× N}-й в позиции пятого бита s4 и второго бита s1 в каждом из (N/6) модулированных битов.

3. Для битов из третьего периода, блок 130 отображения последовательности отображает, в обратном порядке, оставшиеся биты с {(2/3)× N+1}-го по N-й в позиции четвертого бита s3 и первого бита s0 в каждом из (N/6) модулированных битов.

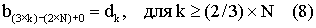

Эти процессы обобщены в уравнениях с (13) по (15). На фиг.19 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

На фиг.19 показана операция перестановки битов для схемы модуляции 64КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Согласно фиг.19, последовательность кодового слова, представляющая собой N-битовый поток, делится на первый период, второй период и третий период. Первый период это промежуток между первым битом d0 и {(1/3)× N}-м битом dN/3-1 последовательности кодового слова. Второй период это промежуток между {(1/3)× N+1}-м битом dN/3 и {(2/3)× N}-м битом d2N/3-1 последовательности кодового слова. Третий период это промежуток между {(2/3)× N+1}-м битом d2N/3 и N-м битом dN-1 последовательности кодового слова. В данном случае, модулированный бит состоит из 6 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N/6.

Первый бит d0 в первом периоде последовательности кодового слова отображается в шестую битовую позицию mN/6-1,s5 (т.е. bN-1) (N/6)-го модулированного бита, последнего модулированного бита, и второй бит d1 в первом периоде отображается в третью битовую позицию mN/6-1,s2 (т.е. bN-4) последнего модулированного бита. Третий бит d2 в первом периоде отображается в шестую битовую позицию mN/6-2,s5 (т.е. bN-7) {(N/6)-1}-го модулированного бита, и четвертый бит d3 в первом периоде отображается в третью битовую позицию mN/6-2,s2 (т.е. bN-10) {(N/6)-1}-го модулированного бита. {(1/3)× N-1}-й бит dN/3-2 в первом периоде отображается в шестую битовую позицию m0,s5 (т.е. b5) первого модулированного бита, и {(1/3)× N}-й бит dN/3-1, последний бит в первом периоде отображается в третью битовую позицию m0,s2 (т.е. b2) первого модулированного бита.

{(1/3)× N+1}-й бит dN/3, первый бит во втором периоде последовательности кодового слова, отображается в пятую битовую позицию mN/6-1,s4 (т.е. bN-2) (N/6)-го модулированного бита, последнего модулированного бита, и {(1/3)× N+2}-й бит dN/3+1, второй бит во втором периоде, отображается во вторую битовую позицию mN/6-1,s1 (т.е. bN-5) последнего модулированного бита. {(2/3)× N-1}-й бит d2N/3-2 во втором периоде последовательности кодового слова отображается в пятую битовую позицию m0,s4 (т.е. b4) первого модулированного бита, и {(2/3)× N}-й бит d2N/3-1, последний бит во втором периоде, отображается во вторую битовую позицию m0,s1 (т.е. b1) первого модулированного бита.

{(2/3)× N+1}-й бит d2N/3, первый бит в третьем периоде последовательности кодового слова, отображается в четвертую битовую позицию mN/6-1,s3 (т.е. bN-3) {N/6}-го модулированного бита, последнего модулированного бита, а {(2/3)× N+2}-й бит d2N/3+1, второй бит в третьем периоде, отображается в первую битовую позицию mN/6-1,s0 (т.е. bN-6) последнего модулированного бита. (N-1)-й бит dN-2 в третьем периоде последовательности кодового слова отображается в четвертую битовую позицию m0,s3 (т.е. b3) первого модулированного бита, и N-й бит dN-1, последний бит в третьем периоде, отображается в первую битовую позицию m0,s0 (т.е. b0) первого модулированного бита.

На фиг.20 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии, что более высокий уровень мощности выделен хвостовой части последовательности кодового слова, согласно варианту осуществления настоящего изобретения.

Согласно фиг.20, на этапе 801, блок 130 отображения последовательности присваивает величине k значение нуль (k=0). На этапе 802, блок 130 отображения последовательности определяет, меньше ли k значения {(1/3)× N}. Если k меньше, чем {(1/3)× N}, то блок 130 отображения последовательности осуществляет операцию этапа 803. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 804. На этапе 804, блок 130 отображения последовательности определяет, меньше ли k значения {(2/3)× N}. Если k больше или равно {(1/3)× N} и меньше {(2/3× N}, то блок 130 отображения последовательности осуществляет операцию этапа 805. В противном случае, блок 130 отображения последовательности осуществляет операцию этапа 806. На этапе 803, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (13). На этапе 805, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (14). На этапе 806, блок 130 отображения последовательности осуществляет битовое отображение на последовательности кодового слова в соответствии с уравнением (15). Операции этапов 803, 805 и 806 осуществляются повторно, пока на этапе 807 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 807 определено, что k меньше N, то блок 130 отображения последовательности увеличивает k на 1 на этапе 808, после чего возвращается к этапу 802.

Выше была описана операция перестановки битов исходной последовательности кодового слова, выдаваемой канальным кодером или канальным перемежителем, осуществляемая до модуляции, согласно вариантам осуществления настоящего изобретения. Теперь, перейдем к описанию операции размещения выходных значений демодулятора в порядке исходной последовательности кодового слова перед декодированием канала или снятием перемежения канала.

Операция размещения выходных значений демодулятора в порядке исходной последовательности кодового слова представляет собой обратную операцию по отношению к вышеописанной операции переупорядочения. Если выходную последовательность демодулятора представить в виде {q0,q1,... ,qk,... ,qN-2,qN-1}, последовательность, выстроенную в исходном порядке перед канальным декодированием или канальным снятием перемежения, представить в виде {p0,p1,... ,pk,... ,pN-2,pN-1}, нижний индекс левого члена b в уравнениях с (2) по (15) обозначить m и нижний индекс правого члена d обозначить n, то процесс размещения значений выходной последовательности демодулятора в исходном порядке перед декодированием канала или снятием перемежения канала можно выразить следующим образом:

qm ⇒ pn, для всех m и n (однако, m и n ∈ {0,1,... ,N-1}) (16)

Варианты осуществления, отвечающие второму аспекту

Операция перестановки битов, согласно вариантам осуществления изобретения, описана по отдельности для случая, однородного распределения мощности в последовательности кодового слова, и для другого случая, когда головная часть и хвостовая часть последовательности кодового слова имеют разные уровни мощности. Кроме того, каждый случай отдельно описан для 8ФМн, 16КАМ и 64КАМ. В нижеследующем описании операции перестановки битов будем предполагать, что количество модулированных битов, составляющих одну последовательность модулированных битов, равно N, и последовательность кодового слова до переупорядочения, т.е. выходная последовательность канального кодера или канального перемежителя представлена в виде {x(0),…,x(k),…,x(N× m-1)}, и последовательность кодового слова после переупорядочения представлена в виде s0(i),... ,sm-1(i), где i∈ {0,... ,N-1}. Кроме того, предположим, что последовательность кодового слова до переупорядочения расположена в порядке систематической части и четностной части. Если последовательность кодового слова не расположена в порядке систематической части и четностной части, то, для достижения этого упорядочения, сначала требуется прямая предварительная обработка.

С. Однородное распределение мощности в последовательности кодового слова

В случае однородного распределения мощности в последовательности кодового слова, улучшить характеристику системы, а именно, снизить частоту пакетных ошибок можно, применив принцип сохранного переупорядочения. Случай однородного распределения мощности в последовательности кодового слова показан на фиг.6.

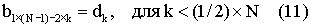

Вариант осуществления С-1 (для схемы модуляции 8ФМн)

Согласно вышесказанному, 2 из 3 битов, образующих один 8ФМн-модулированный бит, имеют более высокую надежность, чем оставшийся 1 бит. В случае использования диаграммы группировки, изображенной на фиг.3, второй бит s1 и третий бит s2 имеют более высокую надежность, чем первый бит s0. При этом, блок 130 отображения последовательности, изображенный на фиг.1, осуществляет следующую операцию переупорядочения выходной кодовой последовательности канального кодера или канального перемежителя перед модуляцией.

1. Для битов из первого периода, блок 130 отображения последовательности последовательно отображает биты с первого по {2× N}-й в позиции второго бита s1 и третьего бита s2 в каждом из N модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности последовательно отображает оставшиеся биты с {2× N+1}-го по {3× N}-й в позицию первого бита s0 в каждом из N модулированных битов.

Эти процессы обобщены в уравнениях с (17) по (19). На фиг.21 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

s0(i) = x(2× N+i) (17)

s1(i) = x(2× i) (18)

s2(i) = x(2× i+1) (19)

На фиг.21 показана операция перестановки битов для схемы модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Заметим, что эта операция перестановки битов идентична операции перестановки битов, показанной на фиг.9.

Согласно фиг.21, последовательность кодового слова, представляющая собой 3N-битовый поток, делится на первый период и второй период. Первый период это промежуток между первым битом x(0) и {2× N}-м битом x(2N-1) последовательности кодового слова, а второй период это промежуток между {2× N+1}-м битом x(2N) и {3× N}-м битом x(3N-1) последовательности кодового слова. В данном случае, модулированный бит состоит из 3 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N.

Первый бит x(2N) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(0) первого модулированного бита, первый бит х(0) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(0) первого модулированного бита, и второй бит x(1) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(0) первого модулированного бита.

Второй бит x(2N+1) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(1) второго модулированного бита, третий бит х(2) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(1) второго модулированного бита, и четвертый бит x(3) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(1) второго модулированного бита.

Третий бит x(2N+2) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(2) третьего модулированного бита, пятый бит х(4) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(2) третьего модулированного бита, и шестой бит x(5) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(2) третьего модулированного бита.

{3N-1}-й бит x(3N-2) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(N-2) (N-1)-го модулированного бита, {2N-3}-й бит х(2N-4) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(N-2) (N-1)-го модулированного бита, и {2N-2}-й бит x(2N-3) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(N-2) (N-1)-го модулированного бита.

{3× N}-й бит x(3N-1) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(N-1) N-го модулированного бита, {2N-1}-й бит х(2N-2) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(N-1) N-го модулированного бита, и {2× N}-й бит x(2N-1) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(N-1) N-го модулированного бита.

На фиг.22 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 8ФМн, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.22, на этапе 311, блок 130 отображения последовательности, присваивает величине i значение нуль (i=0). На этапе 312, блок 130 отображения последовательности осуществляет операцию перестановки битов последовательности кодового слова в соответствующие битовые позиции модулированного бита согласно уравнениям (17)-(19). Таким образом, блок 130 отображения последовательности отображает бит x(2× N+i) в битовом потоке последовательности кодового слова в первую битовую позицию s0(i) i-го модулированного бита, отображает бит x(2× i) в битовом потоке последовательности кодового слова во вторую битовую позицию s1(i) i-го модулированного бита и отображает бит x(2× i+1) в битовом потоке последовательности кодового слова в третью битовую позицию s2(i) i-го модулированного бита. Операция этапа 312 осуществляется повторно, пока на этапе 313 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 313 определено, что i меньше N, то блок 130 отображения последовательности увеличивает i на 1 на этапе 314, после чего возвращается к этапу 312.

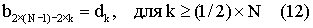

Вариант осуществления С-2 (для схемы модуляции 16КАМ)

Согласно вышесказанному, 2 из 4 битов, образующих один 16КАМ-модулированный бит, имеют более высокую надежность, чем оставшиеся 2 бита. В случае использования диаграммы группировки сигнала, изображенной на фиг.4, второй бит s1 и четвертый бит s3 имеют более высокую надежность, чем первый бит s0 и третий бит s2. При этом, блок 130 отображения последовательности осуществляет следующую операцию переупорядочения выходной последовательности кодового слова канального кодера или канального перемежителя до модуляции.

1. Для битов из первого периода, блок 130 отображения последовательности последовательно отображает биты с первого по {2× N}-й в позиции второго бита s1 и четвертого бита s3 в каждом из N модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности последовательно отображает оставшиеся биты с {2× N+1}-го по {4× N}-й в позиции первого бита s0 и третьего бита s2 в каждом из N модулированных битов.

Эти процессы обобщены в уравнениях с (20) по (23). На фиг.23 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

s0(i) = x(2× N+2× i) (20)

s1(i) = x(2× i) (21)

s2(i) = x(2× N+2× i+1) (22)

s3(i) = x(2× i+1) (23)

На фиг.23 показана операция перестановки битов для схемы модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Заметим, что эта операция перестановки битов идентична операции перестановки битов, показанной на фиг.11.

Согласно фиг.23, последовательность кодового слова, представляющая собой 4N-битовый поток, делится на первый период и второй период. Первый период это промежуток между первым битом x(0) и {2× N}-м битом x(2N-1) последовательности кодового слова, а второй период это промежуток между {2× N+1}-м битом x(2N) и {4× N}-м битом x(4N-1) последовательности кодового слова. В данном случае, модулированный бит состоит из 4 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N.

Первый бит x(2N) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(0) первого модулированного бита, первый бит х(0) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(0) первого модулированного бита, второй бит x(2N+1) во втором периоде последовательности кодового слова отображается в третью битовую позицию s2(0) первого модулированного бита, и второй бит x(1) в первом периоде последовательности кодового слова отображается в четвертую битовую позицию s3(0) первого модулированного бита.

Третий бит x(2N+2) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(1) второго модулированного бита, третий бит х(2) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(1) второго модулированного бита, четвертый бит x(2N+3) во втором периоде последовательности кодового слова отображается в третью битовую позицию s2(1) второго модулированного бита, и четвертый бит x(3) в первом периоде последовательности кодового слова отображается в четвертую битовую позицию s3(1) второго модулированного бита.

{4N-3}-й бит x(4N-4) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(N-2) (N-1)-го модулированного бита, {2N-3}-й бит х(2N-4) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(N-2) (N-1)-го модулированного бита, {4N-2}-й бит x(4N-3) во втором периоде последовательности кодового слова отображается в третью битовую позицию s2(N-2) (N-1)-го модулированного бита, и {2N-2}-й бит x(2N-3) в первом периоде последовательности кодового слова отображается в четвертую битовую позицию s3(N-2) (N-1)-го модулированного бита.

{4N-1}-й бит x(4N-2) во втором периоде последовательности кодового слова отображается в первую битовую позицию s0(N-1) N-го модулированного бита, {2N-1}-й бит х(2N-2) в первом периоде последовательности кодового слова отображается во вторую битовую позицию s1(N-1) N-го модулированного бита, {4× N}-й бит x(4N-1) во втором периоде последовательности кодового слова отображается в третью битовую позицию s2(N-1) N-го модулированного бита, и {2× N}-й бит x(2N-1) в первом периоде последовательности кодового слова отображается в четвертую битовую позицию s3(N-1) N-го модулированного бита.

На фиг.24 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 16КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.24, на этапе 411, блок 130 отображения последовательности присваивает величине i значение нуль (i=0). На этапе 412, блок 130 отображения последовательности осуществляет операцию перестановки битов последовательности кодового слова в соответствующие битовые позиции модулированного бита согласно уравнениям (20)-(23). Таким образом, блок 130 отображения последовательности отображает бит x(2× N+2× i) в битовом потоке последовательности кодового слова в первую битовую позицию s0(i) i-го модулированного бита, отображает бит x(2× i) в битовом потоке последовательности кодового слова во вторую битовую позицию s1(i) i-го модулированного бита, отображает бит x(2× N+2× i+1) в битовом потоке последовательности кодового слова в третью битовую позицию s2(i) i-го модулированного бита, и отображает бит x(2× i+1) в битовом потоке последовательности кодового слова в четвертую битовую позицию s3(i) i-го модулированного бита. Операция этапа 412 осуществляется повторно, пока на этапе 413 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 413 определено, что i меньше N, то блок 130 отображения последовательности увеличивает i на 1 на этапе 414, после чего возвращается к этапу 412.

Вариант осуществления С-3 (для схемы модуляции 64КАМ)

Согласно вышесказанному, 2 из 6 битов, образующих один 64КАМ-модулированный бит, имеют более высокую надежность, чем оставшиеся 2 пары битов. В случае использования диаграммы группировки сигнала, изображенной на фиг.5, третий бит s2 и шестой бит s5 имеют более высокую надежность, чем второй бит s1 и пятый бит s4, а первый бит s0 и четвертый бит s3 имеют более низкую надежность. При этом, блок 130 отображения последовательности осуществляет следующую операцию переупорядочения выходной последовательности кодового слова канального кодера или канального перемежителя до модуляции.

1. Для битов из первого периода, блок 130 отображения последовательности последовательно отображает биты с первого по {2× N}-й в позиции третьего бита s2 и шестого бита s5 в каждом из N модулированных битов.

2. Для битов из второго периода, блок 130 отображения последовательности последовательно отображает биты с {2× N+1}-го по {4× N}-й в позиции второго бита s1 и пятого бита s4 в каждом из N модулированных битов.

3. Для битов из третьего периода, блок 130 отображения последовательности последовательно отображает оставшиеся биты с {4× N+1}-го по {6× N}-й в позиции первого бита s0 и четвертого бита s3 в каждом из N модулированных битов.

Эти процессы обобщены в уравнениях с (24) по (29). На фиг.25 показано, как происходит переупорядочение битов последовательности кодового слова, имеющей место до перестановки.

s0(i) = x(4× N+2× i) (24)

s1(i) = x(2× N+2× i) (25)

s2(i) = x(2× i) (26)

s3(i) = x(4× N+2× i+1) (27)

s4(i) = x(2× N+2× i+1) (28)

s5(i) = x(2× i+1) (29)

На фиг.25 показана операция перестановки битов для схемы модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Заметим, что эта операция перестановки битов идентична операции перестановки битов, показанной на фиг.13.

Согласно фиг.25, последовательность кодового слова, представляющая собой 6N-битовый поток, делится на первый период, второй период и третий период. Первый период это промежуток между первым битом x(0) и {2× N}-м битом x(2N-1) последовательности кодового слова. Второй период это промежуток между {2× N+1}-м битом x(2N) и {4× N}-м битом x(4N-1) последовательности кодового слова. Третий период это промежуток между {4× N+1}-м битом x(4N) и {6× N}-м битом x(6N-1) последовательности кодового слова. В данном случае, модулированный бит состоит из 6 битов, и количество модулированных битов, соответствующих последовательности кодового слова, равно N.

Первый бит x(4N) в третьем периоде последовательности кодового слова отображается в первую битовую позицию s0(0) первого модулированного бита, первый бит х(2N) во втором периоде последовательности кодового слова отображается во вторую битовую позицию s1(0) первого модулированного бита, первый бит х(0) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(0) первого модулированного бита, второй бит x(4N+1) в третьем периоде последовательности кодового слова отображается в четвертую битовую позицию s3(0) первого модулированного бита, второй бит x(2N+1) во втором периоде последовательности кодового слова отображается в пятую битовую позицию s4(0) первого модулированного бита, и второй бит x(1) в первом периоде последовательности кодового слова отображается в шестую битовую позицию s5(0) первого модулированного бита.

{6N-1}-й бит x(6N-2) в третьем периоде последовательности кодового слова отображается в первую битовую позицию s0(N-1) N-го модулированного бита, {4N-1}-й бит x(4N-2) во втором периоде последовательности кодового слова отображается во вторую битовую позицию s1(N-1) N-го модулированного бита, {2N-1}-й бит х(2N-2) в первом периоде последовательности кодового слова отображается в третью битовую позицию s2(N-1) N-го модулированного бита, {6× N}-й бит x(6N-1) в третьем периоде последовательности кодового слова отображается в четвертую битовую позицию s3(N-1) N-го модулированного бита, {4× N}-й бит x(4N-1) во втором периоде последовательности кодового слова отображается в пятую битовую позицию s4(N-1) N-го модулированного бита, и {2× N}-й бит x(2N-1) в первом периоде последовательности кодового слова отображается в шестую битовую позицию s5(N-1) N-го модулированного бита.

На фиг.26 показана процедура для осуществления операции перестановки битов, соответствующей схеме модуляции 64КАМ, при условии однородного распределения мощности в последовательности кодового слова, согласно варианту осуществления настоящего изобретения. Эта процедура осуществляется блоком 130 отображения последовательности, изображенным на фиг.1.

Согласно фиг.26, на этапе 511, блок 130 отображения последовательности присваивает величине i значение нуль (i=0). На этапе 512, блок 130 отображения последовательности осуществляет операцию перестановки битов последовательности кодового слова в соответствующие битовые позиции модулированного бита согласно уравнениям (24)-(29). Таким образом, блок 130 отображения последовательности отображает бит x(4× N+2× i) в битовом потоке последовательности кодового слова в первую битовую позицию s0(i) i-го модулированного бита, отображает бит x(2× N+2× i) в битовом потоке последовательности кодового слова во вторую битовую позицию s1(i) i-го модулированного бита, отображает бит x(2× i) в битовом потоке последовательности кодового слова в третью битовую позицию s2(i) i-го модулированного бита, отображает бит x(4× N+2× i+1) в битовом потоке последовательности кодового слова в четвертую битовую позицию s3(i) i-го модулированного бита, отображает бит x(2× N+2× i+1) в битовом потоке последовательности кодового слова в пятую битовую позицию s4(i) i-го модулированного бита, и отображает бит x(2× i+1) в битовом потоке последовательности кодового слова в шестую битовую позицию s5(i) i-го модулированного бита. Операция этапа 512 осуществляется повторно, пока на этапе 513 не будет определено, что битовое отображение полностью произведено на всех битах последовательности кодового слова. Таким образом, если на этапе 513 определено, что i меньше N, то блок 130 отображения последовательности увеличивает i на 1 на этапе 514, после чего возвращается к этапу 512.

D. Головной части и хвостовой части последовательности кодового слова выделены разные уровни мощности

В случае неоднородного распределения мощности в последовательности кодового слова, можно отдельно рассмотреть следующие два варианта.